стоверности приема передаваемой информации за счет формирования на передающей стороне двоичного кода информации в прямом и инверсном видах сигнала синхронизации, состоящего из единиц, который отличается от любого кода информации, а на приемной стороне - записи информации только в случае совпадения прямого и инверсного кодов информации и выделенного тактового импульса. Причем запись в выходной регистр памяти будет осуществляться только после приема и выделения сигнала синхронизации Устройство содержит на передающей стороне мультиплексор 2, источники

информации 3, счетчики 4, 7, генератор 5 тактовых импульсов, ключ 6, передатчик 8, элементы ИЛИ 9, 10, регистры сдвига 14, 15, блок элементов НЕ 16, делитель частоты 18, дешифратор 17, элементы И 12, 19, 20, элемент НЕ 13; на приемной стороне 21 - приемник 22, регистры сдвига 23, 32, счетчик 24, дешифраторы 25,

35,элементы И 19, 29, блок ключей 27, блок памяти 28, элемент ИЛИ 30, блок поразрядного сравнения 33, блок элементов НЕ 31, делитель частоты

34. Приемная сторона соединена с передающей проводной линией связи

36.1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля и индикации | 1991 |

|

SU1807452A1 |

| Устройство для контроля времени работы оборудования | 1990 |

|

SU1815664A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для передачи и приема цифровой информации | 1986 |

|

SU1322344A1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1547078A1 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Устройство управления передачей информации в многопроцессорной системе | 1988 |

|

SU1640705A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

Изобретение относится к технике передачи цифровой информации по проводной линии связи и может быть применено в системах телеуправления, телесигнализации, телесбора данных. Цель изобретения - повышение функциональной надежности устройства и достоверности приема передаваемой информации за счет формирования на передающей стороне двоичного кода информации в прямом и инверсном видах и сигнала синхронизации, состоящего из единиц, который отличается от любого кода информации, а на приемной стороне- записи информации только в случае совпадения прямого и инверсного кодов информации и выделенного тактового импульса. Причем запись в выходной регистр памяти будет осуществляться только после приема и выделения сигнала синхронизации. Устройство содержит на передающей стороне мультиплексор 2, источники информации 3, счетчики 4, 7, генератор 5 тактовых импульсов, ключ 6, передатчик 8, элементы ИЛИ 9, 10, регистры сдвига 14, 15, блок элементов НЕ 16, делитель частоты 18, дешифратор 17, элементы И 12, 19, 200, элемент НЕ 13

на приемной стороне 21 - приемник 22, регистры сдвига 23, 32, счетчик 24, дешифраторы 25, 35, элементы И 19, 29, блок ключей 27, блок памяти 28, элемент ИЛИ 30, блок поразрядного сравнения 33, блок элементов НЕ 31, делитель частоты 34. Приемная сторона соединена с передающей проводной линией связи 36. 1 ил.

1

Изобретение относится к технике передачи цифровой информации по проводным линиям связи и может быть применено в системах телеуправления, телесигнализации и телесбора двоичной информации.

Цель изобретения - повышение функциональной надежности приема передаваемой информации и ее достоверности.

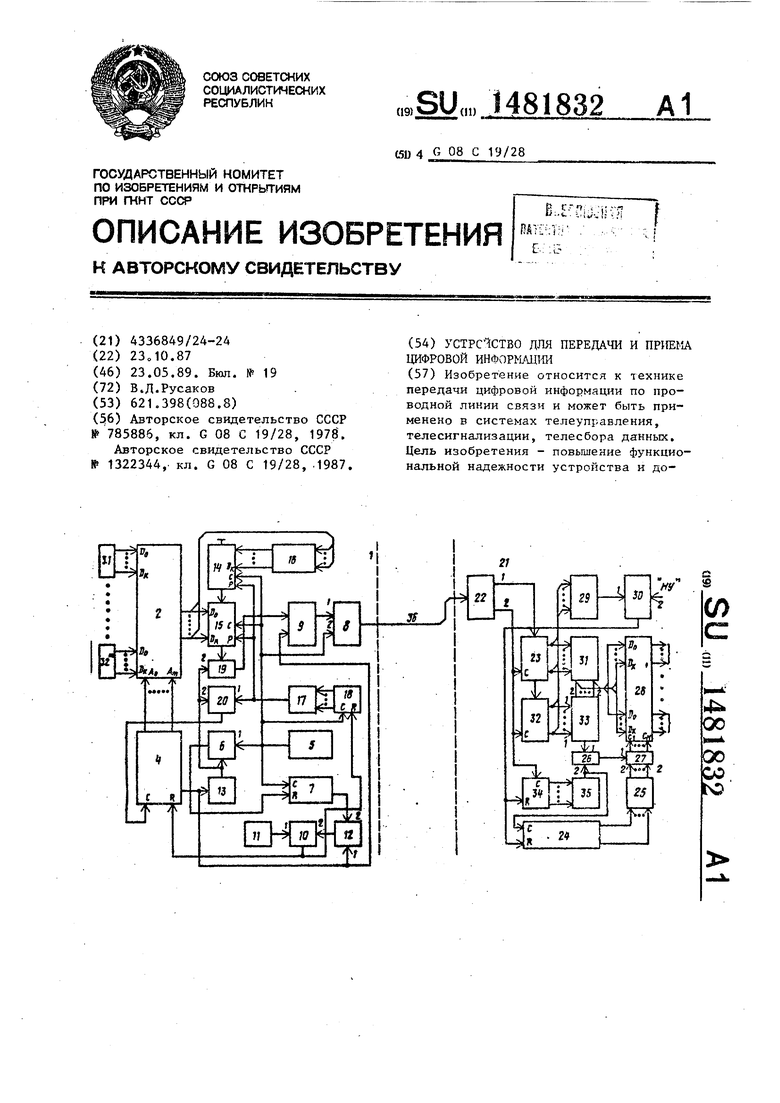

На чертеже представлена функциональная схема устройства для передачи и приема цифровой информации.

Устройство для передачи и приема цифровой информации содержит на передающей стороне 1: мультиплексор 2, источники 3 информации, первый счетчик 4, генератор 5 тактовых импульсов, ключ 6, второй счетчик 7, передатчик 8, первый 9 и второй 10 элементы ИЛИ, вход 11 начальной установки устройства, элемент И 12, элемент НЕ 13, регистры 14 и 15 сдвига, блок 16 элементов НЕ, дешифратор 17, делитель 18 частоты, третий 19, второй 20 элементы И, на приемной стороне 21: приемник 22, первый регистр 23 сдвига, счетчик 24, первый дешифратор 25, второй элемент И 26, блок 27 ключей, блок памяти 28,первый И 29, элемент ИЛИ 30, блок 31 элементов НЕ , второй регистр 32 сдвига, блок 33 поразрядного сравнения, делитель 34 частоты, второй дешифратор 35, линию 36 связи,

Устройство работает следующим образом.

При включении устройства напряжение питания на передающей стороне подается на вход 11, и через

o элемент ИЛИ 10 обнуляются делитель 18 частоты и счетчик 4. Состояние других элементов памяти в этот момент времени не имеет значения. Генератор 5 вырабатывает импуль5 сы прямоугольной формы с параметрами, соответствующими цифровым интегральным схемам, и частотой, необходимой и допустимой для передачи цифровой информации по проводной линии

0 связи Эти импульсы непосредственно поступают на счетный вход счетчика 7, который обнуляется импульсами, поступившими с выхода генератора 5 через ключ 6 на его установочный

5 вход нуля.

. Импульсы с выхода генератора 5 подаются также на счетный вход делителя 18 частоты, который осуществляет деление частоты импульсов, напри0 мер, с коэффициентом, равным восьми. Дешифратор 17 выделяет, например, нулевое состояние делителя 18 и формирует сигнал записи информации, поступившей от источника 3 через

мультиплексор 2 на информационные входы первого 14 и второго 15 регистров, причем на первый регистр 14 информация записывается в инверсном коде (через блок 16 элементов НЕ)„ Этот же сигнал с выхода дешифратора 17 поступает через открытый элемент И 20 на счетный вход счетчика 4, который формирует код адре- са источника 3 информации для мультиплексора 2 и который изменяет свое состояние только после поступления фронта сигнала записи на регистры 14 и 15.

После окончания записи информации в регистры 14 и 15 она продвигается по ним поразрядно под действием тактовых импульсов, поступающих с выход генератора 5. С выхода второго ре- гистра 15 информация поступает через открытый элемент И 19 и элемент ИЛИ 9 на информационный (первый) вхо передатчика 8, с выхода которого она подается в проводную линию 36 связи.

Каждый раз под действием сигнала, поступившего с выхода дешифратора 17 через от-крытый элемент И 20 на счетный вход счетчика 4, последний изменяет свое состояние. В результате код адреса, формируемый с выходов счетчика 4 на адресные входы мультиплексора 2, подключает на входы регистров 14 и 15 цифровую информацию с другого (очередного по номеру) источника 3.

После заполнения счетчика 4 (окончания перебора всех адресов) с приходом следующего импульса на его счетный вход все разряды счетчика 4, выходы которых подключены к адресным входам мультиплексора 2, обнуляются, а последний разряд- счетчика 4, подключенный к входу элемента НЕ 13, устанавливается в состояние логической единицы. Теперь ключ 6 и элементы И 19 и 20 закрываются сигналом логического нуля, формируемым с выхода элемента НЕ 13. На счетный вход счетчика 4 и установочный вход счет- чика 7 прекращаются поступления импульсов, но на счетный вход счетчика 7 они продолжают поступать.

С приходом восьмого импульса на

счетный вход счетчика 7 его четвертый разряд переключается в состояние логической единицы. В результате на выходе элемента И 12 формируется

Q 5

0 5

0

Q

5

5

5

сигнал логической единицы, который через элемент ИЛИ 10 поступает на установочный вход нуля делителя 18 (подтверждает его нулевое состояние) и на установочный вход нуля счетчика 4, который обнуляется. Сигнал логического нуля поступает с выхода счетчика 4 на первые входы элемен- TOI. ИЛИ 9, И 12 и на вход элемента НЕ 13, который формирует сигнал логической единицы на входы элементов И 19 и 20 и вход ключа 6,

Теперь счетный вход счетчика 4 снова открыт для импульсов с выхода дешифратора 17, а на установочный вход нуля счетчика 7 опять поступают импульсы с генератора 5 через ключ 6, которые устанавливают счетчик 7 в нулевое состояние.

Таким образом, каждый цикл опроса источников 3 информации, число которых может быть 2 , завершается формированием сигнала синхронизации, содержащего 2.п разрядов единиц, где п - разрядность одного регистра сдвига.

На приемной стороне 21 включение напряжения питания, а значит и формирование сигнала обнуления (начальной установки) может осуществляться в произвольный момент времени. Формируемый при этом на входе устройства сигнал начальной установки поступает через элемент ИЛИ 30 на установочные входы нуля делителя 34 частоты и счетчика 24.

С передающей стороны 1 по линии 36 связи на приемник 22 информация может поступать в произвольный момент времени. В этом случае с информационного (первого) выхода приемника 22 на последовательный вход регистра 23 начинает поступать информационная последовательность, а на входы синхронизации регистров 23 ч 32 и счетный вход делителя 34 частоты - тактовая частота. Информация продвигается последовательно, поразрядно с первого регистра 23 на второй регистр 32.

Код информации, записанный во втором регистре 32, подается на первые входы блока 33 без инверсии, а код информации, записанный в первом регистре 23, подается на вторые входы блока 33 сравнения через блок 31 элементов НЕ. В случае совпадения кодов блок 33 формирует сигнал на

первый вход элемента И 26. На второй вход последнего должен поступить сигнал с выхода дешифратора 35, который выделяет, например, код нулевого состояния делителя 34 частоты, осуществляющего деление частоты тактовых импульсов с таким же коэффициентом, что и у делителя 18 на передающей стороне 1.

Только при совпадении во времени двух сигналов, поступивших на входы элемента И 26, последний формирует сигнал записи информации через один из открытых ключей блока 27 на соответствующий вход синхронизации . блока 28 памяти.

Передний фронт этого сигнала поступает на вход синхронизации соответствующей ячейки памяти блока 28 раньше, чем задний фронт импульса, поступающего на счетный вход счетчика 24, который формирует код адреса принятой информационной посылки.

Дешифратор 25 декодирует код адреса, поступающий на его входы 1 с выходов счетчика 24 и формирует сигнал для открывания соответствующего ключа блока 27. Выход каждого из ключей блока 27 подключен к соответствующему входу синхронизации блока 28 памяти, на информационные входы которого уже поступил цифровой код информации с выходов регистра 23 через блок 31 элементов НЕ.

Несмотря на то, что информация, поступающая на приемную сторону 21, записывается в первый 23 и второй 32 регистры сдвига до прихода сигнала синхронизации запись ее в регистр памяти не происходит, так как делитель 34 с помощью дешифратора 35 формирует сигнал на один из входов элемента И 26 в момент времени, не совпадающий с моментом времени равенства кодов, поступающих на вход блока 33, и в момент формирования сигнала дешифратором 35 не будет совпадения информации, записанной в первом 23 и втором 32 регистрах сдвига. Информация в регистре 23 должна быть в противофазе или инверсна по отношению к информации, записанной в регистре 32.

После прихода сигнала синхронизации, код которого содержит, например , восемь единиц и отличается от любой информационной посылки, он вы- деляется с помощью элемента 29, и

10

818326

через элемент ИЛИ 30 на установоч- ных входах нуля счетчика 24 и делителя 34 формируется сигнал обнуления. Начиная с момента окончания сигнала синхронизации, поступающая информация записывается в ячейки блока 28 памяти, если ее прямая и инверсная части соответствуют поразрядно и совпадают на входах блока 33. В случае появления ошибки хотя бы в одном из разрядов информационной посылки, записанной в регистрах 23 и 32 сдвига, в блок 28 памяти эта информация не записывается, так как не сформирован сигнал на выходе блока 33. В случае короткого замыкания или обрыва в линии связи на вход приемника 22, а значит и в регистры 23 и 32 сдвига не поступает информационная последовательность, а значит предыдущая информация, записанная

15

20

в блоке 28 памяти, сохраняется. Формула изобретения

Устройство для передачи и приема цифровой информации, содержащее на передающей стороне источники информации, выходы которых подключены к информационным входам мультиплексора, к адресным входам которого подключены выходы группы первого счетчика, выход которого подключен к входу элемента НЕ и первым входам первых элементов И и ИЛИ, выход последнего из которых соединен с первым входом передатчика, генератор тактовых импульсов, выход которого соединен с синхронизирующим входом второго счетчика, первым входом ключа и вторым входом передатчика, выход которого подключен к входу линии связи, выход элемента НЕ соединен с вторым входом ключа, первый вход второго элемента ИЛИ является входом начальной установки устройства, выход второго элемента ИЛИ подключен к установочному входу первого счетчика, выход второго счетчика соединен с вторым входом первого элемента И, выход которогосоединен с вторым входом второго элемента ИЛИ, выход ключа подключен к установочному входу второго счетчика, на приемной стороне - приемник, вход которого соединен с выходом линии связи, первый выход приемника подключен к информационному входу первого регист

pa сдвига, выходы группы которого соединены с соответствующими входами первой группы первого элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого является входом начальной установки устройства, выход элемента ИЛИ подключен к установочному входу счетчика, выходы которого соединены с одноименными входами первого дешифратора, второй элемент И, блок памяти, выходы которого являются выходами устройства, второй выход приемника соединен с синхронизирующим входом первого регистра сдвига, отличающееся тем, что, с целью повышения функциональной надежности устройства и достоверности приема передаваемой информации, в него введены на передающей стороне первый и второй регистры сдвига, второй и третий элементы И,.дешифратор, делитель частоты и блок элементов НЕ, выходы мультиплексора соединены с одноименными информационными входами первого регистра сдвига непосредственно и через блок элементов НЕ с одноименными информационными входами второго регистра сдвига, выход генератора тактовых импульсов соединен с синхронизирующими входами первого и второго регистров сдвига и делителя частоты, установочный вход которого подключен к выходу второго элемента ИЛИ,выходы-к одноименным входам дешифратора, выход которого соединен с первым входом второго элемента И и управляющими входами первого и второго регистров сдвига, вход второго регистра сдвига соединен с шиной нулевого потенциала, выход - с входом перво-

0

5

0

5

0

го регистра сдвига, выход которого подключен к первому входу третьего элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход элемента НЕ подключен к вторым входам второго и третьего элемента И, выход второго элемента И соединен с синхронизирующим входом первого счетчика, на приемной стороне введены второй регистр сдвига, блок поразрядного сравнения, делитель частоты, блок элементов НЕ, второй дешифратор и блок ключей, выходы которого подключены к одноименным синхронизируюпцгм входам блока памяти, второй выход приемника соединен с синхронизирующими входами второго регистра сдвига и делителя частоты, выходы которого подключены к одноименным входам второго дешифратора, выход которого соединен с синхронизирующим входом счетчика и первым входом второго элемента И, выход которого подключен к входу блока ключей, входы группы которого соединены с одноименными выходами первого дешифратора, выходы второго регистра сдвига подключены к одноименным входам второй группы первого элемента И и одноименным входам первой группы блока поразрядного сравнения, выход которого соединен с вторым входом второго элемента И, выходы группы первого регистра сдвига подключены к одноименным входам блока элементов НЕ, выходы которого соединены с одноименными входами второй группы блока поразрядного сравнения и информационными входами блока памяти, выход элемента ИЛИ соединен с установочным входом делителя частоты.

| Устройство для передачи и приема дискретных сигналов | 1978 |

|

SU785886A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для передачи и приема цифровой информации | 1986 |

|

SU1322344A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-23—Подача