СП

4 1

О

sj

00

315

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Цель изобретения - повышение достоверности устройства за счет обнаружения и исправления многократных ошибок.

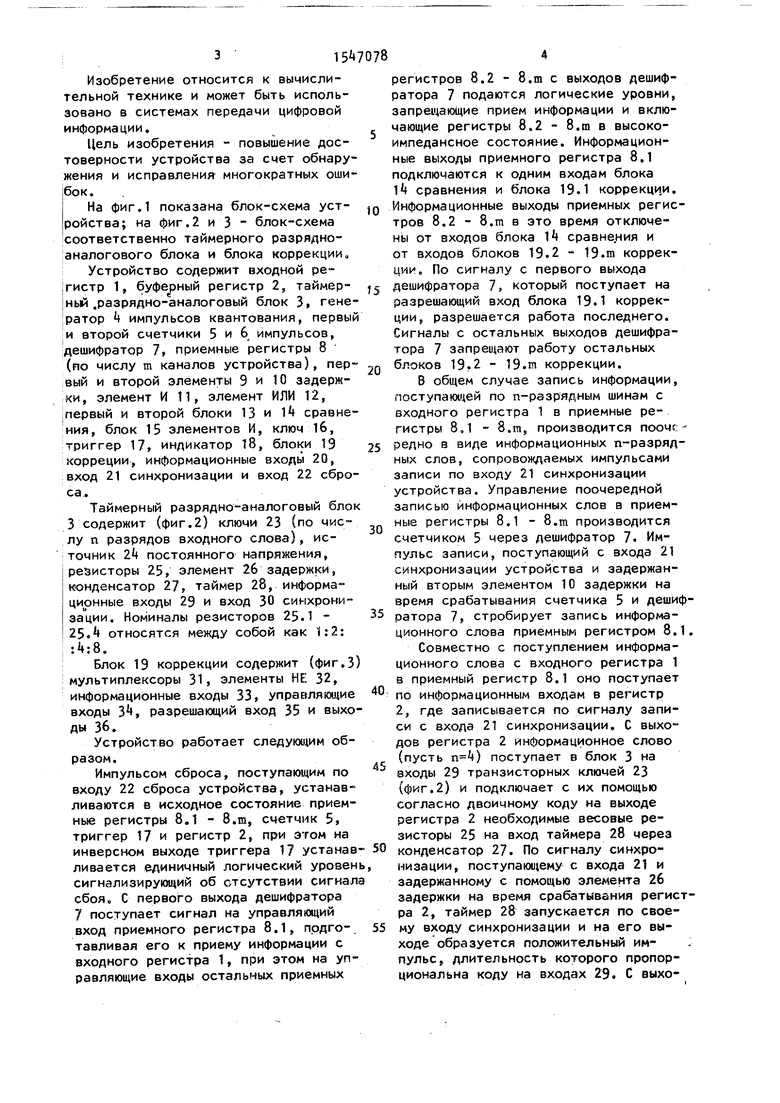

На фиг.1 показана блок-схема устройства; на фиг.2 и 3 - блок-схема соответственно таймерного разрядно- аналогового блока и блока коррекции.

Устройство содержит входной регистр 1, буферный регистр 2, таймер- ный .разрядно-аналоговый блок 3, генератор 1 импульсов квантования, первый и второй счетчики 5 и 6 импульсов, дешифратор 7, приемные регистры 8 (по числу m каналов устройства), первый и второй элементы 9 и 10 задержки , элемент ИИ, элемент ИЛИ 12, первый и второй блоки 13 и 1Ц сравнения, блок 15 элементов И, ключ 16, триггер 17, индикатор 18, блоки 19 корреции, информационные входы 20, вход 21 синхронизации и вход 22 сброса.

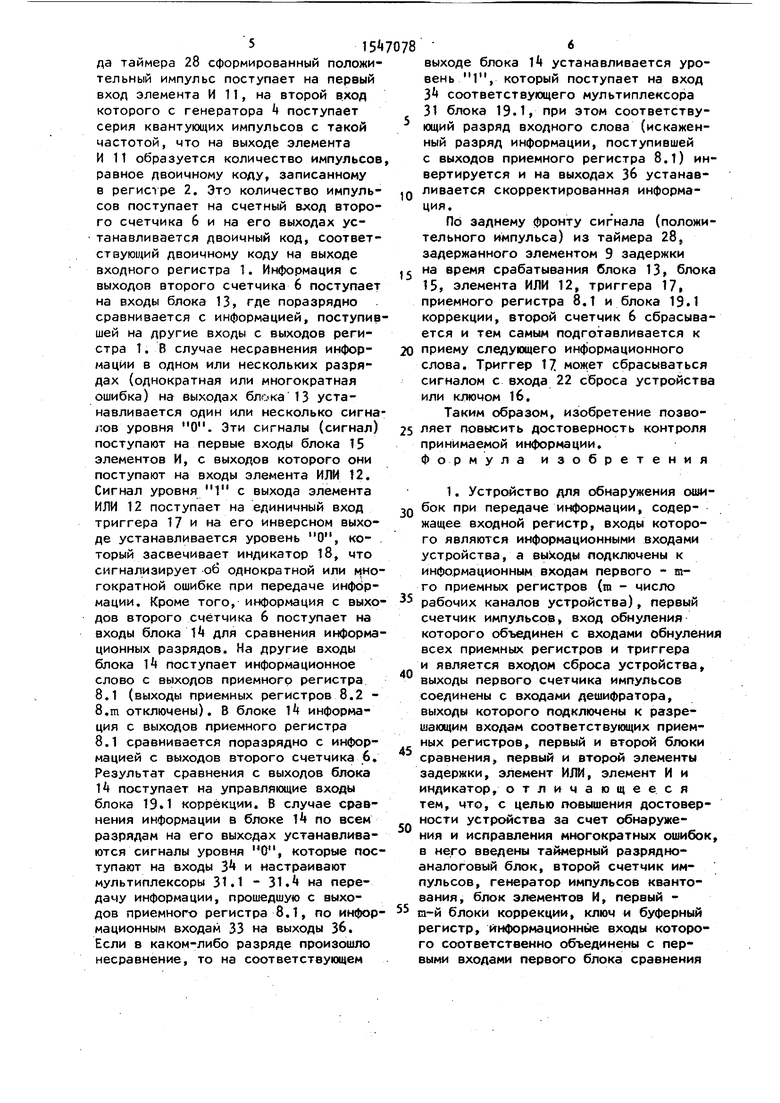

Таймерный разрядно-аналоговый блок 3 содержит (фиг.2) ключи 23 (по числу п разрядов входного слова), источник 2 постоянного напряжения, резисторы 25, элемент 26 задержки, конденсатор 27, таймер 28, информационные входы 29 и вход 30 синхронизации. Номиналы резисторов 25.1 - 25. относятся между собой как 1:2: й:8.

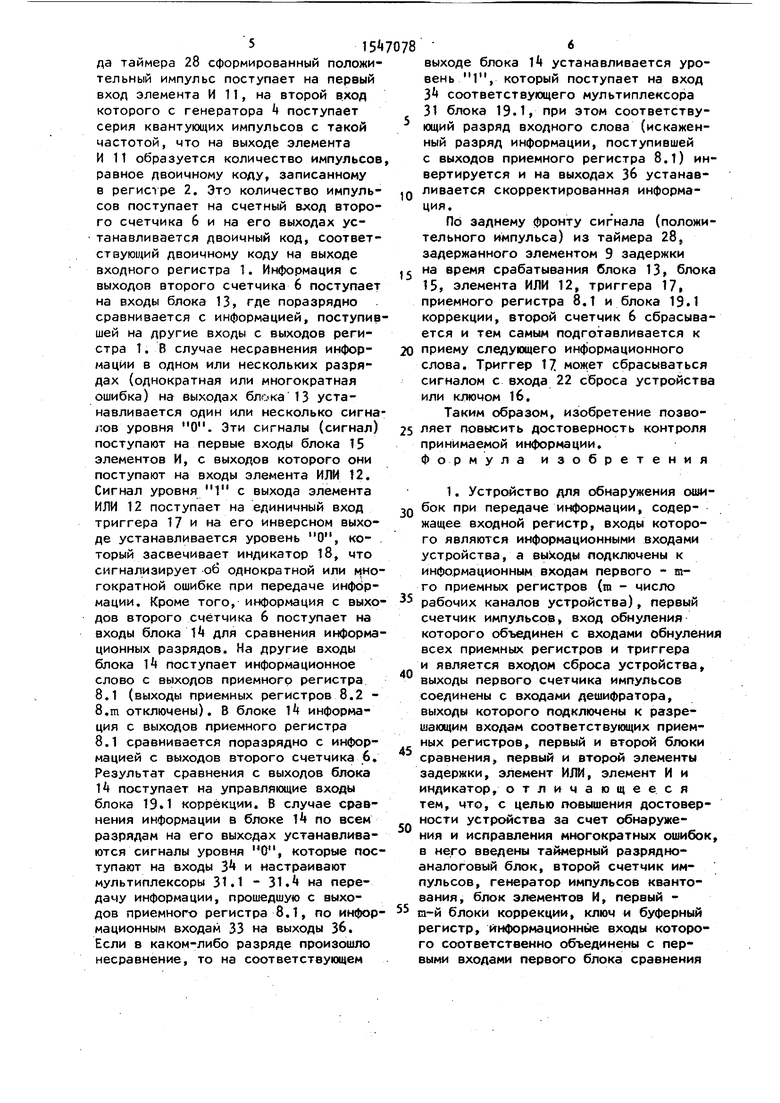

Блок 19 коррекции содержит (фиг.З) мультиплексоры 31, элементы НЕ 32, информационные входы 33, упраЕШяющие входы 3, разрешающий вход 35 и выходы 36.

Устройство работает следующим образом.

Импульсом сброса, поступающим по входу 22 сброса устройства, устанавливаются в исходное состояние приемные регистры 8.1 - В,т, счетчик 5 триггер 17 и регистр 2, при этом на инверсном выходе триггера 1 устанавливается единичный логический уровень сигнализирующий об отсутствии сигнала сбоя. С первого выхода дешифратора 7 поступает сигнал на управляющий вход приемного регистра 8.1, подготавливая его к приему информации с входного регистра 1, при этом на управляющие входы остальных приемных

0

0

5

c

0

5

0

5

0

5

регистров 8.2 - 8.т с выходов дешифратора 7 подаются логические уровни, запрещающие прием информации и включающие регистры 8.2 - 8,ш в высоко- импедансное состояние. Информационные выходы приемного регистра 8.1 подключаются к одним входам блока 1 сравнения и блока 19.1 коррекции. Информационные выходы приемных регистров 8.2 - 8.т в это время отключены от входов блока 1 сравнения и от входов блоков 19.2 - 19.т коррекции. По сигналу с первого выхода дешифратора 7 который поступает на разрешающий вход блока 19.1 коррекции, разрешается работа последнего. Сигналы с остальных выходов дешифратора 7 запрещают работу остальных блоков 19.2 - 19.т коррекции.

В общем случае запись информации, поступающей по n-разрядным шинам с входного регистра 1 в приемные регистры 8.1 - 8.га, производится пооч - редно в виде информационных п-разряд- ных слов, сопровождаемых импульсами записи по входу 21 синхронизации устройства. Управление поочередной записью информационных слов в приемные регистры 8.1 - 8.т производится счетчиком 5 через дешифратор 7. Импульс записи, поступающий с входа 21 синхронизации устройства и задержанный вторым элементом 10 задержки на время срабатывания счетчика 5 и дешифратора 7, стробирует запись информационного слова приемным регистром 8.1.

Совместно с поступлением информационного слова с входного регистра 1 в приемный регистр 8.1 оно поступает по информационным входам в регистр 2, где записывается по сигналу записи с входа 21 синхронизации. С выходов регистра 2 информационное слово (пусть ) поступает в блок 3 на входы 29 транзисторных ключей 23 (фиг.2) и подключает с их помощью согласно двоичному коду на выходе регистра 2 необходимые весовые резисторы 25 на вход таймера 28 через конденсатор 27. По сигналу синхронизации, поступающему с входа 21 и задержанному с помощью элемента 26 задержки на время срабатывания регистра 2, таймер 28 запускается по своему входу синхронизации и на его выходе образуется положительный импульс, длительность которого пропорциональна коду на входах 29. С выхо5 15 да таймера 28 сформированный положительный импульс поступает на первый вход элемента И 11, на второй вход которого с генератора k поступает серия квантующих импульсов с такой частотой, что на выходе элемента И 11 образуется количество импульсов равное двоичному коду, записанному в регистре 2. Это количество импуль- сов поступает на счетный вход второго счетчика 6 и на его выходах устанавливается двоичный код, соответствующий двоичному коду на выходе входного регистра 1. Информация с выходов второго счетчика 6 поступает на входы блока 13, где поразрядно сравнивается с информацией, поступившей на другие входы с выходов регистра 1. В случае несравнения инфор- мации в одном или нескольких разрядах (однократная или многократная ошибка) на выходах блока 13 устанавливается один или несколько сигналов уровня О. Эти сигналы (сигнал) поступают на первые входы блока 15 элементов И, с выходов которого они поступают на входы элемента ИЛИ 12. Сигнал уровня 1 с выхода элемента ИЛИ 12 поступает на единичный вход триггера 17 и на его инверсном выходе устанавливается уровень О, который засвечивает индикатор 18, что сигнализирует об однократной или многократной ошибке при передаче информации. Кроме того, информация с выхо- дов второго счетчика 6 поступает на входы блока 1 для сравнения информационных разрядов. На другие входы блока 14 поступает информационное слово с выходов приемного регистра 8.1 (выходы приемных регистров 8.2 - 8.т отключены). В блоке 1 информация с выходов приемного регистра 8.1 сравнивается поразрядно с информацией с выходов второго счетчика 6. Результат сравнения с выходов блока 1А поступает на управляющие входы блока 19.1 коррекции. В случае сравнения информации в блоке 1 по всем разрядам на его выходах устанавливаются сигналы уровня М0, которые поступают на входы 3 и настраивают мультиплексоры 31.1 - 31. на передачу информации, прошедшую с выходов приемного регистра 8.1, по инфор- мационным входам 33 на выходы 36. Если в каком-либо разряде произошло несравнение, то на соответствующем

0 0 5 п 5

0

выходе блока 14 устанавливается уровень 1, который поступает на вход 3 соответствующего мультиплексора 31 блока 19.1, при этом соответствующий разряд входного слова (искаженный разряд информации, поступившей с выходов приемного регистра 8.1) инвертируется и на выходах 36 устанавливается скорректированная информация.

По заднему фронту сигнала (положительного импульса) из таймера 28, задержанного элементом 9 задержки на время срабатывания блока 13, блока 15, элемента ИЛИ 12, триггера 17, приемного регистра 8.1 и блока 19.1 коррекции, второй счетчик 6 сбрасывается и тем самым подготавливается к приему следующего информационного слова. Триггер 17 может сбрасываться сигналом с входа 22 сброса устройства или ключом 16.

Таким образом, изобретение позволяет повысить достоверность контроля принимаемой информации. Формула изобретения

1. Устройство для обнаружения ошибок при передаче информации, содержащее входной регистр, входы которого являются информационными входами устройства, а выходы подключены к информационным входам первого - т- го приемных регистров (га - число рабочих каналов устройства), первый счетчик импульсов, вход обнуления которого объединен с входами обнуления всех приемных регистров и триггера и является входом сброса устройства, выходы первого счетчика импульсов соединены с входами дешифратора, выходы которого подключены к разрешающим входам соответствующих приемных регистров, первый и второй блоки сравнения, первый и второй элементы задержки, элемент ИЛИ, элемент И и индикатор, отличающееся тем, что, с целью повышения достоверности устройства за счет обнаружения и исправления многократных ошибок, в него введены таймерный разрядно- аналоговый блок, второй счетчик импульсов, генератор импульсов квантования, блок элементов И, первый - ia-й блоки коррекции, ключ и буферный регистр, информационные входы которого соответственно объединены с первыми входами первого блока сравнения

и подключены к выходам входного регистра, вход обнуления буферного регистра объединен с первым выводом ключа и подключен к входу сброса устройства, второй вывод ключа соединен с общей шиной, выходы буферног регистра соединены с информационными входами таймерного разрядно-аналого- вого блока, вход синхронизации которого объединен с входом второго элемента задержки, тактовым входом буферного регистра и счетным входом Первого счетчика импульсов и являетс Еходом синхронизации устройства, выход таймерного разрядно-аналогового блока непосредственно и через первый элемент задержки соединен соответственно с первым входом элемента И и входом обнуления второго счетчика импульсов, выход генератора импульсов лзантования подключен к второму вхо- ДУ элемента И, выход которого соеди- со счетным входом второго счетчика импульсов, выходы которого под- «лючены к вторым входам первого и первым входам второго блоков сравнения, выходы первого блока сравнения соединены с первыми входами блока флементоа И, выходы которого подключены к входам элемента ИЛИ, выход ко-ч-го сединен с установочным входом триггера, инверсный выход кото- пого подключен к входу индикатора, выход которого подключен к входу индикатора выход второго элемента задержки соединен с тактовыми входами первого - тп-го приемных регистров, выходы которых подключены к информационным входам одноименных блоков коррекции и соответственно объединены и подключены к вторым входам второго блока сравнения, выходы которого соединены с вторыми входами блока элементов И и управляющими входами первого - m-го блоков коррекции, разрешающие входы которых подключены соответственно к первому - го-му выходам дешифратора, выходы первого - m-го блоков коррекции являются соответствующими выходами устройства.

2. Устройство по п,1, о т л и - чающееся тем, что таймерный

разрядно-аналоговый блок содержит первый - n-й ключи (п-разрядность входного слова), таймер, элемент задержки и последовательно соединенные источник постоянного напряжения,,

5 первый - n-й резисторы и конденсатор, соединенный другим выводом с информационным входом таймера, тактовый вход которого через элемент задержки подключен к входу синхронизации

0 блока, управляющие входы ключей являются соответствующими информационными входами блока, информационный вход и выход каждого ключа соединена с первым и вторым выводаки одноимен5 ного резистора, выход таймера является выходом блока.

3. Устройство по пИ, отличающееся тем, что блок коррекQ ции содержит первый - rv-й мультиплексоры и первый - элементы НЕ9 аходы которых объединены с первыми информационными входами одноименных мультиплексоров и являются соответствующими информационными входами

блока, выход каждого элемента НЕ

соединен с вторым информационным входом одноименного мультиплексора, входы разрешения всех мультиплексоров объединены и являются входом разрешения блока, управляющие входы первого - п-го мультиплексоров являются соответствующими управляющими входами блока, выходы мультиплексоров являются соответствующими выхо0

5

дами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство ввода информации | 1986 |

|

SU1417015A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1656572A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Таймер | 1985 |

|

SU1357939A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи цифровой информации позволяет повысить достоверность устройства за счет обнаружения и исправления многократных ошибок. Устройство содержит входной регистр 1, счетчик 5 импульсов, дешифратор 7, приемные регистры 8.1-8.M элементы 9, 10 задержки, элемент И 11, элемент ИЛИ 12, блоки 13,14 сравнения, триггер 17 и индикатор 18. Благодаря введению буферного регистра 2, таймерного разрядно-аналогового блока 3, генератора 4 импульсов квантования, счетчика 6 импульсов, блока 15 элементов И, ключа 16 и блоков коррекции 19.1-19.M в устройстве производится пословное сравнение принимаемой информации с кодом, полученным после таймерного разрядно-аналогового преобразования принятого слова в импульс соответствующей длительности, в течение которого действия подсчитываются импульсы квантования, после чего осуществляется коррекция ошибок. 2 з.п. ф-лы, 3 ил.

ЧЗМ

XJ

3

цЕЗ-

XJ

ЗМ

I

J Н

П

ТАЛ

| Техника средств связи | |||

| Научи.- тех | |||

| сб | |||

| Сер | |||

| Системы связи | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Шахтная печь для обжига жира и их глин | 1927 |

|

SU10515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-28—Публикация

1988-03-30—Подача