(21)4177864/24-24

(22)06.01.87

(46) 23.05.89. Бюл. Р 19(71)Таганрогский радиотехнический институт им. В.Д. Калмыкова

(72)В.В. Жила, А.К. Шилов, Н.А. Пуд- зенков и Г.Н. Лукашкова

(53) 681.327.6(088.8) (56) Шигин А.Г., Дерюгин А.А. Цифровые вычислительные машины. - М.: Энергия, 1976, с. 495.

Авторское свидетельство СССР № 932567, кл. G 11 С 11/00, 1972.

(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

(57) Изобретение относится к вычислительной технике. Цель - растирание функциональных возможностей за счет адаптации устройства к параметрам абонента. В устройство введены счетчики и входные и выходные коммутаторы, которые объединяют необходимое количество секций устройства в один или несколько каналов требуемого быстродействия в зависимости от информации, поступающей на вход задания режима работы блока управления. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для управления обменом | 1983 |

|

SU1151976A1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| Устройство для ввода информации | 1988 |

|

SU1580340A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет адаптации быстродействия устройства к параметрам абонента. В устройство введены счетчики и входные и выходные коммутаторы которые объединяют необходимое количество секций устройства в один или несколько каналов требуемого быстродействия в зависимости от информации, поступающей на вход задания режима работы блока управления. 1 ил.

1

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных информационно-измерительных системах, многопроцессорных вычислительных комплексах.

Цель изобретения - расширение функциональных возможностей устройства за счет адаптации быстродействия устройства к параметрам абонента.

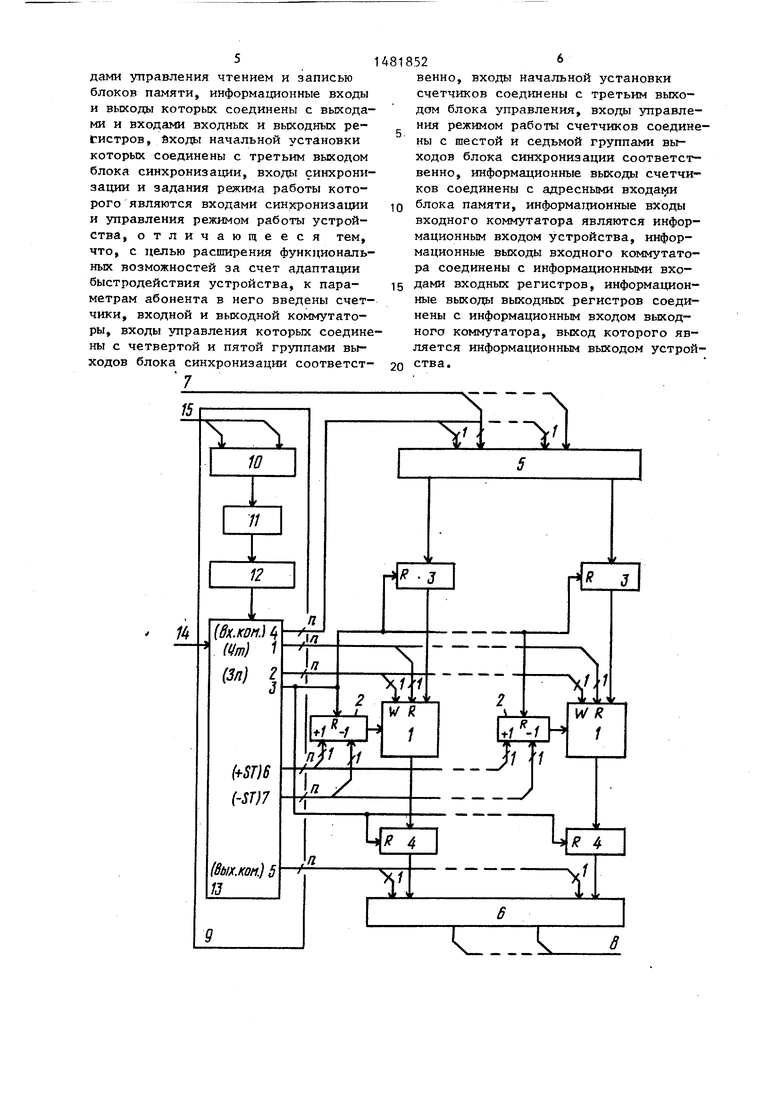

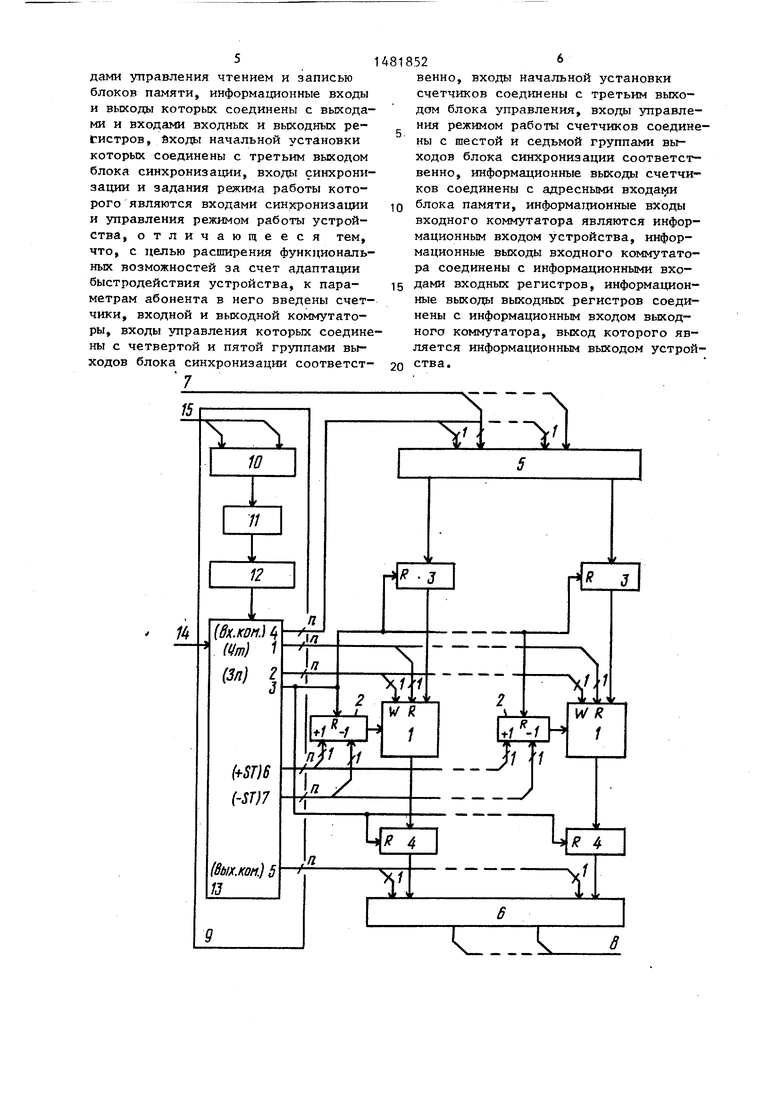

На чертеже представлена структурная схема буферного запоминающего устройства.

Устройство содержит блоки 1 памяти, счетчики 2, регистры 3 и 4, коммутаторы 5 и 6, информационные входы 7 и выходы 8, блок 9 синхронизации, состоящий из последовательно соединенных регистра 10 управления, дешифратора 11, блока 12 постоянной памяти и распределителя 13 импульсов, вход 14 синхронизации блока 9, вход 15 задания режима работы блока 9,

входы 7 соединены с информационными входами коммутатора 5, выходы которого соединены с входами регистров 3, выходы которых соединены с информационными входами блоков 1 памяти, выходы которых соединены с входами регистров 4, выходы которых соединены с информационным входом коммутатора 6, выход которого соединен с выходом 8 устройства, выходы счетчиков 2 соединены с адресными входами блоков 1, первая и вторая группы выходов блока 9 соединены с входами управления чтением и записью блоков 1, третий выход блока 9 - с входами

начальной установки счетчиков 2,-регистров 3 и 4, четвертая и пятая группы выходов блока 9 - с входами управления коммутаторов, шестая и седьмая группы выходов блока 9 - с входами управления режимом работы счетчиков 2.

U)

Устройство работает следующим образом.

Цикл работы БЗУ.состоит из двух этапов: этапа ввода и этапа вывода массивов информационных слов. На первом этапе в блоки 1 вводится информация от всех участвующих в данном цикле обмена абонентов. На втором - эта информация выводится заинтересо- ванным в ней абонентам. Вся информация или некоторая ее часть может не выводиться в данном цикле, т.е. БЗУ используют для хранения массивов информации. Таким образом, предлага- емое устройство работает в трех режимах: обмена, хранения и смешанном. Частным случаем любого из этих режи-t мов является обмен только одним информационным словом, что возможно в известном устройстве. Каждый из режимов предлагаемого БЗУ имеет подрежимы: Первый пришел - первый вышел и Первый «пришел - последний вышел.

С началом этапа ввода на выходе блока 9 вырабатывается сигнал сброса в О, который, поступая на первы входы регистров 3 и 4 и счетчиков 2, очищает их. Одновременно по входу 15 на входы регистра 10 поступают коды абонентов. В кодах содержится информация об абоненте, передающем инфор-i мацию в данном цикле, и об абоненте, принимающем ее. Это необходимо для согласования канала по максимальному быстродействию и требуемой емкости. В режиме хранения код не содержит информацию об абоненте, являющемся приемником, поэтому на этапе вывода введенный массив из БЗУ не выводится. В дешифраторе 11 вырабатываются сигналы, управляющие работой блока 1 постоянной памяти, хранящего программу перестройки распределителя 13 на данный цикл работы. При этом программой . учитывается, что часть секций может быть занята хранением информации, полученной в предыдущих циклах обмена. Выбранная из блока 12 посто- янной памяти программа поступает в распределитель. Затем начинается собственно ввод информации в БЗУ, который синхронизируется сигналами, поступающими на первую группу входов .блока g по входу 14 синхронизации.

По окончании этапа ввода начинается этап вывода. На этом этапе различие в работе устройства в зависимости от подрежимов Первый пришел - первый вышел или Первый пришел - последний вышел заключаемая только в способе формирования адресов ячеек, из которых происходит считывание информации.

В подрежиме Первый пришел - первый вышел этап вывода начинается с появления на выходе блока 9 сигнала сброса в нуль, который, поступая на первые входы адресных счетчиков, формирует адреса нулевых ячеек. С них начинается вывод. Адрес следующей ячейки каждого блока 1 получается при сложении содержимого адресных счетчиков с единичными сигналами, поступающими с пятой группы выходов блока 9 на вторые входы адресных счетчиков 2. В подрежиме Первый пришел - последний вышел адрес ячейки, с которой начинается вывод, сформирован в адресных счетчиках уже на этапе ввода. Следующие адреса получаются вычитанием из содержимого адресных счетчиков по единице путем подачи на их третьи входы единичных сигналов с шестой группы выходов блока 9.

В буферном запоминающем устройстве осуществляется оперативное изменение быстродействия за счет секционирования памяти. Накопитель и связанные с ним регистры и адресные счетчики представляют собой секцию. Несколько секций образуют канал, предоставляемый абоненту. Использование в предлагаемом устройстве коммутаторов, которые в соответствии с программой, заложенной в блоке постоянной памяти, объединяют в каналы необходимое количество секций, позволяет производить адаптацию быстродействия и емкости канала под характеристики соответствующего абонента. Общее количество секций в устройстве определяется числом и быстродействием одновременно обменивающихся абонентов и также быстродействием накопителей.

Формула изобретения

Буферное запоминающее устройство, содержащее входные и выходные регистры, блоки памяти, блок синхронизации, первая и вторая группы выходов которого соединены соответственно с вхо-

51

дами управления чтением и записью блоков памяти, информационные входы и выходы которых соединены с выходами и входами входных и выходных регистров, входы начальной установки которых соединены с третьим выходом блока синхронизации, входы синхронизации и задания режима работы которого являются входами синхронизации и управления режимом работы устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет адаптации быстродействия устройства, к параметрам абонента в него введены счетчики, входной и выходной коммутаторы, входы управления которых соединены с четвертой и пятой группами выходов блока синхронизации соответст 7

818526

венно, входы начальной установки счетчиков соединены с третьим выходом блока управления, входы управления режимом работы счетчиков соединены с шестой и седьмой группами выходов блока синхронизации соответственно, информационные выходы счетчиков соединены с адресными входами

Ю блока памяти, информационные входы входного коммутатора являются информационным входом устройства, информационные выходы входного коммутатора соединены с информационными вхо15 дами входных регистров, информационные выходы выходных регистров соединены с информационным входом выходного коммутатора, выход которого является информационным выходом устрой2о ства.

Авторы

Даты

1989-05-23—Публикация

1987-01-06—Подача