СП

оо

о оо

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1439671A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

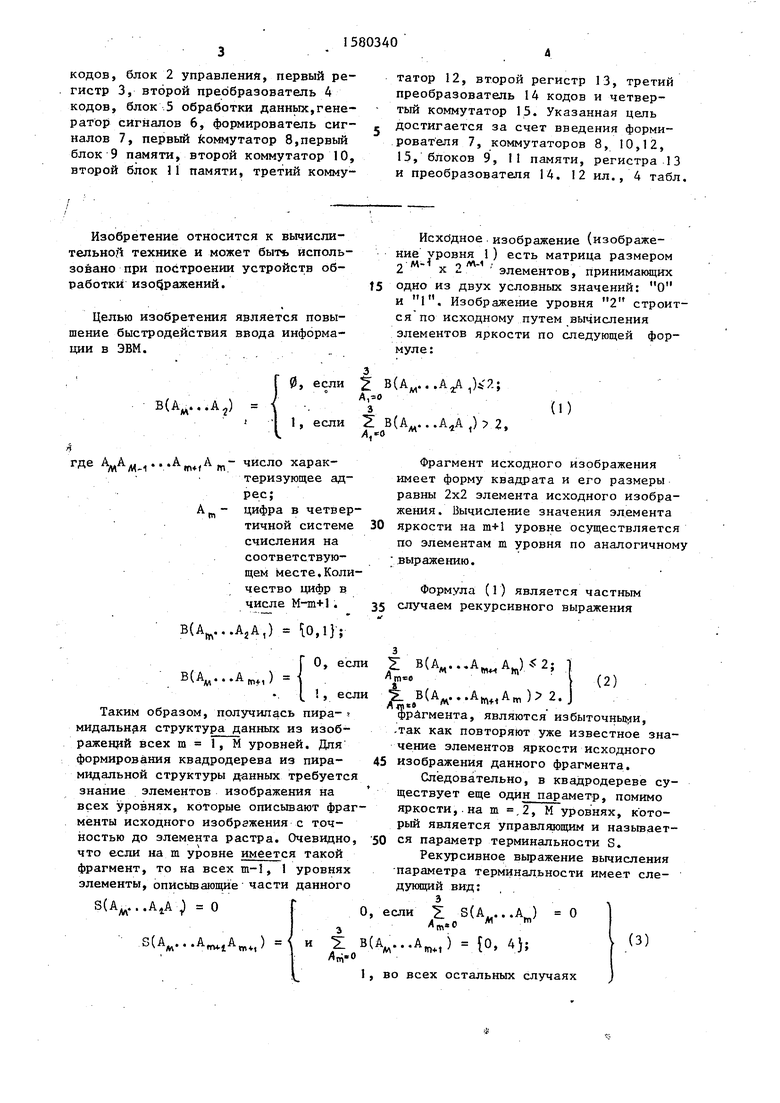

Изобретение относится к вычислительной технике и может быть использовано при построении устройств обработки изображений. Цель изобретения является повышение быстродействия ввода информации. Устройство содержит первый преобразователь кодов, блок управления, первый регистр, второй преобразователь кодов, блок обработких данных и генератор сигналов. В устройство введены формирователь сигналов с первого по четвертый коммутаторы, первый и второй блоки памяти, второй регистр и третий преобразователь кодов. 2 ил.

Упр Улр Фиг

кодов, блок 2 управления, первый регистр 3, второй преобразователь 4 кодов, блок 5 обработки данных,генератор сигналов 6, формирователь сигналов 7, первый коммутатор 8,первый блок 9 памяти, второй коммутатор 10, второй блок 11 памяти, третий коммуИзобретение относится к вычислительной технике и может быть использовано при построении устройств обработки изображений.

Целью изобретения является повышение быстродействия ввода информации в ЭВМ.

0, если

В(АМ...А)

1 , если

де ...,- число харакадАттеризующеерее;

цифра в четвертичной системе счисления на соответствующем месте,Количество цифр в числе М-т+1 .

В(Ат...А,А,) {0,1};

B(V -Am i

О, если Т В(Ам..,Ат„АтЬ 2;

1 , если

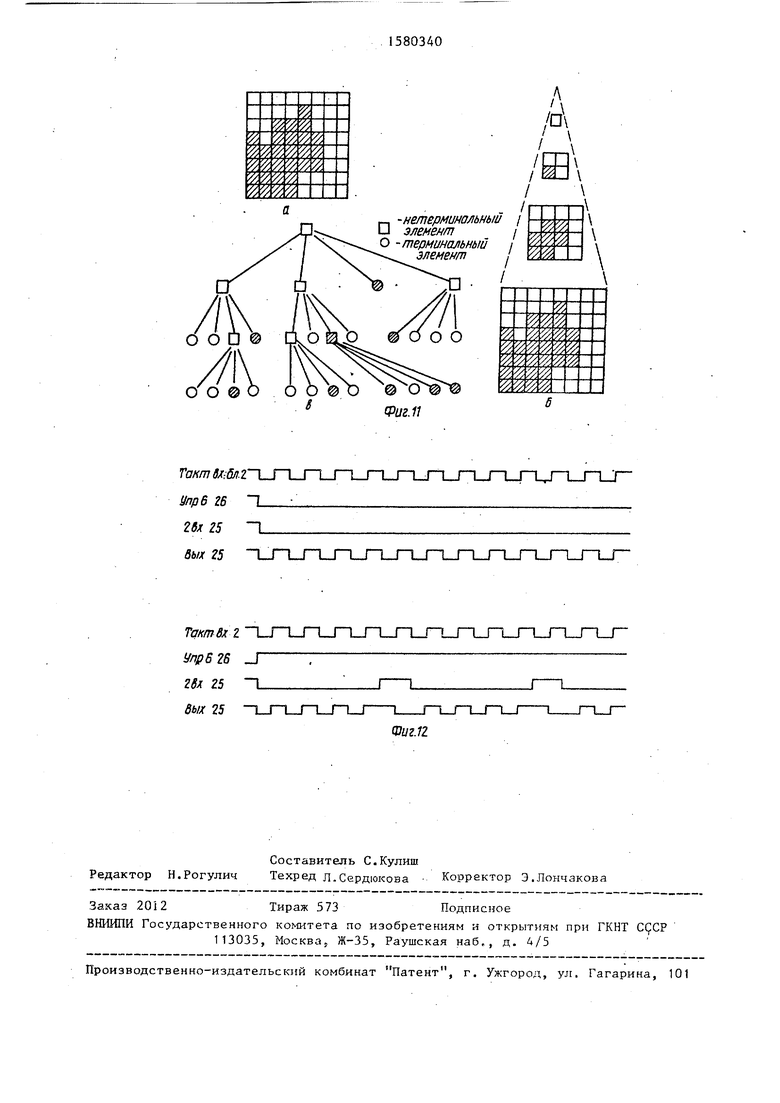

Таким образом, получилась пира- мидальная структура данных из изображений всех m 1, М уровней. Для формирования квадродерева из пирамидальной структуры данных требуется знание элементов изображения на всех уровнях, которые описывают фрагменты исходного изображения с точностью до элемента растра. Очевидно, что если на m уровне имеется такой фрагмент, то на всех т-1, 1 уровнях элементы, описывающие части данного

S(AM...AtA ) О

B(AM...Am+,Ani)2.

фрагмента, являются и так как повторяют уже чение элементов яркос 45 изображения данного ф

Следовательно, в к ществует еще один пар яркости, на m 2, М рый является управляю 50 ся параметр терминаль

Рекурсивное выраже параметра терминально дующий вид: з

О, если Ј SU.....AJ

А п m

Xm.o

5(AM- AmnAm,

(AM...Am+1) JO, 4);

татор 12, второй регистр 13, третий преобразователь 14 кодов и четвертый коммутатор 15. Указанная цель достигается за счет введения формирователя 7, коммутаторов 8, 10,12, 15, блоков 9, 11 памяти, регистра 13 и преобразователя 14. 12 ил., 4 табл.

ние уровня 1)

м-1 о м-1

2 х L элементов

Исходное изображение (изображе- есть матрица размером , принимающих 5 одно из двух условных значений: О и 1м. Изображение уровня 2 строится по исходному путем вычисления элементов яркости по следующей формуле:

2 В(АМ...А2А1); А,о 3

2е(В(Ам.. .А4А ,) 2,

Фрагмент исходного изображения имеет форму квадрата и его размеры равны 2x2 элемента исходного изображения . Вычисление значения элемента яркости на m-Н уровне осуществляется по элементам ш уровня по аналогичному выражению.

Формула (1) является частным случаем рекурсивного выражения

Т В(Ам..,Ат„АтЬ 2;

(2)

B(AM...Am+,Ani)2.

фрагмента, являются избыточными, так как повторяют уже известное значение элементов яркости исходного 45 изображения данного фрагмента.

Следовательно, в квадродереве существует еще один параметр, помимо яркости, на m 2, М уровнях, который является управляющим и называет- 50 ся параметр терминальности S.

Рекурсивное выражение вычисления параметра терминальности имеет следующий вид: з

, если Ј SU.....AJ О

А п m

Xm.o

(AM...Am+1) JO, 4);

(3)

1, во всех остальных случаях

Элемент исходного изображения является всегда терминальным S(A... ...,) 0 по определению.

В связи с тем, что каждый элемент т+1 уровня вычисляется на основании четырех элементов m уровня, образующих квадрат, целесообразно развертку элементов данных в процессе кодирования и передачи осуществлять согласно с процессом вычисления. Развертка элементов га уровня есть рекурсивная Z-развертка т-уровня.

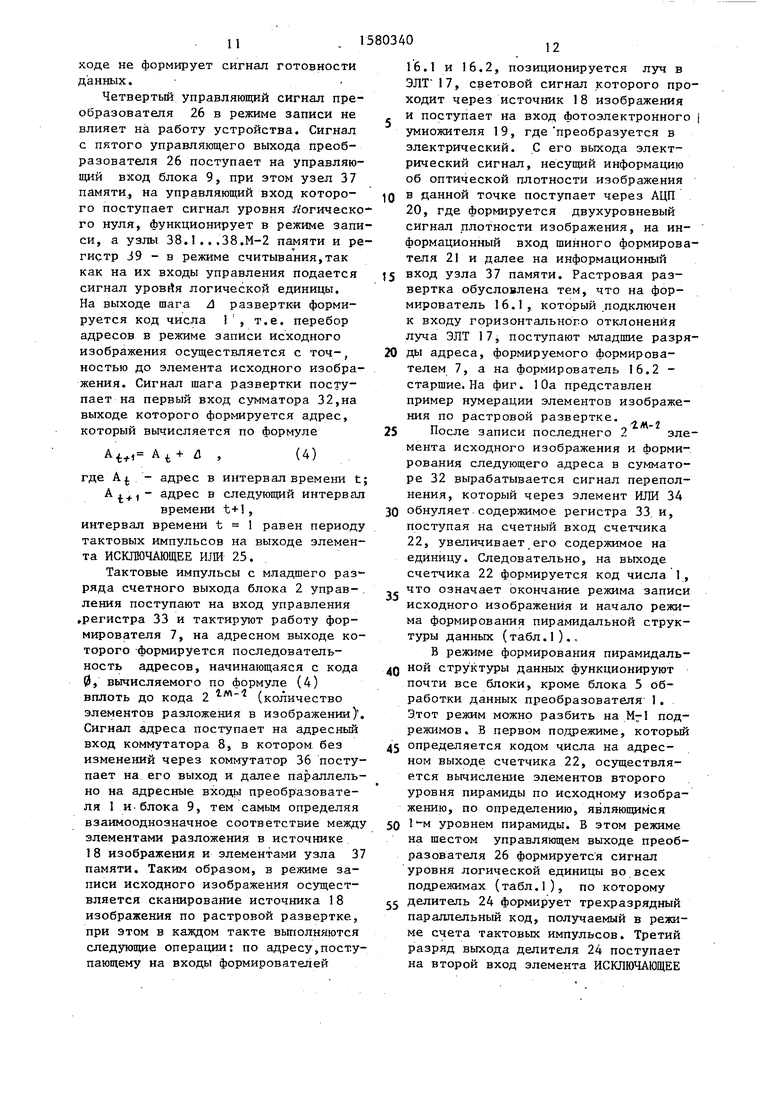

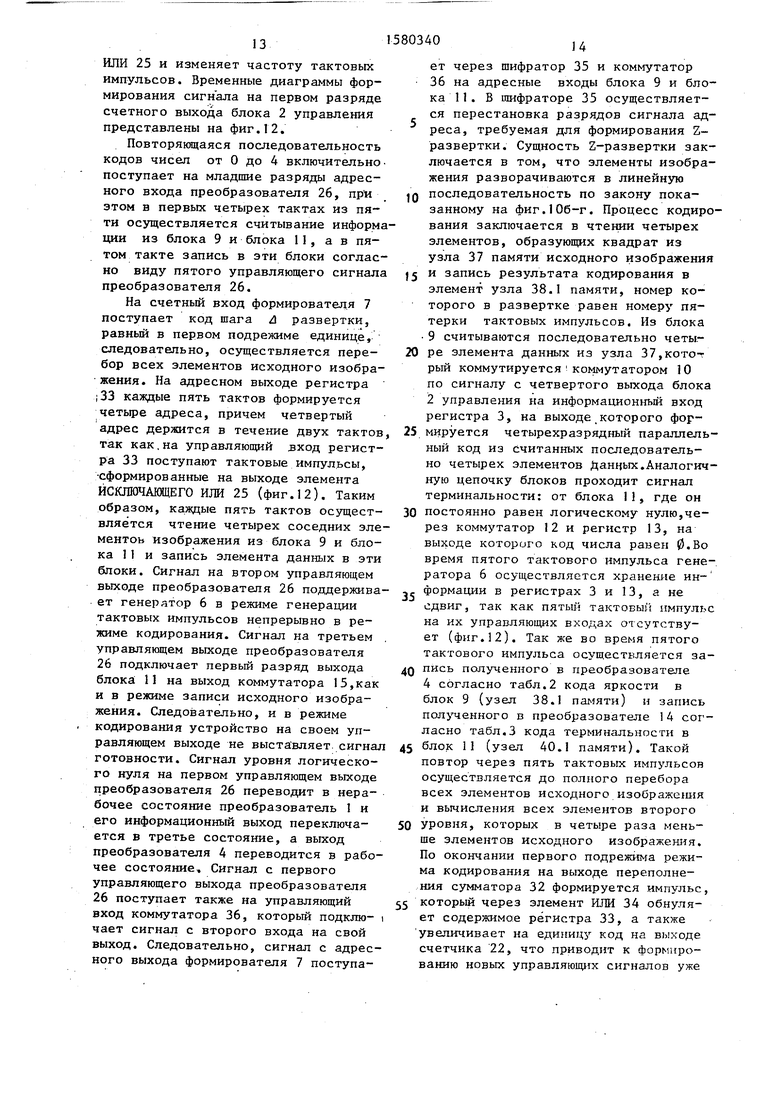

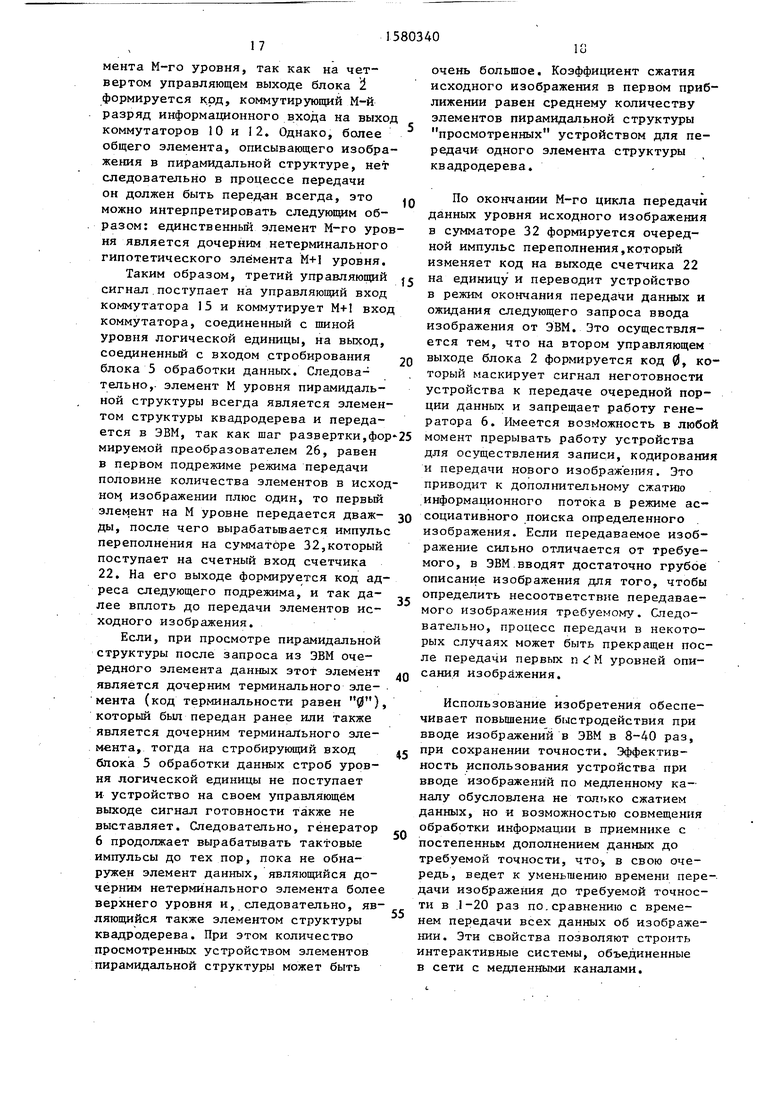

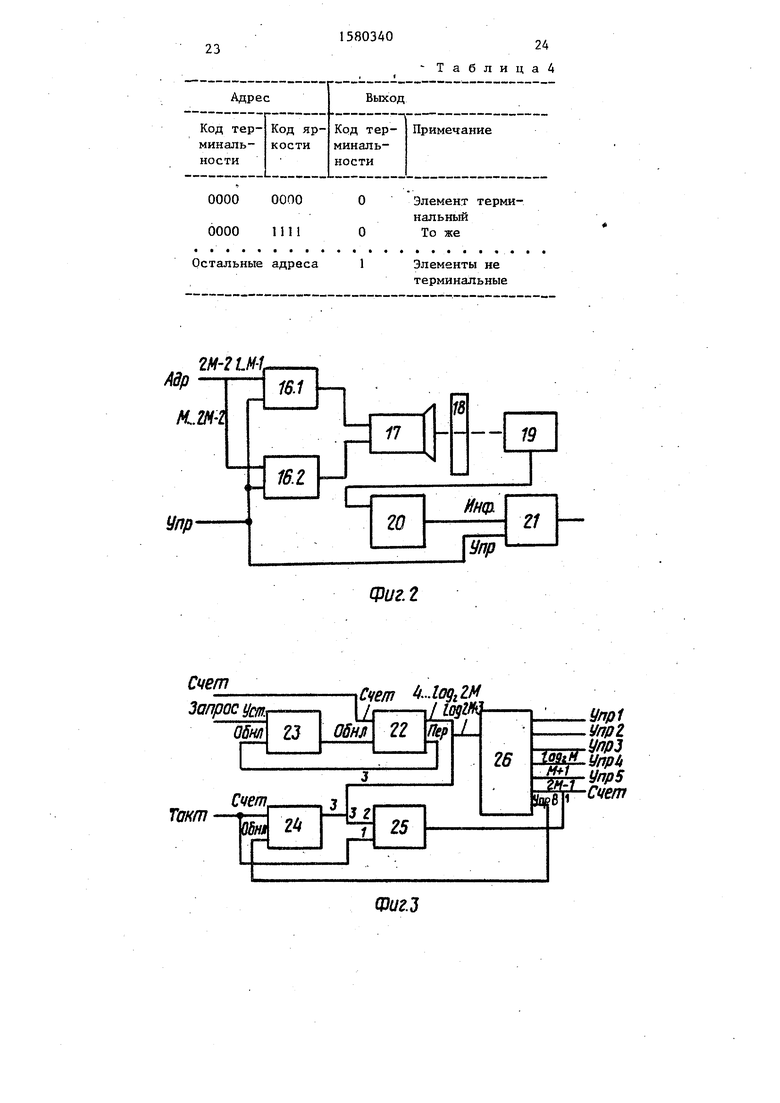

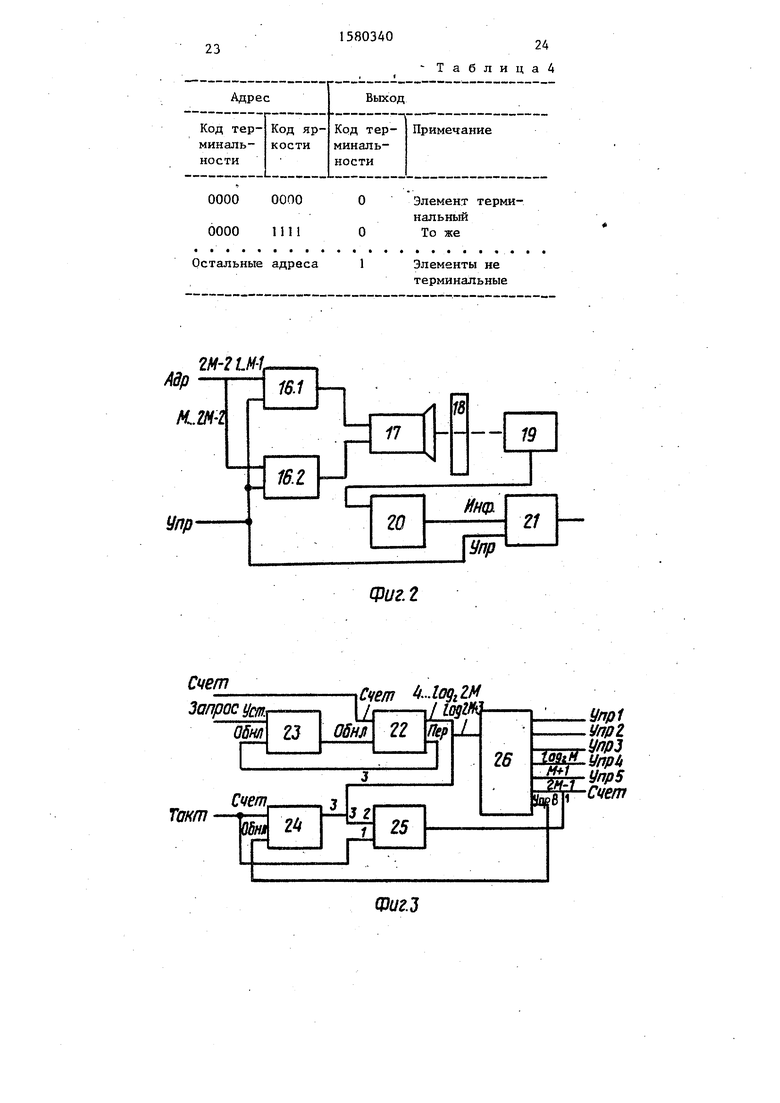

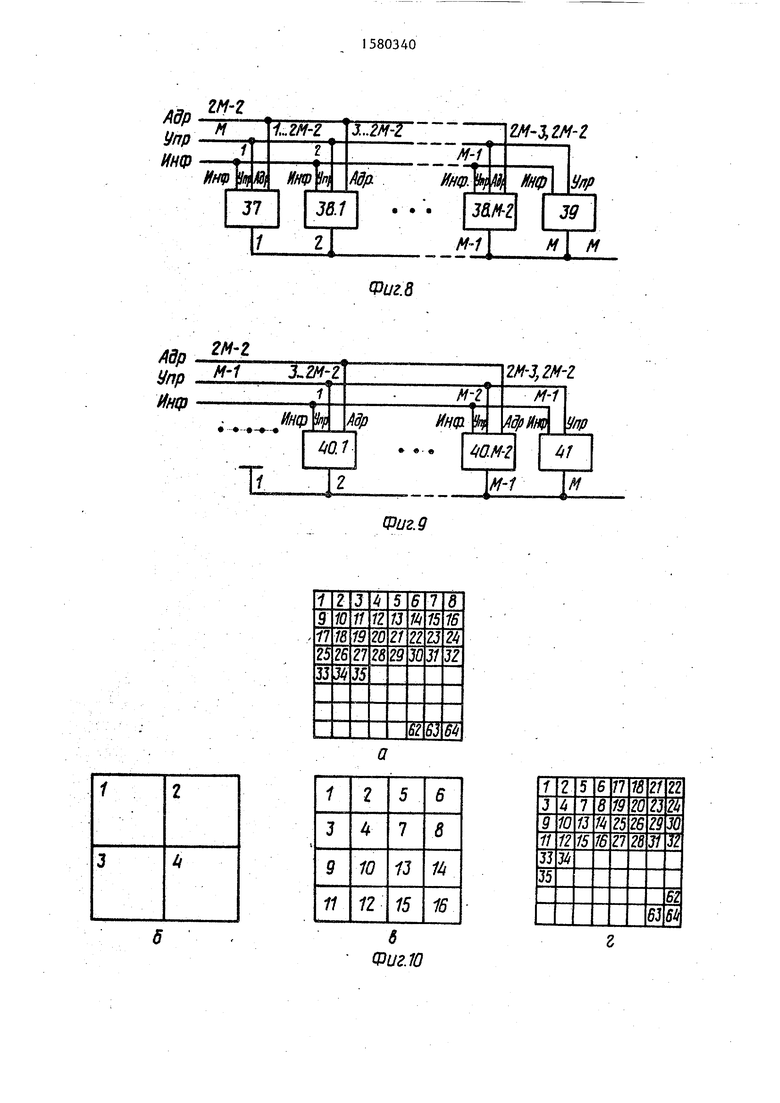

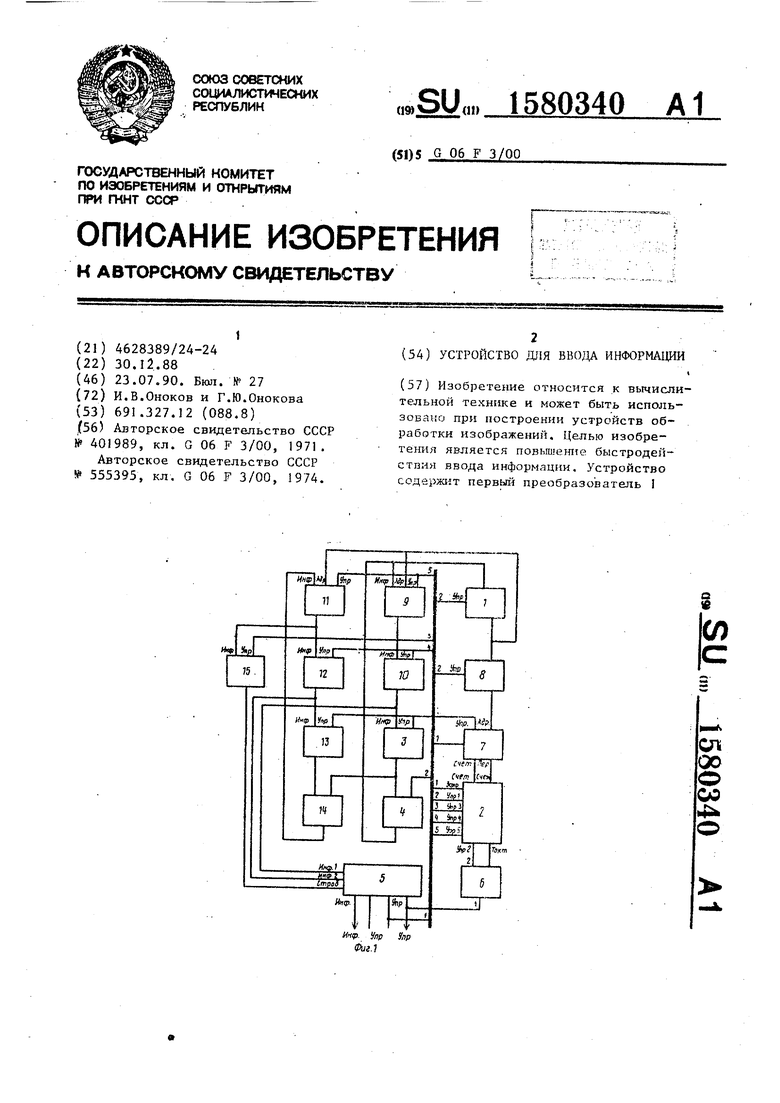

На фиг.1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема первого преобразователя; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема блока обработки данных; на фиг. 5 - функциональная схема генератора; на фиг. 6 - функциональная схема формирователя; на фиг. 7 - функциональная схема первого коммутатора; на фиг.8 функциональная схема первого блока памяти; на фиг.9 - функциональная схема второго блока памяти; на фиг.10 - нумерация элементов изображения (а - растровая развертка; б - Z-развертка 1-го уровня; в - Z-развертка 2-го уровня; г - Z-развертка уровня); на фиг. 11 - графическое изображение: а - растровое; б - пирамидальное; в - квадродерево; на фиг. 12 - временные диаграммы формирования тактового сигнала в устройстве.

Устройство (фиг.1) содержит первый преобразователь 1 кодов, блок 2 управления, первый регистр 3, второй преобразователь 4 кодов, блок 5 обработки данных, генератор 6 сигналов, формирователь 7 сигналов, первый коммутатор 8, первый блок 9 памяти,второй коммутатор 10, второй блок 11 па- мяти, третий коммутатор 12, второй регистр 13, третий преобразователь 14 кодов и четвертый коммутатор 15.

Преобразователь 1 (фиг.2) содержит первый и второй формирователи 16.1 и 16.2, электронно-лучевую трубку (ЭЛТ) 17, источник 18 изображения (например, слайд), фотоэлектронный умножитель 19, аналого-цифровой преобразователь (АЦП) 20 и шинный формирователь 21. В качестве формирователей 16.1 и 16.2 можно использовать микросхему ЦАП 1108ПА1. В качестве фотоэлектронного умножителя можно

использовать фотоэлектронный умножитель ФЭУ-118, в качестве АЦП 20 - микросхему П07ПВ1, а в качестве формирователя 21 - микросхему 589АП16. Блок 2 управления (фиг.З) представляет собой блок формирования управляющих и счетных сигналов, определяющих режимы работы остальных блоков устройства, и содержит счетчик 22, триггер 23, делитель 24, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 25 и преобразователь 26. В качестве счетчика 22 можно использовать счетчик К555ИЕ10. В качестве триггера 23 можно использовать триггер К555ТМ2. В качестве делителя 24 можно использовать счетчик К555ИЕЮ. В качестве элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 можно использовать мик0 росхему К555ЛП5. В качестве преобразователя 26 можно использовать ПЗУ, адресный вход которой имеет разрядность больше или равную logг (2М+3), а разрядность слова данных должна

5 быть равна

Yl + Y2 + УЗ + Y4 + Y5 + Y6 + & 1 + 2 + (logjM + I) + logjM +

30

+ (M + 1) + 1 + (2М-2) - ЗМ + 2 log2M + 4.

Например, можно использовать мик- росхемы 556РТ5.

В табл.1 представлены значения каждого из сигналов, формируемых преобразователем 26 во время цикла записи исходного изображения,циклов кодирования и циклов передачи данных в ЭВМ, а также во время ожидания очередного запроса ввода изображения от ЭВМ.

Физический смысл сигналов, представленных в табл.1: Y1 - работа устройства по растровой (- 1) или рекурсивной развертке ( 0); Y2 - сигнал управления работой генератоРа 6. (если Y2 11 - генератор выработает тактовые импульсы, если Y2 01, то работа генератора зависит от других сигналов, если Y2 00, то работа генератора запрещена); Y3 - код номера уровня плюс единица, по которому четвертый коммутатор 15 коммутирует соответствующий разряд сигнала, считываемого из блока 11 в режиме передачи и служит

для определения избыточных элементов, данных, за счет чего производится усечение пирамидальной структуры данных до квадродерева; Y4 - код номера уровня, по которому коммутатор 10 и коммутатор 12 коммутируют соответствующий разряд сигнала, считываемого из блока 9 и блока 11 для формирования данных в режимах кодирова- ния и передачи; Y5 - позиционный код номера уровня, каждый разряд которого является управляющим сипналом в блоке 9 и в блоке 11; и - старшие разряды сигнала счет, вырабатывав- мого блоком 2 управления. Этот сигнал является шагом Л развертки элементов данных во время записи, кодирования и передачи данных; Y6 - сигнал управления частотой тактовых импульсов (если Y5 О, сигнал в младшем разряде сигнала счета тождественен сигналу на тактовом входе, в противном случае частота на выходе равна 4/5 входной. На фиг. 12 представлены временные диаграммы формирования младшего разряда сигнала счет.

Регистры 3 и 13 представляют собой четырехразрядные сдвиговые реги- стры. В качестве регистров можно использовать микросхемы К555ИР16.

Преобразователь 4 осуществляет преобразование в режиме кодирования по выражению (2). В режиме записи и передачи по сигналу управления с первого управляющего выхода блока 2 управления данный преобразователь переводится в третье состояние и не влияет на информационный вход блока 9. В качестве преобразователя можно использовать ПЗУ 556РТ11. В табл.2 ( приведена таблица истинности ПЗУ, используемой в качестве - преобразователя 4«

Блок 5 обработки данных (фиг.4) является интерфейсным для связи с ЭВМ и содержит регистр 27, формирователь 28, элемент ИЛИ 29. В качестве регистра 27 можно использовать микросхему К531ИР16, а в качестве формирователя 28 - микросхему К531ТМ2, в качестве элемента ИЛИ 29 - микросхему К555ЛЛ1.

Генератор 6 (фиг.5) является стро бируемым. Генератор состоит из элемента 2-2ИАИЛИ 30 и генератора 31. В качестве элемента 2-2И-ИЛИ 30 мож

но использовать микросхему К555ЛР1, а генератор 31 может быть выполнен на микросхеме К555ГГ1.

Формирователь 7(фиг.б) содержит сумматор 32, регистр 33 и элемент ИЛИ 34. В качестве сумматора 32 можно использовать микросхему К555ИМ6, в качестве регистра 33 - микросхему К5 55ИР16, в качестве элемента ИЛИ 34 микросхему К555ЛЛ1.

Коммутатор 8 (фиг.7) содержит шифратор 35 и коммутатор 36. В качестве коммутатора 36 можно использовать микросхемы К555КП11, а в качестве шифратора 35 - колодку с 2М-2 входами и выходами, которые соединяются между собой с помощью навесного монтажа. Между разрядами входа и разрядами выхода существует взаимооднозначное соответствие, представленное в табл.3 и на фиг.76.

0 5

0

0 5

5Q 55

5

Следовательно,первые 1, М-1 разряды входа шифратора соединены с соответствующими нечетными выходами шифратора, а последние М, 2М-2 разряды входа шифратора соединены с соответствующими четными выходами шифратора.

Блок 9 памяти (фиг.8) содержит узел 37 памяти, М-2 узлов 38.1... ...38.М-2 памяти и регистр 39. В качестве узла 37 памяти и узлов 38.1... ...38.М-2 памяти можно использовать микросхемы 132РУ5, а в качестве регистра 39 - микросхему К555ИР16.

Блок 11 памяти (фиг.9) содержит М-2 узлов 40.1...40.М-2 памяти и регистр 41. В качестве узлов 40.1... ...40.М-2 памяти можно использовать микросхемы 132РУ5, а в качестве регистра 41 - микросхему К555ИР16.

Коммутатор 10 и 12 выполняют стандартную функцию коммутации одного из М входов на выход в соответствии с кодом на управляющем входе. В качестве коммутаторов 10 и 12 можно использовать микросхемы К555КП1.

Преобразователь 14 осуществляет преобразование в режиме кодирования по выражению (3). В качестве преобразователя 14 можно использовать микросхему ПЗУ 556РТ11. Старшие четыре разряда адресного входа микросхемы являются первым информационным входом преобразователя 14, а младшие четыре разряда - вторым информационным входом.

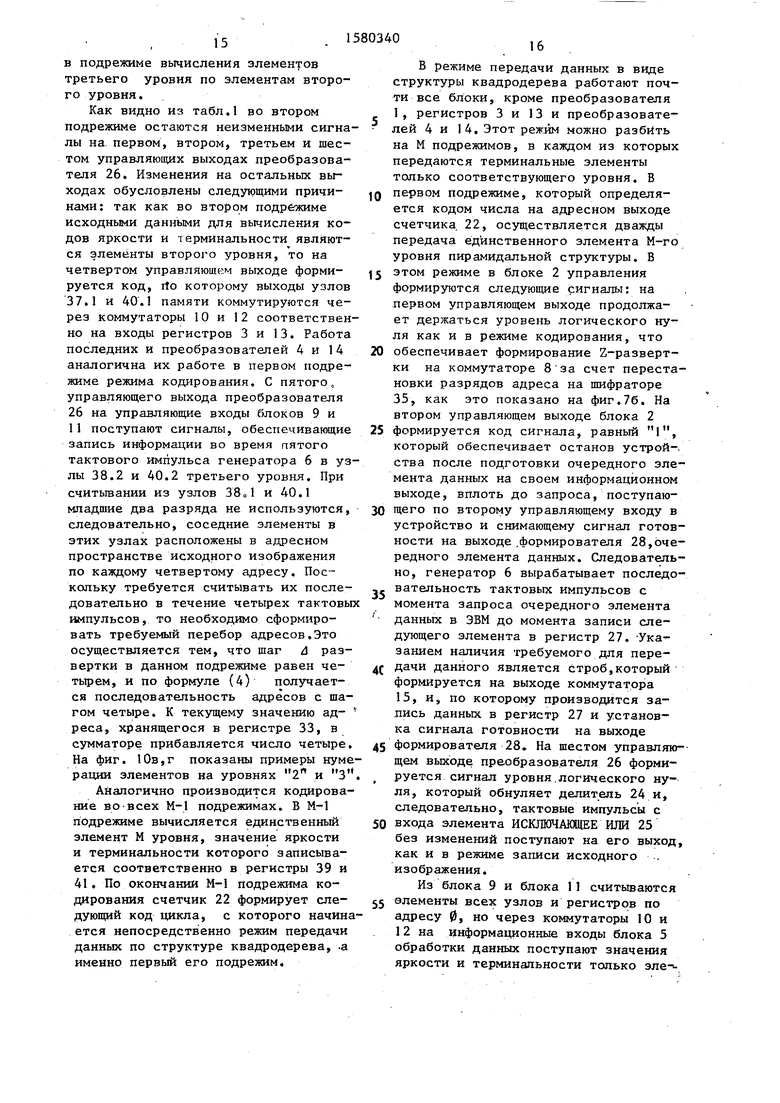

В табл.4 приведена таблица истинности ПЗУ, используемого в качестве преобразователя 14.

Коммутатор 15 выполняет стандартную функцию коммутации одного из М+1 входов на выход в соответствии с кодом на управляющем входе..Младшие m 1, М входов коммутатора соединен соответственно с m I, М разрядами информационного входа коммутатора 15, а на М+1 вход коммутатора подается постоянно уровень логической единицы.

Устройство работает в трех основных режимах: запись исходного изображения; формирование пирамидальной структуры данных (кодирование); передача данных в виде структуры квадродерева.

При поступлении сигнала запроса передачи изображения в ЭВМ уровня логической единицы на первый управляющий вход устройства, оно переходит в режим записи исходного изображения. В этом режиме функционируют следующие блоки: преобразователь 1, блок 2 управления, блок 5 обработки данных, генератор 6, формирователь 7, коммутатор 8, блок 9,коммутатор 15. Все остальные блоки не влияют на ра боту устройства в режиме записи исходного .изображения.

Сигнал запроса с первого управляющего входа устройства поступает на первый вход запроса блока 5 обработки данных, на вход запроса блока 2 управления и на управляющий вход формирователя 7. При этом сигнал запроса через элемент ИЛИ 29 поступает на вход сброса формирователя 28,на выходе которого формируется сигнал уровня логической единицы, который держится вплоть до подготовки первого элемента данных для передачи в ЭВМ. С выхода формирователя 28 сигнал поступает на управляющий вход, указывая на отсутствие данных на информационном выходе устройства, и на первый вход, генератора 6, где через элемент 2-2И--ИЛИ 30 поступает на вход стробирования генератора 31 и переводит его из режима ожидания в режим генерации тактовых импульсов, которые поступают на тактовый вход блока 2 управления. Сигнал запроса поступает на вход установки триггера 23, на выходе которого фор0

0

5

мируется сигнал, который, поступая на вход обнуления счетчика 22,переводит его в режим счета. На информационном выходе счетчика 22 держится код числа 0 до поступления импульса на счетном входе счетчика 22. Сигнал запроса поступает также через элемент ИЛИ 34 на вход обнуления регистра 33, с выхода которого код числа 0 поступает на второй вход сумматора 32 и на адресный вход коммутатора 8.

Таким образом, на выходах преоб5 разователя 26 формируются сигналы

согласно табл. 1 в режиме записи.Уровень логического нуля на тестом управляющем выходе преобразователя 26 держит делитель 24 в режиме обнуления, т.е. на его выходе формируется код числа 0. Следовательно, тактовые импульсы поступают через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 25 на первый разряд счетного выхода блока. 2 управления без изменения, так как на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 в режиме записи исходного изображения постоянно держится сигнал уровня логического нуля (фиг.12). Сигнал уровня логической единицы на первом управляющем выходе преобразователя 26 переводит выход преобразователя 4 в третье состояние, формирователи 6. и 16.2 и шинный формирователь 21 преобразователя 1 переводит в рабочее состояние, а коммутатор 36 коммутатора 8 коммутирует на выход сигналы с первого своего вхгда, следовательно шифратор 35 в режиме записи исходного изображения не влияет на работу устройства., На втором управляющем выходе формируется сигнал уровня логической едишщы в обоих разрядах, который проходит через

5 вторую половину элемента 2-2И-ИЛИ 30 на вход стробирования генератора 31 и поддерживает его в режиме непрерывной генерации тактовых импульсов. На третьем управляющем выходе преоб0 разователя 26 формируется код числа 0. Следовательно, на выход второго коммутатора 15 коммутируется первый разряд выхода блока 11, который постоянно равен логическому нулю. Таким

5 образом, в режиме записи исходного

изображения на стробирующкй вход бло- ка 5 обработки данных сигнал уровня логической единицы не поступает и устройство на своем управляющем вы0

5

0

ходе не формирует сигнал готовности данных.

Четвертый управляющий сигнал преобразователя 26 в режиме записи не влияет на работу устройства. Сигнал с пятого управляющего выхода преобразователя 26 поступает на управляющий вход блока 9, при этом узел 37 памяти, на управляющий вход которого поступает сигнал уровня Логического нуля, функционирует в режиме записи, а узлы 38.1...38.М-2 памяти и регистр J9 - в режиме считывания,так как на их входы управления подается сигнал уровня логической единицы. На выходе шага Л развертки формируется код числа 1 , т.е. перебор адресов в режиме записи исходного изображения осуществляется с точ-, ностью до элемента исходного изображения. Сигнал шага развертки посту- пает на первый вход сумматора 32,на выходе которого формируется адрес, который вычисляется по формуле

At+i At + и , (4)

где А{. - адрес в интервал времени t;

А, + 1- адрес в следующий интервал

времени t+1,

интервал времени t 1 равен периоду тактовых импульсов на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25.

Тактовые импульсы с младшего разряда счетного выхода блока 2 управления поступают на вход управления .регистра 33 и тактируют работу формирователя 7, на адресном выходе которого формируется последовательность адресов, начинающаяся с кода 0, вычисляемого по формуле (4) вплоть до кода 2 -w (количество элементов разложения в изображении). Сигнал адреса поступает на адресный вход коммутатора 8, в котором без изменений через коммутатор 36 поступает на его выход и далее параллельно на адресные входы преобразователя 1 и-блока 9, тем самым определяя взаимооднозначное соответствие между элементами разложения в источнике 18 изображения и элементами узла 37 памяти. Таким образом, в режиме записи исходного изображения осуществляется сканирование источника 18 изображения по растровой развертке, при этом в каждом такте выполняются следующие операции: по адресу,поступающему на входы формирователей

В режиме формирования пирамидаль- 4Q ной структуры данных функционируют почти все блоки, кроме блока 5 обработки данных преобразователя 1. Этот режим можно разбить на М-1 подрежимов. В первом подрежиме, который 45 определяется кодом числа на адресном выходе счетчика 22, осуществляется вычисление элементов второго уровня пирамиды по исходному изображению, по определению, являющимся 50 уровнем пирамиды. В этом режиме на шестом управляющем выходе преобразователя 26 формируется сигнал уровня логической единицы во всех подрежимах (табл.1), по которому 55 делитель 24 формирует трехразрядный параллельный код, получаемый в режиме счета тактовых импульсов. Третий разряд выхода делителя 24 поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ

5

ИЛИ 25 и изменяет частоту тактовых импульсов. Временные диаграммы формирования сигнала на первом разряде счетного выхода блока 2 управления представлены на фиг.12.

Повторяющаяся последовательность кодов чисел от 0 до 4 включительно поступает на младшие разряды адресного входа преобразователя 26, при этом в первых четырех тактах из пяти осуществляется считывание информации из блока 9 и блока 11, а в пятом такте запись в эти блоки согласно виду пятого управляющего сигнала преобразователя 26.

На счетный вход формирователя 7 поступает код шага и развертки, равный в первом подрежиме единице, следовательно, осуществляется перебор всех элементов исходного изображения. На адресном выходе регистра ;33 каждые пять тактов формируется четыре адреса, причем четвертый адрес держится в течение двух тактов так как,на управляющий вход регистра 33 поступают тактовые импульсы, сформированные на выходе элемента ИСКЛЮЧАЮЩЕГО ИЛИ 25 (фиг.12). Таким образом, каждые пять тактов осуществляется чтение четырех соседних эле ментоь изображения из блока 9 и блока 1 1 и запись элемента данных в эти блоки. Сигнал на втором управляющем

выходе преобразователя 26 поддержива- ,, формации в регистрах 3 и 13, а не

ет генератор 6 в режиме генерации тактовых импульсов непрерывно в режиме кодирования. Сигнал на третьем управляющем выходе преобразователя 26 подключает первый разряд выхода блока 11 на выход коммутатора 15,как и в режиме записи исходного изображения. Следовательно, и в режиме кодирования устройство на своем управляющем выходе не выставляет сигнал готовности. Сигнал уровня логического нуля на первом управляющем выходе преобразователя 26 переводит в нерабочее состояние преобразователь 1 и его информационный выход переключается в третье состояние, а выход преобразователя 4 переводится в рабочее состояние. Сигнал с первого управляющего выхода преобразователя 26 поступает также на управляющий вход коммутатора 36, который подклю- i чает сигнал с второго входа на свой выход. Следовательно, сигнал с адресного выхода формирователя 7 поступасдвиг, так как пятый тактовый импу на их управляющих входах отсутству ет (фиг.12). Так же во время пятог тактового импульса осуществляется

4Q пись полученного в преобразователе 4 согласно табл.2 кода яркости в блок 9 (узел 38.1 памяти) н запи полученного в преобразователе 14 с ласно табл.3 кода терминальности в

45 блок 11 (узел 40.1 памяти). Такой повтор через пять тактовых импульс осуществляется до полного перебора всех элементов исходного изображен и вычисления всех элементов второг

50 Уровня, которых в четыре раза мен ше элементов исходного изображени По окончании первого подрежима реж ма кодирования на выходе переполне ния сумматора 32 формируется импул

55 который через элемент ИЛИ 34 обнул ет содержимое регистра 33, а также увеличивает на единицу код на выхо счетчика 22, что приводит к формир ванию новых управляющих сигналов у

ет через шифратор 35 и коммутатор 36 на адресные входы блока 9 и блока 11. В шифраторе 35 осуществляется перестановка разрядов сигнала ад- реса, требуемая для формирования Z- развертки. Сущность Z-развертки заключается в том, что элементы изображения разворачиваются в линейную

последовательность по закону показанному на фиг.10б-г. Процесс кодирования заключается в чтении четырех элементов, образующих квадрат из узла 37 памяти исходного изображения

и запись результата кодирования в элемент узла 38.1 памяти, номер которого в развертке равен номеру пятерки тактовых импульсов. Из блока 9 считываются последовательно четы0 ре элемента данных из узла 37,кото- рый коммутируется коммутатором 10 по сигналу с четвертого выхода блока 2 управления на информационный вход регистра 3, на выходе которого фор5 мируется четырехразрядный параллельный код из считанных последовательно четырех элементов Данных.Аналогичную цепочку блоков проходит сигнал терминальности: от блока 11, где он

0 постоянно равен логическому нулю,через коммутатор 12 и регистр 13, на выходе которого код числа равен 0.Во время пятого тактового импульса генератора 6 осуществляется хранение инсдвиг, так как пятый тактовый импульс на их управляющих входах отсутствует (фиг.12). Так же во время пятого тактового импульса осуществляется запись полученного в преобразователе 4 согласно табл.2 кода яркости в блок 9 (узел 38.1 памяти) н запись полученного в преобразователе 14 согласно табл.3 кода терминальности в

блок 11 (узел 40.1 памяти). Такой повтор через пять тактовых импульсов осуществляется до полного перебора всех элементов исходного изображения и вычисления всех элементов второго

Уровня, которых в четыре раза меньше элементов исходного изображения. По окончании первого подрежима режима кодирования на выходе переполнения сумматора 32 формируется импульс,

который через элемент ИЛИ 34 обнуляет содержимое регистра 33, а также увеличивает на единицу код на выходе счетчика 22, что приводит к формиро- ванию новых управляющих сигналов уже

в подрежиме вычисления элементов третьего уровня по элементам второго уровня.

Как видно из табл.1 во втором подрежиме остаются неизменными сигналы на первом, втором, третьем и шестом управляющих выходах преобразователя 26. Изменения на остальных выходах обусловлены следующими причинами: так как во втором подрежиме исходными данными для вычисления кодов яркости и терминальности являются элементы второго уровня, то на четвертом управляющем выходе формируется код, rto которому выходы узлов 37.1 и 40.1 памяти коммутируются через коммутаторы 10 и 12 соответственно на входы регистров 3 и 13. Работа последних и преобразователей 4 и 14 аналогична их работе в первом подрежиме режима кодирования. С пятого, управляющего выхода преобразователя 26 на управляющие входы блоков 9 и 11 поступают сигналы, обеспечивающие запись информации во время пятого тактового импульса генератора 6 в узлы 38.2 и 40.2 третьего уровня. При считывании из узлов 38„1 и 40.1 младшие два разряда не используются, следовательно, соседние элементы в этих узлах расположены в адресном пространстве исходного изображения по каждому четвертому адресу. Поскольку требуется считывать их последовательно в течение четырех тактовы импульсов, то необходимо сформировать требуемый перебор адресов,Это осуществляется тем, что шаг Л развертки в данном подрежиме равен четырем, и по формуле (4) получается последовательность адресов с шагом четыре. К текущему значению ад- реса, хранящегося в регистре 33, в сумматоре прибавляется число четыре. На фиг. Юв,г показаны примеры нумерации элементов на уровнях 2 и 3 Аналогично производится кодирование во всех М-1 подрежимах. В М-1 подрежиме вычисляется единственный элемент М уровня, значение яркости и терминальности которого записывается соответственно в регистры 39 и 41. По окончании М-1 подрежима кодирования счетчик 22 формирует следующий код цикла, с которого начинается непосредственно режим передачи данных по структуре квадродерева, -а именно первый его подрежим.

5

0

В режиме передачи данных в виде структуры квадродерева работают почти все блоки, кроме преобразователя 1, регистров 3 и 13 и преобразователей 4 и 14. Этот режим можно разбить на М подрежимов, в каждом из которых передаются терминальные элементы только соответствующего уровня. В первом подрежиме, который определяется кодом числа на адресном выходе счетчика, 22, осуществляется дважды передача единственного элемента М-го уровня пирамидальной структуры. В этом режиме в блоке 2 управления формируются следующие сигналы: на первом управляющем выходе продолжает держаться уровень логического нуля как и в режиме кодирования, что обеспечивает формирование Z-разверт- ки на коммутаторе 8 за счет перестановки разрядов адреса на шифраторе 35, как это показано на фиг.76. На втором управляющем выходе блока 2 5 формируется код сигнала, равный 1, который обеспечивает останов устрой-, ства после подготовки очередного элемента данных на своем информационном выходе, вплоть до запроса, поступающего по второму управляющему входу в устройство и снимающему сигнал готовности на выходе .формирователя 28,очередного элемента данных. Следовательно, генератор 6 вырабатывает последовательность тактовых импульсов с момента запроса очередного элемента данных в ЭВМ до момента записи следующего элемента в регистр 27. -Указанием наличия требуемого для передачи данного является строб,который формируется на выходе коммутатора 15, и, по которому производится запись данных в регистр 27 и установка сигнала готовности на выходе

45 формирователя 28. На шестом управляющем выходе преобразователя 26 формируется сигнал уровня логического нуля, который обнуляет делитель 24 и, следовательно, тактовые импульсы с

50 входа элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25

без изменений поступают на его выход, как и в режиме записи исходного изображения.

Из блока 9 и блока 11 считываются

55 элементы всех узлов и регистров по адресу 0, но через коммутаторы 10 и 12 на информационные входы блока 5 обработки данных поступают значения яркости и терминальности только эле0

5

4С

мента М-го уровня, так как на четвертом управляющем выходе блока 2 формируется код, коммутирующий М-й разряд информационного входа на выход коммутаторов 10 и 12. Однако, более общего элемента, описывающего изображения в пирамидальной структуре, нет следовательно в процессе передачи он должен быть передан всегда, это можно интерпретировать следующим образом: единственный элемент М-го уровня является дочерним нетерминального гипотетического элемента М+1 уровня. Таким образом, третий управляющий сигнал поступает на управляющий вход коммутатора 15 и коммутирует М+1 вход коммутатора, соединенный с шиной уровня логической единицы, на выход, соединенный с входом стробирования блока 5 обработки данных. Следовательно, элемент М уровня пирамидальной структуры всегда является элементом структуры квадродерева и переда

30

35

40

ется в ЭВМ, так как шаг развертки,фор-25 момент прерывать работу устройства мируемой преобразователем 26, равен в первом подрежиме режима передачи половине количества элементов в исходном, изображении плюс один, то первый элемент на М уровне передается дважды, после чего вырабатывается импульс переполнения на сумматоре 32,который поступает на счетный вход счетчика 22. На его выходе формируется код адреса следующего подрежима, и так далее вплоть до передачи элементов исходного изображения.

Если, при просмотре пирамидальной структуры после запроса из ЭВМ очередного элемента данных этот элемент является дочерним терминального элемента (код терминальности равен 0), который был передан ранее или также является дочерним терминального элемента, тогда на стробирующий вход блока 5 обработки данных строб уровня логической единицы не поступает и устройство на своем управляющем выходе сигнал готовности также не выставляет. Следовательно, генератор 6 продолжает вырабатывать тактовые импульсы до тех пор, пока не обнаружен элемент данных, являющийся дочерним нетерминального элемента более верхнего уровня и, следовательно, являющийся также элементом структуры квадродерева. При этом количество просмотренных устройством элементов пирамидальной структуры может быть

45

50

55

для осуществления записи, кодирован и передачи нового изображения. Это приводит к дополнительному сжатию информационного потока в режиме ас социативного поиска определенного изображения. Если передаваемое изоб ражение сильно отличается от требуе мого, в ЭВМ вводят достаточно грубо описание изображения для того, чтоб определить несоответствие передавае мого изображения требуеьюму. Следовательно, процесс передачи в некото рых случаях может быть прекращен по ле передачи первых n f M уровней опи сания изображения.

Использование изобретения обеспе чивает повышение быстродействия при вводе изображений в ЭВМ в 8-40 раз, при сохранении точности. Эффективность использования устройства при вводе изображений по медленному каналу обусловлена не только сжатием данных, но и возможностью совмещени обработки информации в приемнике с постепенным дополнением данных до требуемой точности, что, в свою оче редь, ведет к уменьшению времени пер дачи изображения до требуемой точно ти в 1-20 раз по сравнению с временем передачи всех данных об изображе нии. Эти свойства позволяют строить интерактивные системы, объединенные в сети с медленными каналами.

0

5

0

очень большое. Коэффициент сжатия исходного изображения в первом приближении равен среднему количеству элементов пирамидальной структуры просмотренных устройством для передачи одного элемента структуры квадродерева.

По окончании М-го цикла передачи данных уровня исходного изображения в сумматоре 32 формируется очередной импульс переполнения,который изменяет код на выходе счетчика 22 на единицу и переводит устройство в режим окончания передачи данных и ожидания следующего запроса ввода изображения от ЭВМ. Это осуществляется тем, что на втором управляющем выходе блока 2 формируется код 0, который маскирует сигнал неготовности устройства к передаче очередной порции данных и запрещает работу генератора 6. Имеется возможность в любой

0

5

0

5 момент прерывать работу устройства

5

0

5

для осуществления записи, кодирования и передачи нового изображения. Это приводит к дополнительному сжатию информационного потока в режиме ассоциативного поиска определенного изображения. Если передаваемое изображение сильно отличается от требуемого, в ЭВМ вводят достаточно грубое описание изображения для того, чтобы определить несоответствие передаваемого изображения требуеьюму. Следовательно, процесс передачи в некоторых случаях может быть прекращен после передачи первых n f M уровней описания изображения.

Использование изобретения обеспечивает повышение быстродействия при вводе изображений в ЭВМ в 8-40 раз, при сохранении точности. Эффективность использования устройства при вводе изображений по медленному каналу обусловлена не только сжатием данных, но и возможностью совмещения обработки информации в приемнике с постепенным дополнением данных до требуемой точности, что, в свою очередь, ведет к уменьшению времени передачи изображения до требуемой точности в 1-20 раз по сравнению с временем передачи всех данных об изображении. Эти свойства позволяют строить интерактивные системы, объединенные в сети с медленными каналами.

Формула изобретения

Устройство для ввода информации, содержащее первый преобразователь кодов, блок управления, первый ре- гистр, второй преобразователь кодов, блок обработки данных и генератор сигналов, первый выход блока управления соединен с управляющим входом первого преобразователя кодов, инфор- мационный выход и выход готовности блока обработки данных являются соответственно информационным выходом и выходом готовности устройства,первый вход запроса блока обработки дан- ных соединен с входом обнуления блока управления и является первым управляющим входом устройства, выход первого регистра соединен с информационным входом второго преобразователя кодов, отличающееся тем, что, с целью повышения быстродействия ввода информации, в устройство введены формирователь сигналов, с первого по четвертый коммутаторы, первый и второй блоки памяти, второй регистр и третий преобразователь кодов,первый вход генератора сигналов соединен с выходом готовности блока обработки данных, второй вход запроса которого является вторым управляющим входом устройства, второй вход генератора сигналов соединен с вторым выходом блока управления, тактовый вход которого соединен с выходом генератора сигналов, адресный выход формирователя сигналов соединен с информационным входом первого коммутатора,выход которого соединен с адресными входа

ми первого преобразователя кодов,пер- довходами первого и второго регистров,

вого и второго блоков памяти, выходвыход второго регистра соединен с

первого преобразователя кодов соеди-информационным входом третьего преобнен с информационным входом первогоразователя кодов.

0

5

0

5

блока памяти и с выходом второго преобразователя кодов, информационный и управляющие входы которого соединены соответственно с управляющим входом третьего преобразователя кодов и с первым выходом блока управления, третий, четвертый и пятый выходы которого соединены соответственно с управляющим входом четвертого коммутатора, управляющими входами второго и третьего коммутаторов и управляющими входами первого и второго блоков памяти, счетные вход и выход блока управления соединены соответственно с выходом переноса и счетным входом формирователя сигналов,управляющий выход которого соединен с управляющими входами первого и второго регистров, управляющий вход первого коммутатора соединен с первым выходом блока управления, вход обнуления которого соединен с управляющим входом формирователя сигналов, выход третьего преобразователя кодов соединен с информационным входом второго регистра, выход которого соединен с информационными входами третьего и четвертого коммутаторов,выход первого блока памяти соединен с информационным входом второго блока памяти, выход четвертого коммутатора соединен со стробирующим входом блока обработки данных, первый и второй информационные входы которого соединены соответственно с выходами второго и третьего коммутаторов, выходы второго и третьего коммутаторов соединены соответственно с информационными

000В

О OIB

Адрес Д Адрес Д Адрес

Вход Выход Вход Выход

М-1

Таблица I

М

Таблица2

Д j Адрес | Д

ТаблицаЗ

М

М+1

М+2

2М+3 2М-2

М-1 2М-2

23

1580340

0000 0000 О

0000 1111 О

Остальные адреса 1

Счет

24 Таблица4

Элемент терминальныйТо же

Элементы не терминальные

Фиг. 2

Фиг.З

2

инф гм-2 ннф.

Счет

гм-1

Упр

Фиг, 5

ннф.

Обнл.

33

2Н-2

Адр.

-Улр Перенос

Фиг. 6

Фиг. 7

Адр Упр Инф

2M-Z

И

Фиг. 8

щ..ТЕ

Фиг. 9

6 Фиг.10

Упрб гб L 2бх 25 1 6мг 25

Тактвх 2 УпрВ2В Г 26л 25 L бых 25

D

-нетерминальный элемент

О -терминальный элемент

I

Фиг 11

| 0 |

|

SU401989A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1974 |

|

SU555395A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-12-30—Подача