Изобретение относится к вычислительной технике, в частности к организации контроля функционирования ЭВМ и отладки программ.

Целью изобретения является повышение быстродействия при отладке,

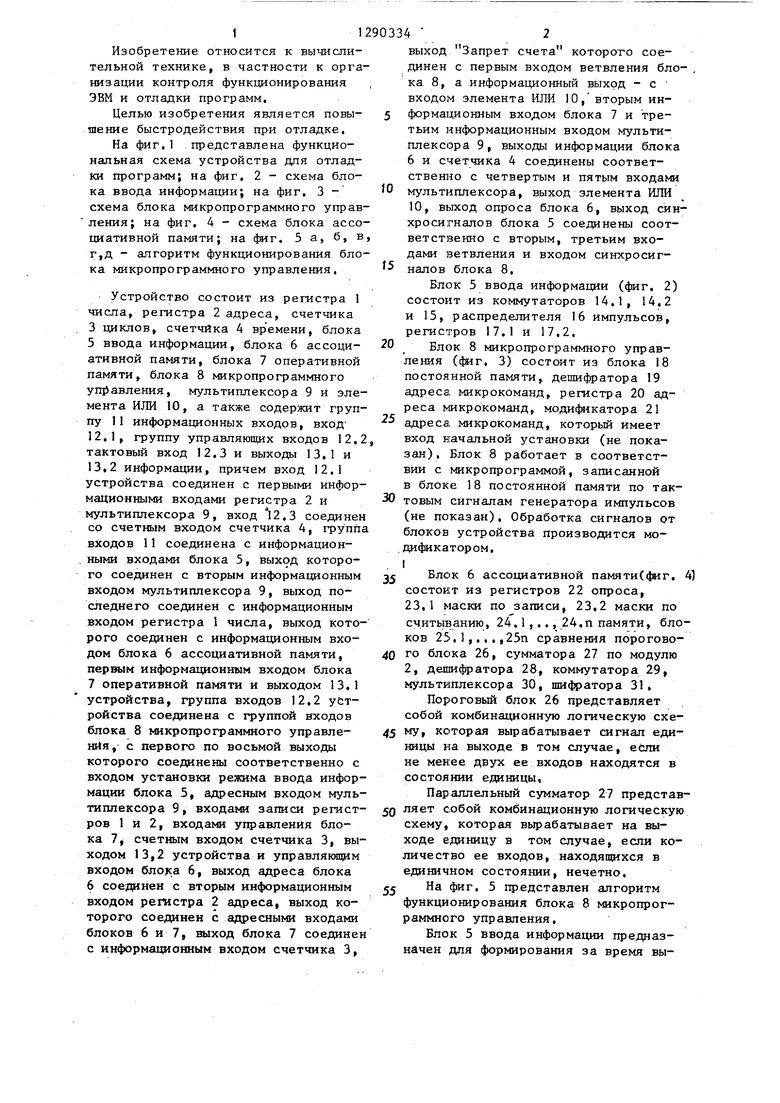

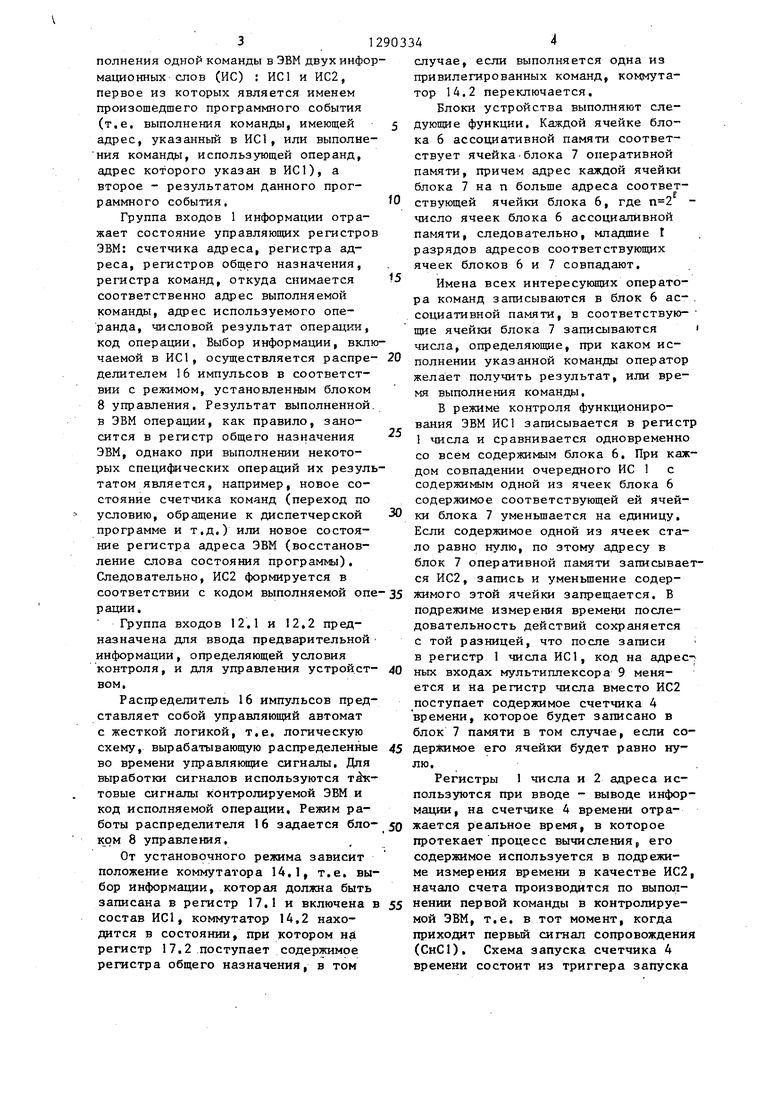

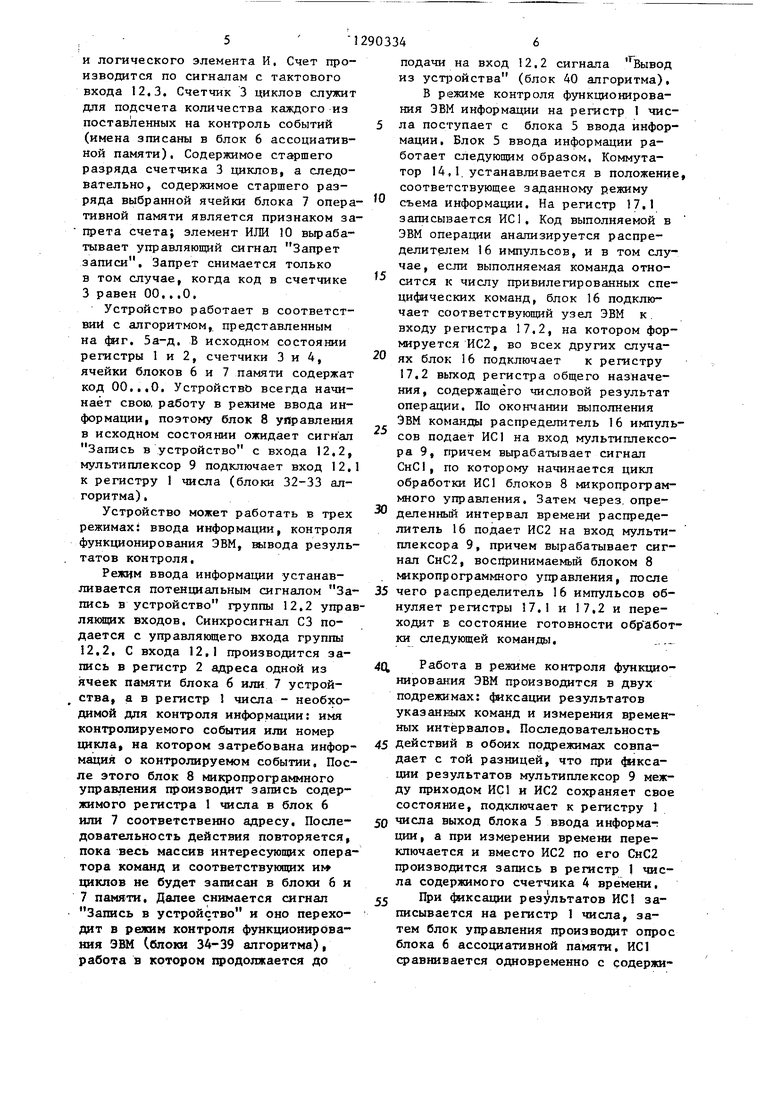

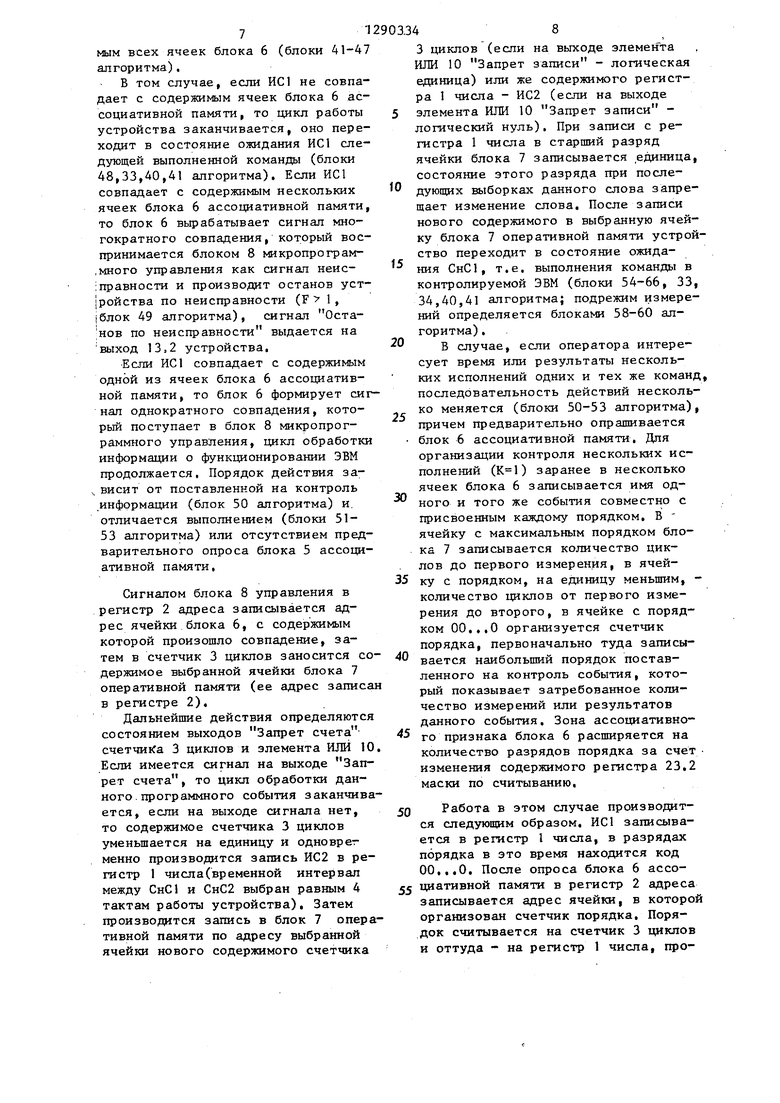

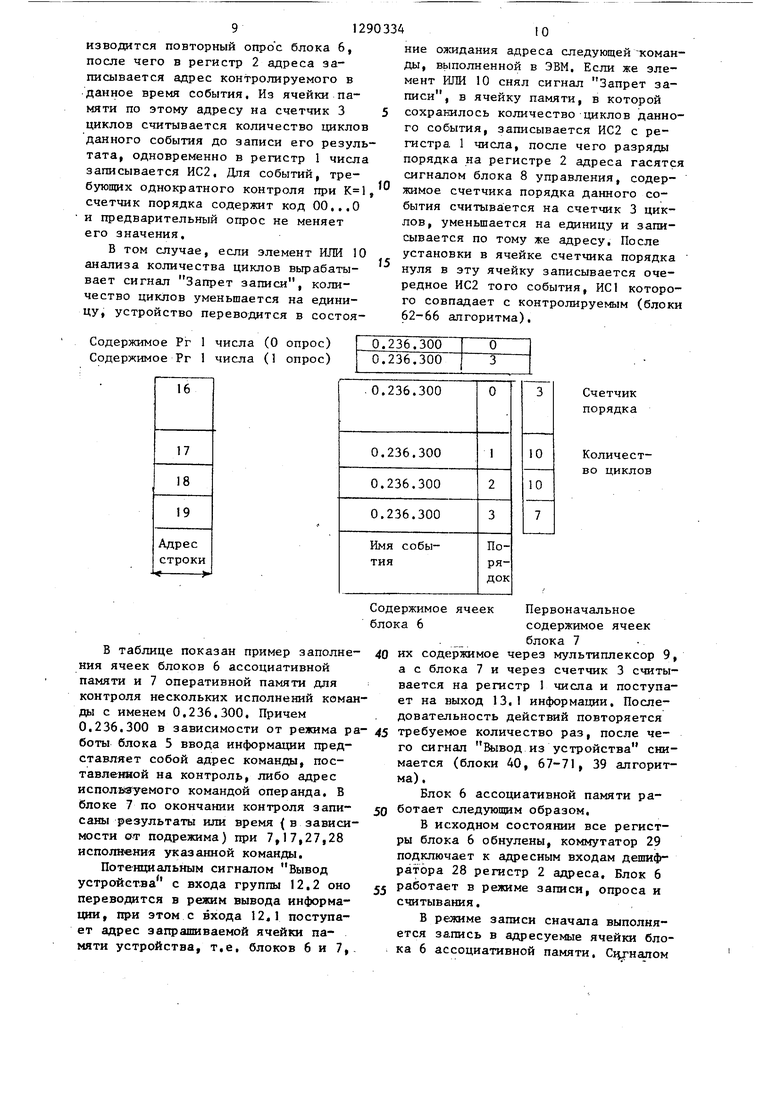

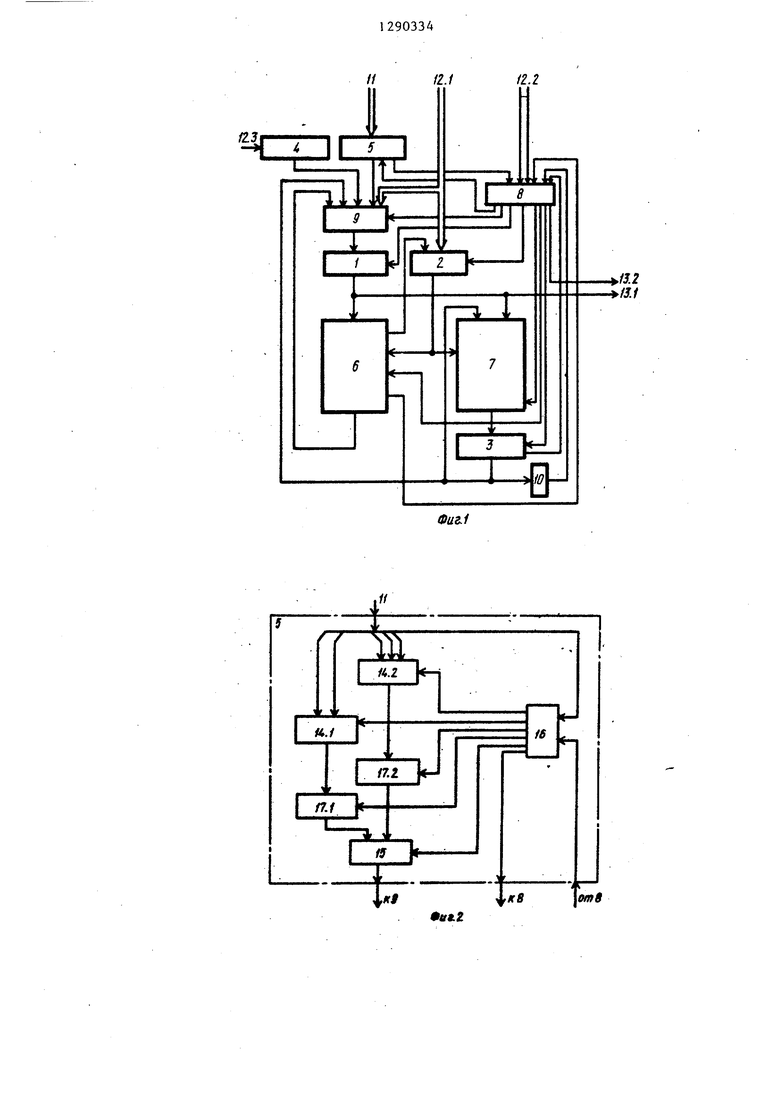

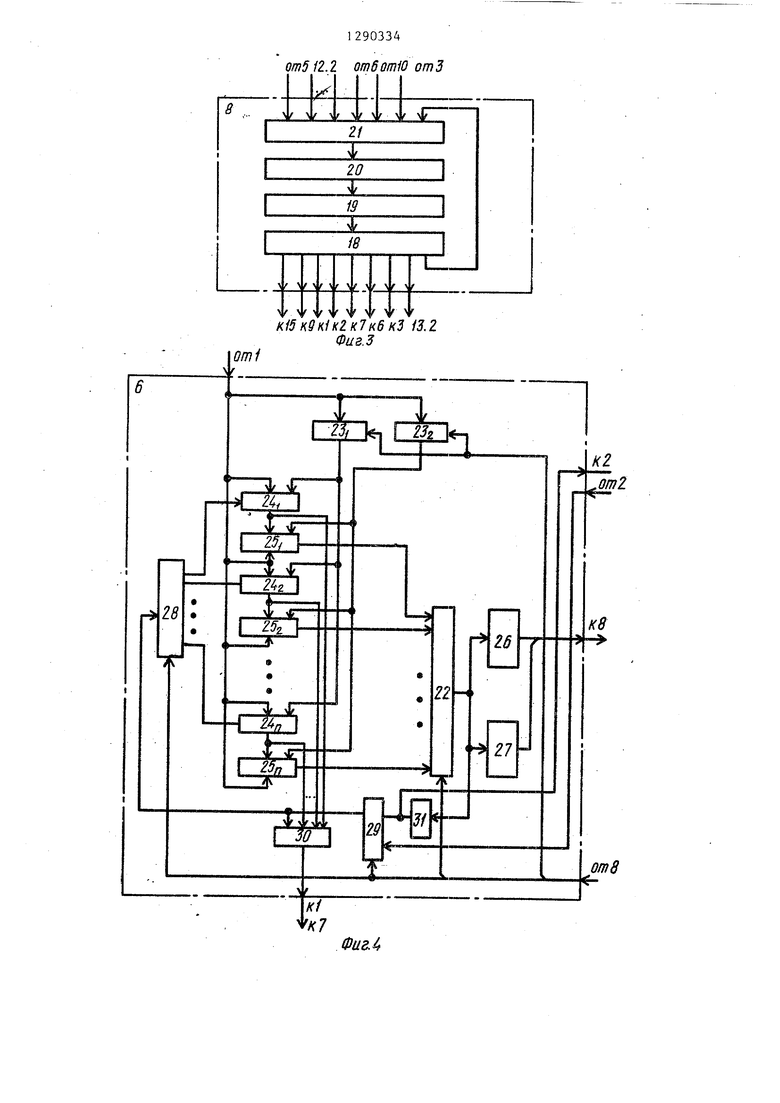

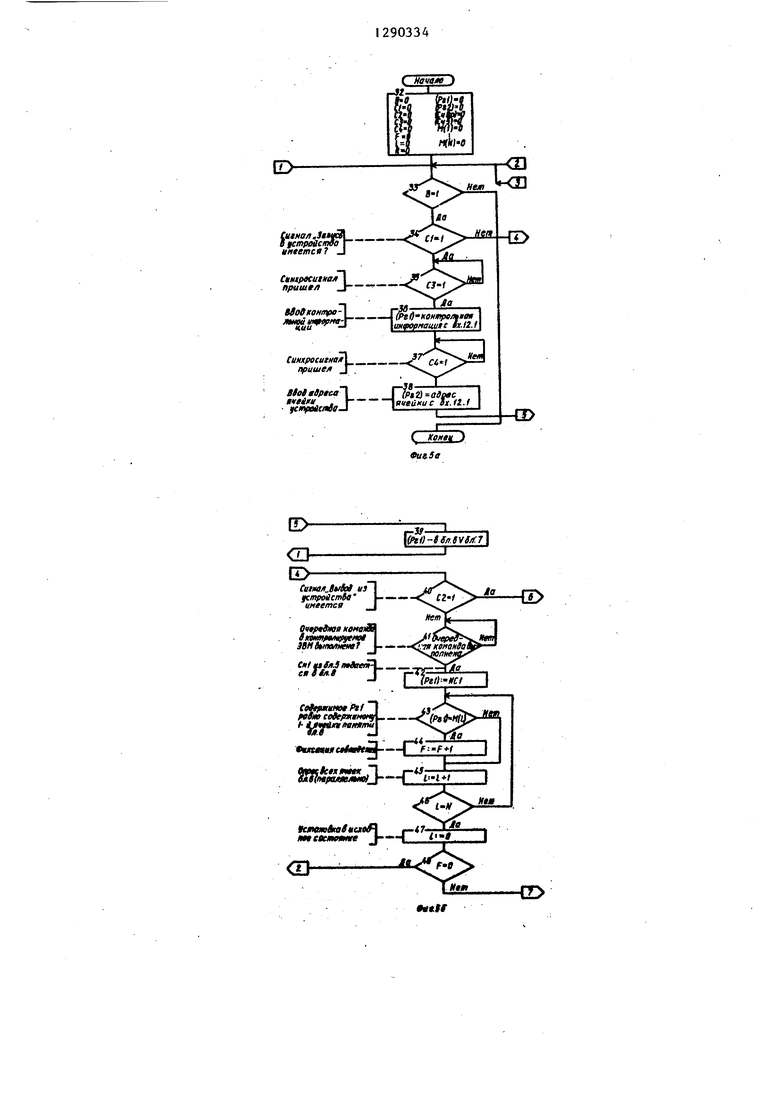

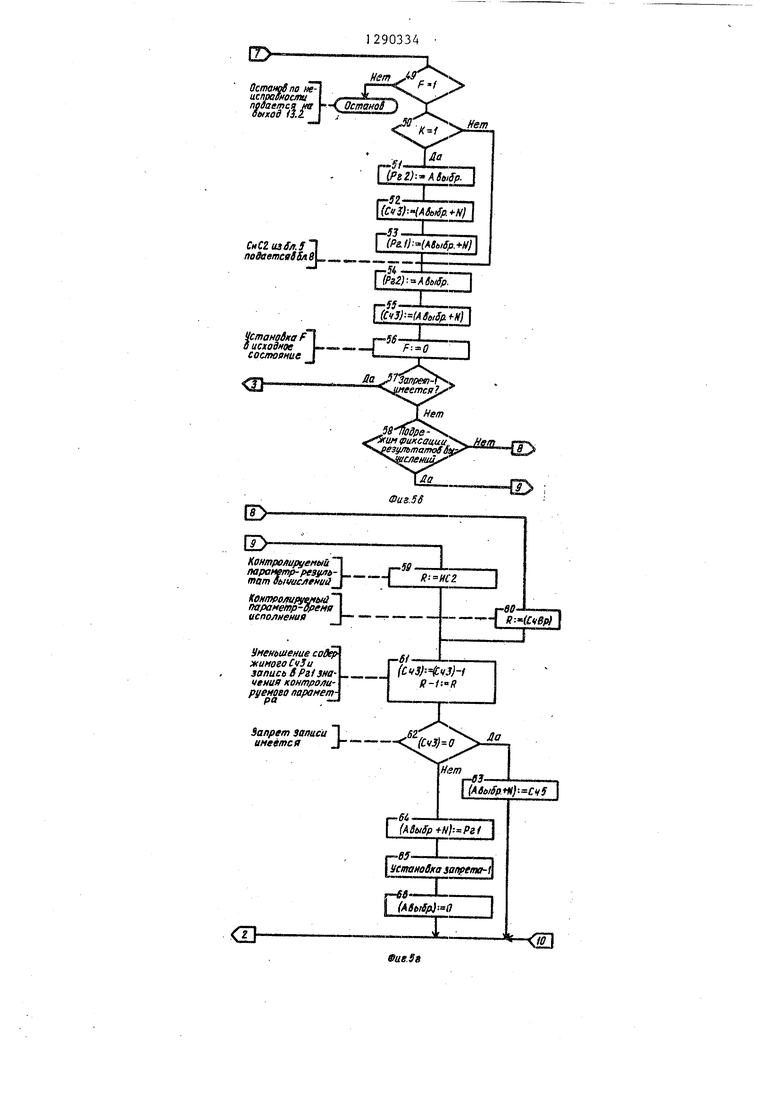

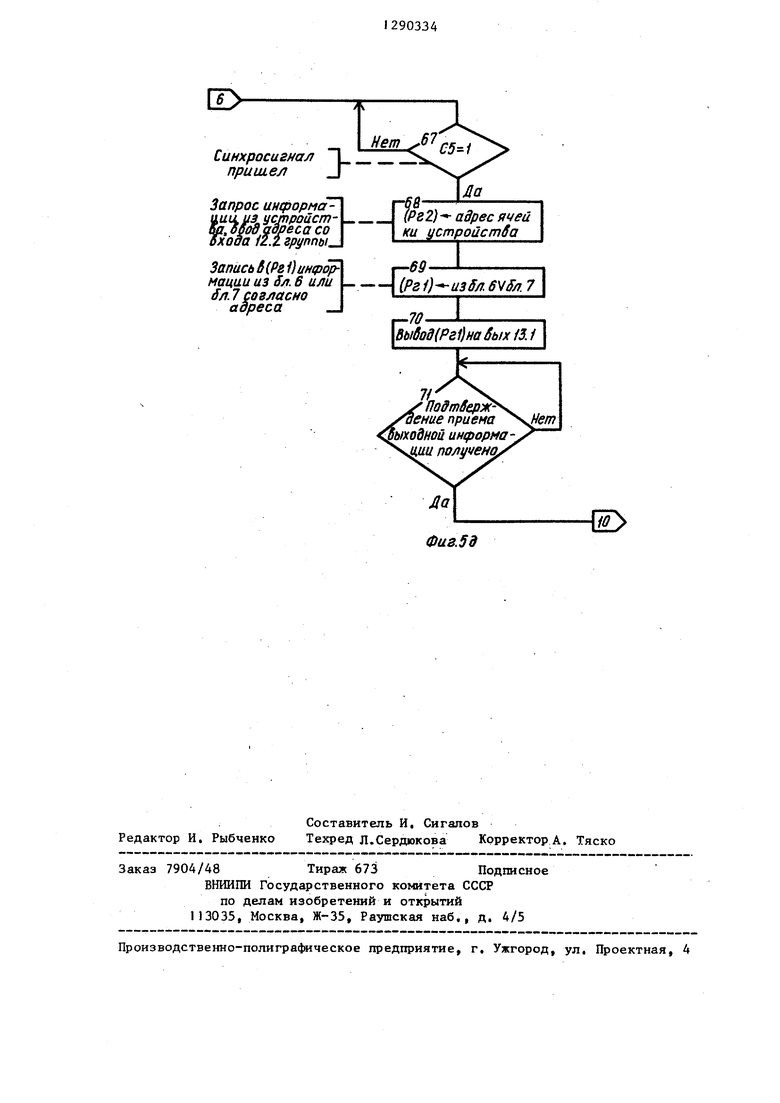

На фиг.1 представлена функциональная схема устройства для отладки программ; на фиг, 2 - схема блока ввода информации; на фиг. 3 - схема блока микропрограммного управления; на фиг, 4 - схема блока ассоциативной памяти; на 4иг. 5 а, б, в г,д - алгоритм функционирования блока микропрограммного управления.

Устройство состоит из регистра 1 числа, регистра 2 адреса, счетчика 3 циклов, счетчика 4 вр емени, блока

5ввода информации, блока 6 ассоциативной памяти, блока 7 оперативной памяти, блока 8 микропрограммного ущ5авления, мультиплексора 9 и элемента ИЛИ 10, а также содержит группу 11 информационных входов, вход- 12,1, группу управляющих входов 12.2 тактовый вход 12.3 и выходы 13,1 и 13,2 информации, причем вход 12.1 устройства соединен с первыми информационными входами регистра 2 и мультиплексора 9, вход l2,3 соединен со счетным входом счетчика 4, гру ппа

входов 11 соединена с информационными входами блока 5, выход которого соединен с вторым информационным входом мультиплексора 9, выход последнего соединен с информационным входом регистра 1 числа, выход которого соединен с информационным вхо- дом блока 6 ассоциативной памяти, первым информационным входом блока 7 оперативной памяти и вьпсодом 13,1 устройства, группа входов 12,2 у&т- ройства соединена с группой входов блока 8 микропрограммного управления, с первого по восьмой выходы которого соединены соответственно с входом установки режима ввода информации блока 5, адресным входом мультиплексора 9, входами записи регистров 1 и 2, входами управления блока 7 счетным входом счетчика 3, выходом 13,2 устройства и управлякнцим входом блок.а 6, выход адреса блока

6соединен с вторым информационным входом регистра 2 адреса, выход которого соединен с адресными входами блоков 6 и 7, выход блока 7 соединен с информационным входом счетчика 3,

выход Запрет счета которого соединен с первым входом ветвления бло- , ка 8, а информационный выход - с входом элемента ИЛИ 10, вторым информационным входом блока 7 и третьим информационным входом мультиплексора 9, выходы информации блока 6 и счетчика 4 соединены соответственно с четвертым и пятым входами

мультиплексора, выход элемента ИЛИ 10, выход опроса блока 6, выход синхросигналов блока 5 соеданены соответственно с вторым, третьим входами ветвления и входом синхросигналов блока 8.

Блок 5 ввода информации (фиг, 2) состоит из коммутаторов 14,1, 14,2 и 15, распределителя 16 импульсов, регистров 17,1 и 17.2.

Блок 8 микропрограммного управления (4иг. 3) состоит из блока 18 постоянной памяти, дешифратора 19 адреса микрокоманд, регистра 20 адреса ьикрокоманд, модификатора 21

адреса микрокоманд, который имеет вход начальной установки (не показан) . Блок 8 работает в соответствии с микропрограммой, записанной в блоке 18 постоянной памяти по тактовым сигналам генератора импульсов (не показан). Обработка сигналов от блоков устройства производится мо- дификатором,

Блок 6 ассоциативной памяти(}иг, 4} состоит из регистров 22 опроса, 23,1 маски по записи, 23,2 маски по считыванию, 24,1,.,,24,п памяти, блоков 25.1,..,,25п сравнения порогового блока 26, сумматора 27 по модулю 2, депифратора 28, коммутатора 29, мультиплексора 30, ши атора 31,

Пороговый блок 26 представляет собой комбинационную логическую схему, которая вырабатывает сигнал единицы на выходе в том случае, если не менее двух ее входов находятся в состоянии единицы.

Параллельный сумматор 27 представляет собой комбинационную логическую схему, которая вырабатывает на выходе единицу в том случае, если количество ее входов, находящихся в единичном состоянии, нечетно.

На фиг. 5 представлен алгоритм функционирования блока 8 микропрограммного управления.

Блок 5 ввода информации предназначен для формирования за время вы

3

полнения одной команды в ЭВМ двух инфомационных слов (ИС) ; ИС1 и ИС2, первое из которых является именем произошедшего программного события (т.е. выполнения команды, имеющей

адрес, указанный в ИС1, или выполне ния команды, использующей операнд, адрес которого указан в ИС1), а второе - результатом данного программного события,

Группа входов 1 информации отражает состояние управляющих регистро ЭВМ: счетчика адреса, регистра адреса, регистров общего назначения, регистра команд, откуда снимается

соответственно адрес выполняемой команды, адрес используемого операнда, числовой результат операции код операции. Выбор информации, вклчаемой в ИС1, осуществляется распре делителем 16 импульсов в соответствии с режимом, установленным блоком 8 управления. Результат выполненной в ЭВМ операции, как правило, заносится в регистр общего назначения ЭВМ, однако при выполнении некоторых специфических операций их резултатом является, например, новое состояние счетчика команд (переход по условию, обращение к диспетчерской программе и т,д,) или новое состояние регистра адреса ЭВМ (восстановление слова состояния программы), Следовательно, ИС2 формируется в соответствии с кодом выполняемой on рации.

Группа входов 12,1 и 12,2 предназначена для ввода предварительной информации, определяющей условия контроля, и для управления устройст вом.

Распределитель 16 импульсов представляет собой управляющий автомат с жесткой логикой, т.е, логическую схему, вырабатывающую распределенны во времени управляющие сигналы. Для выработки сигналов используются т товые сигналы контролируемой ЭВМ и код исполняемой операции. Режим работы распределителя 16 задается бло ком 8 управления.

От установочного режима зависит положение коммутатора 14,1, т,в, выбор информации, которая должна быть записана в регистр 17,1 и включена состав ИС1, коммутатор 14,2 находится в состоянии, при котором на регистр 17,2 поступает содержимое регистра общего назначения, в том

5

0334

5

o

5

0 0 5

0

5 0

5

4

случае, если выполняется одна из привилегированных команд, коцмута- тор 14,2 переключается.

Блоки устройства выполняют следующие функции. Каждой ячейке блока 6 ассоциативной памяти соответствует ячейка-блока 7 оперативной памяти, причем адрес каждой ячейки блока 7 на п больше адреса соответствующей ячейки блока 6, где число ячеек блока 6 ассоциаливной памяти, следовательно, младшие I разрядов адресов соответствующих ячеек блоков 6 и 7 совпадают,

Имена всех интересующих оператора команд записываются в блок 6 ас- . социативной памяти, в соответствую- ячейки блока 7 записываются числа, определяющие, при каком исполнении указанной команды оператор желает получить результат, или время выполнения команды,

В режиме контроля функционирования ЭВМ ИС1 записывается в регистр 1 числа и сравнивается одновременно со всём содержимым блока 6, При каждом совпадении очередного ИС 1 с содержимым одной из ячеек блока 6 содержимое соответствующей ей ячейки блока 7 уменьшается на единицу. Если содержимое одной из ячеек стало равно нулю, по зтому адресу в блок 7 оперативной памяти записывается ИС2, запись и уменьшение содержимого зтой ячейки запрещается, В подрежиме измерения времени последовательность действий сохраняется с той разницей, что после записи в регистр 1 числа ИС1, код на адрес- ных входах мультиплексора 9 меняется и на регистр числа вместо ИС2 поступает содержимое счетчика 4 времени, которое будет записано в блок 7 памяти в том случае, если содержимое его ячейки будет равно нулю,

Регистры 1 числа и 2 адреса используются при вводе - выводе информации, на счетчике 4 времени отражается реальное время, в которое протекает процесс вычисленияр его содержимое используется в подрежиме измерения времени в качестве ИС2, начало счета производится по выполнении первой команды в контролируемой ЭВМ, т,е, в тот момент, когда приходит первьм сигнал сопровождения (СиС1), Схема запуска счетчика 4 времени состоит из триггера запуска

10

f5

20

25

5 4290334

и логического элемента И, Счет производится по сигналам с тактового входа 12,3. Счетчик 3 циклов служит для подсчета количества каждого из поставленных на контроль событий (имена зписаны в блок 6 ассоциативной памяти). Содержимое старшего разряда счетчика 3 циклов, а следовательно, содержимое старшего разряда выбранной ячейки блока 7 оперативной памяти является признаком за- прета счета; элемент ИЛИ 10 вырабатывает управляющий сигнал Запрет записи. Запрет снимается только в том случае, когда код в счетчике 3 равен 00...0.

Устройство работает в соответствии с алгоритмом, представленным на фиг. 5а-д. В исходном состоянии регистры 1 и 2, счетчики 3 и 4, ячейки блоков 6 и 7 памяти содержат код 00...0. Устройство всегда начинает свою, рг1боту в режиме ввода информации, поэтому блок 8 управления в исходном состоянии ожидает сигнал Запись в устройство с входа 12.2, мультиплексор 9 подключает вход 12.1 к регистру 1 числа (блоки 32-33 алгоритма) .

Устройство может работать в трех режимах: ввода информации, контроля функционирования ЭВМ, вывода результатов контроля.

Режим ввода информации устанавливается потенциальным сигналом Запись в устройство группы 12.2 управляющих входов. Синхросигнал СЗ подается с управляющего входа группы 12.2. С входа 12.1 производится запись в регистр 2 адреса одной из ячеек памяти блока б или 7 устройства, а в регистр 1 числа - необходимой для контроля информации: имя контролируемого события или номер цикла, на котором затребована информация о контролируемом событии, После этого блок 8 микропрограммного управления производит запись содержимого регистра 1 числа в блок 6 или 7 соответственно адресу. После- довательность действия повторяется, пока весь массив интересующих оператора команд и соответствую1цих и циклов не будет записан в блоки 6 и 7 памяти. Далее снимается сигнал Запись в устройство и оно переходит в режим контроля функционирования ЭВМ (блоки 34-39 алгоритма), работа в котором щ)одолжается до

и л

30

35 ч

40,

45 д

50 ч

55

5

0

5

подачи на вход 12,2 сигнала Ъывод из уст1зойства (блок 40 алгоритма), В р(вжиме контроля функционирования ЭВМ информации на регистр 1 числа поступает с блока 5 ввода информации. Блок 5 ввода информации работает следующим образом. Коммутатор 14,1. устанавливается в положение, соответствующее заданному режиму съема информации. На регистр записывается ИС1. Код выполняемой в ЭВМ операции анализируется распределителем 16 импульсов, и в том случае , если выполняемая команда отно0

сится к числу привилегированных специфических команд, блок 16 подключает соответствуюшяй узел ЭВМ к. входу регистра 17,2, на котором формируется ИС2, во всех других случаях блок 16 подключает к регистру 17.2 выход регистра общего назначения, содержащего числовой результат операции. По окончании выполнения ЭВМ команды распределитель 16 импульсов подает ИС1 на вход мультиплексора 9, причем вырабатывает сигнал СнС1, по которому начинается цикл обработки ИС1 блоков 8 микропрограммного управления. Затем через, определенный интервал времени распределитель 16 подает ИС2 на вход мультиплексора 9, причем вырабатывает сигнал СнС2, восйринимаемый блоком 8 микропрограммного управления, после 5 чего распределитель 16 импульсов обнуляет регистры 17,1 и 17,2 и переходит в состояние готовности обр абот- ки следующей команды....0, Работа в режиме контроля функцио- нирован ия ЭВМ производится в двух подрежимах: фиксации результатов указанных команд и измерения временных интервалов. Последовательность

5 действий в обоих подрежимах совпадает с той разницей, что при фиксации результатов мультиплексор 9 между приходом ИС1 и ИС2 сохраняет свое состояние, подключает к регистру 1

50 числа выход блока 5 ввода информа-г ции, а при измерении времени переключается и вместо ИС2 по его СнС2 производится запись в регистр 1 числа содержимого счетчика 4 времени.

55 При фиксации результатов НС записывается на регистр 1 числа, затем блок управления производит опрос блока 6 ассоциативной памяти, ИС1 сравнивается одновременно с содержимым всех ячеек блока 6 (блоки 41-47 алгоритма),

В том случае, если ИС1 не совпадает с содержимым ячеек блока 6 ассоциативной памяти, то цикл работы устройства заканчивается, оно переходит в состояние ожидания ИС1 следующей выполненной команды (блоки 48,33,40,41 алгоритма). Если ИС1 совпадает с содержимым нескольких ячеек блока 6 ассоциативной памяти, то блок 6 вьфабатывает сигнал многократного совпадения, который воспринимается блоком 8 микропрограм- много управления как сигнал неис- правности и производит останов уст- ройства по неисправности (F 1, блок 49 алгоритма), сигнал Оста- нов по неисправности выдается на выход 13s2 устройства,

Если ИС1 совпадает с содержимым одной из ячеек блока 6 ассоциативной памяти, то блок 6 формирует сигнал однократного совпадения, который поступает в блок 8 микропрограммного управления, цикл обработки информации о функционировании ЭВМ продолжается. Порядок действия за- висит от поставленной на контроль информации (блок 50 алгоритма) и. отличается выполнением (блоки 51- 53 алгоритма) или отсутствием предварительного опроса блока 5 ассоциативной памяти,

Сигналом блока 8 управления в егистр 2 адреса записывается адес ячейки блока 6, с содержимым которой произошло совпадение, затем в счетчик 3 циклов заносится содержимое выбранной ячейки блока 7 оперативной памяти (ее адрес записан в регистре 2),

Дальнейшие действия определяются состоянием выходов Запрет счета счетчивГа 3 циклов и элемента ИЛИ 10, сли имеется сигнал на выходе Запрет счета, то цикл обработки даного, программного события заканчивается, если на выходе сигнала нет, то содержимое счетчика 3 циклов уменьшается на единицу и одноврет менно производится запись ИС2 в регистр 1 числа(временной интервал между СнС1 и СнС2 выбран равным 4 тактам работы устройства). Затем производится запись в блок 7 оперативной памяти по адресу выбранной ячейки нового содержимого счетчика

5

0

5

3 циклов (если на выходе элемента , ИЛИ 10 Запрет записи - логическая единица) или же содержимого регистра 1 числа - ИС2 (если на выходе элемента ИЛИ 10 Запрет записи - логический нуль), При записи с регистра 1 числа в старший разряд ячейки блока 7 записывается единица, состояние этого разряда при последующих выборках данного слова запрещает изменение слова. После записи нового содержимого в выбранную ячейку блока 7 оперативной памяти устройство переходит в состояние ожидания СнС1, т,е, выполнения команды в контролируемой ЭВМ (блоки 54-66, 33, 34,40,41 алгоритма; подрежим измерений определяется блоками 58-60 алгоритма) ,

В случае, если оператора интересует время или результаты нескольких исполнений одних и тех же команд, последовательность действий несколько меняется (блоки 50-53 алгоритма), причем предварительно опрашивается блок 6 ассоциативной памяти. Для организации контроля нескольких исполнений () заранее в несколько ячеек блока 6 записывается имя одного и того же события совместно с присвоенным каждому порядком, В ячейку с максимальным порядком блока 7 записывается количество циклов до первого измерения, в ячейку с порядком, на единицу меньшим, - количество циклов от первого измерения до второго, в ячейке с порядком 00,,,О организуется счетчик порядка, первоначально туда записывается наибольший порядок поставленного на контроль события, который показывает затребованное количество измерений или результатов данного события. Зона ассоциативного признака блока 6 расширяется на количество разрядов порядка за счет изменения содержимого регистра 23,2 маски по считыванию.

0

5

0

5

Работа в этом случае производится следующим образом, ИС1 записывается в регистр 1 числа, в разрядах порядка в это время находится код 00,,,О, После опроса блока 6 ассо- 55 циативной памяти в регистр 2 адреса записывается адрес ячейки, в которой организован счетчик порядка. Порядок считывается на счетчик 3 циклов и оттуда - на регистр 1 числа, про50

9129

изводится повторный опро с блока 6, после чего в регистр 2 адреса записывается адрес контролируемого в данное время события. Из ячейки па мяти по этому адресу на счетчик 3 циклов считывается количество циклов данного события до записи его результата, одновременно в регистр 1 числа записывается ИС2, Для событий, требующих однократного контроля при , счетчик порядка содержит код 00...О и предварительный опрос не меняет его значения.

В том случае, если элемент ИЛИ 10 анализа количества циклов вырабатывает сигнал Запрет записи, количество циклов уменьшается на единицу, устройство переводится в состоя

Содержимое Рг 1 числа (О опрос) Содержимое Рг 1 числа (1 опрос)

16

17

Адрес строки «

В таблице показан пример заполнения ячеек блоков 6 ассоциативной памяти и 7 оперативной памяти для контроля нескольких исполнений команды с именем 0.236.300. Причем 0.236.300 в зависимости от режима работы блока 5 ввода информации представляет собой адрес команды, поставленной на контроль, либо адрес исполвзуемого командой операнда, В блоке 7 по окончании контроля записаны результаты или время { в зависимости от подрежима) при 7,17,27,28 исполнения указанной команды.

Потенциальным сигналом Вывод устройства с входа группы 12,2 оно переводится в режим вывода информации, при этом с входа 12,1 поступает адрес запрашиваемой ячейки памяти устройства, т.е. блоков 6 и 7,34

10

ние олсидания адреса следующей команды, выполненной в ЭВМ. Если же элемент ШШ 10 снял сигнал Запрет записи, в ячейку памяти, в которой сохранилось количество циклов данного события, записывается ИС2 с регистра 1 числа, после чего разряды порядка на регистре 2 адреса гасятся сигналом блока 8 управления, содержимое счетчика порядка данного события считывается на счетчик 3 циклов, уменьшается на единицу и записывается по тому же адресу. После установки в ячейке счетчика порядка нуля в эту ячейку записывается очередное ИС2 того события, ИС1 которого совпадает с контролируемым (блоки 62-66 алгоритма).

Счетчик порядка

Количество циклов

одержимое ячеек лока 6

0

Первоначальное содержимое ячеек . блока 7

их содержимое через мультиплексор 9, а с блока 7 и через счетчик 3 считывается на регистр 1 числа и поступает на выход 13.1 информации. Последовательность действий повторяется 45 требуемое количество раз, после чего сигнал Вывод из устройства снимается (блоки 40, 67-71, 39 алгоритма) .

Блок 6 ассоциативной памяти ра- 50 ботает следующим образом.

В исходном состоянии все регистры блока 6 обнулены, коммутатор 29 подключает к адресным входам дешифратора 28 регистр 2 адреса. Блок 6 JJ работает в режиме записи, опроса и считывания.

В режиме записи сначала выполняется запись в адресуемые ячейки блока 6 ассоциативной памяти. Сг налом

де однократного совпадения - 1, Если же регистр 22 опроса не содержит ни одной единицы, на выходах блока 26 и сумматора 27 - О,

Содержимое регистра 22 опроса подается на вход шифратора 31, на выходах которого формируется адрес ячейки, с ассоциативным признаком которой произошло совпадение. Этот адрес поступает на выходы адреса блока 6 ассоциативной памяти. Сформированный адрес ячейки записывается .в регистр 2 по сигналу блока 8 управления при поступлении на блок 8

Запись с блока 8 микропрограммного управления возбуждается выход дешифратора 28, соответствующий содер 38имому счетчика регистра 2 адреса, и информация с регистра 1 числа за- . писывается в указанную ячейку,

После окончания записи массива информации в ячейки блока 6 производится запись в регистры 23,1 и 23.2 маски с регистра 1 числа по специальным сигналам с блока 8 микропрограммного управления,

В режиме опроса блок 6 ассоциативной памяти работает следующим образом, В случае совпадения информации регистра 1 числа с содержимым одного из регистров 24 на выходе подсоединенного к нему блока 25 сравнения вырабатывается потенциал, соответствующий уровню 1, По сигналу опроса блока 8 микропрограм- много управления производится запись 1 в разряд регистра 22 опроса, соответству1ощий ячейке блока 6 ассоциативной памяти, содержимое которой равно информации на входе блока 6, Так как одновремен но в регистр 22 опроса могут быть записаны несколько единиц, проводится анализ многократного совпадения пороговым блоком 26,

В том случае, если в регистре 22 опроса содержится более одной единицы на выходе многократного совпадения блока 6 ассоциативной памяти вырабатывается 1, На выходе сумматора 27 по модулю 2 и соответственно на выходе однократного совпадения блока 6 ассоциативной памяти 1 появляется тогда, когда в регистре 22 содержится нечетное количество единиц, следовательно, если в регистре 22 опроса содержится одна единица, то на выходе многократного совпадения вьфабатывается О, а на выхо-

сигнала однократного совпадения, при зтом на выходе мультиплексора 30 устанавливается код, равный содержимому мпадщих Г разрядов выбранной ячейки ассоциативной памяти,

В режиме считывания код с регистра 2 адреса поступает через коммутатор 29 на адресные входы мультиплексора 30, на выход которого поступает информация с соответствующей адресу ячейки блока 6 ассоциативной памяти.

Таким образом, предлагаемое устройство позволяет строить трассу выполнения программы с указанием последовательности событий (последовательность событий определяется.по времени их наступления) без нарушения временной диаграммы работы ЭВМ, причем измеряет временные интервалы между заданными командами и фиксирует результаты выполнения заданных команд, что значительно расширяет область применения и повьппа- ет эффективность и быстродействие устройства при отладке программного обеспечения и контроле функционирования специализированных ЭВМ, содержащихся в системах управления, ра- ботающих в реальном масштабе времени.

Устройство позволит исключить использование специализированной ЭВМ для измерения времени работы элемен- тов программы путем введения в тело программы специально разработанных вставок. Сокращение времени измерения временных интервалов ведет к сокращению времени отладки программных изделий в целом; кроме того, отпадает необходимость разработки и включения программных вставок.

Формула изобретения

Устройство для отладки программ, содержащее регистр числа, элемент ЛИ, регистр адреса, счетчик циклов, блок ассоциативной памяти, блок оперативной памяти и блок микропрограммного управления, причем выход регистра числа соединен с информационным входом блока ассоциативной памяти и является информационным выходом устройства, выход поля адреса блока ассоциативной памяти соединен с первым информационным входом регистра адреса, выход которого соединен с адресными входами блоков ассоto

5

131290334

иативной и оперативной памяти, адресый вход устройства соединен с вторым нформационным входом регистра адреса, нформацио шый выход счетчика циклов оединен с первым информаи 1онным входом 5 блока оперативной памяти, группа входов заданного режима и условий контроля устройства соединена с группой входов задания ветвления блока микропрограммного управления, первый, второй, третий, четвертый пятый выходы блока микропрограммного управления соединены соответственно с входами записи регистра числа, регистра адреса, со счетным входом счетчика циклов, с входом обращения блока оперативной памяти, с входом обращения блока ассоциативной памяти, отличающееся тем, что, с целью повышения ) быстродействия при отладке, в устойство введены счетчик времени, блок ввода информации и мультиплексор , причем блок ввода информации содержит первый, второй и третий коммутаторы, первый и второй регисты и распределитель импульсов, причем информационньш вход устройства соединен с информационными входами первого и второго коммутаторов, вход задания режима устройства соеинен с входом задания режима распределителя импульсов блока ввода ин- формаоди, выходы первого и второго коммутаторов блока ввода информации соединены с информационными входами соответственно первого и второго регистров блока ввода информации, нформационные выходы первого и второго регистров блока ввода информации соединены соответственно с первым и вторым информационными входами третьего коммутатора блока вво- да информации, информационный выход третьего коммутатора блока ввода информации соединен с первым инфор.м ш с вх к вы тр вы к в пе вх ги го ци ад вт пл ин чи вт оп ус до ны ть пл ка ве т в 35 р о n к в

20

25

30

40

45

o

5

0334

5

14

.мационным входом мультиплексора, шестой, седьмой и восьмой выходы блока М1 кропрограммного управления соединены соответственно с тактовым входом распределителя импульсов блока ввода информации, адресным входом мультиплексора и тактовым . выходом устройства, первый, второй, третий, четвертый, пятый и шестой выходы распределителя импульсов блока ввода информации соединены соответственно с управляющими входами первого и второго коммутаторов, с входами записи первого и второго регистров, управляющим входом третьего комм: гтатора блока ввода информации и с входом логических условий блока микропрограммного управления, адресный вход устройства соединен с вторым информационным входом мультиплексора, выход которого соединен с информационным входом регистра числа, выход которого соединен с вторым информац;ионным входом блока оперативной памяти, тактовый вход устройства соединен со счетным входом счетчика времени, информационный выход которого соединен с третьим информационным входом мультиплексора, информационный выход блока оперативной памяти соединен с четвертым информационным входом коммутатора и через элемент ИЛИ с первым входом модификации адреса блока мик- 35 ропрогр,аммного управления, информационный и признаковый выходы блока ; ассоциативной памяти соединены соответственно с пятым информационным входом 1)ультиш1ексора и вторым входом модификации адреса блока микро- nporpaMi Cioro управления, выход бло- ка оперативной памяти соединен с информационным входом счетчика циклов, выход переполнения которого соединен с третьим входом модификации адреса

0

5

30

40

45

блока микропрограммного управления.

f2.3i

II

ли

//11.1

il.l

Ж

/6

,,Х8

от§

omSiZ.l отботЮ отЗ

,Л««3|

ficmpaeciaffo Г entemceJ J

CtiMpMutm l npumta J

a

IKTI

Синхросигнал пришел Jf

йМввр еаЛ

vieifH , f- ymftatMa

)tfVc ln.fi.t

L.

(, Xoxtt 9ue.Sa

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Устройство для поиска информации в памяти | 1988 |

|

SU1520547A1 |

Изобретение относится к области вычислительной техники, в частности к организации контроля функционирования ЭВМ и отладки программ. Цель изобретения - повышение быстродействия при отладке. Устройство содержит регистр числа, регистр адреса, счет,чик циклов, счетчик времени, блок ввода информации, блок ассоциативной памяти, блок оперативной памяти, блок микропрограммного управ- ле1шя, мультиплексор и элемент ИЛИ. Устройство позволяет исключить использование ЭВМ для 1 измерения времени работы элементов программы путем введения в тело программы специально разработанных вставок. 5 ил., 1 табл. Q (О fe О 00 00 4

CLr

Ciuiia/t,tbiM us ecmpoicmta vneemce

ч квнвЛ

/ тагжг

Си ttf/ij авваеяР- еявЛ.

Ce fKUtetPil Ювмв северявнвму t-tJHyunMMmia

«utnMcWMr«}E/lrMMMir

ктм0Ав «айЛ

fH9 слс яяалл p

,

(l ta-tiflevSa:7

n iaemcsi а -

аыкйд

Cntiui3Sfl.5 ao&iemeifiSa8L,,

Установка f

О исходное I

состояние j

/«-а±.

(Ptl)(

.«-J.

{C4S}:«(f(6blSp.N}

--53 - I 1

I (Pa.ti-- iAtbi6p.-H)

Г-54 . -,

/f32 ;:./4fo/.J

p-ffi

{jftJA-gM fe/J/jfy/j

Фиг.5в

Контромруеный параметр-результат SbimcjtfHuii

KOHUipo/fUfye/iMi

паранетр-1у ема

исполнения

Уменьшение содер- иного CvJu запись 8 Рг1 значения контроли- руеново паранет.SS-

-вО

f-gp-

{

r-tf/-()- $:чзН

Синхросигнал 1 пришел j

Запрос ииформа 4u.(jLU3 ycjnpoucm- L м,ббодадреса со 6X0 да 12.2 группы Л

Запись 6(Рг 1)имр нации из Sfl. 6 или блЛ согласно адреса

г

I 1Рг2) адрес ки ycmpoucmSa

69РУ--it)

из Уд 6Vfл. 7

701

Выбод(Рг1)на бых 13.1

Составитель И, Сигалов Редактор И. Рыбченко Техред Л.Сердюкова Корректор А. Тяско

Заказ 7904/48Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигра4ическое предприятие, г, Ужгород, ул. Проектная, 4

7Г

Подтвержу 1ение приема

шоЬной. информа- и получено

Фиг.5д

| Фараджев В | |||

| А | |||

| Комплекс аппаратных средств ЭВМ для отладки прог- paMhft i реального времени | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1983-04-01—Подача