4Ь

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство подавления низкочастотных помех при приеме видеоимпульсного сигнала | 1988 |

|

SU1626389A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1640823A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1533005A1 |

| Устройство выделения информационных импульсов при наличии помех | 1982 |

|

SU1046944A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1215164A1 |

| Устройство выделения информационных импульсов при наличии помех | 1986 |

|

SU1401616A2 |

| Устройство для аналого-цифрового преобразования импульсных сигналов | 1987 |

|

SU1564725A1 |

| Трехпозиционное реле | 1982 |

|

SU1034180A1 |

| Устройство для цифровой фильтрации | 1983 |

|

SU1109889A1 |

| Устройство выделения информационных импульсов с фиксированной амплитудой на фоне узкополосной помехи | 1979 |

|

SU896765A1 |

Изобретение относится к радиотехнике и может быть использовано в импульсной технике. Целью изобретения является повышение точности воспроизведения информационных импульсов в условиях помех. Устройство содержит дефференцирующую цепь 1, алгебраический сумматор 2, интегратор 3, таймер 4, логический элемент 5, вероятностное реле 6, элемент задержки 7 и одновибратор 8. Поставленная цель достигается введением элементов 2-8. Это обеспечивает повышение точности воспроизведения импульсных сигналов на фоне медленно меняющейся помехи. 3 ил.

со о JИзобретение относится к радиотехнике и может использоваться для воспроизведения импульсных сигналов произвольной формы, искаженных HHSKO частотными и высокочастотными помехами

Цель изобретения - повышение точности воспроизведения информационных импульсов произвольной формы в уело- виях помех.

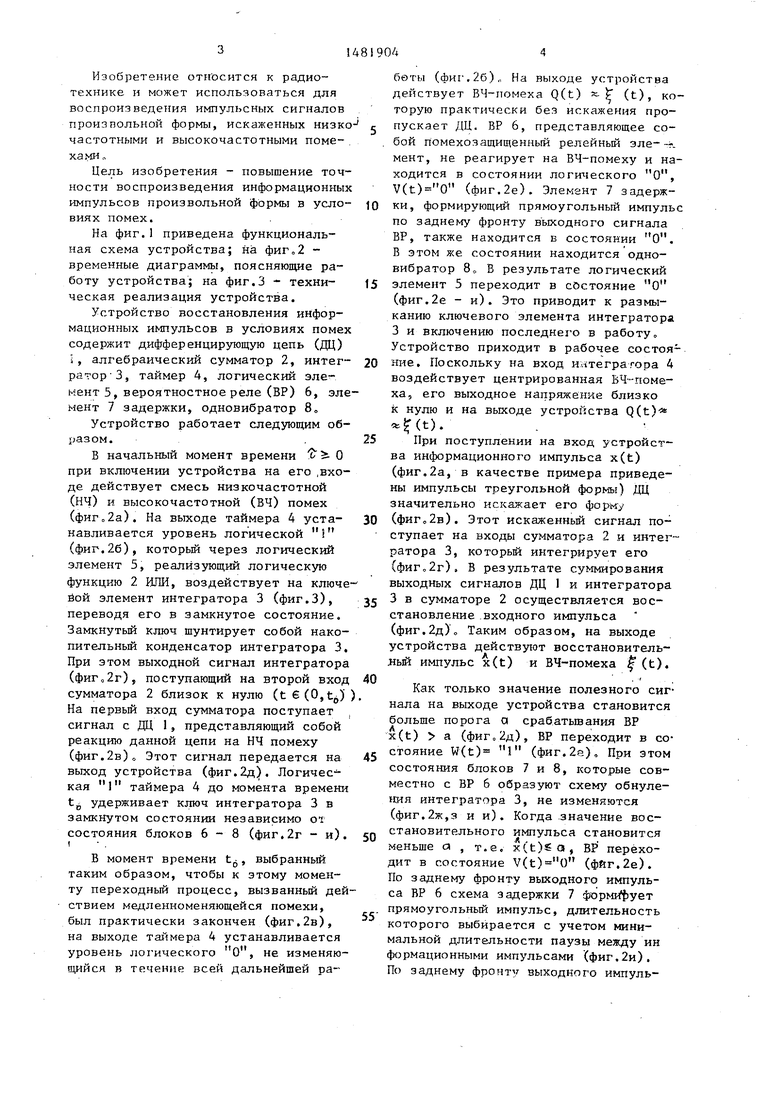

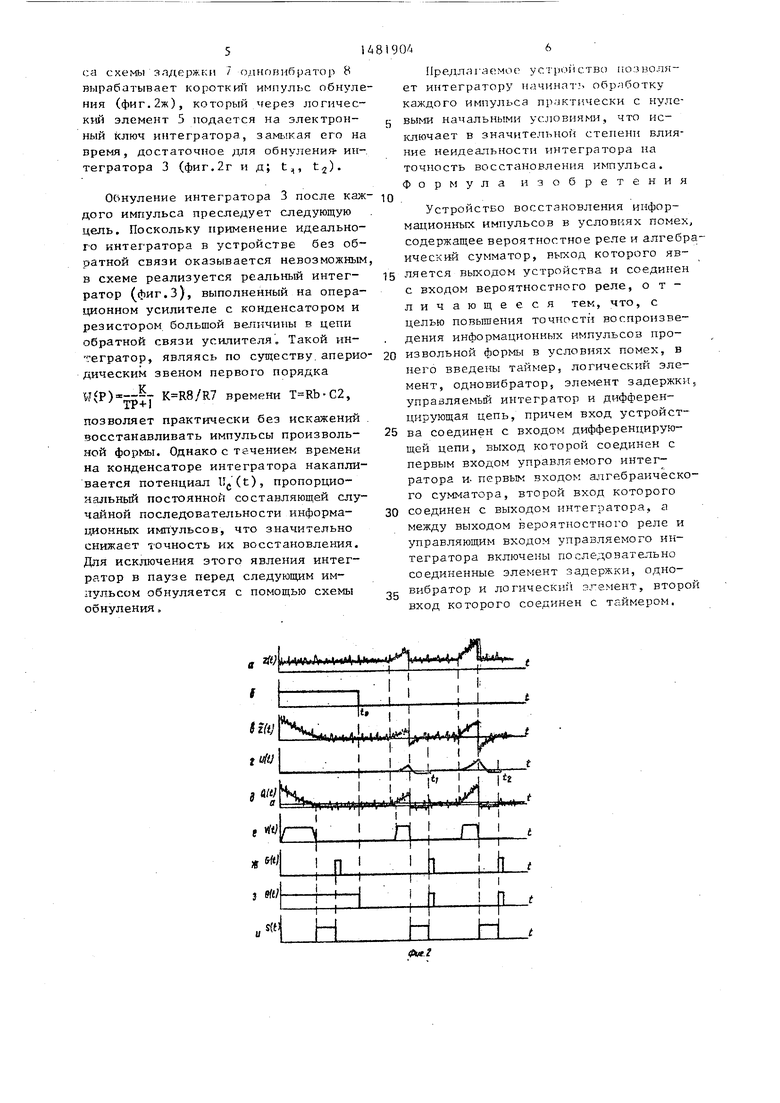

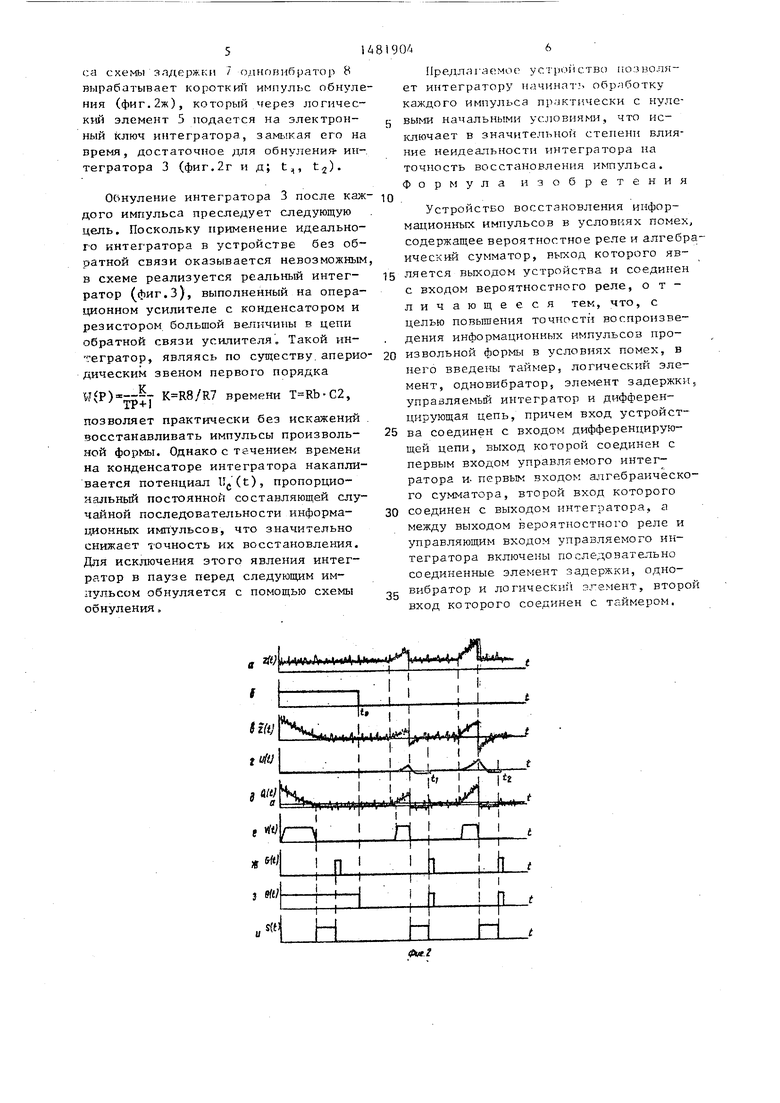

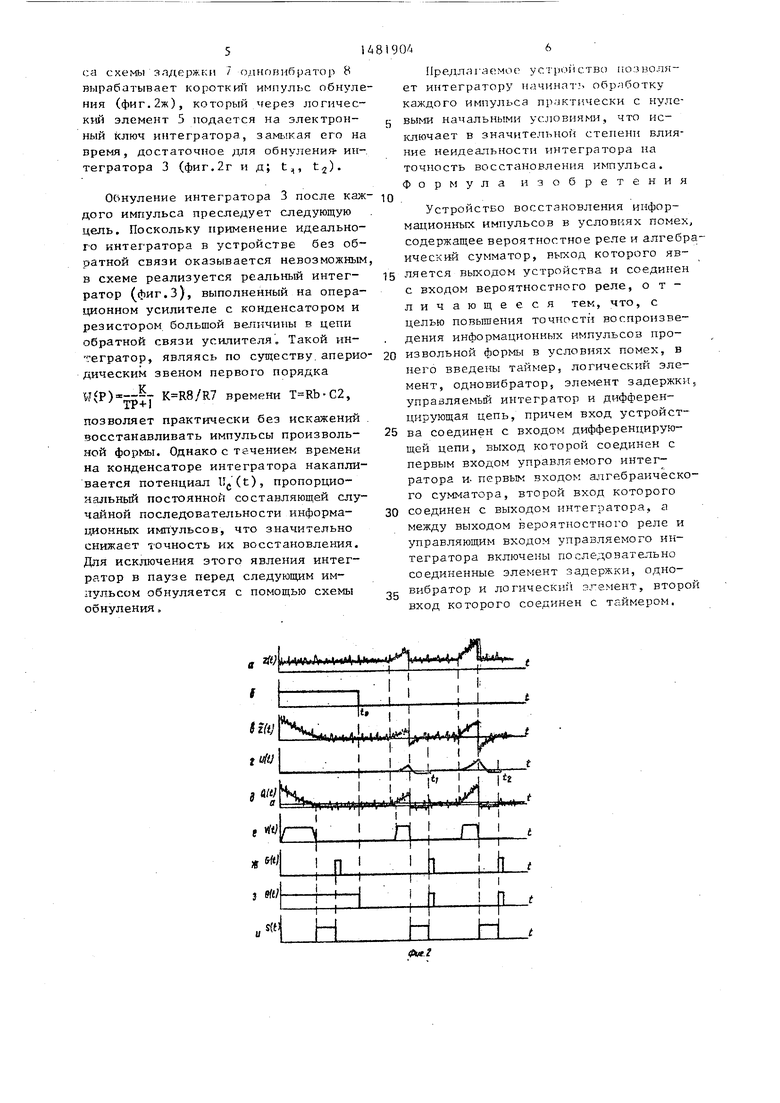

На фиг.1 приведена функциональная схема устройства; на фиг о 2 - временные диаграммы, поясняющие работу устройства; на фиг.З - техни- ческая реализация устройства.

Устройство восстановления информационных импульсов в условиях помех содержит дифференцирующую цепь (ДЦ) 1, алгебраический сумматор 2, интег- 3, таймер 4, логический элемент 5, вероятностное реле (ВР) 6, элемент 7 задержки, одновибратор 8

Устройство работает следующим образом.

В начальный момент времени Ј/5-0 при включении устройства на его .входе действует смесь низкочастотной (НЧ) и высокочастотной (ВЧ) помех (фиГо2а). На выходе таймера 4 уста- навливается уровень логической (фиг.26), который через логический элемент 5, реализующий логическую функцию 2 ИЛИ, воздействует на ключе ёой элемент интегратора 3 (фиг.З), переводя его в замкнутое состояние. Замкнутый ключ шунтирует собой накопительный конденсатор интегратора 3. При этом выходной сигнал интегратора (фиг„2г), поступающий на второй вход сумматора 2 близок к нулю (t 6(0,t0) На первый вход сумматора поступает сигнал с ДЦ 1, представляющий собой реакцию данной цепи на НЧ помеху (фиг.2в)о Этот сигнал передается на выход устройства (фиг.2д). Логичес™ кая 1 таймера 4 до момента времени tD удерживает ключ интегратора 3 в замкнутом состоянии независимо oi

состояния блоков 6-8 (фиг.2г -и).

t

В момент времени t0, выбранный таким образом, чтобы к этому моменту переходный процесс, вызванный действием медленноменяющейся помехи, был практически закончен (фиг.2в), на выходе таймера 4 устанавливается уровень логического О, не изменяющийся в течение всей дальнейшей paбеты (фиг.2б), На выходе устройства действует ВЧ-помеха Q(t) J- (t), которую практически без искажения пропускает ДЦ. ВР 6, представляющее собой помехозащищенньгй репейный эле- - мент, не реагирует на ВЧ-помеху и находится в состоянии логического О, V(t)0 (фиг.2е). Элемент 7 задержки, формирующий прямоугольный импуль по заднему фронту выходного сигнала ВР, также находится в состоянии О. В этом же состоянии находится одно- вибратор 8о В результате логический элемент 5 переходит в состояние О (фиг.2е - и). Это приводит к размыканию ключевого элемента интегратора 3 и включению последнего в работу о Устройство приходит в рабочее состояние. Поскольку на вход интегратора 4 воздействует центрированная ВЧ-поме- ха, его выходное напряжение близко к нулю и на выходе устройства (Xt) ).

При поступлении на вход устройства информационного импульса x(t) (фиг.2а, в качестве примера приведены импульсы треугольной формы) ДЦ значительно искажает его форму (фиг02в). Этот искаженный сигнал поступает на входы сумматора 2 и интегратора 3, которьй интегрирует его (фиг„2г), В результате суммирования выходных сигналов ДЦ 1 и интегратора 3 в сумматоре 2 осуществляется восстановление входного импульса (фиг.2д)0 Таким образом, на выходе устройства действуют восстановительный импульс x(t) и ВЧ-помеха (t).

Как только значение полезного сигнала на выходе устройства становится больше порога а срабатывания ВР x(t) а (фиг.2д), ВР переходит в состояние W(t) 1 (фиг.2е)„ При этом состояния блоков 7 и 8, которые совместно с ВР 6 образуют схему обнуления интегратора 3, не изменяются (фиг.2ж,з и и). Когда значение восстановительного импульса становится меньше а , т.е. x(t)Јfl, ВР переходит в состояние V(t)0 (фйг.2е). По заднему фронту выходного импульса ВР 6 схема задержки 7 формирует прямоугольный импульс, длительность которого выбирается с учетом минимальной длительности паузы между ин формациоиными импульсами (фиг.2и). По заднему фрочт г выходного импуль51

са схемы задержки 7 олновнбратор 8 вырабатывает коротки импульс обнуления (фиг.2ж), который через логический элемент 5 подается на электронный ключ интегратора, замыкая его на время, достаточное для обнуления- ин).

тегратора 3 (фиг.2г ид; t.,, t2

Обнуление интегратора 3 после каждого импульса преследует следующую цель. Поскольку применение идеального интегратора в устройстве без обратной связи оказывается невозможным в схеме реализуется реальный интегратор (фиг.З), выполненный на операционном усилителе с конденсатором и резистором большой величины в цепи обратной связи усилителя. Такой интегратор, являясь по существу апериодическим звеном первого порядка

W(P)|y K R8/R7 времени T Rb-C2,

позволяет практически без искажений восстанавливать импульсы произвольной формы. Однако с течением времени на конденсаторе интегратора накапливается потенциал Uc(t), пропорциональный постоянной составляющей случайной последовательности информационных импульсов, что значительно снижает точность их восстановления. Для исключения этого явления интегратор в паузе перед следующим импульсом обнуляется с помощью схемы обнуления,

zft

А,ицлЛм. )уц4-м иЦ - t

ЗДГЧЧц.,,и1.и.миИ

гМ

sit

Предлагаемое устройство позволяет интегратору начинать обработку каждого импульса практически с нулевыми начальными условиями, что исключает в значительной степени влияние неидеальности интегратора на точность восстановления импульса. Формула изобретения

5

0

5

Устройство восстановления информационных импульсов в условиях помех, содержащее вероятностное реле и алгебраический сумматор, выход которого является выходом устройства и соединен с входом вероятностного реле, отличающееся тем, что, с целью повышения точности воспроизведения информационных импульсов про- 0 извольной формы в условиях помех, в него введены таймер, логический элемент, одновибратор, элемент задержки,, управляемый интегратор и дифференцирующая цепь, причем вход устройства соединен с входом дифференцирующей цепи, выход которой соединен с первым входом управляемого интегратора и- первым входом алгебраического сумматора, второй вход которого соединен с выходом интегратора, а между выходом вероятностного реле и управляющим входом управляемого интегратора включены последовательно соединенные элемент задержки, одно- вибратор и логически; темент, второй вход которого соединен с таймером.

5

«Вход

т

fuxfS

SipMOf- юсттн тле

т

58

т

| Оксман А.К | |||

| Передача телевизионных сигналов по коаксиальным кабелям | |||

| - М„: Связь, 1966, с.200 | |||

| Устройство выделения информационных импульсов при наличии помех | 1980 |

|

SU930697A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-05-23—Публикация

1987-08-05—Подача