Изобретение относится к средствам преобразования формы представления информации и может быть использовано в системах передачи и обработки непрерывных изменяющихся в большом диапазоне сигналов для преобразования этих сигналов в двоичный код в условиях воздействия низкочастотной и высокочастотной помех.

Цель изобретения - повышение точности преобразователя.

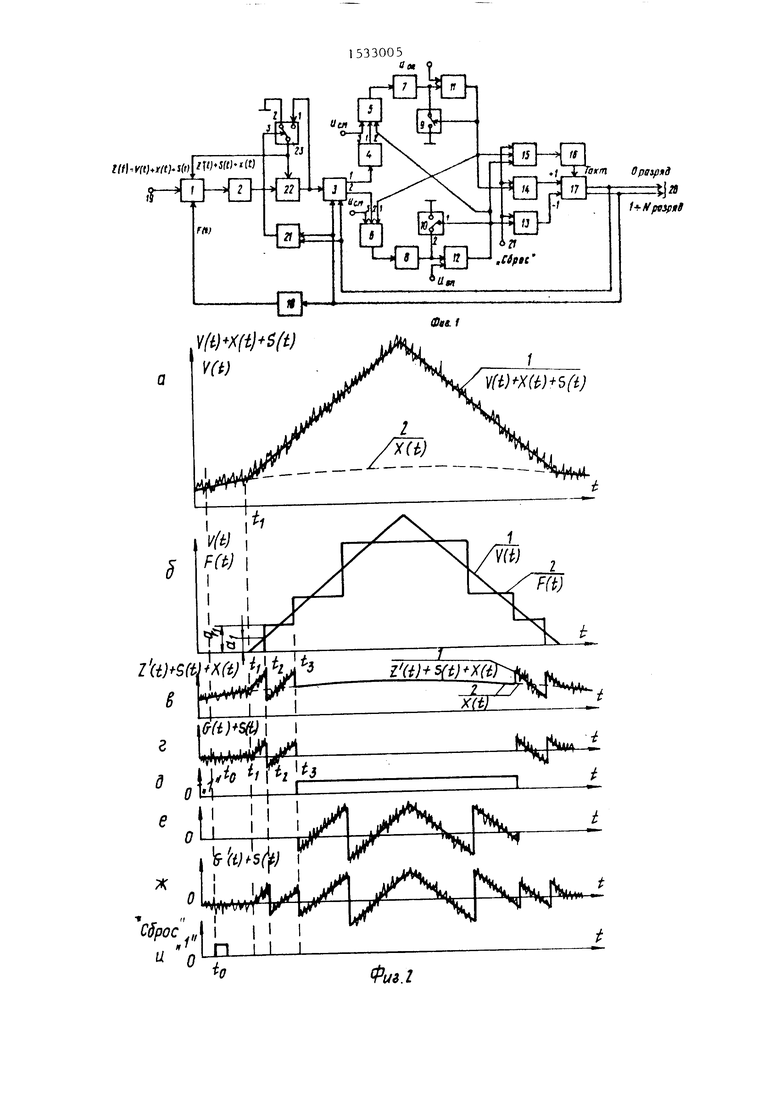

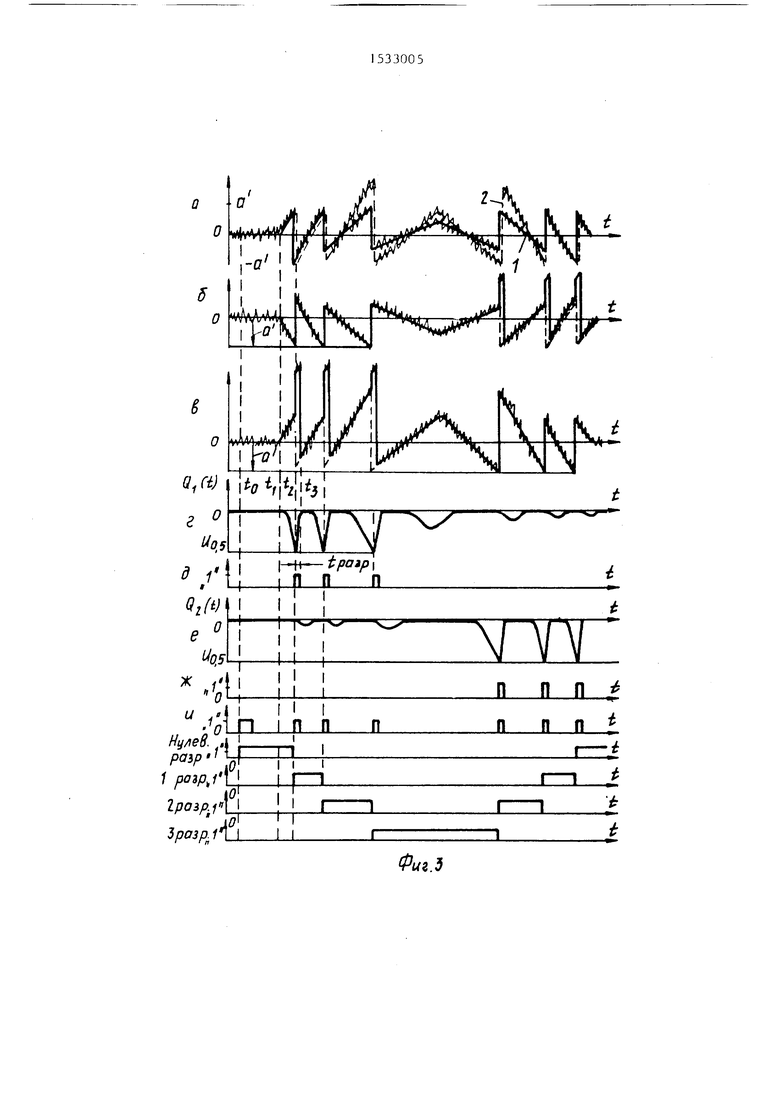

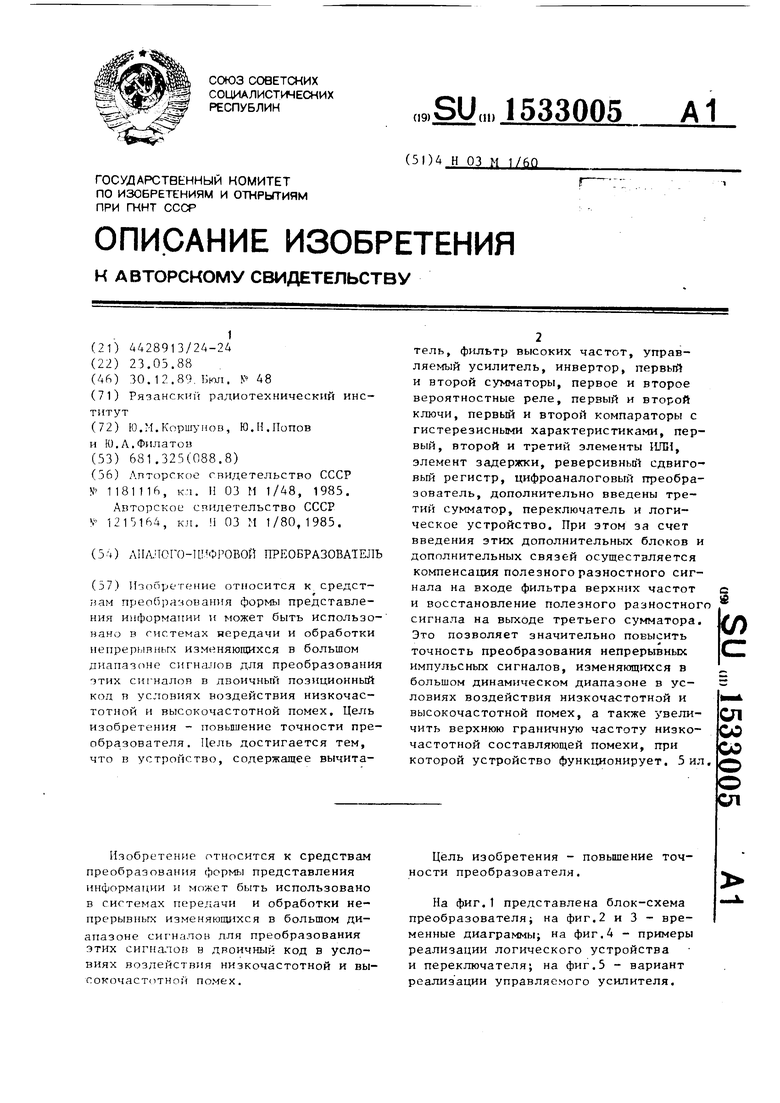

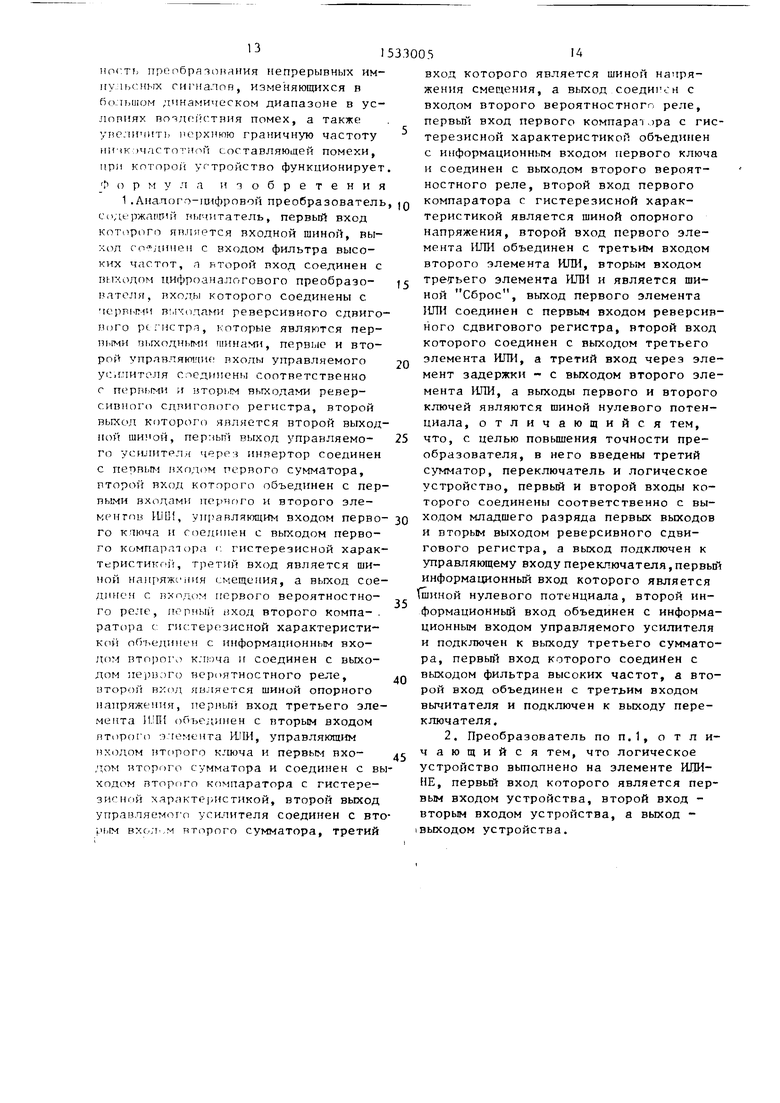

На фиг.1 представлена блок-схема преобразователя; на фиг.2 и 3 - временные диаграммы; на фиг.4 - примеры реализации логического устройства и переключателя; на фиг.5 - вариант реализации управляемого усилителя.

Преобразователь (фиг.1) состоит из нычнтателя 1, фильтра 2 высоких частот, управляемого усилителя 3, инвертора 4, сумматоров 5 и 6, вероятностных реле 7 и 8, ключей 9 и 10, компараторов 11 и 12 с гистереэисной характеристикой, элементов ИЛИ 13-15, элемента 16 задержки, реверсивного сдвигового регистра 17, цифроаналого- вого преобразователя (ЦАП) 18, входной тины 19 , (N+1)-разрядной выходной тины 20, логического устройства 21,

сумматора

переключателя 23.

выполненного на операционном усилителе 27, с одним входом цифровой регулировки усиления, а также логического устройства. Выход второго каскада является первым выходом управляемого усилителя, а выход третьего к асьала - вторым выходом. Коэффициенты пергцачи по первому и второму выходам изменяются в зависимости от выходного кода согласно таблице 1 . )то достигается изменением состояния ключей 28-32, выполненных на полевых транзисторах, и соотношением резисторов 33-49. Клю

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1983 |

|

SU1215164A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1640823A1 |

| Устройство для аналого-цифрового преобразования импульсных сигналов | 1987 |

|

SU1564725A1 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство выделения полезного сигнала | 1984 |

|

SU1236398A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство выделения информационных импульсов с фиксированной амплитудой на фоне узкополосной помехи | 1979 |

|

SU896765A1 |

| Цифровой согласованный фильтр | 1986 |

|

SU1406740A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

Изобретение относится к средствам преобразования формы представления информации и может быть использовано в системах передачи и обработки непрерывных изменяющихся в большом диапазоне сигналов для преобразования этих сигналов в двоичный позиционный код в условиях воздействия низкочастотной и высокочастотной помех. Цель изобретения - повышение точности преобразователя. Цель достигается тем, что в устройство, содержащее вычитатель, фильтр высоких частот, управляемый усилитель, инвертор, первый и второй сумматоры, первое и второе вероятностные реле, первый и второй ключи, первый и второй компараторы с гистерезисными характеристиками, первый, второй и третий элементы ИЛИ, элемент задержки, реверсивный сдвиговый регистр, цифроаналоговый преобразователь, дополнительно введены третий сумматор, переключатель и логическое устройство. При этом за счет введения этих дополнительных блоков и дополнительных связей осуществляется компенсация полезного разностного сигнала на входе фильтра верхних частот и восстановление полезного разностного сигнала на выходе третьего сумматора. Это позволяет значительно повысить точность преобразования непрерывных импульсных сигналов, изменяющихся в большом динамическом диапазоне в условиях воздействия низкочастотной и высокочастотной помех, а также увеличить верхнюю граничную частоту низкочастотной составляющей помехи, при которой устройство функционирует. 5 ил.

Логическое устройство 21 может быть|г чи 28-32 замыкаются

выполнено на элементе ИЛИ-НЕ 24 (фиг.4), переключатель 23 - на коммутаторе 590 КПЗ.

на их управляющие вх нала, а размыкаются сигнала Г1. Требуем чей 28-32 в зависимо

Коэффициенты передачи управляемого усилителя 3 по первому и второму выходам выбраны из условий обеспечения постоянной относительной погрешности преобразования во всем диапазоне изменения сигнала. Зависимости коэффициентов К, и К2 передачи управляемого усилителя 3 соответственно по первому и второму выходам от кода, записанного на выходе реверсивного сдвигового регистра 17, приведены в таблице, причем младший разряд реверсивного сдвигового регистра не является инпри ih с i уши.нии

на их управляющие входы iiyienoi о сигнала, а размыкаются при ш« чупче.ши сигнала Г1. Требуемые (оет.яния ключей 28-32 в зависимости от коця oOoe 0

5

формационным, его назовем нучевь м, поскольку в него предваритепьно записывается 1. Эта 1 хранится в нулевом разряде при отсутствии полезного сигнала. Информационными являются N старших разрядов из (N-H) разрядов реверсивного сдвигового регистра, соответственно разряды кода с выхода этого регистра назовем младший - нулевым, а N старших - инЛормациош ы ми. Выходы N старших информационных разрядов реверсивного сдвигового регистра назовем первыми ныхмдными шинами, а выход его нулевого разряда - второй выходной шиной.

Значение максимального коэффициента передачи Кимнуправляемого усилителя 3 зависит от величины кванта преобразования q i первого младшего разряда ЦАП 18 и уровня срабатывания вероятностных реле 7 и 8 а и а при

выбранных

п

соответственно порогах

/2,

-q 12.

т.е.

1

о

-- 2

а 7 q,.

В этом случае максимальный коэффициент усиления Гма„е управляемого определяется выражением MC,V - К . Состояние 3 каждого ключа обозначает Замкнут, а состояние Р Разомкнут. Логичес- мч устройство управляемого усилителя, число каскадов и изменение коэффициентов передачи отдельных каскадов в зависимости от кода может быть

усилителя

.. i

30

35

40

различным, но общие коэффициенты усн- 25 го коэффициента усиления как по первому, так и по второму выходам, на выходе логического устройства 21 сформирован сигнал О (фиг.2д). Под действием О, поступающего на первый управляющий вход переключателя 23 с выхода логического устройства 21, он открыт по второму входу и закрыт по первому входу, при этом на его выходе устанавливается нулевой потенциал. После окончания импульса Сброс (фиг.2и) при нулевом полезном сигнале на входе устройства (фиг.26, ломаная 1) и наличии только низкочастотной помехи X(t) и высокочастотной помехи S(t) (фиг.2а) на выходах компаратора 11 (фиг.Зд), компаратора 12 (фиг.Зж), на выходах элементов Ш1И 13-15 (фиг.Зи) и на выходе элемента 16 задержки формируются сигналы О, близких к нулевому потенциалу. Ключи 9 и 10 разомкнуты, причем помехи проходят на выход вычитателя 1 (фиг.2в). Фильтр подавляет низкочастотную помеху X(t) и пропускает практически без изменений высокочатотную помеху S(t) (фиг.2г), которая проходит через сумматор 22 на вход управляемого усилителя 3 (фиг.2ж). Усиленная с максимальным коэффициентом усиления помеха S(t) поступает (фиг.За) через инвертор А на первый вход сумматора 5 и на второй вход сумматора 6 (фиг.За). На второй вход сумматора 5 и первый вход сумматора 6 поотнетстшш с таблицей.

На фиг.2а ломаной 1 изображен входной сигнал Z(tJ , представляющий собой аддитивную смесь полезного сигнала V(tJ, низкочастотной помехи X(t) и высокочастотной помехи S(t), кривой 2 изображена низкочастотная помеха X(t). На фиг.26 ломаной 1 представлен входной полезный сигнал V(t), криво 2 - сигнал F(t) с выхода ПАП 18. На фиг.2в изображен сигнал с выход, пычитат еля 1 , ломаной 1 - аддитивная смесь полезного разностного сигнала Z (t), ВЧ-помехи S(t) и НЧ-помехи X ( L ), кривой 2 - НЧ - помеха X(l). На фиг.2г представлен сигнал на выходе фильтра, на фиг.2д- сигнач на иы::оде логического устрой-

с 1 в Л

11

на сриг.-е - сигнал на выходе

перекнючателч 23, на фиг.2ж - сигнал на выходе сумматора 22. Сигнал Сброс изображен на фиг.2и.

На фиг.За ломаной 1 изображен сигнал с первого выхода управляемого усилителя 3, а ломаной 2 - сигнал с его второго выхода. На фиг.36 представлен сигнал нл выходе сумматора 5, на фиг.Зи - сигнал на выходе сумматора 6. На фиг.Зг изображен сигнал с выхода пер ятнпстного реле 7,на фиг.Зд - импульсы с выхода компаратора 11, на ФИГ.ЗР,Ж - соответственно сигналы с ных.да блоков 8 и 12.

45

50

55

0

5

0

На фиг.Зи изображены импульсы с выхода элемента ИЛИ 15, на фнг.Зк - сигналы на выходе реверсивного сдвигового регистра 17.

Преобразователь работа ; следующим образом.

В исходном состоянии реверсивный сдвиговый регистр 17 сигналом Сброс (фиг.2и), поступившим в момент t0 с шины Сброс, приводится в начальное состояние, при этом записывается 1 в его нулевой (младший) разряд, а в остальные - О (фиг.Зк). При этом наличие 1 в нулевом разряде соответствует нулевому полезному сигналу V(t) на выходе вычитателя 1 (фиг.2б, ломаная 1), нулевым потенциалам на выходах ЦАП 18 и переключателя 23. Под действием полученного (N-H)-разрядного кода на выходе ЦАП 18 устанавливается нулевой потенциал (фиг.26, ломаная 2), управляемый усилитель 3 приводится в состояние максимально30

25

35

25

40

25

25

45

25

50

25

55

ступают потенциалы О с выходов соответственно компараторов 12 и 11. На третьи входы сумматоров 5 и 6 подается напряжение смещения Ucw , необходимое для обеспечения работы вероятного реле 8 на сигналы отрицательной полярности, а также для обеспечения работы вероятностного реле 7 на сигналы положительной полярности.Для

этой цели, а также для того тобы применить одинаковые вероятностные реле, используется инвертор 4. Сигналы с выходов сумматора 5 (фиг.36) и сумматора 6 (фнг.Зв) поступают соответственно на входы вероятностных реле 7 и 8. Вероятностное реле 7 определяет положение входного сигнала по отношению к положительному порогу л к„акс Я/2, где Кмак- максимальный коэффициент усиления управляемого усилителя 3, п - величина кванта преобразования на первом шаге. Вероятностное реле 8 определяет положение сит па на его входе по отно- шению к отрицательному порогу - а - v 0/2. При этом на выходах вепла КС- 1

роятностного реле 7 (фиг.Зг) и вероятностного реле 8 (фиг.Зе) формируют

ности пребывания входного сигнала соответственно выше положительного порога а и ниже отрицательного порога -а1. Вероятность пребывания усиленной с максимальным коэффициентом

усиления К помехи S(t) выше кс

ложительного порога а близка к нулю, поэтому на выходе вероятностного реле 7 формируется потенциал, близкий к нулю (фиг.Зг). Аналогично на выходе вероятностного реле 8 формируется такой же потенциал (фиг.Зе). На вторые входы компараторов 11 и 12 подается опорное напряжение Uon, необходимое для обеспечения нужных режимов работы компараторов. Поскольку на входы компараторов 11 и 12 поступают сигналы, близкие к нулю и не превосходящие первых уровней их срабатывания U05 (фиг.3г,е), то они не изменяют своего состояния и на их выходах остаются сформированные сигналы О (фиг.Зд.ж).

При поступлении на вход устройства в момент t. полезного сигнала

по- 55

ложительнон полярности V(t) с нало женной на него низкочастотной помехой X(t) и высокочастотной помехой S(t) (фиг.2а, ломаная 1) фильтр 2 верхних

0

5

0

0

5

0

5

0

5

частот подавляет низкочастотную помеху X(t) и пропускает практически без искажений полезный сигнал V(t) и высокочастотную помету S(t) (фиг.2г) через сумматор 22 на вход.управляемого усилителя 3 (фиг.2ж). Сигнал V(t) и полезный разностный сигнал Z (t) V(t)-F(t), который формируется на выходе вычитателя 1 (Фиг.2в), идентичны, так как сигнал F(t), поступающий с выхода ЦАП 18 на второй, и сигнал, поступающий с выхода переключателя 23 на третий импортирующие входы вычитатели 1, равны нупю (фиг.2б, ломаная 2, фиг.2е). Аналогично сигнал G(t,) , поступающий с выхода фильтра 2 на вход гуммато-- ра 22 (фиг.2г), и сигнал r (t) с выхода сумматора 22 (фиг.2ж) идентичны, поскольку на другой вход сумматора 22 поступает нученой потенциал с выхода переключателя 23. Искажения полезного гигнача (t) фильтром 2 верхних частот незначительны и ими можно пренебречь. Однаг-о для наглядности сигнал 0(t) (фш.2г) на выходе фильтра и гиг на i ( (t) na выходе сумматора 22 изоГрллечы отличающимися от сигналов ча входе устройства и Z (t) на выходе вычитателя 1 (фиг.2в). Vrц к иная с коэффициентом усиления К „„, лп.гитивн)н

М i к

смесь полезного сигн,1 ia vT(r; и высокочастотной S(t) помехи (фш . 5а. ломаная 2) поступает на второй вход сумматора 6, на первый вход которого поступает О с выхода комгтар ITP- ра 11, а на третий i гупаеч напряжение смещения 1 rw . Версия i нпг-ь пребывания сигнала пололи тепьноп полярности на входи версия г not т ног реле 8 ниже порога отрицав п ной полярности - а (фиг. Зц4 о титкл к НУЛЮ, поэтому вероятностное ре к 8 не изменяет своего состояния и i ei о выхода на вход компаратора 12 сигнал Q2(t), близкий по CHOTMV значению к нулю (фиг.Зе). Компаратор 2 также не изменяет своего (остояния, на его выходе остается сш нал О (фиг.Зж). Усиленная коэффициентом аддитивная смесь полевого сигнала V(t) и высокочастотной помехи S(t) (фиг.За, ломаная 1) поступает на первый вход сумматора 5, на нто- рой вход которого поступает О с- выхода компаратора 12, а на третий вход поступает напряжение смещения l Crv.Bep HI --с гъ npt лития гигна la пси ожиii к и ITO гярн с ти нюне положитечь- Hfт п poiт i возрэстает с нараста- нт 1 и U( it inoi о сигнала (фш.За, ло- М1Ч11 1), ни юму сигна i О,(U на ни i i т ьч 7 отрицательной потярноо и, т i pi MI и иптчыи этой вероятности

- но ( п по ( ноем ябсопютно- 1 in пицц (Jin1-. Зг ) . Временная диаг- i MI i t i ч1«г иньс-нтирования поле з i1 т i i i i не сигналя / (t) г н i- | f и i n 1Л( тотной гоме ой (. L I-1 i ii tf i ооятностного реле 7 1рпн ill 11 J 11 , 36 . Как т г гько CHI - н i г о i 4i рочтностнг о реле 7

l HI

Г 1 НЯ Г

( Y )МП 1

L

i С 1МЯ

гн 0,5

г. . -и 11

с

соответствую (фнг. Зг) , на HI I-

П MOMt. HT t ; ПО i т г- , , i „ 1 . Зд) . Эют i i г к i нт. управ яющий вхот, | i H( pi м вхг сумматор-) 6,

и мг нта 111И 1 А и на пс MI па ИТИ 15, а также

MIT pentprИВНО1О ГДВНipi 17. Ключ 9 замыкает- , t) с вероят1 i)l МИ В ) Ж НХП 1 В ОД Г I i

о 1 in

,1 ИГ ч

Т1

и 11

п )Г PS it спадчст со чнтчения, i HiKio 1 ер1ятчостн 0,5 до j i t , с кп t re iuyromeio псроятнос- ivit )И . ), та время t i , orojjot оО словлено чнутрен- и t пр( i и1 t i пои ключа 9, В момент 1 ил ITTin гиг па Q (t) ня выхоi iu р т лс о ретс 7 (фй.3г) i -1 т ) г р 11 . i 1бчтмвает i на его в о к с} 01 чип1 t гея сигнал О. Таим м, н) впходе компаратора 11 фо мил1 РТС i импг1ьс, Kc-TopiM nocTVna- т ii i терими н о сумматора 6, бчо- тор ir т . тнос репе 8 на врьмя

) uponf т и р ятностного реле 8 не - i дчмл j. i t rrio, чтобы избежать его ж/-HOI с р in jTi тания в момент эа- п id нтв г i i 4t ния вилодного кода, кт n ri п )ньн tiirna.ii нарастает, Ре- ( I in ц л ( т овий рпистр 17 пере- i IHT я m Хранение в режим пи и что, т.е. происходи сдвиг н ioi j ipnni разрядов, передним ( м и t i пса, поступающего с выма коми т 11 (фиг.Зд) через i и мс- IT И1 И 1 i на его вход сложения, п i н ii MI им i ия реверсивного сдви Hoi i pi i и тр i 17 при этом поступает н i i i i к мпараторч 12 (фиг.Зж) ч pv э i, ц МИ 13. Передний фронт |мтг,лтст с п i n компаратора 11 по

0

5

0

5

0

5

0

5

0

5

также череч элемент И.1 15 на вход элемента 16 задержки iде задерживается на время t, . .держка элементом 16 зад(жки на время г;гс|дневелика, но необх ,4има для надежного обеспечения нежима Сдвиг вправо реверсивног сдвигового регистра 17 н MOMtнт ппнхода перелне- го фронта ИМПУЛЬСЭ с выхода лемен- та 16 задержки на третий (тактоьый) вхсм регистра 17. С пр гходом в момент t , пепедне о фронта импутьса с выхода элемента 16 задержки на третий (тактовый) вхол реверсивного сдвигового регистра 17 на его (N+1)-разрядном выходе 20 происходит сдвиг 1 на один разряд в сторону старших разрядов. В данном сп}чае осуществляется сдвиг 1 из нулевого разряда в первый разряд (фиг.ЗьЛ. Полученный (N+1)-разрядный позиционный коц с лзыхода реверсивного сдвигового регнст- pi 17 поступает на соответствующие управгяющие входы управляемого уси- титепя 3. Код, образованный N старшими разрядами реверсивного сдвигового регистпа 17, поступает на соот- BCTCTrfVtoinnf входы N-ртзрядього ЦАП 18. В о ттпетстгши с записанным на вы-ч де PI. чс ргивного сдвигового регистра 17 коэффициент усиления управтяемо- 1 о ус нлителя 3 по первому н по второ- м выходам изменяется согласно приведенной в табпице зависимости, а на выходе 1{АП 18 формируется потенциал T(t), которьп поступает на второй инвертирующий вход вычитателя 1 (фиг.26, поманая 2). Hi выходе вычнтателя 1 формируете разностный CHI нал 7 (t) ) - F (t) с наложенной на него ни коччстстной noNie ой X(t) и высокочастотной помехой S(r), который поступает на вход фильтра 2 верхних частот (фиг.2в). С окончанием тактового им- uvтьса с выхода элемента ИЛИ 15 (фиг.Зи), задержанного на время Сза( элементом 16 задержки, заканчивается первь такт.

Если входной сигнал V(t) (фиг.26, юманая 1) продолжает нарастать, то нарастает и разностный сигнал Z (t) (фиг.2в), тогда весь цикл работы устройства повторяется. Отличие второго такта и последующих от первого заключается лишь в том, что в конце второго такта, кактоаько на выходе реверсивного сдвигового регистра 1 7 осуществится

сдвиг i из первого во второй разряд в момент t э , на выходе логического устройства 21 появляется Г (Лиг.2д). Под воздействием 1, поступающей на управляющий вход переключателя 23, он размыкается по второму входу и замыкается по первому входу, при этом подключает выход сумматора 22 к

10

сигналом с выхода вероятностного реле 8 уровня U

о,Ч,

его второму входу и третьему (инверти-п ной величине (фиг.Зе). При достижении рующему) входу вычитателя 1. На выходе переключателя 23 формируется сигнал G (t), искаженный высокочастотной помехой S(tJ (фнг.2е). На второй (инвертирующий) вход вычитателя 1 поступает сигнал F(t) с выхода ЦАП 18, соответствующий новому значению кода. Таким образом, на выходе вычитате15

соо гнететвующего

вероятности 0,5, на выходе компаратора 12 формируется сигнал Г1 (фиг.Зж). В этом случае устройство работает так же, как при нарастании сигнала V(t) на входе устройства, только паботэет цепочка, в состав которой входят следующие элементы: сумматор ft, вероятностное реле 8, ключ 10, компаратор 12, элемент ИЛИ 13, вместо пеппчги, образованной инвертором 4, сумматором 5, вероятностным реле 7, ключом 9, компаратором 11 и элементом ИЛИ 14, а сдвиг 1, записанной в очном и- разрядов реверсивного сдвиг иного регистра 17, осуществляется па один разряд влево, т.е. н сторону младших разрядов. ГА л и 1 записана в одном

ля 1 с момента t э формируется сигнал

мента

матора 2.Z,

тому, что с

постный

мехами.

момента t.

г

уже не сам раз- сигнал Z (t), искаженный по- поступает с выхода вычитателя 1 на вход фильтра 2, где подвергается искажению, а на вход фильтра поступает сигнал, близкий нулю, а также низкочастотная помеха X(t) (фиг.2в).

Если разностный сигнал Z (t) на выходе сумматора 22 спадает (фиг.ж), т.е. спадает сигнал V(t) (фиг.2б, ломаная 1), то соответственно спадают сигналы на первом и втором выходах управляемого усилителя 3 (фиг.За). Вероятность пребывания сигнала с первого выхода управляемого усилителя 3 (фиг.За, ломаная 1) выше положительного порога а1. уменьшается, поэтому сигнал Q ,(t) на выходе вероятностного реле 7, пропорциональный этой вероятности, уменьшается по абсолютной величине до нуля

(фнг.Зг). Вероятность пребывания сигнала отрицательной полярности г второго выхода управляемого усилителя 3 (фиг.За, ломаная 2) ниже отрицательного порога - а увеличивается, а следовательно, сигнал Q(t:) с выхода вероятностного реле 8, пропорциональный

этой вероятности, растет

абсолют-

сигналом с выхода вероятностного реле 8 уровня U

о,Ч,

ной величине (фиг.Зе). При достижении

из Разрядов

соо гнететвующего

вероятности 0,5, на выходе компаратора 12 формируется сигнал Г1 (фиг.Зж). В этом случае устройство работает так же, как при нарастании сигнала V(t) на входе устройства, только паботэет цепочка, в состав которой входят следующие элементы: сумматор ft, вероятностное реле 8, ключ 10, компаратор 12, элемент ИЛИ 13, вместо пеппчги, образованной инвертором 4, сумматором 5, вероятностным реле 7, ключом 9, компаратором 11 и элементом ИЛИ 14, а сдвиг 1, записанной в очном и- разрядов реверсивного сдвиг иного регистра 17, осуществляется па один разряд влево, т.е. н сторону младших разрядов. ГА л и 1 записана в одном

кода на выходе- рен рейв - ного сдвигового регистра 17 старше первого разряда, то нч выходе отческого устройства 21 мсчаегся си - нал 1, поступающий на управляют in вход переключателя 2ч, который закрыт по второму входу н открыт по пс-i j ,12

мм,ч т on ч

му входу, при этом выход подключен к его второму BXOJLV,-и к третьему (инверсному) входу вычитателя 1 Если 1 записана в перш in или нуп«- вой разряд реверсинног 1 слын регистра 17, то на выАсде инчческо- го устройства 21 формирует с и О, под действием которого iiepeiui} ч.ггель 23 закрывается по первому х, и открывается по второму вход}, при этом на второй вход сумматора 22 и тритий1 (инверсный) вход вычигжет 1 поступает нулевой потенциал.

Таким образом, благодаря дополнительных блоков и связен, осуществляющих компенсацию центральных импульсов полезного рашостнгго сигнала Z (t) V(tJ - 1() на nxo- де фильтра 2, восстановление полезного разностного сигнала Z (t) на выходе сумматора 22, предиагаемыи преобразователь позволяет по сравнение с известным значптч п,о поньн гт ь i оч13

преобразования непрерывных им- и 1ь ных снгнатов, изменяющихся в da тьшом динамическом диапазоне в условиях воздействия помех, а также vne шчнть верхнюю граничную частоту ни ж часто т11 п составляющей помехи, при которой vrтройство функционирует. Формула и т о б р е т е н и я

15

35

теристикой является шиной опорного напряжения, второй вход первого эле мента ИЛИ объединен с третьим входо второго элемента ИЛИ, вторым входом третьего элемента ИЛИ и является ши ной Сброс, выход первого элемента ИЛИ соединен с первым входом реверс ного сдвигового регистра, второй вх которого соединен с выходом третьег элемента ИЛИ, а третий вход через э мент задержки - с выходом второго э мента ИЛИ, а выходы первого и второ ключей являются шиной нулевого поте циала, отличающийся тем, что, с целью повышения точности пре образователя, в него введены третий сумматор, переключатель и логическо устройство, первый и второй входы к торого соединены соответственно с в ходом младшего разряда первых выход и вторым выходом реверсивного сдвигового регистра, а выход подключен управляющему входу переключателя, пер информационный вход которого являет

{шиной нулевого потенциала, второй и формационный вход объединен с инфор ционным входом управляемого усилите и подключен к выходу третьего сумма ра, первый вход которого соединен с выходом фильтра высоких частот, а в рой вход объединен с третьим входом вычитателя и подключен к выходу пер ключателя.

1533005

14

вход которого является шиной напряжения смещения, а выход соедигсн с входом второго вероятностного реле, первый вход первого компарат ipa с гис- терезиснон характеристикой объединен с информационным входом первого ключа и соединен с выходом второго вероятностного реле, второй вход первого

Q компаратора с гистерезисной харак50 5 0 Q $

5

теристикой является шиной опорного напряжения, второй вход первого элемента ИЛИ объединен с третьим входом второго элемента ИЛИ, вторым входом третьего элемента ИЛИ и является шиной Сброс, выход первого элемента ИЛИ соединен с первым входом реверсивного сдвигового регистра, второй вход которого соединен с выходом третьего элемента ИЛИ, а третий вход через элемент задержки - с выходом второго элемента ИЛИ, а выходы первого и второго ключей являются шиной нулевого потенциала, отличающийся тем, что, с целью повышения точности преобразователя, в него введены третий сумматор, переключатель и логическое устройство, первый и второй входы которого соединены соответственно с выходом младшего разряда первых выходов и вторым выходом реверсивного сдвигового регистра, а выход подключен к управляющему входу переключателя, первый информационный вход которого является

{шиной нулевого потенциала, второй информационный вход объединен с информационным входом управляемого усилителя и подключен к выходу третьего сумматора, первый вход которого соединен с выходом фильтра высоких частот, а второй вход объединен с третьим входом вычитателя и подключен к выходу переключателя.

ltt}--V(t)+r(t)t(n

V(№(il+$ft) Vft)

I,. .

ff

Ж

cSpoc Л i ||i , to

Им

1+tfptWt

ФвИ

1

V(i)+X(t)+Sft)

/

Фиг.г

If

1 Р«А/ П

w

2p03f.

Зрозрп

Фиг.Ъ

if ВыхоОд суппотора 13

ШЛЕ1

PffSptff

входного

ntt

.О разряд

f-epsapfd

56

Редактор А.Огар

Физ.5

Составитель В.Махнанов

Техред М.Ходанич Корректор Н.Король

590 КПЗ

U

JL

ll

1Л 2А 3t

kR

18 2В 3В

4Д

не 8ni сутатвре О и Иынислитем f

U- В

8 8м.

Г

а

0bt4

fit

1 бы ход

2быход

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1215164A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-23—Подача