&

Јь

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1533005A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1215164A1 |

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для интегрирования | 1983 |

|

SU1108470A1 |

| Устройство для определения моментов экстремумов гармонических сигналов | 1981 |

|

SU1004899A1 |

| Устройство для вычисления параметров нелинейных колебательных систем | 1985 |

|

SU1302243A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Устройство для управления синусоидальными вибрациями | 1985 |

|

SU1269112A1 |

| Устройство для управления преобразователем | 1985 |

|

SU1246300A1 |

Изобретение относится к средствам преобразования информации и может быть использовано в системах передачи и обработки непрерывных изменяющихся сигналов в двоичный позиционный код в условиях воздействия низкочастотной и высокочастотной помех. Цель изобретения - повышение точности преобразования непрерывных сигналов, существенно изменяющихся в процессе преобразования в код в условиях воздействия низкочастотной и высокочастотной помех, Цель достигается тем, что в устройство, содержащее вычитатель, фильтр верхних частот, инвертор, два сумматора, два вероятностных реле, два ключа, два компаратора с гистерезисными характеристиками, цифроаналоговый преобразователь, реверсивный счетчик, введены два инвертора, два переключателя и блок управления. За счет введения этих дополнительных блоков и дополнительных связей осуществляется изменение порогов срабатывания релейных элементов устройства, что приводит к компенсации искажающего воздействия на полезный сигнал фильтра верхних частот. Это позволяет повысить точность преобразования непрерывных импульсных сигналов в условиях воздействия низкочастотной и высоко- частотной помех. 1 з.п. ф-лы, 5 ил. (Л

Изобретение относится к средствам преобразования формы представления информации и может быть использовано в системах передачи и обработки информации для преобразования непрерывных, существенно изменяющихся в процессе преобразования сигналов в двоичный позиционный код в условиях воздействия низкочастотной и высокочастотной помех о

Uелью изобретения является повышение точности преобразования непрерывных сигналов, существенно изменяющихся в процессе преобразования

в код в условиях воздействия низкочастотной и высокочастотной помех.

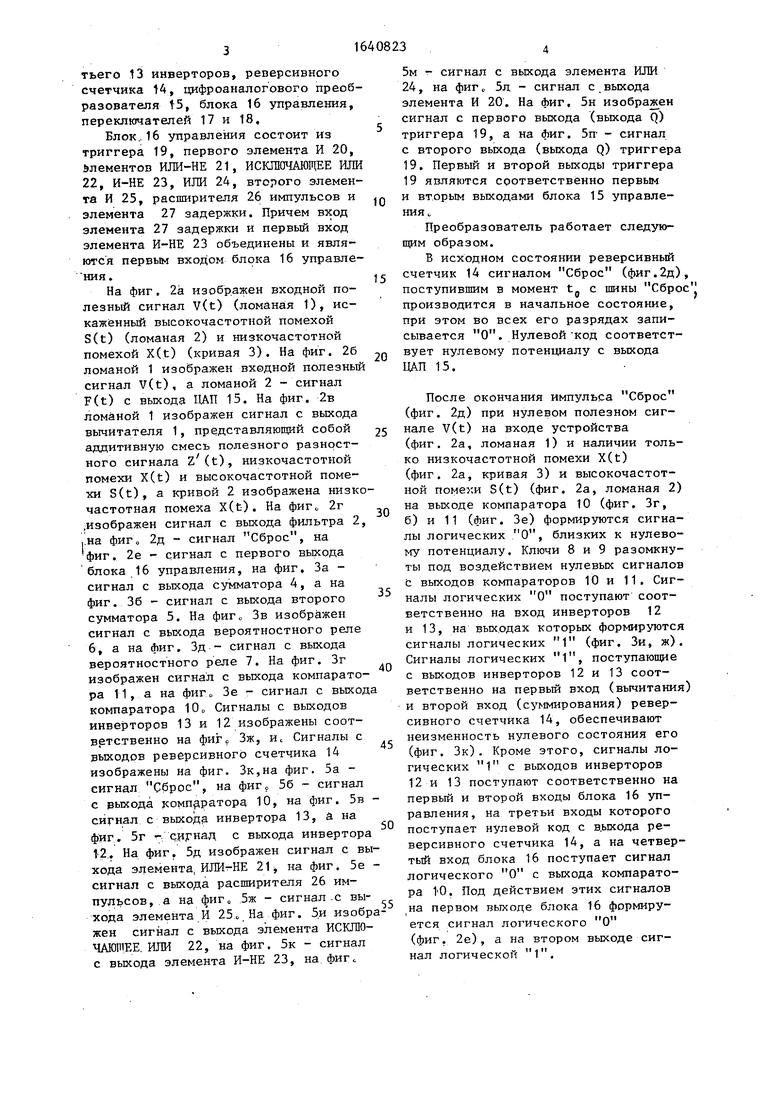

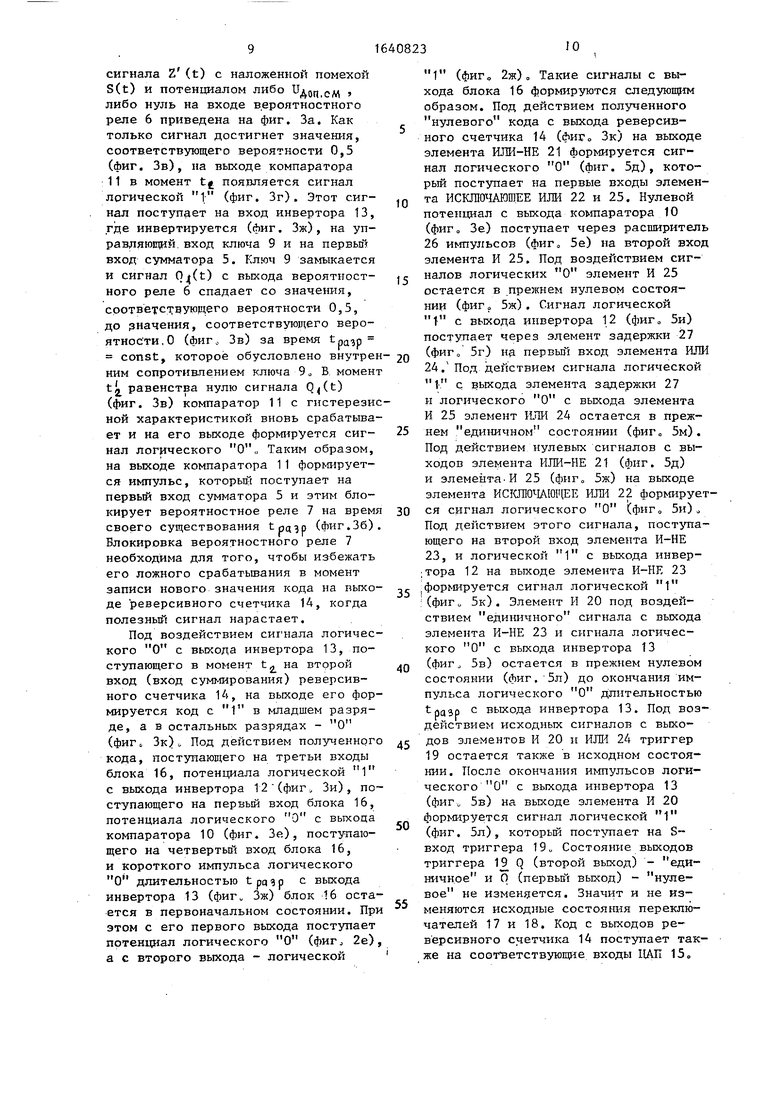

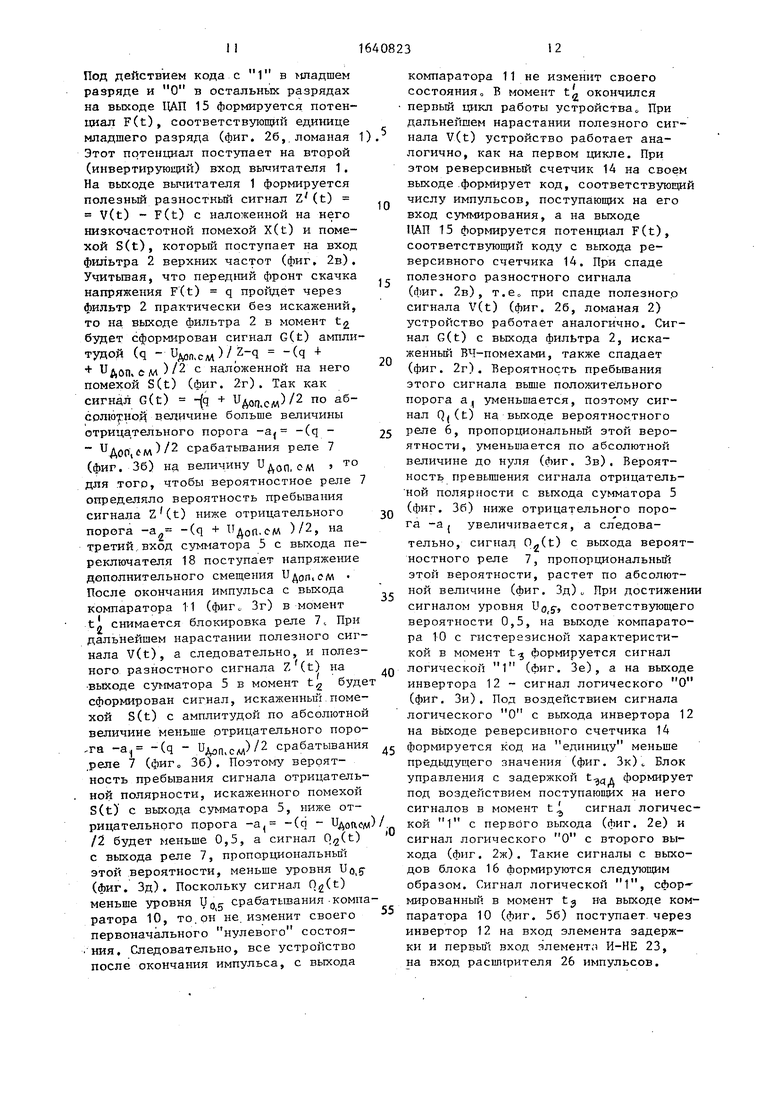

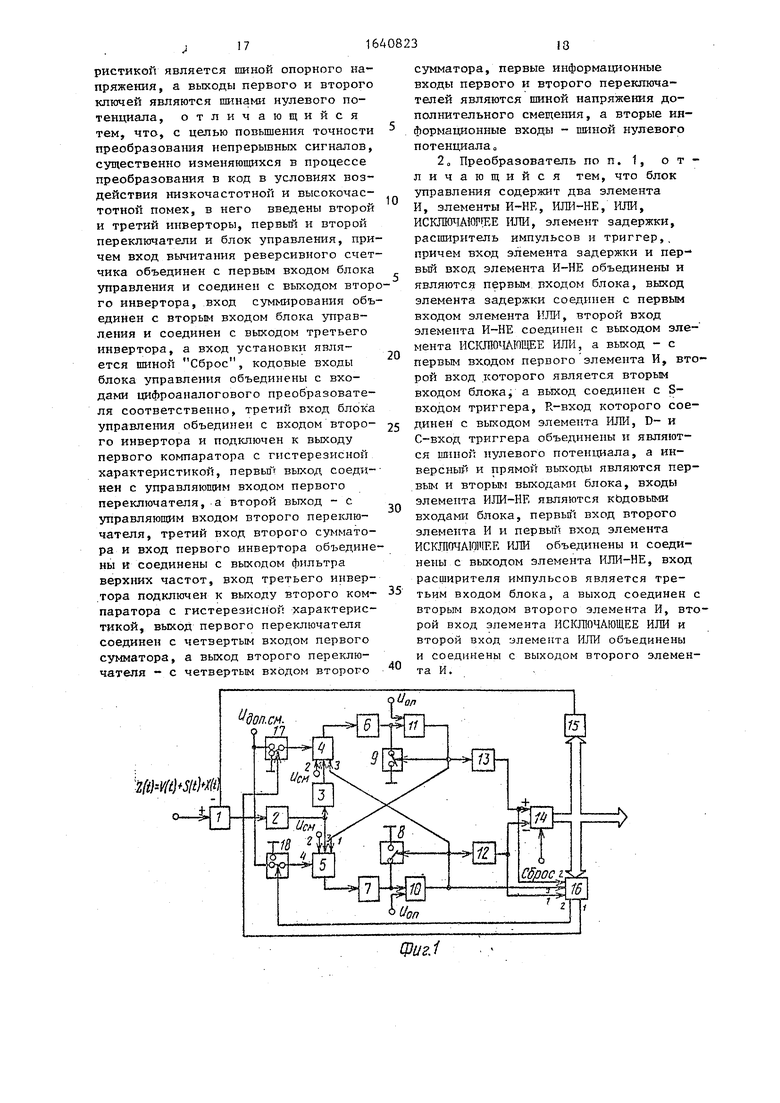

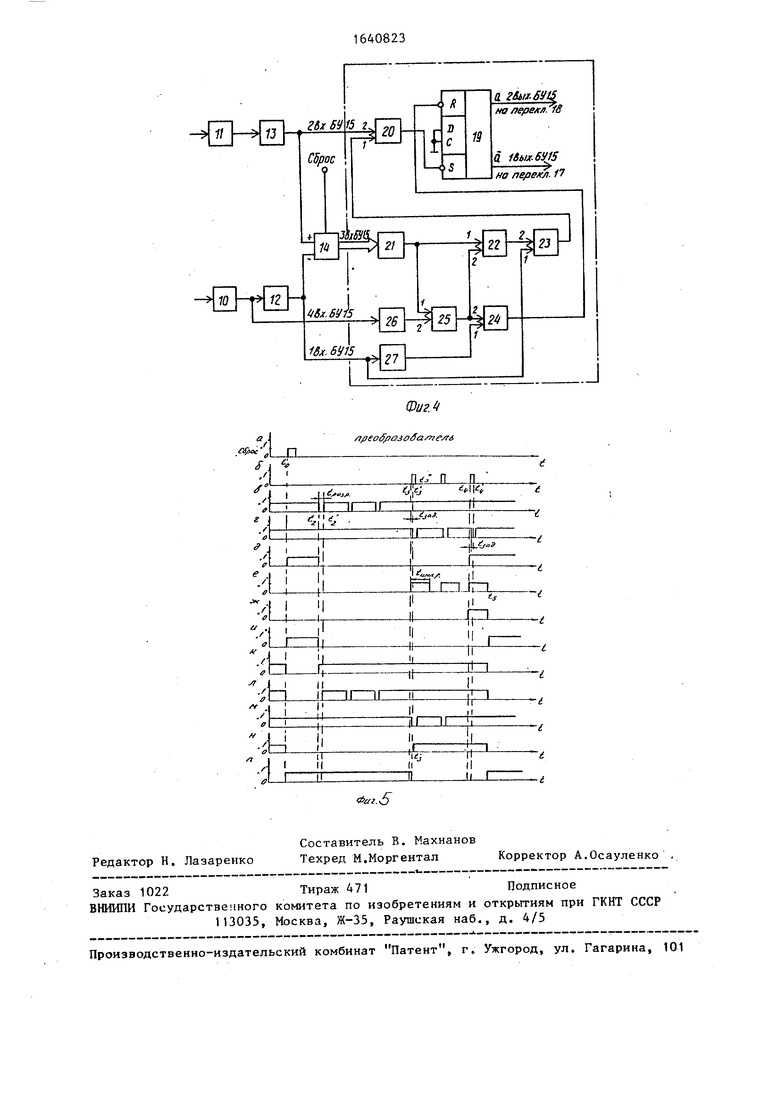

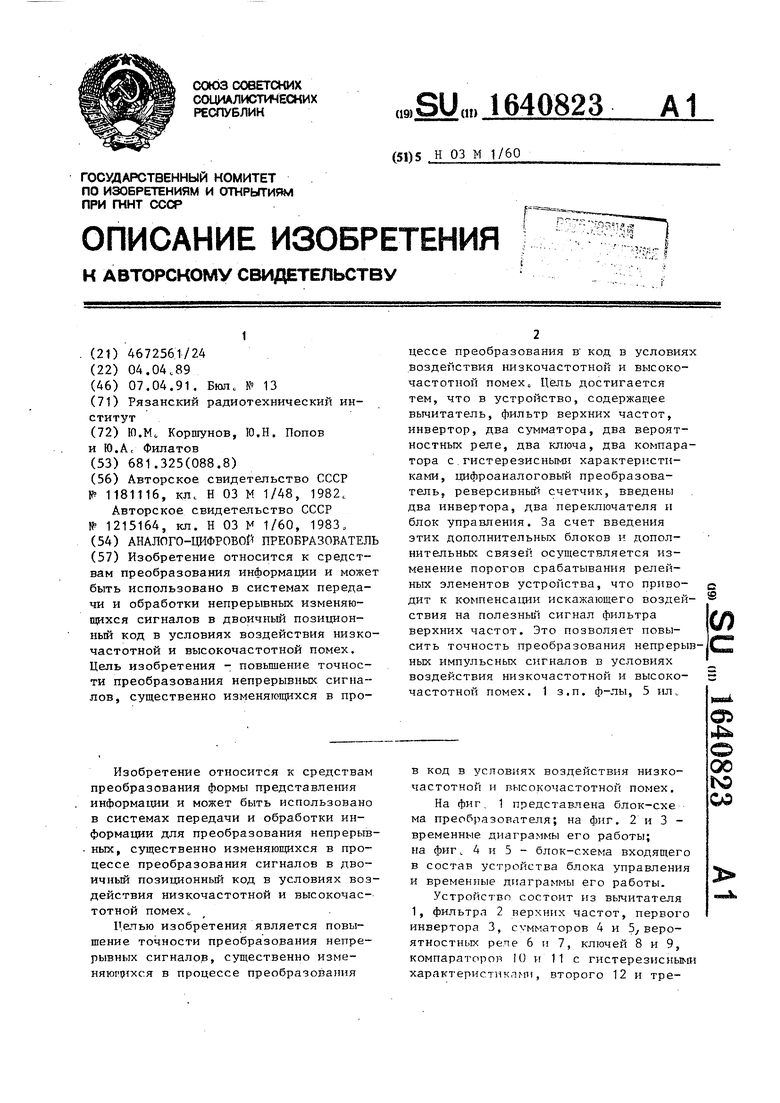

На фиг 1 представлена блок-схе ма преобразователя; на фиг. 2 и 3 - временные диаграммы его работы; на фиг. 4 и 5 - блок-схема входящего в состав устройства блока управления и временные диаграммы его работы.

Устройство состоит из вычитателя 1, фильтра 2 верхних частот, первого инвертора 3, с мматоров 4 и 5, вероятностных репе 6 и 7, ключей 8 и 9, компараторов IU и 11 с гистерезисными характеристиками, второго 12 и тре00

к

со

тьего 13 инверторов, реверсивного счетчика 14, цифроаналогового преобразователя t5, блока 16 управления, переключателей 17 и 18.

Блок,16 управления состоит из триггера 19, первого элемента И 20, Элементов ИЛИ-НЕ 21, ИСКЛЮЧАЮЩЕЕ ИЛИ 22, И-НЕ 23, ИЛИ 24, второго элемента И 25, расширителя 26 импульсов и элемента 27 задержки. Причем вход элемента 27 задержки и первый вход элемента И-НЕ 23 объединены и являются первым входом блока 16 управле- ния.

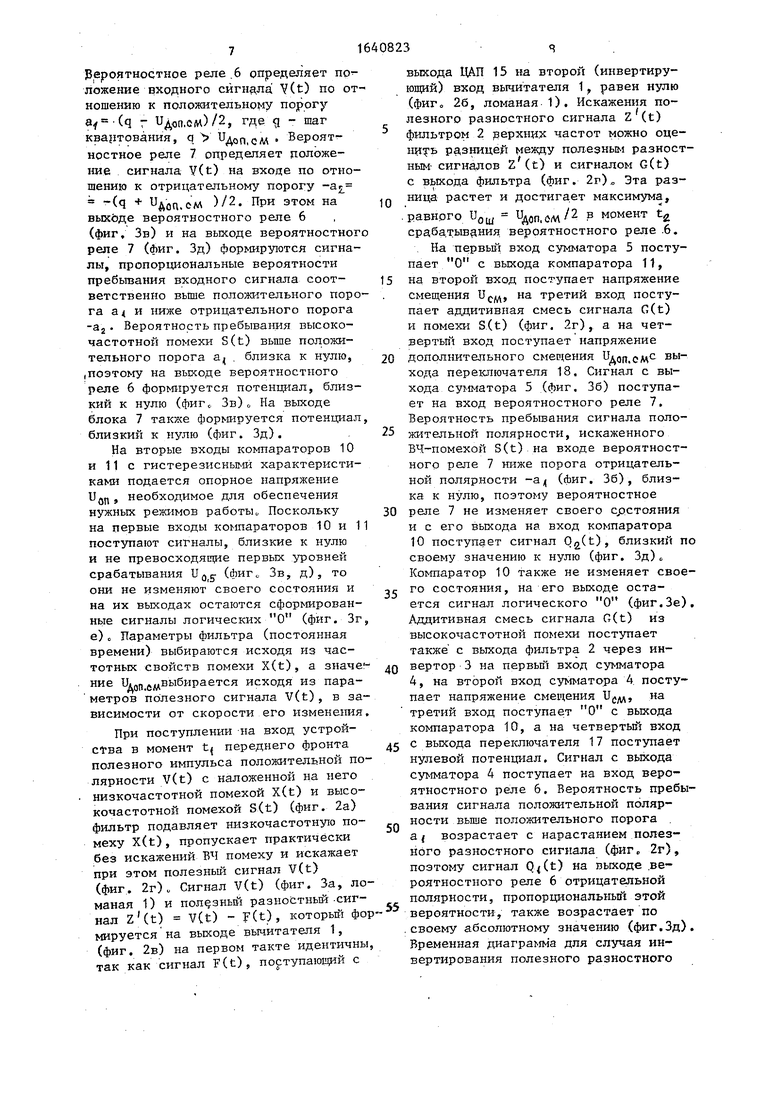

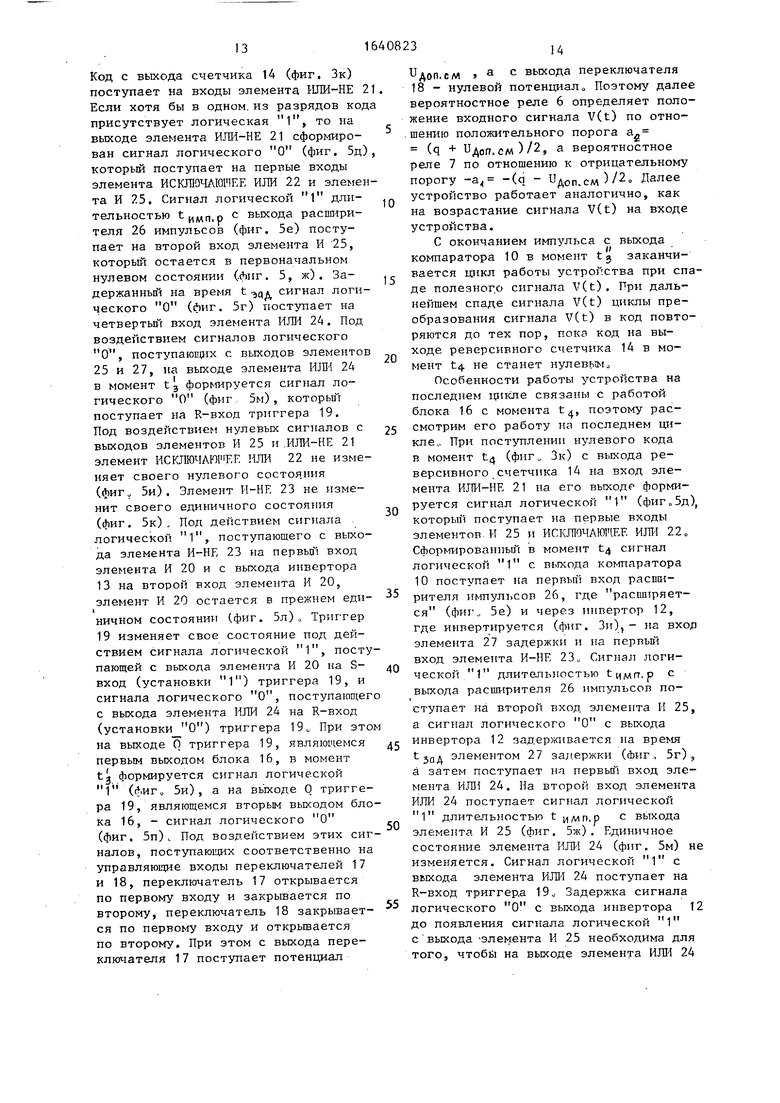

На фиг, 2а изображен входной полезный сигнал V(t) (ломаная 1), искаженный высокочастотной помехой S(t) (ломаная 2) и низкочастотной помехой X(t) (кривая 3). На фиг. 26 ломаной 1 изображен входной полезный сигнал V(t), а ломаной 2 - сигнал F(t) с выхода ЦАП 15. На фиг. 2в ломаной 1 изображен сигнал с выхода вычитателя 1, представляющий собой аддитивную смесь полезного разностного сигнала Z (t), низкочастотной помехи X(t) и высокочастотной помехи S(t), а кривой 2 изображена низкочастотная помеха X(t) . На фиг, 2г .изображен сигнал с выхода фильтра 2, , на фиг о 2д - сигнал Сброс, на фиг. 2е - сигнал с первого выхода блока 16 управления, на фиг. За - сигнал с выхода сумматора 4, а на фиг. 36 - сигнал с выхода второго сумматора 5. На фиг„ Зв изображен сигнал с выхода вероятностного реле 6, а на фиг. Зд - сигнал с выхода вероятностного реле 7. На фиг. Зг изображен сигнал с выхода компаратора 1 1 , а на фиг 0 Зе - сигнал с выход компаратора Юс, Сигналы с выходов инверторов 13 и 12 изображены соответственно на фиг« Зж, иь Сигналы с выходов реверсивного счетчика 14 изображены на фиг. Зк,на фиг. 5а - сигнал Сброс, на фиг о 56 - сигнал с рыхода компаратора 10, на фиг. 5в сигнал с выхода инвертора 13, а на фиг. 5г - сигнад с выхода инвертора 1-2. На фиг. 5д изображен сигнал с выхода элемента, ИЛИ-НЕ 21, на фиг. 5е сигнал с выхода расширителя 26 импульсов, а на фиг, 5ж - сигнал с вы- хода элемента И 25 о На фиг. 5и изобржен сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22, на фиг. 5к - сигнал с выхода элемента И-НЕ 23, на фиг.

0

5

0

5

0

5

0

5

0

5м - сигнал с выхода элемента ИЛИ 24, на фиг о 5д - сигнал с.выхода элемента И 20. На фиг. 5н изображен сигнал с первого выхода (выхода Q) триггера 19, а на фиг. 5п- - сигнал с второго выхода (выхода Q) триггера 19. Первый и второй выходы триггера 19 являются соответственно первым и вторым выходами блока 15 управления о

Преобразователь работает следующим образом.

В исходном состоянии реверсивный счетчик 14 сигналом Сброс (фиг.2д), поступившим в момент tQ с шины Сброс производится в начальное состояние, при этом во всех его разрядах записывается О. Нулевой код соответствует нулевому потенциалу с выхода ЦАП 15.

После окончания импульса Сброс (фиг. 2д) при нулевом полезном сигнале V(t) на входе устройства (фиг. 2а, ломаная 1) и наличии только низкочастотной помехи X(t) (фиг. 2а, кривая 3) и высокочастотной помехи S(t) (фиг. 2а, ломаная 2) на выходе компаратора 10 (фиг. Зг, б) и 11 (фиг. Зе) формируются сигналы логических О, близких к нулевому потенциалу. Ключи 8 и 9 разомкнуты под воздействием нулевых сигналов с выходов компараторов 10 и 11. Сигналы логических О поступают соответственно на вход инверторов 12 и 13, на выходах которых формируются сигналы логических 1 (фиг. Зи, ж). Сигналы логических 1, поступающие с выходов инверторов 12 и 13 соответственно на первый вход (вычитания) и второй вход (суммирования) реверсивного счетчика 14, обеспечивают неизменность нулевого состояния его (фиг. Зк). Кроме этого, сигналы логических 1 с выходов инверторов 12 и 13 поступают соответственно на первый и второй входы блока 16 управления, на третьи входы которого поступает нулевой код с выхода реверсивного счетчика 14, а на четвертый вход блока 16 поступает сигнал логического О с выхода компаратора 1-0. Под действием этих сигналов (на первом выходе блока 16 формируется сигнал логического О (фиг. 2е), а на втором выходе сигнал логической 1.

Формирование таких сигналов происходит следующим образом. При приходе сигнала Сброс (фиг. 5а) в момент t0 на выходе реверсивного счетчика 14 формируется нулевой код (фиг. Зк), который поступает на входы элемента ИЛИ-НЕ 21. Под действием нулевого кода на выходе элемента ИЛИ-НЕ 21 формируется сигнал логической 1 (фигс 5а). Этот сигнал поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 и на первый вход элемента И 25. Сигнал логической 1 с выхода инвертора 12 (Лиг. Зд) поступает на первый вход элемента И-НЕ 23 и через элемент задержки 27 (Лиг 5г) на первый вход элемента ИЛИ 24. Сигнал логического О с выхода компаратора 10 (фиг.Зе, 5б) через расширитель 26 импульсов (фиг. 5е) поступает на второй вход элемента И 25, на выходе которого под действием этого сигнала формируется логический О (фиг. 5ж). Логический О с выхода элемента И 25 поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 и на второй вход элемента ИЛИ 24, на выходе которого под действием сигнала логической 1 с выхода элемента задержки сформирован сигнал логической 1 (фиг о 5м). Сигнал логической 1 с выхода элемента ИЛИ 24 поступает на R-вход (вход установки О) триггера 19. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 под действием сигнала логической 1 с выхода элемента ИЛИ-НЕ 21 и логического О с выхода элемента И 24 формируется сигнал логической 1 (фигь 5и). Под действием сигнала логической 1 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22, поступающего на второй ввод элемента И-НЕ 23, и сигнала логической 1 с выхода инвертора 12,на выходе элемента И-НЕ 23 формируется сигнал логического О (фиг,, 5к) , который затем поступает на первый вход элемента И 20, на второй вход которого поступает с выхода инвертора 13 сигнал логической 1 (фиг. 5в). Под действием этих сигналов на выходе элемента И 20 формируется сигнал логического О (фиг„ 5л), который поступает на S-вход (установки 1) триггера t9.Ha выходе триггера 19,являющемся первым выходом блока 16,под действием логического выхода элемента

0

5

0

5

0

5

0

5

0

5

И 20 и сигнала логической 1 с выхода ИЛИ 24 формируется сигнал логического О (фиг. 5н), а на выходе О триггера 19, являющемся вторым входом блока 16 т сигнал логической 1 (фиг. 5п).

Под воздействием логического О, поступающего на управляющий вход первого переключателя 17 с первого выхода блока 16, переключатель 17 закрыт по первому информационному входу и открыт по второму информационному входу, при этом на его выходе устанавливается нулевой потенциал. Под действием сигнала логической 1, поступающего на управляющий вход второго переключателя 18 с второго выхода блока 16, переключатель 18 закрыт по второму информационному входу и открыт по первому информационному входу, при этом на его выходе устанавливается напряжение дополнительного смещения см . Фильтр 2 подавляет низкочастотную помеху X(t) и пропускает практически без изменений высокочастотную помеху S(t) (фиг. 2г), которая поступает на третий вход сумматора 5 и через инвертор 3 на первый вход сумматора 4. На вторые входы сумматоров 4 и 5 поступает напряжение смещения UOM, необходимое для обеспечения работы вероятностного реле 7 на сигналы отрицательной полярности и для обеспечения работы вероятностного реле 6 на сигналы положительной полярности. Для этой :се цели, а также для того, чтобы применять одинаковые вероятностные реле, используется инвертор 3„ Для обеспечения изменения уровней срабатывания вероятностных реле 6 и 7 на четвертые входы сумматоров 4 и 5 поступают сигналы соответственно с выходов переключателей 17 и 18. На третий вход сумматора

4и первьй вход сумматора 5 поступают сигналы логических О, близкие к нулевому потенциалу с выходов соответственно компараторов 10 и 11. На четвертый вход сумматора 4 поступает нулевой потенциал с выхода первого переключателя 17, а на четвертый вход сумматора 5 с выхода переключателя 18 поступает напряжение дополнительного смещения идОП|СА1. Сигналы

с выходов сумматоров 4 (фиг. За) и

5(фиг. 36) поступают соответственно на выходы вероятностных реле 6 и 7.

Рероятностное реле 6 определяет положение входного сигнала Y(t) по отношению к положительному порогу &1К (q г идоп.см)/2, где $ - шаг квантования, q идОП|СМ . Вероятностное реле 7 определяет положение сигнала V(t) на входе по отношению к отрицательному порогу -а -(q + U доп. ом )/2. При этом на выходе вероятностного реле 6 (фиг, Зв) и на выходе вероятностного реле 7 (фиг. Зд) формируются сигналы, пропорциональные вероятности пребывания входного сигнала соответственно выше положительного порога а и ниже отрицательного порога -а2 . Вероятность пребывания высокочастотной помехи S(t) выше положительного порога а близка к нулю, ,поэтому на выходе вероятностного реле 6 формируется потенциал, близкий к нулю (фигс Зв) с, На выходе блока 7 также формируется потенциал, близкий к нулю (фиг. Зд).

На вторые входы компараторов 10 и 11 с гистерезисными характеристиками подается опорное напряжение иоп, необходимое для обеспечения нужных режимов работы„ Поскольку на первые входы компараторов 10 и 11 поступают сигналы, близкие к нулю и не превосходящие первых уровней срабатывания U0iS- (йигс Зв, д), то они не изменяют своего состояния и на их выходах остаются сформированные сигналы логических О (фиг. Зг, е)с Параметры фильтра (постоянная времени) выбираются исходя из частотных свойств помехи X(t), а значение и.оП1СМвыбирается исходя из параметров полезного сигнала V(t), в зависимости от скорости его изменения.

При поступлении на вход устройства в момент tj переднего фронта полезного импульса положительной полярности V(t) с наложенной на него низкочастотной помехой X(t) и высокочастотной помехой S(t) (фиг. 2а) фильтр подавляет низкочастотную помеху X(t), пропускает практически без искажений ВЧ помеху и искажает при этом полезный сигнал V(t) (фиг. 2г)„ Сигнал V(t) (фиг. За, ломаная 1) и полезный разностный сигнал Z (t) V(t) - F(t), который фор мируется на выходе вычитателя 1, (фиг. 2в) на первом такте идентичны, так как сигнал F(t), поступающий с

выхода ЦАП 15 на второй (инвертирующий) вход вычитателя 1, равен нулю (фиго 26, ломаная 1). Искажения полезного разностного сигнала Z (t) фильтром 2 верхних частот можно оценить разницей между полезным разностным сигналов z (t) и сигналом G(t) с выхода фильтра (фиг. 2г), Эта разJQ ница растет и достигает максимума, равного иащ UAOfliCM/2 в момент t& срабатывания вероятностного реле 6.

На первый вход сумматора 5 поступает О с выхода компаратора 11,

15 на второй вход поступает напряжение смещения Ucw, на третий вход поступает аддитивная смесь сигнала G(t) и помехи S(t) (фиг. 2г), а на четвертый вход поступает напряжение

20 дополнительного смещения Цдоп.см0 вы хода переключателя 18. Сигнал с выхода сумматора 5 (Лиг. 36) поступает на вход вероятностного реле 7, Вероятность пребывания сигнала поло25 жительной полярности, искаженного ВЧ-помехой S(t) на входе вероятностного реле 7 ниже порога отрицательной полярности -ац (Лиг. 36), близка к нулю, поэтому вероятностное

30 реле 7 не изменяет своего состояния и с его выхода на вход компаратора 10 поступает сигнал Q2(t), близкий по своему значению к нулю (фиг. Зд)„ Компаратор 10 также не изменяет свое- ос го состояния, на его выходе остается сигнал логического 0й (фиг.Зе), Аддитивная смесь сигнала 0(t) из высокочастотной помехи поступает также с выхода фильтра 2 через ин40 вертор 3 на первый вход сумматора 4, на второй вход сумматора 4 поступает напряжение смещения U,,M, на третий вход поступает О с выхода компаратора 10, а на четвертый вход

45 с выхода переключателя 17 поступает нулевой потенциал. Сигнал с выхода сумматора 4 поступает на вход вероятностного реле 6. Вероятность пребывания сигнала положительной полярности выше положительного порога а( возрастает с нарастанием полезного разностного сигнала (фиг„ 2г), поэтому сигнал ) на выходе вероятностного реле 6 отрицательной полярности, пропорциональный этой вероятности, также возрастает по своему абсолютному значению (фиг.Зд). Временная диаграмма для случая инвертирования полезного разностного

50

55

сигнала Z (t) с наложенной помехой S(t) и потенциалом либо 11дог см , либо нуль на входе вероятностного реле 6 приведена на фиг. За. Как только сигнал достигнет значения, соответствующего вероятности 0,5 (фиг. Зв), на выходе компаратора 11 в момент t появляется сигнал логической 1 (фиг. Зг). Этот сигнал поступает на вход инвертора 13, где инвертируется (фиг. Зж), на управляющий вход ключа 9 и на первый вход сумматора 5. Ключ 9 замыкается и сигнал Qj((t) с выхода вероятностного реле 6 спадает со значения, соответствующего вероятности 0,5, до значения, соответствующего веро

ятности.О (фиго Зв) за время t

разр

const, которое обусловлено внутрен ним сопротивлением ключа 90 Б момент t равенства нулю сигнала Q(t) (фиг. Зв) компаратор 11 с гистерезис ной характеристикой вновь срабатывает и на его выходе формируется сигнал логического Таким образом, на выходе компаратора 11 формируется импульс, который поступает на первый вход сумматора 5 и этим блокирует вероятностное реле 7 на время своего существования (Лиг.36). Блокировка вероятностного реле 7 необходима для того, чтобы избежать его ложного срабатывания в момент записи нового значения кода на выходе реверсивного счетчика 14, когда полезный сигнал нарастает.

Под воздействием сигнала логического О с выхода инвертора 13, поступающего в момент t на второй вход (вход суммирования) реверсивного счетчика 14, на выходе его формируется код с 1 в младшем разряде, а в остальных разрядах - О (фиг0 Зк)„ Под действием полученного кода, поступающего на третьи входы блока 16, потенциала логической 1 с выхода инвертора 12 (фиг, Зи), поступающего на первый вход блока 16, потенциала логического О с выхода компаратора 10 (фиг, Зе), поступающего на четвертый вход блока 16, и короткого импульса логического О длительностью с выхода инвертора 13 (фиг Зж) блок 16 остается в первоначальном состоянии. При этом с его первого выхода поступает потенциал логического О (фигл 2е), а с второго выхода - логической

0

5

5

0

0

5

0

5

5 i

0

1 (фиг, 2ж)о Такие сигналы с выхода блока 16 формируются следующим образом. Под действием полученного нулевого кода с выхода реверсивного счетчика 14 (фиг Зк) на выходе элемента ШШ-НЕ 21 формируется сигнал логического О (фиг. 5д), который поступает на первые входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 и 25. Нулевой потенциал с выхода компаратора 10 (фиг о Зе) поступает через расширитель 26 импульсов (фиг о 5е) на второй вход элемента И 25. Под воздействием сигналов логических О элемент И 25 остается в прежнем нулевом состоянии (фиг о 5ж). Сигнал логической I с выхода инвертора 12 (фиг0 5и) поступает через элемент задержки 27 (фиг„ 5г) на первый вход элемента ИЛИ 24/ Под действием сигнала логической 1 с выхода элемента задержки 27 и логического О с выхода элемента И 25 элемент ИЛИ 24 остается в прежнем единичном состоянии (фиг„ 5м). Под действием нулевых сигналов с выходов элемента ИЛИ-НЕ 21 (фиг. 5д) и элемента И 25 (фиг0 5ж) на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 формируется сигнал логического О (фиг0 5и)„ Под действием этого сигнала, поступающего на второй вход элемента И-НЕ 23, и логической 1 с выхода инвертора 12 на выходе элемента И-НЕ 23 формируется сигнал логической 1 (фиг„ 5к). Элемент И 20 под воздействием единичного сигнала с выхода элемента И-НЕ 23 и сигнала логического О с выхода инвертора 13 (фиг0 5в) остается в прежнем нулевом состоянии (фиг. 5л) до окончания импульса логического О длительностью tpgjp с выхода инвертора 13. Под воздействием исходных сигналов с выходов элементов И 20 и ИЛИ 24 триггер 19 остается также в исходном состоянии. После окончания импульсов логического О с выхода инвертора 13 (фиг о 5в) на выходе элемента И 20 формируется сигнал логической 1 (фиг. 5л), который поступает на S- вход триггера 19„ Состояние выходов триггера 19 Q (второй выход) - единичное и 0 (первый выход) - нулевое не изменяется. Значит и не изменяются исходные состояния переключателей 17 и 18, Код с выходов реверсивного счетчика 14 поступает также на соответствующие входы ЦАП 15,

Под действием кода с 1 в младшем разряде и О в остальных разрядах на выходе ЦАП 15 формируется потенциал F(t), соответствующий единице младшего разряда (фиг. 26, ломаная 1) Этот потенциал поступает на второй (инвертирующий) вход вы нтателя 1. На выходе вычитателя 1 формируется полезный разностный сигнал Z (t) V(t) - F(t) с наложенной на него низкочастотной помехой X(t) и помехой S(t), который поступает на вход фильтра 2 верхних частот (фиг, 2в). Учитывая, что передний фронт скачка напряжения F(t) q пройдет через фильтр 2 практически без искажений, то на выходе фильтра 2 в момент tg будет сформирован сигнал G(t) амплитудой (q - -(q +

Uion. ем)/2 с наложенной на него помехой S(t) (фиг. 2г). Так как сигнал G(t) -(q + иАоп.см)/2 по аб солютлой, величине больше величины отрицательного порога -aj -(q -ид00(6М)/2 срабатывания реле 7 (фиг. 36) на величину иДоП| ом , то для того, чтобы вероятностное реле 7 определяло вероятность пребывания сигнала Z (t) ниже отрицательного порога -а2 -(q + Пд0п.см )/2, на третий вход сумматора 5 с выхода переключателя 18 поступает напряжение дополнительного смещения идОП1ем . После окончания импульса с выхода компаратора 11 (фиГс Зг) в момент

ti снимается блокировка реле 1,. При дальнейшем нарастании полезного сигнала V(t), а следовательно, и полезного разностного сигнала Z (t) на выходе сумматора 5 в момент сформирован сигнал, искаженный помехой S(t) с амплитудой по абсолютной величине меньше отрицательного порога -а, -(q - UAon,CA,)/2 срабатывания реле 7 (фиг„ 36). Поэтому вероятность пребывания сигнала отрицательной полярности, искаженного помехой S(t) с выхода сумматора 5, ниже отрицательного порога а, -(q - Uftonc,w /2 будет меньше 0,5, а сигнал 02(t) с выхода реле 7, пропорциональный этой вероятности, меньше уровня UO.JT (фиг. Зд). Поскольку сигнал Q2(t) меньше уровня U0(5 срабатывания компаратора 10, то он не изменит своего первоначального нулевого состояния. Следовательно, все устройство после окончания импульса, с выхода

tg буде

5

0

5

0

5

0

5

5

компаратора 11 не изменит своего состояния В момент t окончился первый цикл работы устройства При дальнейшем нарастании полезного сигнала V(t) устройство работает аналогично, как на первом цикле. При этом реверсивный счетчик 14 на своем выходе формирует код, соответствующий числу импульсов, поступающих на его вход суммирования, а на выходе ЦАП 15 формируется потенциал F(t), соответствующий коду с выхода реверсивного счетчика 14. При спаде полезного разностного сигнала (Фиг, 2в), т.е„ при спаде полезного сигнала V(t) (Лиг. 2б, ломаная 2) устройство работает аналогично. Сигнал G(t) с выхода фильтра 2, искаженный ВЧ-помехами, также спадает (фиг. 2г). Вероятность пребывания этого сигнала выше положительного порога а) уменьшается, поэтому сигнал Q|(t) на выходе вероятностного реле 6, пропорциональный этой вероятности, уменьшается по абсолютной величине до нуля (Лиг. Зв). Вероятность превышения сигнала отрицательной полярности с выхода сумматора 5 (фиг. 36) ниже отрицательного порога -а( увеличивается, а следовательно, сигнал 0-,(t) с выхода вероятностного реле 7, пропорциональный этой вероятности, растет по абсолютной величине (Лиг. Зд)„ При достижении сигналом уровня , соответствующего вероятности 0,5, на выходе компаратора 10 с гистерезисной характеристикой в момент t-j Формируется сигнал логической 1 (Фиг. Зе), а на выходе инвертора 12 - сигнал логического О (фиг. Зи). Под воздействием сигнала логического О с выхода инвертора 12 на выходе реверсивного счетчика 14 формируется код на единицу меньше предыдущего -значения (фиг. Зк) „ Блок управления с задержкой t формирует под воздействием поступающих на него сигналов в момент t сигнал логической 1 с первого выхода (фиг. 2е) и сигнал логического О с второго выхода (фиг. 2ж). Такие сигналы с выходов блока 16 Лормируются следующим образом. Сигнал логической 1, сфор мированный в момент ts на выходе компаратора 10 (фиг. 56) поступает через инвертор 12 на вход элемента задержки и первый вход элемента И-НЕ 23, на вход расширителя 26 импульсов.

Код с выхода счетчика 14 (фиг, Зк) поступает на входы элемента ИЛИ-НЕ 2 Если хотя бы в одном, из разрядов код присутствует логическая 1, то на выходе элемента ИЛИ-НЕ 21 сформирован сигнал логического О (фиг. 5д) который поступает на первые входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 и элемента И 25. Сигнал логической 1 длительностью t(1Mrlip с выхода расширителя 26 импульсов (фиг. 5е) поступает на второй вход элемента И 25, который остается в первоначальном нулевом состоянии (Лиг. 5, ж). Задержанный на время t сигнал логического О (Лиг. 5г) поступает на четвертый вход элемента ИЛИ 24. Под воздействием сигналов логического О, поступающих с выходов элементов

25 и 27, иа выходе элемента ИЛИ 24 j i

в момент t з формируется сигнал логического О (фиг 5м), который поступает на R-вход триггера 19. Под воздействием нулевых сигналов с выходов элементов И 25 и ИЛИ-НЕ 21 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22 не изменяет своего нулевого состояния (фиги 5и), Элемент И-НЕ 23 не изменит своего единичного состояния (фиг. 5к), Под действием сигнала логической 1, поступающего с выхода элемента И-НЕ 23 на первый вход элемента И 20 и с выхода инвертора 13 на второй вход элемента И 20, элемент И 20 остается в прежнем единичном состоянии (фиг. 5л)0 Триггер 19 изменяет свое состояние под действием сигнала логической 1, поступающей с выхода элемента И 20 на S- вход (установки 1) триггера 19, и сигнала логического О, поступающег с выхода элемента ИЛИ 24 на R-вход (установки О) триггера 19„ При это на выходе 0 триггера 19, являющемся первым выходом блока 16, в момент tj Формируется сигнал логической 1 (фиг„ 5и), а на въ коде О триггера 19, являющемся вторым выходом блока 16, - сигнал логического О (фиг, 5п)t Под воздействием этих сигналов, поступающих соответственно на управляющие входы переключателей 17 и 18, переключатель 17 открывается по первому входу и закрывается по второму, переключатель 18 закрывается по первому входу и открывается по второму. При этом с выхода переключателя 17 поступает потенциал

0

5

0

5

о $

0

5

5

доп.см а с выхода переключателя 18 - нулевой потенциал о Поэтому далее вероятностное реле 6 определяет положение входного сигнала V(t) по отношению положительного порога а. (q + )/2, а вероятностное реле 7 по отношению к отрицательному порогу -а,, -(q - )/2„ Далее устройство работает аналогично, как на возрастание сигнала V(t) на входе устройства.

С окончанием импульса с выхода компаратора 10 в момент tj заканчивается цикл работы устройства при спаде полезного сигнала V(t). При дальнейшем спаде сигнала V(t) циклы преобразования сигнала V(t) в код повторяются до тех пор, пока код на выходе реверсивного счетчика 14 в момент t4 не станет нулевым0

Особенности работы устройства на последнем цикле связаны с работой блока 16 с момента t, поэтому рассмотрим его работу на последнем цикле,. При поступлении нулевого кода в момент t (фиг0 Зк) с выхода реверсивного счетчика 14 на вход элемента ИЛИ-НЕ 21 на его выходе формируется сигнал логической 1 (фиг„5д), который поступает на первые входы элементов И 25 и ИСКЛЮЧАЮЩЕЕ ИЛИ 22. Сформированный в момент t4 сигнал логической 1 с выхода компаратора 10 поступает на первый вход расширителя импульсов 26, где расширяется (фиг, 5е) и через инвертор 12, где инвертируется (фиг. Зи), - на вход элемента 27 задержки и на первый вход элемента И-НЕ 23„ Сигнал логической 1 длительностью .p с выхода расширителя 26 импульсов поступает на второй вход элемента И 25, а сигнал логического О с выхода инвертора 12 задерживается на время t Зад элементом 27 задержки (биг, 5г), а затем поступает на первый вход элемента ИЛИ 24. На второй вход элемента ИЛИ 24 поступает сигнал логической 1 длительностью t иддп,р с выхода элемента И 25 (фиг. 5ж). Единичное состояние элемента ИЛИ 24 (фиг. 5м) не изменяется. Сигнал логической 1 с выхода элемента ИЛИ 24 поступает на R-вход триггера 190 Задержка сигнала логического О с выхода инвертора 12 до появления сигнала логической 1 с выхода элемента И 25 необходима для того, чтобй на выходе элемента ИЛИ 24

исключить появление в интервале времени от tfy. до t сигнала логического О. Сигнал логической 1 с выхода элемента И 25 поступает также на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22. При неодновременном появлении сигналов логической 1 на первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 в момент, близкий к t4, на выходе этого элемента возникает короткий импульс логической 1 (фиг. 5и). Длительность этого импульса обусловлена разностью задержки цепочки, состоящей из инвертора 12, реверсивного счетчика 14, элемента ИЛИ-НЕ 21, и цепочки, состоящей из расширителя 26 импульсов и элемента И 25„ Этот импульс приходит на вход элемента И-НЕ 23 с задержкой по сравнению с приходом на другой его вход сигнала логического О с выхода инвертора 13. Поэтому единичное состояние элемента И-НЕ 23 в момент, близкий к не изменяется, а еле- довательно, не изменяется единичное. состояние элемента И 20, на оба входа которого поступают сигналы логической 1 с выхода элемента И НЕ 23 и инвертора 13. Не изменяется состояние триггера 19, поскольку на его R- и S-входы поступают сигналы логических 1 с выходов элементов ИЛИ 24 и И 20. После окончания сиг- длительностью

нала логической 1

tM/wn.pc выхода расширителя 26 импульсов (фиг с 5е) на выходе элемента И 25 в момент t Нормируется сигнал логического О (фиг. 5ж), а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 - сигнал логической 1 (фиг05и). Поскольку t pqip , то к этому моменту на выходе инвертора 12 сформирован сигнал логической 1 (фиг. Зи), который поступает на первый вход элемента И-НЕ 23 и через элемент 27 задержки на первый вход элемента ИЛИ 24. Единичное состоя- ние элемента ИЛИ 24 не изменяется (фиг о 5м), а на выходе элемента ИЛИ-НЕ 23 формируется сигнал логического О (фиг. 5к), который поступает на первый вход элемента И 20. На выходе элемента И 20 формируется сигнал логического О (фиг. 5л), который переводит триггер 19 в другое состояние, при этом на его выходе (} формируется сигнал логического О а на выходе Q - сигнал логической

0

5

5

0

0

5

0

5

0

5

Под воздействием сигналов с выхода триггера 19 переключатель 17 закрывается по первому входу и открывается по второму, а переключатель 18 закрывается по второму входу и открывается по первому0 Устройство перешло в исходное состояние и готово к преобразованию следующего информационного импульса V(t), искаженного ВЧ-помехой S(t) и НЧ-помехой X(t)„

Формула изобретения

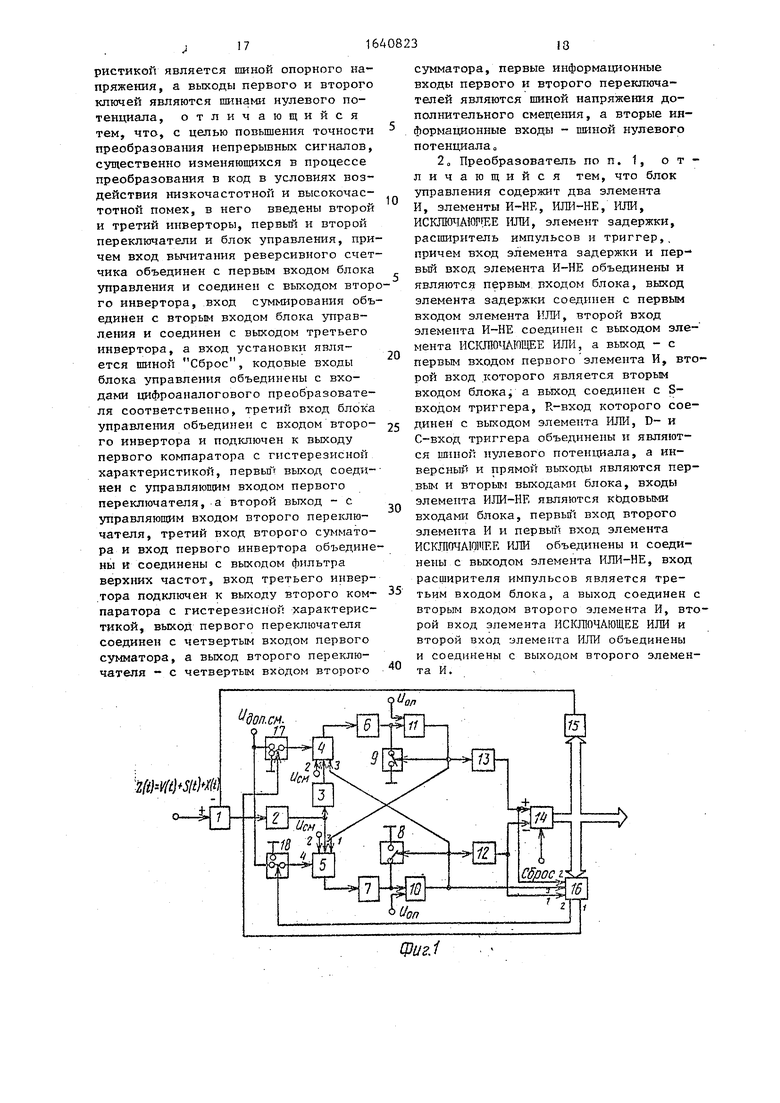

1 о Аналого-цифровой преобразователь, содержащий фильтр верхних частот, первый инвертор, первый и второй сумматоры, первое и второе вероятностные реле, первый и второй ключи, первый и второй компараторы с гистерезисными характеристиками, цифроаналоговый преобразователь, реверсивный счетчик и вычитатель, первый вход которого является входной шиной, выход соединен с входом фильтра верхних частот, а второй вход - с выходом цифроаналогового преобразователя, входы которого соединены с соответствующий выходами реверсивного счетчика, которые являются выходными шинами, первый вход первого сумматора соединен с выходом первого инвертора, второй вход является шиной напряжения смещения, третий вход объединен с управляющим входом первого ключа и соединен с выходом первого компаратора с гисте- резисной характеристикой, а выход соединен с входом первого вероятностного реле, первый вход второго компаратора с гистерезисной характеристикой объединен с информационным входом второго ключа и соединен с выходом первого вероятностного реле, а второй вход является шиной опорного напряжения, управляющий вход второго ключа объединен с первым входом второго сумматора и соединен с выходом второго компаратора с гистереэисной характеристикой, второй вход второго сумматора является шиной напряжения смещения, а выход соединен с входом второго вероятностного реле, первый вход первого компаратора с гистерезисной характеристикой объединен с информационным входом первого ключа и соединен с выходом второго вероятностного реле, второй вход первого компаратора с гистерезисной характеристикой является шиной опорного напряжения, а выходы первого и второго ключей являются шинами нулевого потенциала, отличающийся тем, что, с целью повышения точности преобразования непрерывных сигналов, существенно изменяющихся в процессе преобразования в код в условиях воздействия низкочастотной и высокочастотной помех, в него введены второй и третий инверторы, первый и второй переключатели и блок управления, причем вход вычитания реверсивного счетчика объединен с первым входом блока управления и соединен с выходом второго инвертора, вход суммирования объединен с вторым входом блока управления и соединен с выходом третьего

инвертора, а вход установки является шиной Сброс, кодовые входы блока управления объединены с входами цифроаналогового преобразователя соответственно, третий вход блока управления объединен с входом второго инвертора и подключен к выходу первого компаратора с гистерезисной характеристикой, первый выход соединен с управляющим входом первого переключателя, а второй выход - с управляющим входом второго переключателя, третий вход второго сумматора и вход первого инвертора объединены и соединены с выходом фильтра верхних частот, вход третьего инвертора подключен к выходу второго компаратора с гистерезисной характеристикой, выход первого переключателя соединен с четвертым входом первого сумматора, а выход второго переключателя - с четвертым входом второго

#«М//Ш о-44

0

5

0

5

0

сумматора, первые информационные входы первого и второго переключателей являются шиной напряжения дополнительного смещения, а вторые информационные входы - шиной нулевого потенциала„

2„ Преобразователь по п. 1, отличающийся тем, что блок управления содержит два элемента И, элементы И-НЕ, ИЛИ-НЕ, ИЛИ, ИСКЛЮЧАКРЕЕ ИЛИ, элемент задержки, расширитель импульсов и триггер,, причем вход элемента задержки и первый вход элемента И-НЕ объединены и являются первым входом блока, выход элемента задержки соединен с первым входом элемента ИЛИ, второй вход элемента И-НЕ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход - с первым входом первого элемента И, второй вход которого является вторым входом блока, а выход соединен с S- входом триггера, R-вход которого соединен с выходом элемента ИЛИ, D- и С-вход триггера объединены и являются шиной нулевого потенциала, а инверсный и прямой выходы являются первым и вторым выходами блока, входы элемента ИЛИ-НЕ являются кодовыми входами блока, первый вход второго элемента И и первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ объединены и соединены с выходом элемента ИЛИ-НЕ, вход расширителя импульсов является третьим входом блока, а выход соединен с вторым входом второго элемента И, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход элемента ИЛИ объединены и соединены с выходом второго элемента И.

Ј

.л

2W. 2.

-

г6x5У

Сдрос о

1

5sJ

/2

«Л-.

.7У

16х БУ15

a z&ti.6ut$

г.

f

UA,

Я

налерехл. 1В

О 1бых.6У15

на перекл. П

26

25

h

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1181116A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1215164A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-07—Публикация

1989-04-04—Подача