ход которого соединен с адресным входом первого блока постоянной памяти, йнформационньй выход которого подключен к информационному входу седьмого регистра, выход третьего сумматора соединен с адресным входом второго блока постоянной памяти, информационный выход которого подключен к второму входу второго сум матора, информационный вход блока памяти соединен с выходом первого умножителя, первый выход блока синхронизации подключён к управляющему входу третьего регистра и счетному

входу счетчика, второй RI.IXCUI; блока синхронизации соединен с управляющими входами первого и второго регистров, третий, четвертый, пятый, шестой и седьмой выходы блока синхронизации подключены к управляющим входам соответственно третьего регистра,блока памяти, первого регистра, шестого и седьмого регистров, а восьмой вьпсод блока синхронизации подключен к входу обнуления счетчика и управляющим входам четвертого пятого, восьмого и девятого регистров .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Цифровой фильтр | 1990 |

|

SU1739483A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство для вычисления полиномов с фиксированными коэффициентами | 1982 |

|

SU1019456A1 |

УСТРОЙСТВО ДЛЯЦИФРОВОЙ ФИЛЬТРАЦИИ, содержащее первый блок постоянной памяти, первый резистор, установочный вход которого является информационным входом устройства, первый умножитель, выход которого соединен с первым входом первого сумматора, выход кдторого подключен к информационному входу второго регистра, информационный выход которого подключен к информационному входу третьего регистра, информационный выход которого соединен с первым входом первого умножителя, установочный вход третьего регистра подключен к информационному выходу четвертого регистра, информационный вход которого является входом задания первого коэффициента устройства, второй вход первого сумматора соединен с информационным выходом пятого регистра, информационный вход которого является входом задания второго коэффициента устройства, второй сумматор, шестой регистр, седьмой регистр, информационный выход которого соединен с первым входом блока сравнения и первым входом второго умножителя, выход которого подключен к первому входу третьего сзт матора, второй вход которого соединен с информационным выходом восьмого регистра, информационный вход которого является i входом задания третьего коэффициента устройства, второй вход второго (Л умножителя соединен с информационным выходом девятого регистра, информационный вход которого является .входом задания, четвертого коэффициента устройства, входом задания пятого коэффициента которого является второй вход блока сравнения, выход которого является информационным выходом устройства, блок синхронизасо ции, отличающееся тем, 00 00 что, с целью повьппения быстродействия и сокращения аппаратурных затрат, со оно содержит второй блок постоянной памяти, блок памяти и счетчик, информационньй выход которого соединен с вторым входом первого умножителя и информационным входом первого регистра, информационный выход которого подключен к адресному входу блока памяти, информационный выход которого соединен с первым входом второго сумматора, выход которого подключен к информационному входу шестого регистра, информационный вы

Изобретение относится к цифровой вычислительной технике и предназначено для определения положения сигнала произвольной формы относительнб заданного уровня в условиях помех и может быть использовано при решении задач обнаружения и фильтрации.

Известно устройство для фильтрации (аналоговое вероятностное реле), содержащее нелинейный интегратор с положительной и отрицательной обратной связью, ориентированное на обработку непрерывного сигнала С11.

Однако это устройство обеспечиваетг лишь квазиоптимальное, решение о состоянии полезного сигнала относительно заданного уровня в условиях помех, так как получены в классе RC-цепей из условия приближенного равенства выходного сигнала этого устройства апостериорной вероятности V(t) tP n(t) a/Z(t)3 пребывания полезного сигнала n(t) над уровнем а при наличии сигнала ) n(t) + + S(t), где S(t) - помеха.

Оптимальное решение дает цифровая обработка дискретных отсчетов Z Z(t)/t .vA.t (it - шаг дискретизации) наблюдаемого сигнала Z(t) по нелинейному алгоритму, описанному в С2. Согласноэтому алгоритму, апостериорная вероятность V; P(Un a/Zn прёбьгоания полезного сигнала Uv над уровнем а при наличии наблюдения Z находится по формуле

dv.}

(1)

гдeJi(Zи) P(ZH/UH a)/P(Z/UH а) отношение правдоподобия, вычисляемое при гауссовой помехе 5 и равномерном распределении полезного сигнала по формуле

),Savoi} p(

С2)

где с , d, с, d - const.

а V;; (1-Яд, - q) + (3)

результат прогноза апостериорной вероятности, полученной по апостериорной вероятности , вьиисленной в предьщущий дискретный момент времени п-1, с учетом априорных вероятностей перекода q PdJ ) , Ч« P(UM 6 a/Uii-i a) , представляющих

собой условные вероятности перехода полезного сигнала за шаг дискретизации из состояния Ur,- а в состояние а и наоборот.

Принятие решения 31лС(0,1| о состоянии сигнала UQ относительно порога а производится по критерию максимума апостериорной вероятности, согласно следующему правилу:

/1, если V 0,5 , . OH

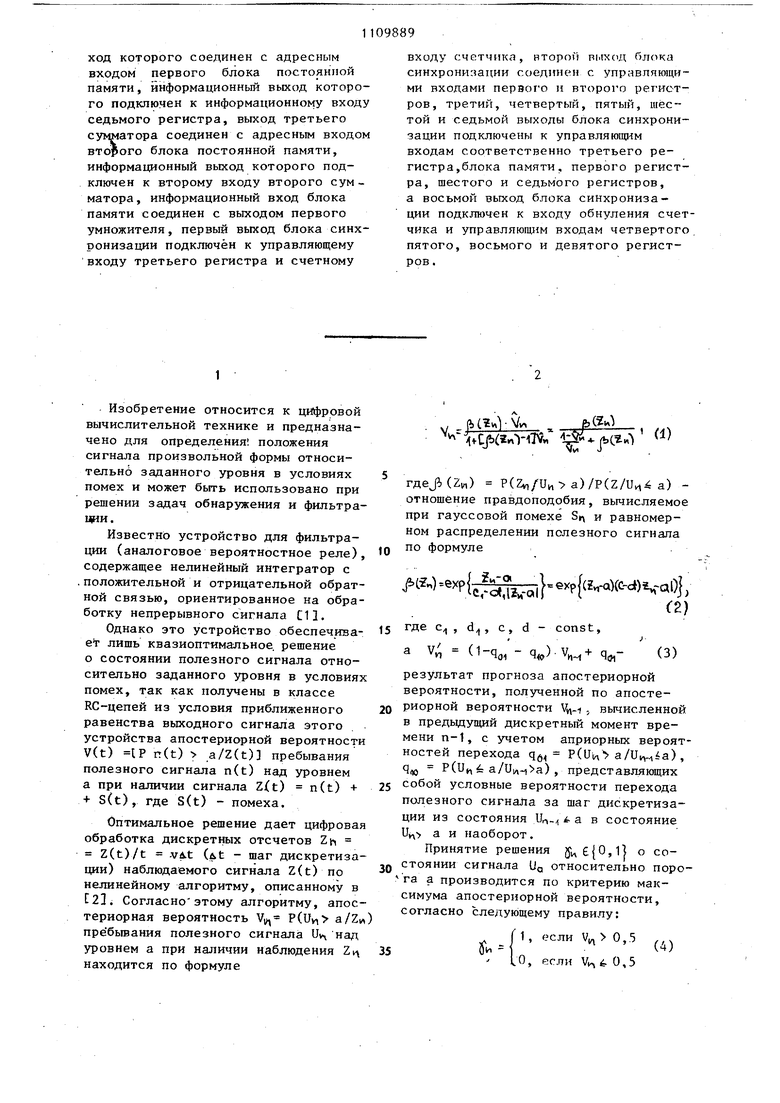

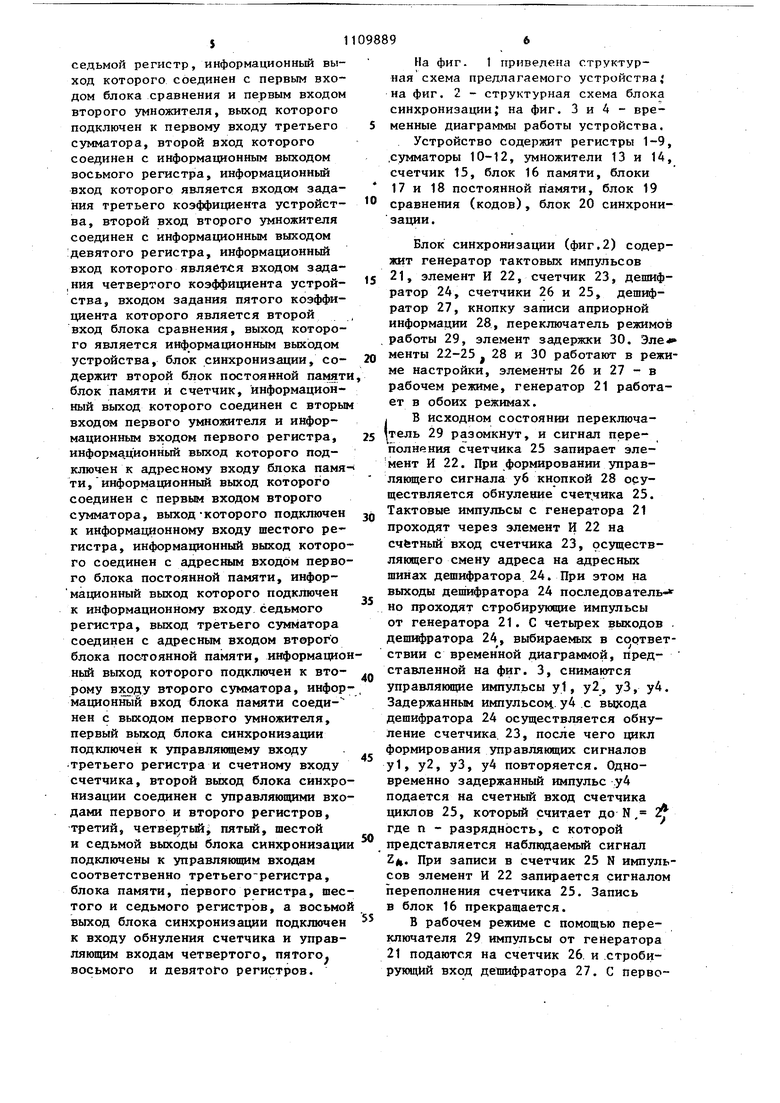

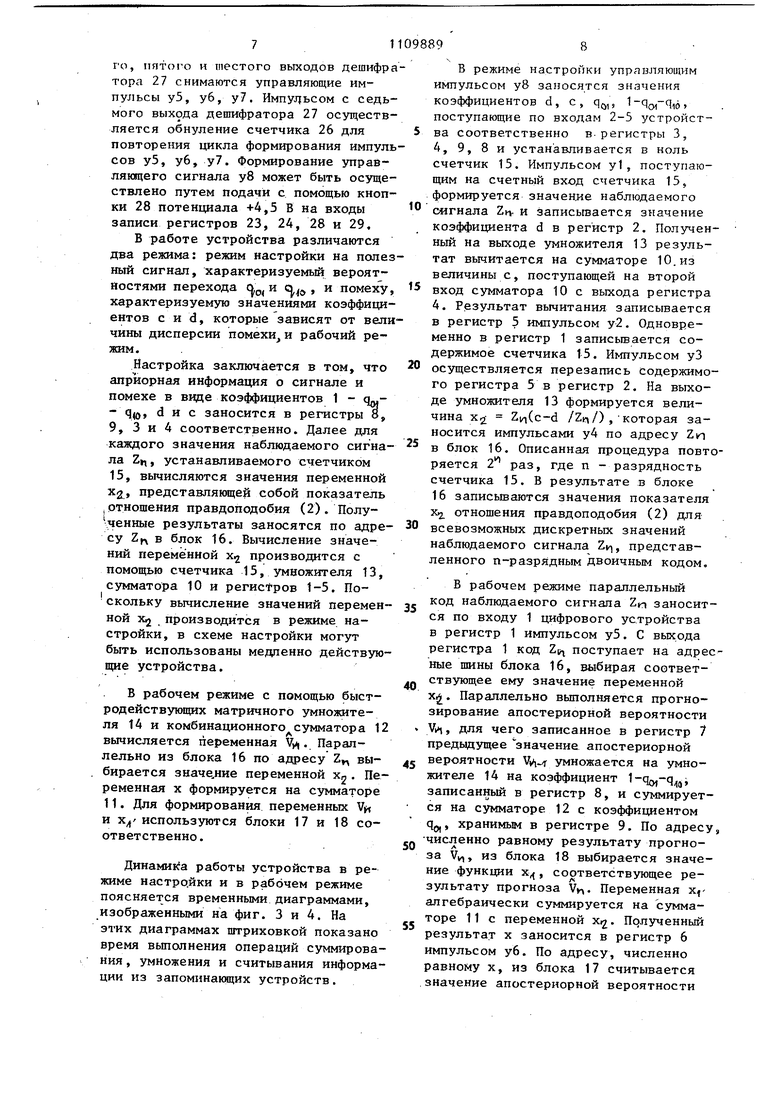

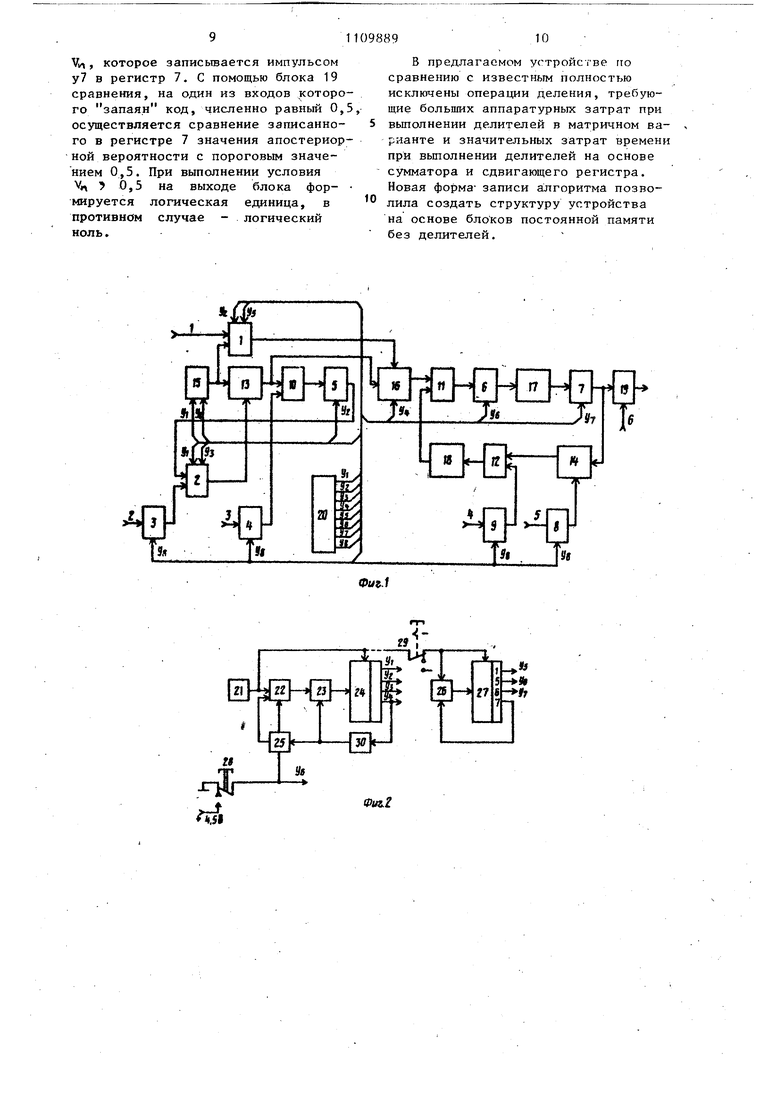

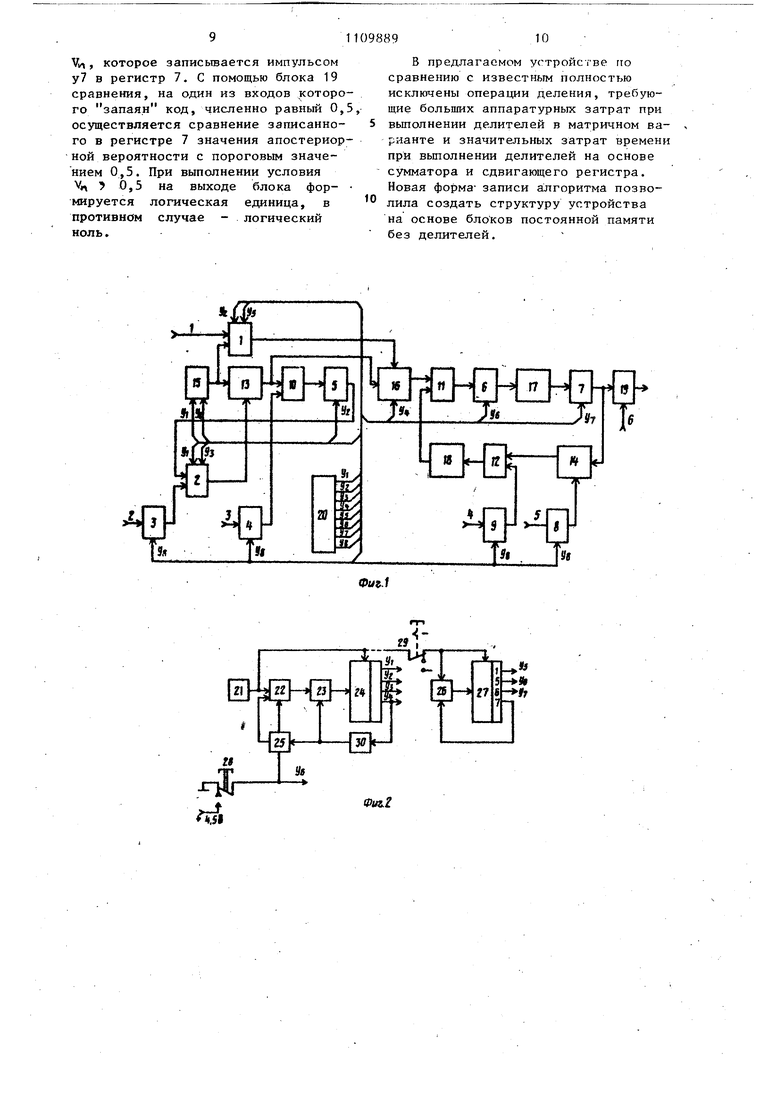

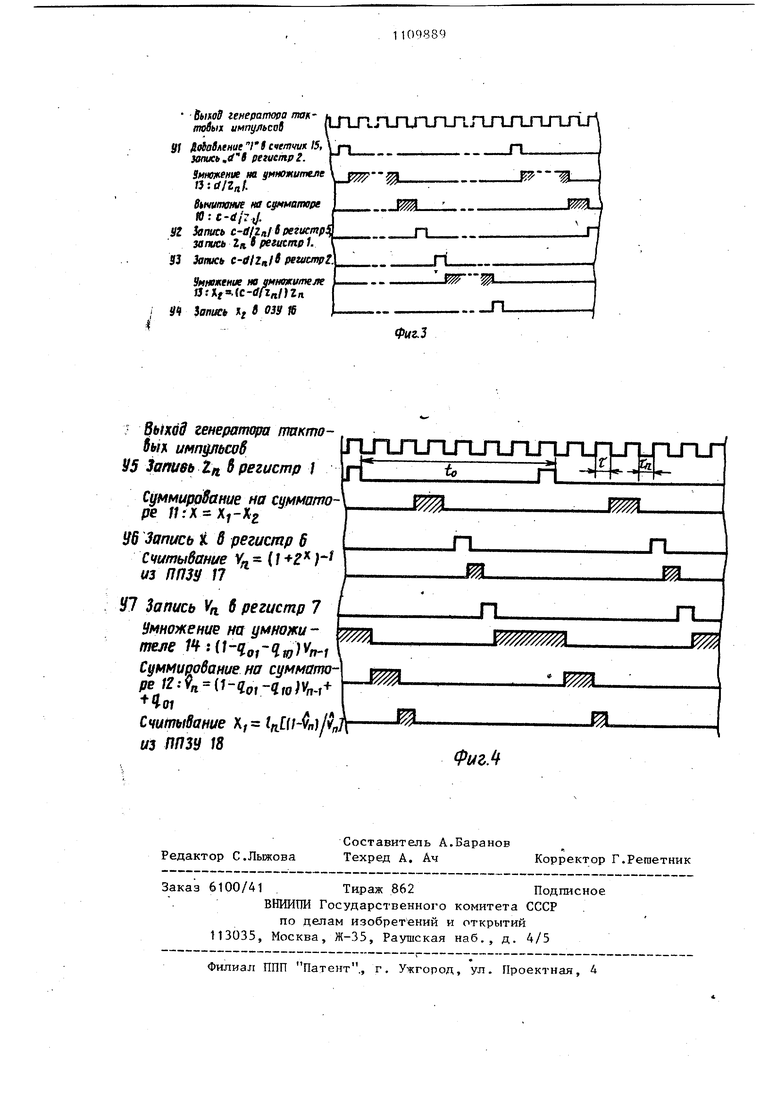

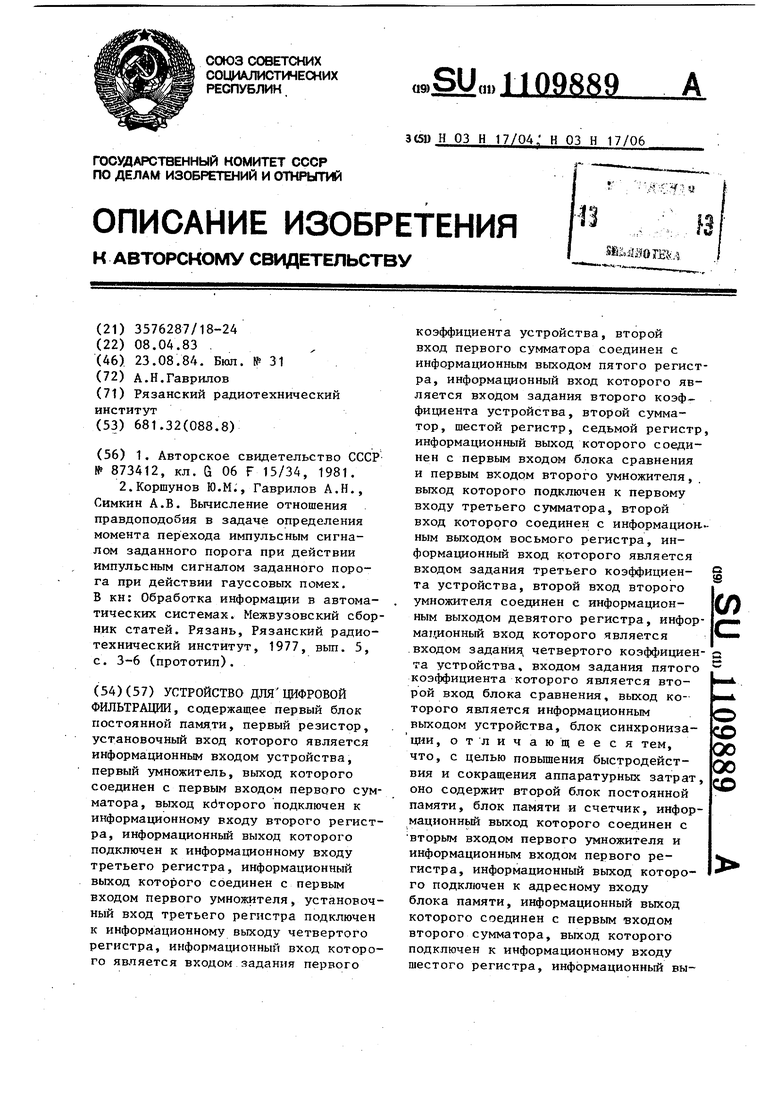

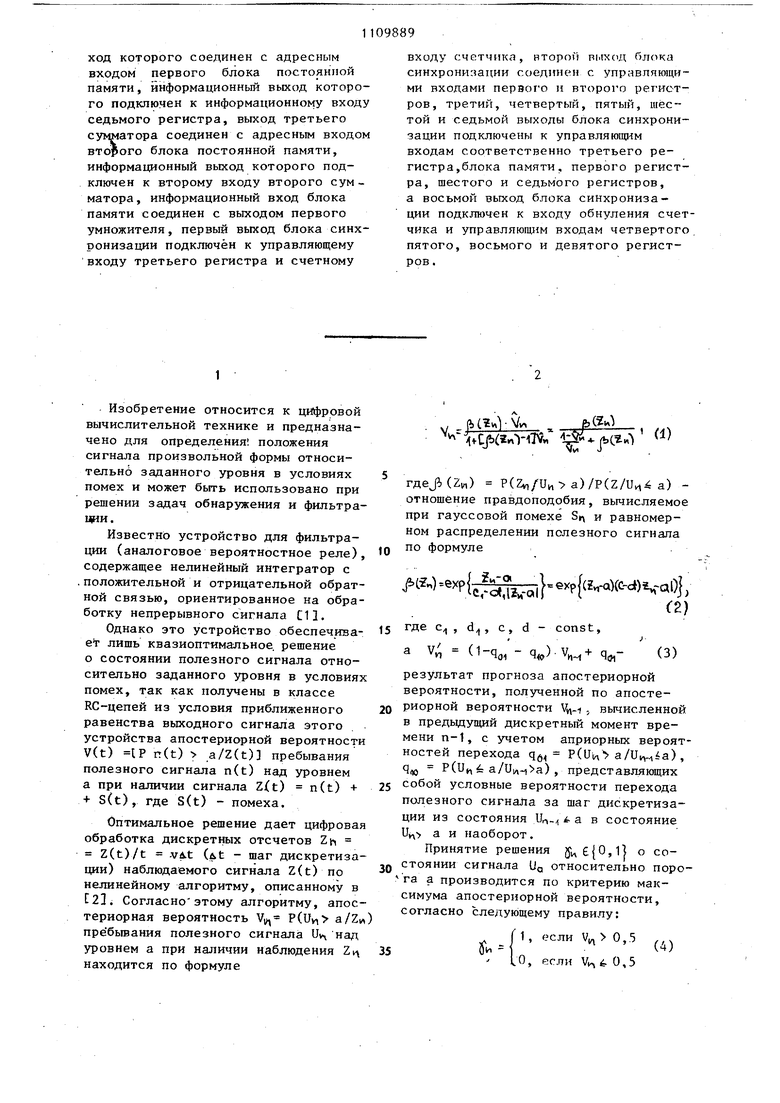

LO, если 0,5 Решение Vn 1 ук.-г ЫГаг.1- па сост ние полезного сигнала ЬЦ ,ч, решение к1 « сосугояние U 4 а. А-огорйтм (1)-(4) при а и может быть реализован с помощью цифрового специализир ованного вычислительного устройства, которое является наиболее близким по технической сущности к изобретению и которое содержит пе вый, второй,третийJ четвертый, пятый, шестой, седьмой, восьмой и девятый регистры: первый, второй и третий сумматоры, первый и второй умножители, первый и второй делители постоянное запоминающее устройство J устройство сравнения кодов; устройство управления, причем, первый вход вычислительного устройства соединен с входом первого регистра, выход которого подключен к первому входу первого умножителя, второй вход которого соединен с выходом второго регистра, подключенного сво им первым входом к выходу третьего регистра-; выход первого умножителя соединен с первым входом пятого регистра и первым входом первого сумматора, второй вход которого подклю чен к выходу четвертого регистра; выход первого сумматора подключен к второму входу второго регистра и постоянному запоминающему устройств выход которого -соединен с первыми входами первого делителя и второго сумматора, выход которого подключен к второму входу первого делителя, соединенного своим выходом с входом шестого регистра, выход которого подключен к первому входу устройств сравнения кодов и второго умножител второй вход которого соединен с выходом восьмого регистра, а выход по ключен к первому входу третьего С5 матора, второй вход которого соединен с выходом седьмого регистра, а первый и второй выходы подключены соответственно к первому и второму входам второго делителя, выход которого соединен через девять й регистр с вторым .входом второго сумма тора, второй, третий, четвертый и пятый входы устройства соединены с информационными входами соответст венно третьего, четвертого, седьмог и восьмого регистров шестой вход устройства соединен с вторым входом устройства сравнения кодов, выход которого подключен к выходу устройства, перпый )Д устроГкгтва управления соединен с первым управ- . ляющим входом второго регистра и управляющим входом первого регистра, второй выход устройства управления соединен с вторым управляющим входом пятого регистра, третий выход устройства управления соединен с вторым управляющим входом второго регистраi четвертый выход устройства управления соединен с.первым управляющим входом пятого регистра и управляющим входом девятого регистра} пятый выход устройства управления соединен с управляющим входом шестого регистра шестой выход устройства управления соединен с управлякщими входами третьего, четвертого., седьмого и восьмого регистров. Известное устройство обеспечивает более высокую точность обработки по сравнению с аналоговыми вероятностными реле, поскольку в отличие от них цифровое устройство реализует оптимальный алгоритм (1)-(4). Однако сложность аппаратурной реализации и низкое быстродействие описанного цифрового устройства ограничивает область его использования. Целью изобретения является повышение быстродействия и сокращение аппаратурных затрат. Указанная цель достигается тем, что устройство для цифровой фильтра ции, содержащее первый блок постоянной памяти, первый регистр , установочный вход которого является информационным входом устройства, первый умножитель, выход которого соединен с первым входом первого сумматора, выход которого подключен к информационному входу второго регистра , информационный выход которого подключен к информационному входу третьего регистра, информационный выход которого соединен с первым входом первого умножителя, установочный вход третьего регистра подключен к информационному выходу четвертого регистра, информационный вход которого является входом задания .первого коэффициента устройства, второй вход первого сумматора соединен с информационным ыходом пятого регистра, информационный вход которого является входом задания второго коэффициента устройства, второй сумматор, шестой регистр. седьмой регистр, информационный выход которого соединен с первым входом блока сравнения и первым входом второго умножителя, выход которого подключен к первому входу третьего сумматора, второй вход которого соединен с информационным выходом восьмого регистра, информационный вход которого является входсм задания третьего коэффициента устройства, второй вход второго умножителя соединен с информационным выходом :девятого регистра, информационный вход которого являет-ся входом зада,ния четвертого коэффициента устройства, входом задания пятого коэффициента которого является второй вход блока сравнения, выход которого является информационным выходом устройства, блок синхронизации, содержит второй блок постоянной памят блок памяти и счетчик, информационный выход которого соединен с вторы входом первого умножителя и информационным входом первого регистра, информа ционный выход которого подключен к адресному входу блока памя ти,информационный выход которого соединен с первым входом второго сумматора, выход-которого подключен к информационному входу шестого регистра, информационный выход которо го соединен с адресным входом перво го блока постоянной памяти, информационный выход которого подключен к информационному входу седьмого регистра, выход третьего сзп матора соединен с адресным входом второго блока постоянной памяти, информацио ный выход которого подключен к второму входу второго сумматора, инфор мационный вход блока памяти соеди- нен с выходом первого умножителя, первый выход блока синхронизации подключен к управлякнцему входу третьего регистра и счетному входу счетчика, второй выход блока синхро низации соединен с управляющими вхо дами первого и второго регистров, третий, четве1)тьй; пятый, шестой и седьмой выходы блока синхронизаци подключены к управляющим входам соответственно третьего регистра, блока памяти, первого регистра, шес того и седьмого регистров, а восьмо выход блока синхронизации подключен к входу обнуления счетчика и управляющим входам четвертого, пятого, восьмого и девятого регистров. На фиг. 1 приведена структурная схема предлагаемого устройства, на фиг. 2 - структурная схема блока синхронизации; на фиг. 3 и 4 - временные диаграммы работы устройства. Устройство содержит регистры 1-9, .сумматоры 10-12, умножители 13 и 14, счетчик 15, блок 16 памяти, блоки 17 и 18 постоянной памяти, блок 19 сравнения (кодов), блок 20 синхронизации . Блок синхронизации (фиг,2) содержит генератор тактовых импульсов 21, элемент И 22, счетчик 23, дешифратор 24, счетчики 26 и 25, дешифратор 27, кнопку записи априорной информации 28, переключатель режимов работы 29, элемент задержки 30. Эле менты 22-25 28 и 30 работают в режиме настройки, элементы 26 и 27 - в рабочем режиме, генератор 21 работает в обоих режимах. i В исходном состоянии переключа1тель 29 разомкнут, и сигнал переполнения счетчика 25 запирает эле- мент И 22. При формировании управляющего сигнала у6 кнопкой 28 осуществляется обнуление счет,чика 25. Тактовые импульсы с генератора 21 проходят через элемент И 22 на счётный вход счетчика 23, осуществляющего смену адреса на адресных шинах дешифратора 24. При этом на выходы депшфратора 24 последователь- но проходят стробирующие импульсы от генератора 21. С четырех выходов . дещ1 ратора 24, выбираемых в соответствии с временной диаграммой, представленной на фиг. 3, снимаются управляющие импульсы у1, у2, уЗ, у4. Задержанным импульсом. у4 с выхода дешифратора 24 осуществляется обнуление счетчика. 23, после чего цикл формирования управляющих сигналов у1, у2, уЗ, у4 повторяется. Одновременно задержанный импульс .у4 подается на счетный вход счетчика циклов 25, который считает до N , где п - разрядность, с которой представляется наблюдаемый сигнал . При записи в счетчик 25 N импульсов элемент И 22 запирается сигналом переполнения счетчика 25. Запись в блок 16 прекращается. В рабочем режиме с помощью переключателя 29 импульсы от генератора 21 подаются на счетчик 26. и стробирующИй вход дешифратора 27. С иервого, пято1о и шестого выходов дешифра тора 27 снимаются управляющие импульсы у5, у6, у7. Импу-цьсом с седьмого выхода дешифратора 27 осуществляется обнуление счетчика 26 для повторения цикла формирования импуль сов у5, у6, у7. Формирование управляющего сигнала у8 может быть осуществлено путем подачи с помощью кнопки 28 потенциала +4,5 В на входы записи регистров 23, 24, 28 и 29, В работе устройства различаются два режима: режим настройки на полез ный сигнал, характеризуемый вероятйостями перехода UQ и сз. , и помеху характеризуемую значениями коэффициентов с и d, которые зависят от вели чины дисперсии помехи, и рабочий реНастройка заключается в том, что априорная информация о сигнале и помехе в виде коэффициентов 1 - qjj,- q, d и с заносится в регистры 8, 9, 3 и 4 соответственно. Далее для каждого значения наблюдаемого сигнала Z|,, устанавливаемого счетчиком 15, вычисляются значения переменной Х2, представлянлцей собой показатель ,отношения правдоподобия (2). Полученные результаты заносятся по адресу Zf в блок 16. Вычисление значений переменной х производится с помощью счетчика 15, умножителя 13, сумматора 10 и регистров 1-5. Поскольку вычисление значений переменной Х2 производится в режиме настройки, в схеме настройки могут быть использованы медпенно действующие устройства. В рабочем режиме с помощью быстродействующих матричного умнояоителя 14 и комбинационного сумматора 12 вычисляется переменная V, Параллельно из блока 16 по адресу Z вы, бирается значе нне переменной Xj . Переменная X формируется на сумматоре 11. Для формирования переменных V и используются блоки 17 и 18 соответственно. Динамика работы устройства в режиме настройки и в рабочем режиме поясняется временными диаграммами, изображенными на фиг. 3 и 4. На этих диаграммах штриховкой показано время вьтолнения операций суммирования , умножения и считывания информации из запоминакицих устройств. В режиме настройки управляющим импульсом у8 заносятся значения коэффициентов d, с, q,, , поступающие по входам 2-5 устройства соответственно в-регистры 3, 4, 9, 8 и устанавливается в ноль счетчик 15. Импульсом у1, поступающим на счетный вход счетчика 15, формируется значение наблюдаемого сигнала и записывается значение коэффициента d в регистр 2. Полученный на выходе умножителя 13 результат вычитается на сумматоре 10.из величины с, поступающей на второй вход сумматора 10 с выхода регистра 4. Результат вычитания записывается в регистр 5 импульсом у2, Одновременно в регистр 1 записьшается содержимое счетчика 15. Импульсом уЗ осуществляется перезапись содержимого регистра 5 в регистр 2. На выходе умножителя 13 формируется величина х, Zi(c-d ) ,которая заносится импульсами у4 по адресу Zvn в блок 16. Описанная процедура повторяется 2 раз, где п - разрядность счетчика 15. В результате в блоке 16 записьшаются значения показателя отношения правдоподобия (2) для всевозможных дискретных значений наблюдаемого сигнала Z, представленного п-разрядным двоичным кодом. В рабочем режиме параллельный код наблюдаемого сигнала Zn заносится по входу 1 цифрового устройства в регистр 1 импульсом у5. С выхода регистра 1 код Zi/ поступает на адресные шины блока 16, выбирая соответствующее ему значение переменной х. Параллельно выполняется прогнозирование апостериорной вероятности , для чего записанное в регистр 7 предыдущее значение апостериорной вероятности умножается на умножителе 14 на коэффициент 1-qo, записанный в регистр 8, и суммируется на сумматоре 12 с коэффициентом , хранимым в регистре 9. По адресу, -численно равному результату прогноза Vv), из блока 18 выбирается значение функции x,j, соответствующее результату прогноза V. Переменная х алгебраически суммируется на сумматоре 11 с переменной х. Полученный результат х заносится в регистр 6 импульсом у6. По адресу, численно равному X, из блока 17 считывается значение апостериорной вероятности Vv, которое записьшается импульсом у7 в регистр 7. С помощью блока 19 сравнения, на один из входов которо го запаян код, численно равньй 0, осуществляется сравнение записанного в регистре 7 значения апостериор ной вероятности с пороговым значением 0,5. При выполнении условия V У 0,5 на выходе блока формируется логическая единица, в противном случае - логический ноль. В предлагаемом устройсчве по сравнению с известным полностью исключены операции деления, требующие больших аппаратурных затрат при выполнении делителей в матричном варианте и значительных затрат времени при вьшолнении делителей на основе сумматора и сдвигающего регистра. Новая форма- записи алгоритма позволила создать структуру устройства на основе блоков постоянной памяти без делителей.

JTЛJтnлJ-.ЛJaлJ J

rr

1 Выход генератора та ктоенератора такта- /

sflbcog|n/inJiJiJiJTJ7M i.O

Ьыи имт

Zn б регистр / Н toг - F-f--Pk У5 Запиеь

CuMMupoSctHue на сумматоре (Г;Х Х,-Х2

У6 Запись t в регистр 6 Считывание ) из ППЗУ 17

У7 Запись УЛ б регистр 7

Умножение на умножи теле nt{1-4oj-ci jVf j

Суммирование на сумматоре 1г:9п (1-11о,-ч1,.+ 4отл л

Считывание X/ из ППЗУ 18

.,,JM-.:

П.

Фиг.3

п

гт

ж

.Ш

п

:ШШт.

Ж

ФигМ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вероятностное реле | 1979 |

|

SU873412A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычисление отношения правдоподобия в задаче определения момента перехода импульсным сигналом заданного порога при действии импульсным сигналом заданного порога при действии гауссовых помех | |||

| В кн: Обработка информации в автоматических системах | |||

| Межвузовский сборник статей | |||

| Рязань, Рязанский радиотехнический институт, 1977, вьш | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-08—Подача