Изобретение относится к электротехнике и может быть использовано в устройствах защиты сверхпроводящих магнитных систем.

Цель изобретения повышение чувствительности и быстродействия датчика путем осуществления компенсации реактивного напряжения с высокой точностью.

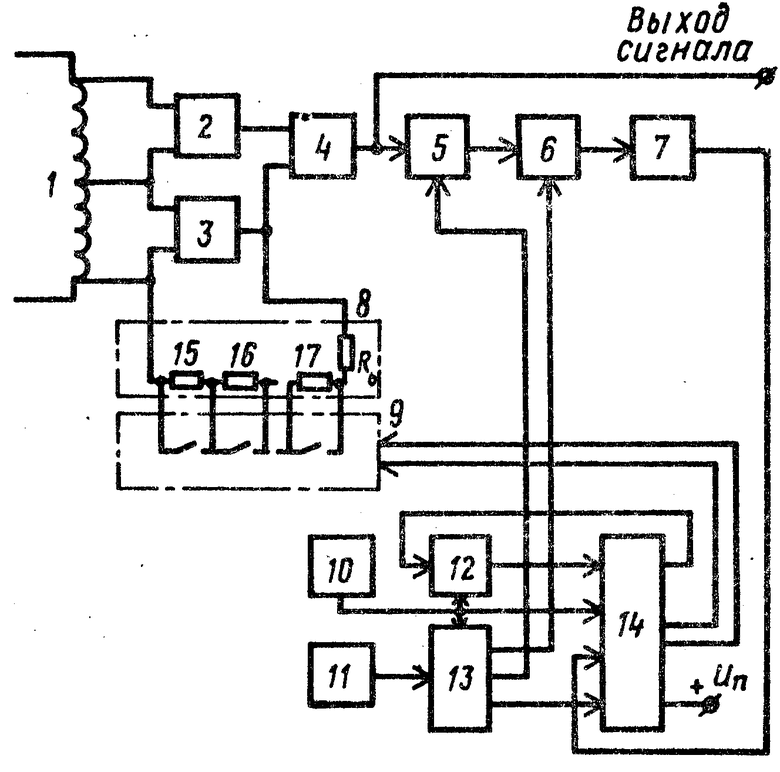

На чертеже показана функциональная схема датчика нормальной фазы.

Датчик содержит сверхпроводящую обмотку 1 с отводом от середины, два дифференциальных усилителя 2 и 3, сумматор 4, ключ 5, интегратор 6, компаратор 7, блок 8 резисторов, блок 9 ключей, блок 10 внешнего запуска, генератор 11 тактовых импульсов, триггер 12 разрешения, регистр 13 сдвига и регистр 14 последовательно приближения, причем неинвертирующие входы дифференциальных усилителей 2 и 3 подсоединены к концам обмотки 1, а инвертирующие входы к отводу от средней точки обмотки 1, выходы дифференциальных усилителей 2 и 3 подключены к входу сумматора 4, выход которого через ключ 5 связан с входом интегратора 6, выход интегратора 6 подключен к входу компаратора 7, выход которого, в свою очередь, связан с информационным входом регистра 14 последовательного приближения, выход блока 10 внешнего запуска связан с входом установки в единицу триггера 12, входом установки регистра 13 сдвига и входом пуска регистра 14 последовательного приближения, при этом тактовый вход регистра 13 сдвига связан с выходом генератора 11 тактовых импульсов, а первый информационный выход регистра 13 сдвига с входом сброса интегратора 6, второй выход регистра 13 сдвига с входом управления ключа 5, а третий с тактовым входом регистра 14 последовательного приближения, выход "Конец преобразования" которого соединен с входом сброса триггера 12, а информационные выходы регистра 14 последовательного приближения связаны с соответствующими входами управления ключей в блоке ключей 9, причем каждый ключ шунтирует соответствующий резистор в последовательной цепи резисторов 8, которая включена в цепь обратной связи дифференциального усилителя 3.

Датчик работает следующим образом.

В начале цикла заведения тока в сверхпроводящую обмотку 1, когда ток мал и переход обмотки в нормальное состояние маловероятен, производится компенсация реактивного напряжения. Начало компенсации определяется подачей от блока 10 внешнего запуска команды "Пуск" на входы установки триггера 12 и регистра 13 сдвига, а также на вход "Пуск" регистра последовательного приближения 14. При этом триггер 12 устанавливается в единичное состояние и подает на вход разрешения регистра 14 последовательного приближения сигнал разрешения работы. Регистр 14 устанавливается в исходное состояние, имеющее логическую "1" в старшем разряде и "0" в остальных, а регистр 13 сдвига в исходное состояние, имеющее "1" на первом выходе и логические "0" на втором и третьем выходах. Логическая "1" с первого выхода регистра 13 сдвига сбрасывает интегратор 6 в нуль, ключ 5 разомкнут, так как на его управляющий вход подан сигнал логического "0" с второго выхода регистра 13 сдвига, а логическая "1" с выхода старшего разряда регистра 14 размыкает соответствующий ключ в блоке 9 ключей, и в цепь обратной связи дифференциального усилителя 3 подключается сопротивление 15 из блока 8 резисторов. Поскольку компенсация осуществляется в отсутствие сигнала нормальной фазы (Uнф=0), то после подключения резистора 15 на выходе сумматора 4 устанавливается напряжение раскомпенсации, равное

Uр=К4(U1K2-U2K3), где Uр напряжение раскомпенсации;

U1, U2 напряжение на первой и второй половинах обмотки;

К2, К3 коэффициенты передачи дифференциальных усилителей 2 и 3;

К4 коэффициент передачи сумматора 4.

При поступлении первого тактового импульса от генератора 11 регистр 13 сдвига устанавливается в состояние логической "1" на втором выходе и логического "0" на первом и третьем выходах, тем самым снимая сигнал сброса с входа сброса интегратора 6 и замыкая ключ 5. На выходе интегратора 6 появляется линейно нарастающее напряжение от входного сигнала. На выходе компаратора 7 устанавливается сигнал логической "1" при положительной полярности выходного напряжения интегратора 6, что свидетельствует о недостаточной величине коэффициента передачи дифференциального усилителя 3, и при отрицательной полярности логический "0", что говорит о слишком большой величине коэффициента передачи дифференциального усилителя 3. По второму такту генератора 11 регистр 13 сдвига устанавливается в состояние логического "0" на первом и втором выходах и логической "1" на третьем выходе. При этом ключ 5 размыкается и заряд интегратора прекращается. Перепад 0/1 на третьем выходе регистра 13 сдвига используется как тактовый сигнал для регистра 14 последовательного приближения, который по этому перепаду устанавливается в состояние, имеющее логический "0" или логическую "1" на первом старшем выходе в зависимости от того, какой сигнал, логическая "1" или логический "0", поступает с выхода компаратора 7 на информационный вход регистра 14. На втором выходе регистра 14 устанавливается сигнал логической "1", а на остальных выходах логические "0", подключая в цепь обратной связи дифференциального усилителя 3 резистор 16 из блока 8 резисторов и оставляя подключенным и отключая резистор 15 в зависимости от полярности сигнала раскомпенсации. По следующему такту генератора 11 регистр 13 сдвига устанавливается в исходное логическое состояние и цикл повторяется сначала, но во втором цикле логическое состояние первого выхода регистра 14 сохраняется, второй выход меняет свое состояние в зависимости от сигнала с выхода компаратора 7 и третий выход устанавливается в состояние логической "1", подключая в цепь обратной связи дифференциального усилителя 3 следующий резистор, и так далее. Величина сопротивлений 15, 16, 17 в блоке 8 резисторов выбирается по формуле

Ri+1=  R1 где i=1, 2 N.

R1 где i=1, 2 N.

Резистор Ro в блоке 8 резисторов служит для ограничения минимального коэффициента передачи дифференциального усилителя 3 и равен

Ro=  Ri

Ri

По истечении n циклов, в которых производился последовательный перебор резисторов в цепи обратной связи дифференциального усилителя 3, резистор 14 выдает сигнал "Конец преобразования", сбрасывающий в нуль триггер 12, который в свою очередь запрещает работу регистра 14, предохраняя систему от случайных сбоев. На выходе сумматора 4 формируется минимальное напряжение раскомпенсации.

Точность компенсации определяется количеством подключаемых в цепь обратной связи дифференциального усилителя 3 резисторов, откуда выбирается разрядность регистра 14 последовательного приближения. Практически устройство может быть реализовано с использованием стандартных элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивной дельта-модуляции | 1981 |

|

SU1149396A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Трансверсальный фильтр | 1981 |

|

SU1083344A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Цифровой кондуктометр | 1986 |

|

SU1374144A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| УСТРОЙСТВО КОНТРОЛЯ МЕСТОПОЛОЖЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 1992 |

|

RU2042922C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

Изобретение относится к электротехнике, в частности к релейной защите. Цель изобретения повышение чувствительности и быстродействия путем осуществления компенсации реактивного напряжения с высокой точностью. Датчик содержит усилители 2, 3, сумматор 4, ключ 5, интегратор 6, выключенный на входе компаратора 7, блок 8 резисторов, блок ключей 9, блок 10 внешнего запуска, генератор 11 тактовых импульсов, триггер 12 разрешения, регистр 13 сдвига и регистр 14 последовательного приближения. В начале цикла заведения тока в сверхпроводящую обмотку 1, когда ток мал и переход обмотки в нормальное состояние маловероятен, производится компенсация реактивного напряжения. Начало компенсации определяется подачей от блока 10 внешнего запуска команды "Пуск" на входы установки триггера 12 и регистра 13 сдвига, а также на вход "Пуск" регистра 14 последовательного приближения. Регистр 14 последовательного приближения устанавливается в исходное состояние, имеющее логическую "1" в старшем разряде и "0" в остальных, а регистр 13 сдвига имеет "1" на первом выходе и логические "0" на втором и третьем выходах. Логическая "1" с первого выхода регистра 13 сдвига сбрасывает интегратор 6 в нуль, ключ 5 разомкнут, а логическая "1" с выхода старшего разряда регистра 14 последовательного приближения размыкает соответствующий ключ в блоке 9 ключей, и в цепь обратной связи дифференциального усилителя 3 подключается резистор из блока 8 резисторов. 1 ил.

ДАТЧИК НОРМАЛЬНОЙ ФАЗЫ СВЕРХПРОВОДЯЩЕЙ КАТУШКИ С ОТВОДОМ ОТ СЕРЕДИНЫ С АВТОМАТИЧЕСКОЙ КОМПЕНСАЦИЕЙ РЕАКТИВНОГО НАПРЯЖЕНИЯ, содержащий два дифференциальных усилителя, неинвертирующие входы которых соединены с клеммой для подключения к средней точке сверхпроводящей катушки, а инвертирующие с клеммами для соединения с крайними ее выводами, сумматор, входы которого подключены к выходам дифференциальных усилителей, отличающийся тем, что, с целью повышения чувствительности и быстродействия датчика путем осуществления компенсации реактивного напряжения с высокой точностью, в него введены ключ, интегратор, компаратор, последовательная цепь из резисторов, блок ключей с N ключами, блок внешнего запуска, генератор тактовых импульсов, триггер, регистр сдвига и M-разрядный регистр последовательного приближения, причем вход интегратора через ключ соединен с выходом сумматора, а выход интегратора соединен с входом компаратора, выход которого соединен с информационным входом регистра последовательных приближений, при этом информационные выходы регистра последовательных приближений соединены с входами управления соответствующих ключей в блоке ключей, а сами ключи включены параллельно резисторам в последовательной цепи из N-резисторов, которая включена в цепь обратной связи одного из дифференциальных усилителей, выход генератора тактовых импульсов подключен к входу регистра сдвига, первый выход которого подключен к входу сброса интегратора, второй выход к входу управления ключом, а третий выход к тактовому входу регистра последовательных приближений, причем выход "Конец преобразователя" регистра последовательных приближений связан с входом сброса триггера, а вход разрешения регистра последовательных приближений с выходом триггера, вход установки которого соединен с выходом блока внешнего запуска, который также связан с входом установки регистра сдвига и с входом запуска регистра последовательных приближений.

| Woods E.L | |||

| - Proc | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| California | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1995-11-20—Публикация

1987-05-12—Подача