Изобретение предназначено для использования в технике цифровой связи и найдет широкое применение в вычислительной технике.

Известно устройство - дельта-сигма-модулятор, содержащее компаратор, цифровой анализатор, блок управления шагом квантования, умножитель сигналов и интегратор 1.

Однако в модуляторе для управления шагом квантования используется линейный участок экспоненты при заряде конденсатора через резистор, что реализует линейный закон компандирования, который не позволяет в области малых сигналов получить приемлемое отношение сигнал-шум ввиду быстрого роста шага квантования на начальном участке. Это снижает динамический диапазон преобразуемого сигнала и точность преобразования сигналов малых уровней.

Наиболее близким к изобретению по технической суш,ности и достигаемому результату является модулятор, содержащий последовательно соединенные интегратор, компаратор, второй вход которого является входом устройства, цифровой анализатор, блок управления шагом квантования, умножитель сигналов, второй вход которого соединен с вторым выходом цифрового анализатора, являющимся выходом устройства, а выход умножителя сигналов соединен с входом интегратора, блок управления шагом квантования включает в себя детектор уровня модуляции, нелинейный ступенчатый генератор тока, два вентиля и интегратор.

Модулятор работает следующим образом. Входной речевой сигнал поступает на первый вход сумматора, на его второй вход поступает сигнал с обратной связи. С выхода сумматора сформированный по амплитуде сигнал поступает на вход тактируемого триггера и далее на сдвиговый регистр. При наличии на выходах тактируемого триггера (один из которых является выходом модулятора) четырех подряд следуюии-;х идентичных символов на выходе детектора уровня модуляции вырабатывается сигнал, открывающий вентиль и включающий интегратор скорости передачи слов.

Сигнал с интегратора скорости передачи слов поступает на нелинейный ступенчатый генератор тока, выходной ток с которого является током двойного интегратора звуковой частоты. Сигнал с выходов тактируемого триггера одновременно поступает через вентиль на входы двойного интегратора звуковой частоты, изменяя таким образом знак его выходного напряжения. Схема работает как система автоматического регулирования, сводя к минимуму ошибку на входе сумматора.

Так, если скорость изменения входного сигнала превышает скорость изменения сигнала на выходе интегратора звуковой частоты в течение более чем четырех тактов работы тактируемого триггера, на выходе интегратора скорости слов вырабатывается уровень напряжения, при котором нелинейный ступенчатый генератор тока увеличивает ток двойного интегратора звуковой частоты и изменяет соотношение скорости изменения входного сигнала и сигнала обратной связи. Таким образом, сигнал обратной связи следит за входным сигналом 2.

Однако модулятор известного устройства имеет высокую чувствительность к изменению элементов схемы, схема чувствительна не только к нарушению отношения резисторов: 153 и 155, 156 и 154, 138 и 143, но также и к абсолютной величине номиналов этих резисторов, кроме того, у нее принципиально низкая температурная стабильность ввиду неполной температурной компенсации, так как термокомпенсирующие транзисторы 147 и 157 принципиально должны работать в режиме токов, отличающихся от токов компенсируемых транзисторов на величину глубины компандирования, которая пропорциональна динамическому диапазону преобразуемого сигнала.

В модуляторе закон изменения шага квантования аппроксимируется кусочно-линейно четырьмя сегментами, что дает низкую хочность реализации заданного закона адаптации. Увеличение динамического диапазона известного устройства входит в противоречие с его температурной стабильностью и точностью.

Таким образом, известное устройство имеет низкий динамический диапазон преобразуемого сигнала и низкую точность воспроизведения закона адаптации.

Цель изобретения - увеличение точности и расширение динамического диапазона преобразуемого сигнала.

Поставленная цель достигается тем, что в устройстве для адаптивной дельтамодуляции, содержащем последовательно соединенные интегратор, компаратор, второй вход которого является входом устройства, цифровой анализатор, блок управления щагом квантования, умножитель сигналов, второй вход которого соединен с вторым выходом цифрового анализатора, являющимся выходом устройства, а выход умножителя сигналов соединен с входом интегратора, блок управления .шагом квантования выполнен в виде последовательно соединенных управляемого источника опорного напряжения, дифференциального усилителя и фильтра нижних частот, выход которого соединен через цепь положительной обратной связи с вторым входом дифференциального усилителя.

В модуляторе реализуется плавная харак теристика изменения шага квантования, глубина и точность которой определяется глубиной положительной обратной связи (отношением резисторов), а динамический диапазон :преобразуемого сигнала может быть рколь угодно большим, так как он определяется отношением максимального выходного напряжения дифференциального усилителя и минимальным шагом квантования.

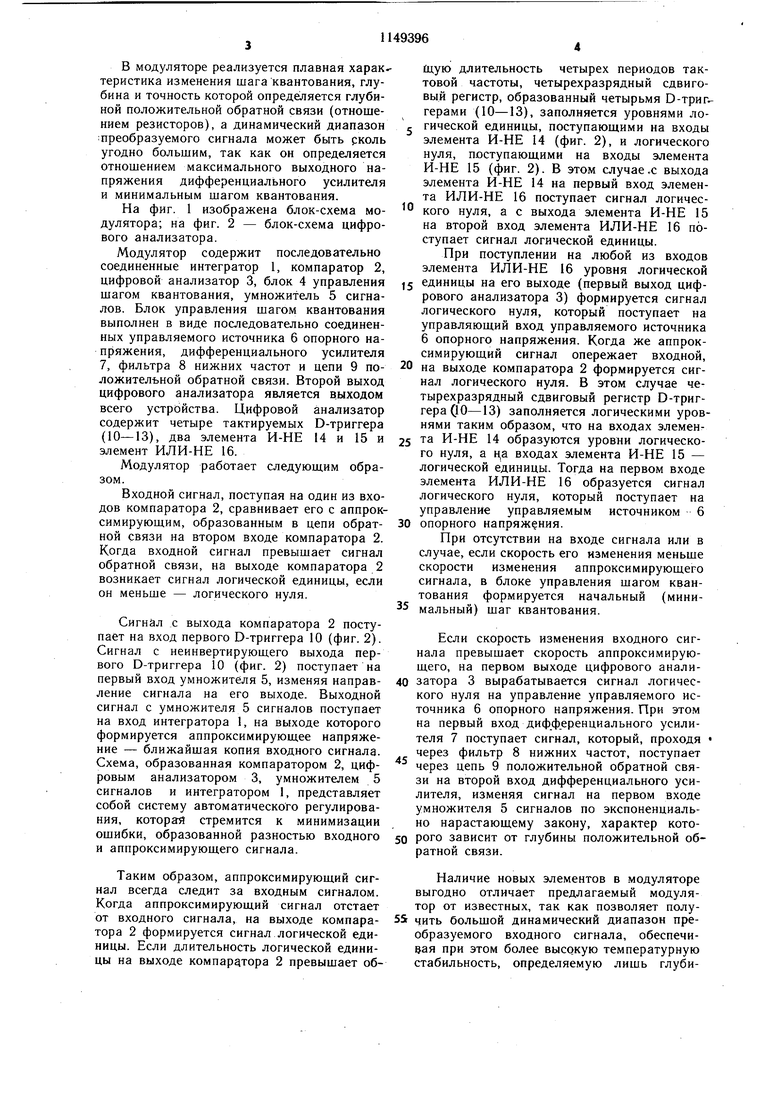

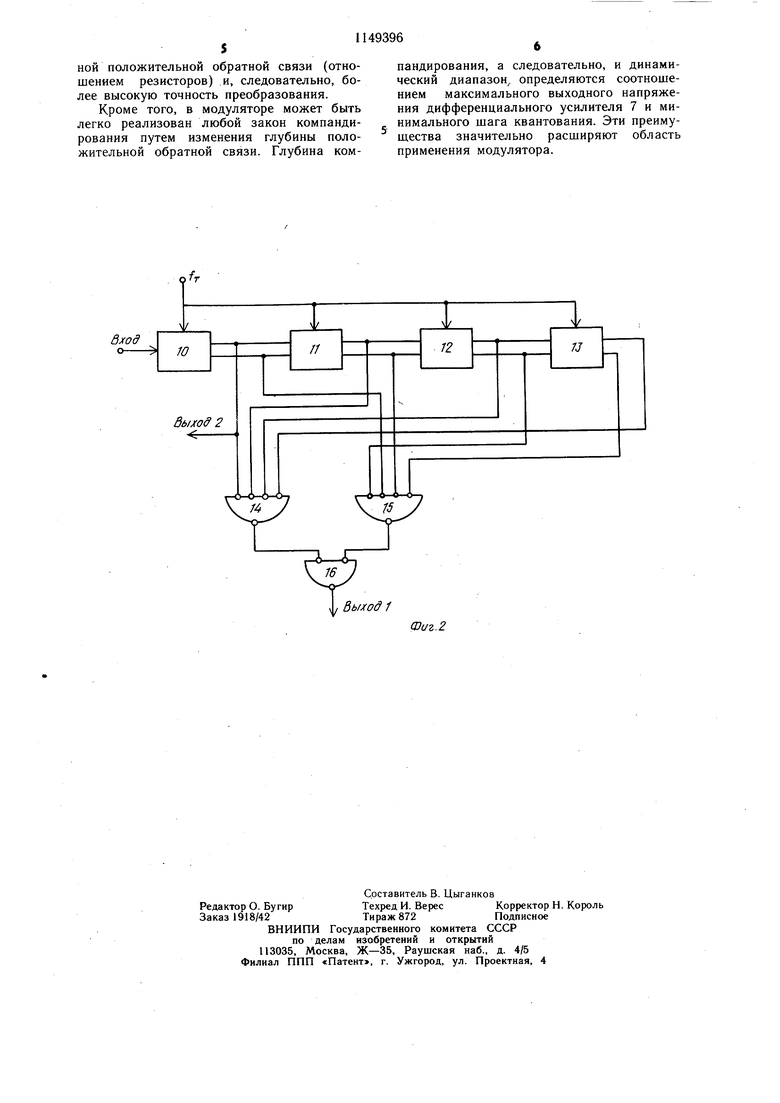

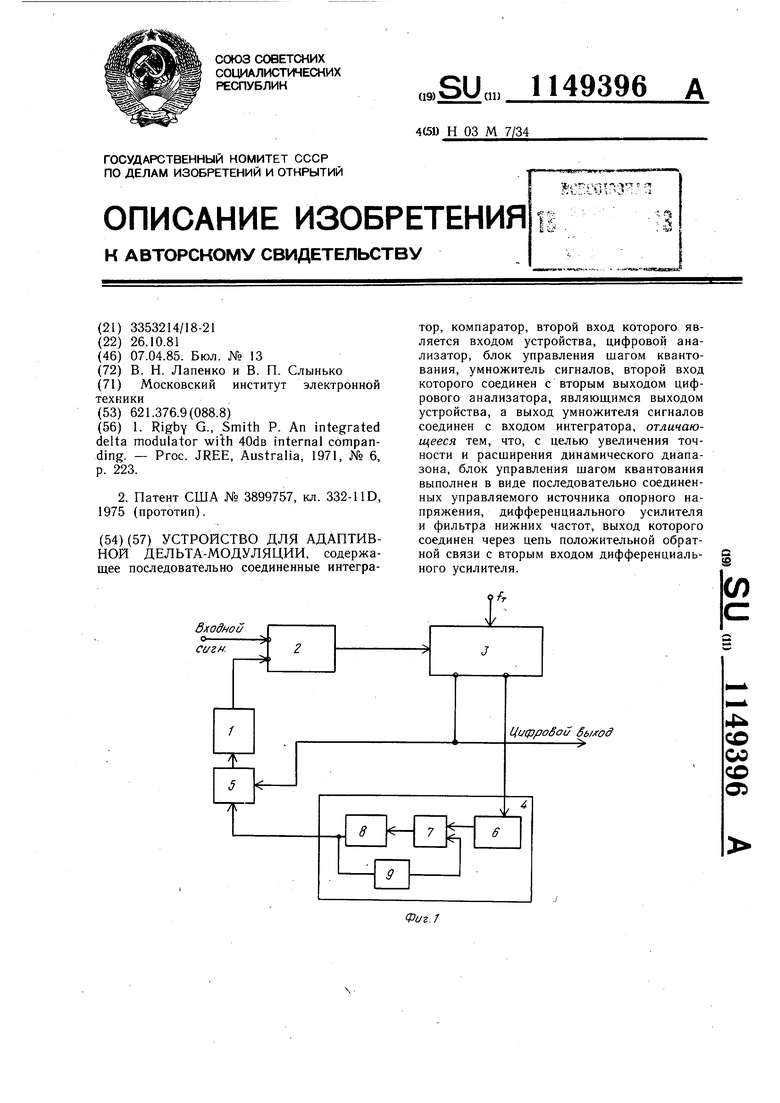

На фиг. 1 изображена блок-схема модулятора; на фиг. 2 - блок-схема цифрового анализатора.

Модулятор содержит последовательно соединенные интегратор 1, компаратор 2, цифровой анализатор 3, блок 4 управления шагом квантования, умножитель 5 сигналов. Блок управления шагом квантования выполнен в виде последовательно соединенных управляемого источника 6 опорного напряжения, дифференциального усилителя 7, фильтра 8 нижних частот и цепи 9 положительной обратной связи. Второй выход цифрового анализатора является в.ыходом всего устройства. Цифровой анализатор содержит четыре тактируемых D-триггера (10-13), два элемента И-НЕ 14 и 15 и элемент ИЛИ-НЕ 16.

Модулятор работает следуюшим образом.

Входной сигнал, поступая на один из входов компаратора 2, сравнивает его с аппроксимирующим, образованным в цепи обратной связи на втором входе компаратора 2. Когда входной сигнал превышает сигнал обратной связи, на выходе компаратора 2 возникает сигнал логической единицы, если он меньше - логического нуля.

Сигнал с выхода компаратора 2 поступает на вход первого D-триггера 10 (фиг. 2). Сигнал с неинвертируюшего выхода первого D-триггера 10 (фиг. 2) поступает на первый вход умножителя 5, изменяя направление сигнала на его выходе. Выходной сигнал с умножителя 5 сигналов поступает на вход интегратора 1, на выходе которого формируется аппроксимируюш.ее напряжение - ближайшая копия входного сигнала. Схема, образованная компаратором 2, цифровым анализатором 3, умножителем 5 сигналов и интегратором 1, представляет собой систему автоматического регулирования, которая стремится к минимизации ошибки, образованной разностью входного и аппроксимируюшего сигнала.

Таким образом, аппроксимирующий сигнал всегда следит за входным сигналом. Когда аппроксимирующий сигнал отстает от входного сигнала, на выходе компаратора 2 формируется сигнал логической единицы. Если длительность логической единицы на выходе компаратора 2 превышает общую длительность четырех периодов тактовой частоты, четырехразрядный сдвиговый регистр, образованный четырьмя D-триг герами (10-13), заполняется уровнями ло- гической единицы, поступающими на входы элемента И-НЕ 14 (фиг. 2), и логического нуля, поступающими на входы элемента И-НЕ 15 (фиг. 2). В этом случае,с выхода элемента И-НЕ 14 на первый вход элемента ИЛИ-НЕ 16 поступает сигнал логического нуля, а с выхода элемента И-НЕ 15 на второй вход элемента ИЛИ-НЕ 16 поступает сигнал логической единицы.

При поступлении на любой из входов элемента ИЛИ-НЕ 16 уровня логической

5 единицы на его выходе (первый выход цифрового анализатора 3) формируется сигнал логического нуля, который поступает на управляющий вход управляемого источника 6 опорного напряжения. Когда же аппроксимирующий сигнал опережает входной,

0 на выходе компаратора 2 формируется сигнал логического нуля. В этом случае четырехразрядный сдвиговый регистр D-триггера (10-13) заполняется логическими уровнями таким образом, что на входах элемента И-НЕ 14 образуются уровни логического нуля, а н,а входах элемента И-НЕ 15 - логической единицы. Тогда на первом входе элемента ИЛИ-НЕ 16 образуется сигнал логического нуля, который поступает на управление управляемым источником 6

0 опорного напряжения.

При отсутствии на входе сигнала или в случае, если скорость его изменения меньше скорости изменения аппроксимирующего сигнала, в блоке управления шагом квантования формируется начальный (мини5 мальный) шаг квантования.

Если скорость изменения входного сигнала превышает скорость аппроксимируюшего, на первом выходе цифрового анализатора 3 вырабатывается сигнал логического нуля на управление управляемого источника 6 опорного напряжения. При этом на первый вход дифференциального усилителя 7 поступает сигнал, который, проходя через фильтр 8 нижних частот, поступает через цепь 9 положительной обратной связи на второй вход дифференциального усилителя, изменяя сигнал на первом входе умножителя 5 сигналов по экспоненциально нарастающему закону, характер которого зависит от глубины положительной обратной связи.

Наличие новых элементов в модуляторе выгодно отличает предлагаемый модулятор от известных, так как позволяет полуS чить большой динамический диапазон преобразуемого входного сигнала, обеспечивая при этом более высокую температурную стабильность, определяемую лишь глубиной положительной обратной связи (отношением резисторов) и, следовательно, более высокую точность преобразования. Кроме того, в модуляторе может быть легко реализован любой закон компандирования путем изменения глубины положительной обратной связи. Глубина компандирования, а следовательно, и динамический диапазон, определяются соотношением максимального выходного напряжения дифференциального усилителя 7 и минимального шага квантования. Эти преимуобластьщества значительно расширяют применения модулятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек адаптивного дельта-модулятора | 1986 |

|

SU1378063A1 |

| Дельта-модулятор | 1987 |

|

SU1474850A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Низкоскоростной дельта-модулятор | 1983 |

|

SU1138950A1 |

| Дельта-кодер | 1984 |

|

SU1197087A1 |

| Дельта-модулятор для передачи речевых сигналов | 1990 |

|

SU1795554A1 |

| Дельта-кодер с инерционным компандированием | 1985 |

|

SU1305877A1 |

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ ДЕЛЬТА-МОДУЛЯЦИИ, содержащее последовательно соединенные интегравходной о тор, компаратор, второй вход которого является входом устройства, цифровой анализатор, блок управления шагом квантования, умножитель сигналов, второй вход которого соединен с вторым выходом цифрового анализатора, являющимся выходом устройства, а выход умножителя сигналов соединен с входом интегратора, отличающееся тем, что, с целью увеличения точности и расширения динамического диапазона, блок управления шагом квантования выполнен в виде последовательно соединенных управляемого источника опорного напряжения, дифференциального усилителя и фильтра нижних частот, выход которого соединен через цепь положительной обратной связи с вторым входом дифференциального усилителя. ЦифроЗой Sb/jfoff

Выход 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Rigby G., Smith P | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| - Proc | |||

| JREE, Australia, 1971, № 6, p | |||

| Способ исправления пайкой сломанных алюминиевых предметов | 1921 |

|

SU223A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3899757, кл | |||

| Приспособление, обнаруживающее покушение открыть замок | 1910 |

|

SU332A1 |

Авторы

Даты

1985-04-07—Публикация

1981-10-26—Подача