z z z

ij.t . - .

х

11288692

Изобретение относится к вычислительной технике и может быть исполь- зовано для выполнения операций вида

при оперативном выполнении

групповых операций.

Целью изобретения является, увеличение быстродействия.

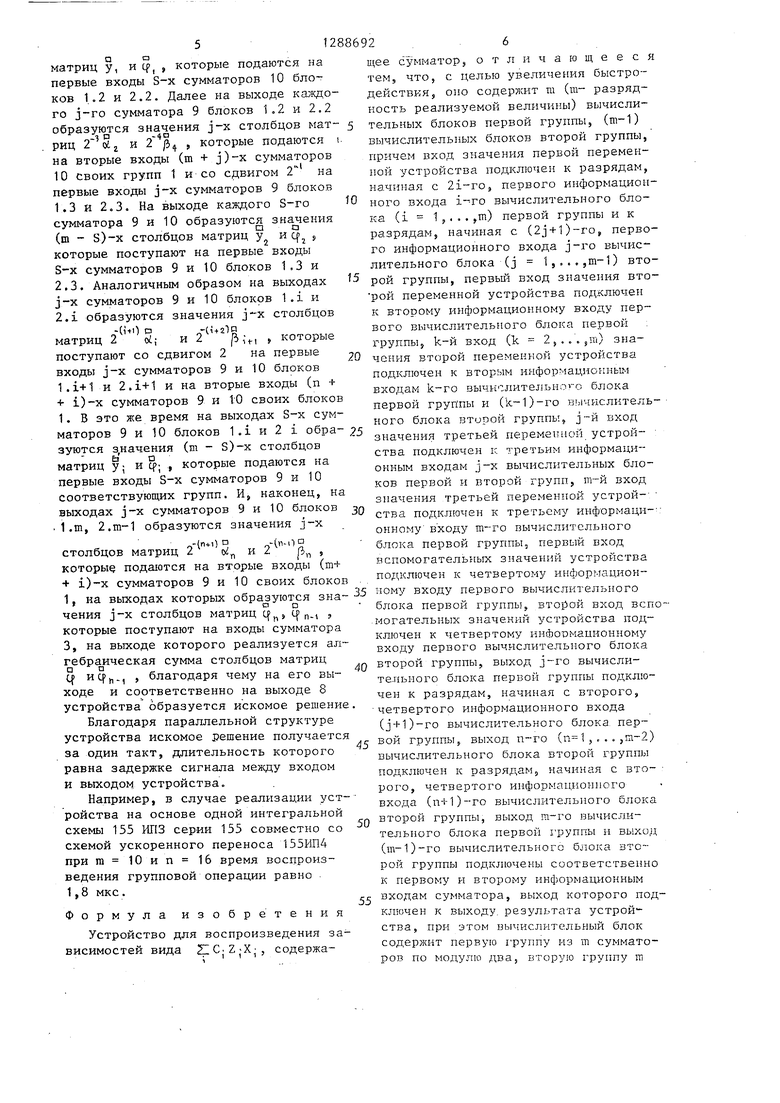

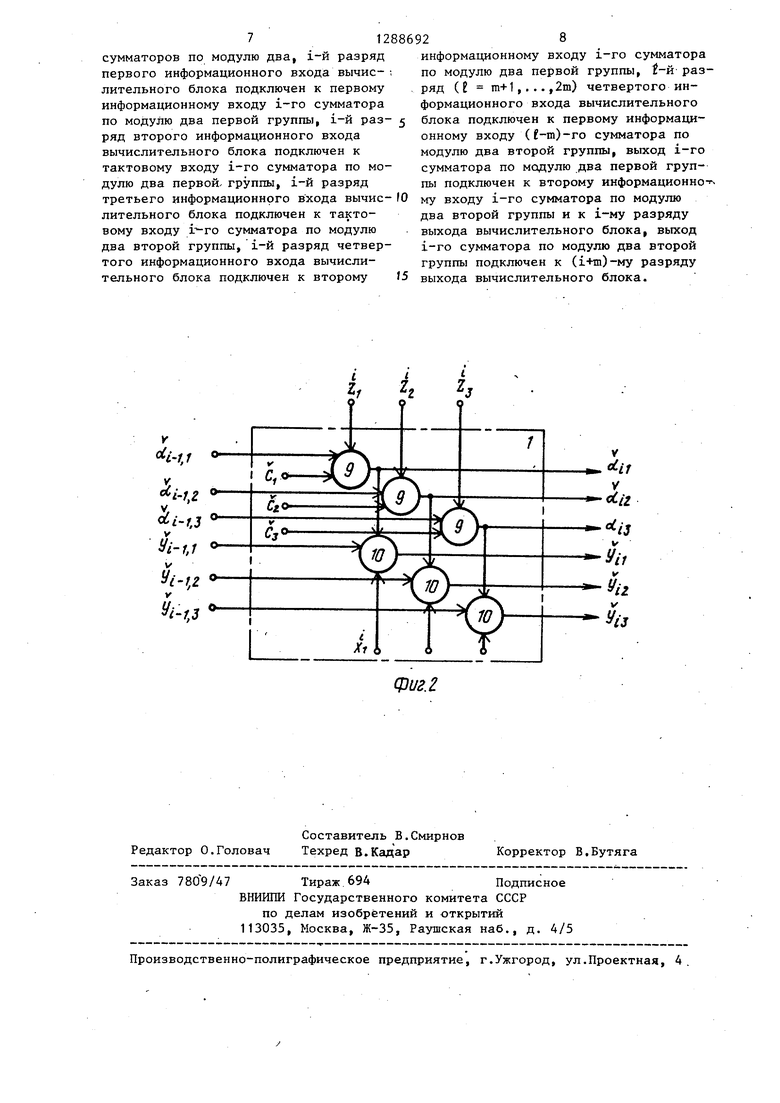

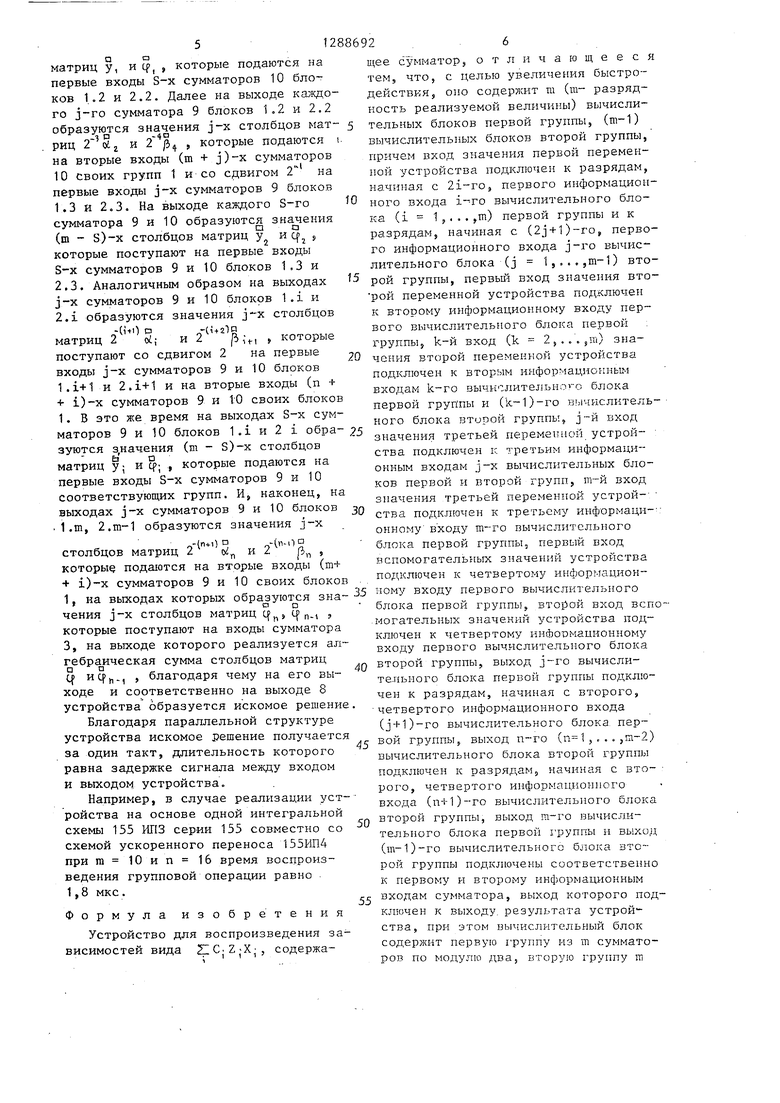

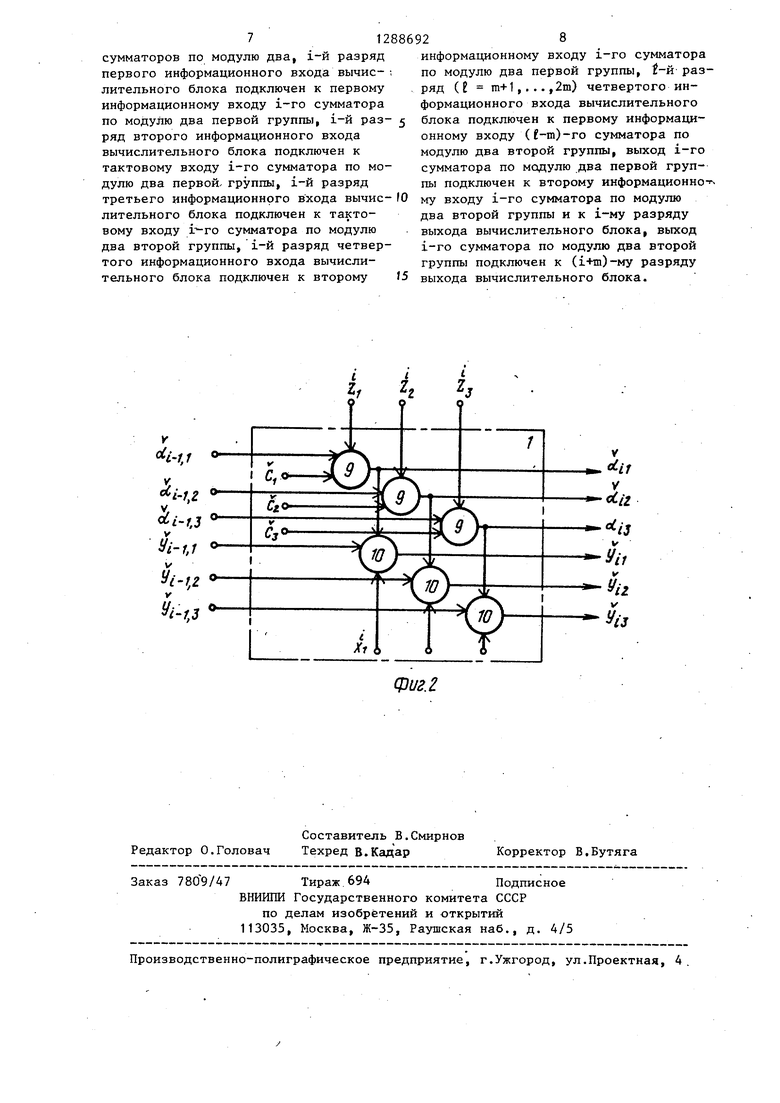

На фиг.1 приведена блок-схема уст- представляющих собой разрядное изоб- ройства для случая, когда m 3, п 0 ражение чисел соответственно; 3; на фиг.2 - схема вычислительного У разрядный вектор вида у блока.

Устройство содержит первый 1.1, второй 1.2 и третий 1.3 вычислител - ные блоки первой группы, первый 2.1 и второй 2.2 вычислительные блоки ; второй группы, сумматор 3, первый i 4.1, второй 4,2 и третий 4.3 входы устройства значения первой перемен15

b i i ч iu(( ) Z,, (Z, , Zj,

..., Z) - векторы бинарных элементов

, составленные из i компонентов

V

20

m-paзpя :l;ныx векторов Х,

20

Z,,...,Z соответственно.

Выражение 212 С z X; вычи

itl

ся по разрядным рекуррентным з

ной, первый 5.1, второй 5.2 и третий

5.3 входы устройства значения второй

переменной, первый 6.1, второй 6.2 и

третий 6.3 входы устройства значения

третьей переменной, первьй 7.1 И вто- 25 и га 2 о и

рой 7.2 входы вспомогательных значе- У) 2 oi,®Xi , 2 ot, 2 C®Z, ;

НИИ устройства, выход 8 результата

устройства, сумматоры 9 по модулю

два первой группы и сумматоры 10 по

модулю два второй группы.

Устройство для моделирования зависимости вида

Y z:c-z-Xi

JM 5 J

работает следующим образом.

Моделируемая зависимость в разрядной форме представлена как

у у, + ,j, , 2, +2

,.«х,, , 2-

-li а U

30+2 C®Z;;

i 1,. . .,n,

а выражение ZI t + l со

35 ственно.

D-3D u aD-30 U

Cf, 2 |i,®Z, 2, 2 C©X, ;

, D |c;,u -.(U,, о a.,u,,,,,

iri1:1

где С

°(0

x

матрицы бинарных элементов, составленные из разрядных векторов вида

z z z

ij.t . - .

х

15

b i i ч iu(( ) Z,, (Z, , Zj,.

..., Z) - векторы бинарных элементов

, составленные из i компонентов

V

m-paзpя :l;ныx векторов Х,

Z,,...,Z соответственно.

Выражение 212 С z X; вычисляетitl

ся по разрядным рекуррентным зависиу у, + ,j, , 2,

,.«х,, , ,.-н .

-li а U

+2 C®Z;;

i 1,. . .,n,

а выражение ZI t + l соответi 1

ственно. .

D-3D u aD-30 U

Cf, 2 |i,®Z, 2, 2 C©X, ;

-40 2 p, +

D . о-40 LJ.40

40 г , - 2 p,®Z,, 2 (i.

.5 D U

+ 2 ceXj}

D a-(Uiia

Q .,- 2 P;.PZ.

45-(r;«l) D

+ C0X;;

t1

i 1n-1.

50

а U.

где С® Z;

D U

C;

Операции, представляющие собой разрядное изображение покомпонентного умноже1щя векторов С . (С, ,C,i,. . ., решение у 0,2351074. Значения Zj .С) ; X;(i,, k-z, ... Х) реали- и Xj (j 1,2,3) в разрядной форме

имеют вид

z,

зуется как СХ;(С,Х,, ,.,.,

(- Y -jt

5 t t t

Конечный результат формируется Z, (1000) ; Zj, (0111) ; Z, (0101) ; D u , , uX, (0101) ; X, (1001) ; X, (1001) ,

y УпХ Я.л далее г,(1,0,0) Z, (0,1,1);

где X (1,1,-...,1),0Z, (0,1,0); Z, (0,1,1); X,(0,1,

Рассмотрим пример для n 4 иt u+ u+ u

m 3. О , X,(1,0,0) ; Хз(0,0,0); X

C, 0,5625; a -0,375; C,0,3125;.. . n . г -Гг г г

0,5; Z, 0,4375; Z, 0,3125; X, , Ц-СС.,С,,С,; .

0,3125; X2 0,5625; Xg 0,5625 и /5Вычислительный процесс значений yj :

i 1, У, 2 V,®X, (0,0,0) 2 oi, 2 С® Z, (0,140625; 0; 0). i 2, 2 V, + 2 С® Z (0,0703125; 0,0234375; 0,019532) , У2 у, + 2 oi,® X, (0,0703125; 0; 0); i 3, 2 Vj + 2 С® Z3 (0,0351526; 0,017578; 0,009766) ,

У} Уг+ 2 V5®X, (0,0703125; 0; 0);

i 4, + 2 C® Z (0,0175781; 0,0102538; 0,0061037), y X (0,0878906; 0,0102538; 0,0061037) .

Вычислительный процесс значений

i 1, q, 2 p.;©Z2 (0; 0,046875; 0,0390625),

2/32 2 C®X,(0; 0,046875; 0,0390625) ; i 2, , 2 + 2 C®X.j (0,0175781; 0,02334375; 0,0105312) ,

cr cp, + 2з(0,0703125;. 0,0390625) ; i 3, )4 + 2 C®X, (0,008789; 0,0117187; 0,0097656),

Cf,q) Z (0; 0,0820312; 0,0488281)

45 I Конечный результат определяет- .. в схеме устройства протекает переходся какной процесс. После окончания переходIJ uного процесса в схеме в сумматоре 9

Y Y,.X + cfjX 0,0878906.+ блоков 1.1 и 2,1 образуются значения + 0,0102538 + 0,0061037 + 0,0820312 + матриц Г S, и 2, соответственно. + 0,0488281 0,2351074, Каждый j-й столбец (J 1,...,т) матгде Х (1, 1, 1) .рицы 2 о(, и 2 подается на второй

Устройство работает следующим об-вход j-ro сумматора 10 соответственразом,но блоков 1.1 и 2.1 и со сдвигом 2

После подачи на входы 4.1-4.3 соот-55на первый вход j-ro сумматора 9 бловетственно С,, С, С, т.е. С, наков 1.2 и 2.2. В это же время на вывходы 5.1, 5.2 и 5.3 - значений Z, ,ходе каждого S-ro (S m + 1,...,2m)

Zj, Z, соответственно, на входы 6.1,сумматора 9 блоков 1.1 и 2.1 образу6.2, 6.3 - X, , Х, X, соответственно iются значения (т - S) X столбцов

имеют вид

риц и 2 jb , которые подаются

сумматоров

I

СДВИГОМ / на

матриц у, и q, , которые подаются на первые входы S-x сумматоров 10 блоков 1.2 и 2,2. Далее на выходе каждого j-ro суьматора 9 блоков 1.2 и 2.2 образуются значения j-x столбцов мат-

на вторые входы (т + j)x 10 своих групп 1 и со первые входы j-x сумматоров 9 блоков 1.3 и 2.3. На выходе каждого S-ro сумматора 9 и 10 образуются значения (т - S)x столбцов матриц у и q., j которые поступают на первые входы S-X сумматоров 9 и 10 блоков 1.3 и 2.3. Аналогичным образом на выходах j-x сумматоров 9 и 10 блоков 1.1 и 2.1 образуются значения j-x столбцов

сз „-(i+aln матриц 2 Ы; и 2 i,-, которые

поступают со сдвигом 2 на первые входы j-x сумматоров 9 и 10 блоков 1.1+1 и 2.1+1 и на вторые входы (п + + 1)-х сумматоров 9 и Т О своих блоков 1. В это же время на выходах S-x сумматоров 9 и 10 блоков 1.1 и 2 1 обра-

зуются значения (т - S)-x столбцов

ь а матриц у; и , KOTOpBie подаются на

первые входы S-x сумматоров 9 и 10 соответствующих групп. И, наконец, на выходах j-x сумматоров 9 и 10 блоков . i.т, 2.т-1 образуются значения j-x

-(пч-О D

столбцов матриц 2 (х;.

и

. . которые подаются на вторые входы (т+

+ 1)-х сумматоров 9 и 10 своих блоков 1, на выходах которых образуются значения j-x столбцов матриц ц), ц n-i которые поступают на входы сумматора 3, на выходе которого реализуется алгебраическая сумма столбцов матриц Cf Mtph-i благодаря чему на его выходе и соответственно на выходе 8 устройства образуется искомое решение

Благодаря параллельной структуре устройства искомое решение получается за один такт, длительность которого равна задержке сигнала между входом и выходом устройства.

Например, в случае реализации устройства на основе одной интегральной схемы 155 ИПЗ серии 155 совместно со схемой ускоренного переноса 155ИП4 при га 10 и п 16 время воспроизведения групповой операции равно 1,8 МКС.

Формула изобретения Устройство для воспроизведения зависимостей вида

Z:C|Z;X;,

содержащее сумматор, отличающееся тем, что, с целью увеличения быстродействия, оно содержит m (m- разрядность реализуемой величины) вычислительных блоков первой группы, (in-1) вычислительных блоков второй группы, причем вход значения первой переменной устройства подключен к разрядам, начиная с первого информационного входа вычислительного блока (1 1,...,т) первой группы и к разрядам, начиная с (2j+1)-ro, первого информационного входа j-ro вычислительного блока (J 1,...,т-1) второй группы, первьш вход значения вто- рой переменной устройства подключен к второму информационному входу первого вычислительного блока первой группы, k-й вход (1с 2,...5т) значения второй переменной устройства подключен к вторым информационным входам k-ro вь чи глительно1-о блока первой группы и (k-l)-ro вычислительного блока втирой группы, j-й вход значения третьей переметшей устройства подключен к. третьим информационным входам j-x вычислительных блоков первой и второй групп, т-й вход

значения третьей переменной устрой- ства подключен к третьему информацн- : онному входу т-го вычислительного блока первой группы, первый вход вспомогательных значений устройства подключен к четвертому информгщионному входу первого вычислительного блока первой группы, второй вход вспоогательных значений устройства подлючен к четвертому инфоомапионному входу первого вычислительного блока

второй группы, выход j-ro вычислительного блока первой группы подключен к разрядам, начиная с второго, четвертого информационного входа (j+1)-ro вычислительного блока первой группы, выход п-го (п 1 , , .. ) вычислительного блока второй группы подключен к разрядам, начиная с вто- рого, четвертого информационного входа (n-i-l)--ro вычислительного блока

второй группы, выход га-го вычислительного блока первой группы и выход (т-1)-го вычислительного блока второй группы подключены соответственно к первому и второму информационным

входам сумматора, выход которого подключен к выходу, результата устройства, при этом вычислительный блок содержит первую группу из m сумматоров по модулю два, вторую группу го

сумматоров по модулю два, i-й разряд первого информационного входа вычис- ; лительного блока подключен к первому информационному входу i-ro сумматора по модулю два первой группы, i-й раз- 5 ряд второго информационного входа вычислительного блока подключен к тактовому входу i-ro сумматора по модулю два первой- группы, i-й разряд

информационному входу i-ro суммат по модулю два первой группы, t-й р ряд (Е m+1,,..,2m) четвертого и формационного входа вычислительно блока подключен к первому информац онному входу (f-m)-го сумматора п модулю два второй группы, выход i сумматора по модулю два первой гр пы подключен к второму информацио

третьего информационного входа вычис- (О му входу i-ro сумматора по модулю

лительного блока подключен к тактовому входу сумматора по модулю два второй группы, i-й разряд четвертого информационного входа вычислительного блока подключен к второму 5

два второй группы и к i-му разряду выхода вычислительного блока, вых i-ro сумматора по модулю два втор группы подключен к (i+m)-My разряд выхода вычислительного блока.

8

5 информационному входу i-ro сумматора по модулю два первой группы, t-й разряд (Е m+1,,..,2m) четвертого информационного входа вычислительного блока подключен к первому информационному входу (f-m)-го сумматора по модулю два второй группы, выход i-ro сумматора по модулю два первой группы подключен к второму информационному входу i-ro сумматора по модулю

два второй группы и к i-му разряду выхода вычислительного блока, выход i-ro сумматора по модулю два второй группы подключен к (i+m)-My разряду выхода вычислительного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Генератор случайных чисел | 1985 |

|

SU1302275A1 |

| Устройство для умножения двоичных чисел в дополнительном коде | 1983 |

|

SU1191907A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для умножения элементов конечных полей | 1984 |

|

SU1226445A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| Множительно-делительное устройство | 1981 |

|

SU1267407A2 |

| Матричный вычислитель | 1985 |

|

SU1283791A1 |

Чз

Редактор О.Головач

Составитель В.Смирнов Техред В.Кадар

Заказ 7809/47 Тираж.694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4.

Корректор В.Бутяга

| Устройство для вычисления суммы квадратов к чисел | 1977 |

|

SU717759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления суммы произведений | 1973 |

|

SU717765A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-07—Публикация

1985-01-14—Подача