Изобретение относится к вычислительной технике и может быть использовано в специализированных ычислителях.

Цель изобретения - упрощение устройства.

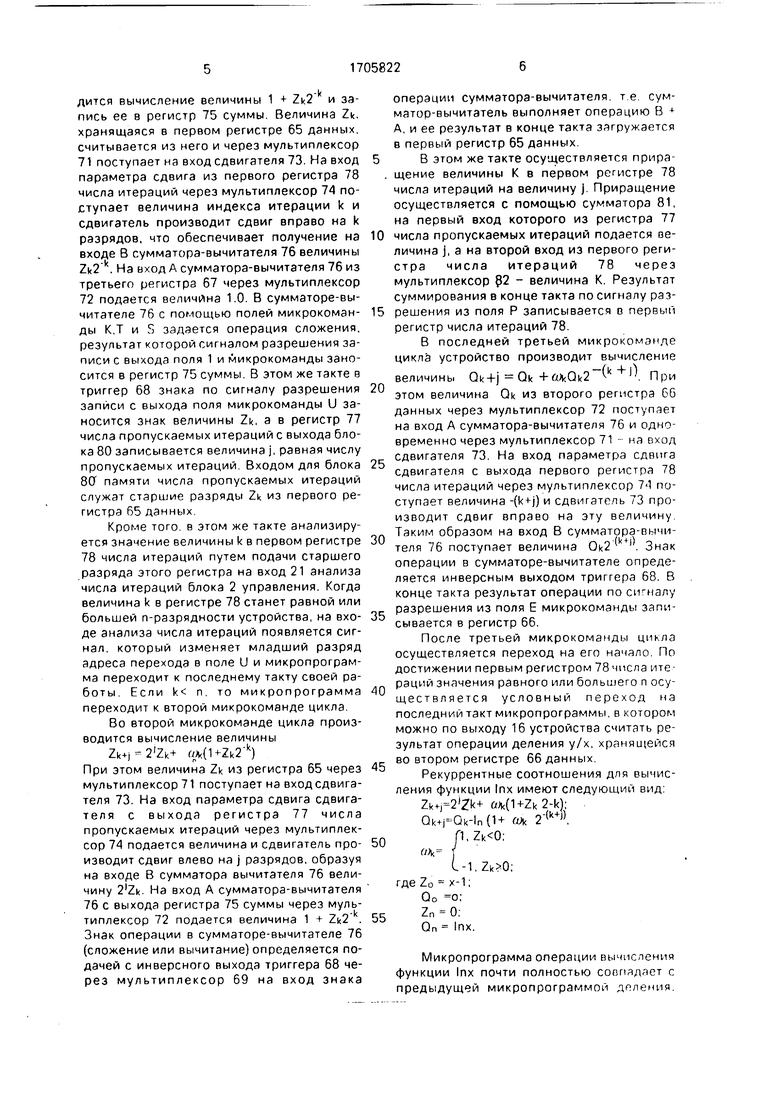

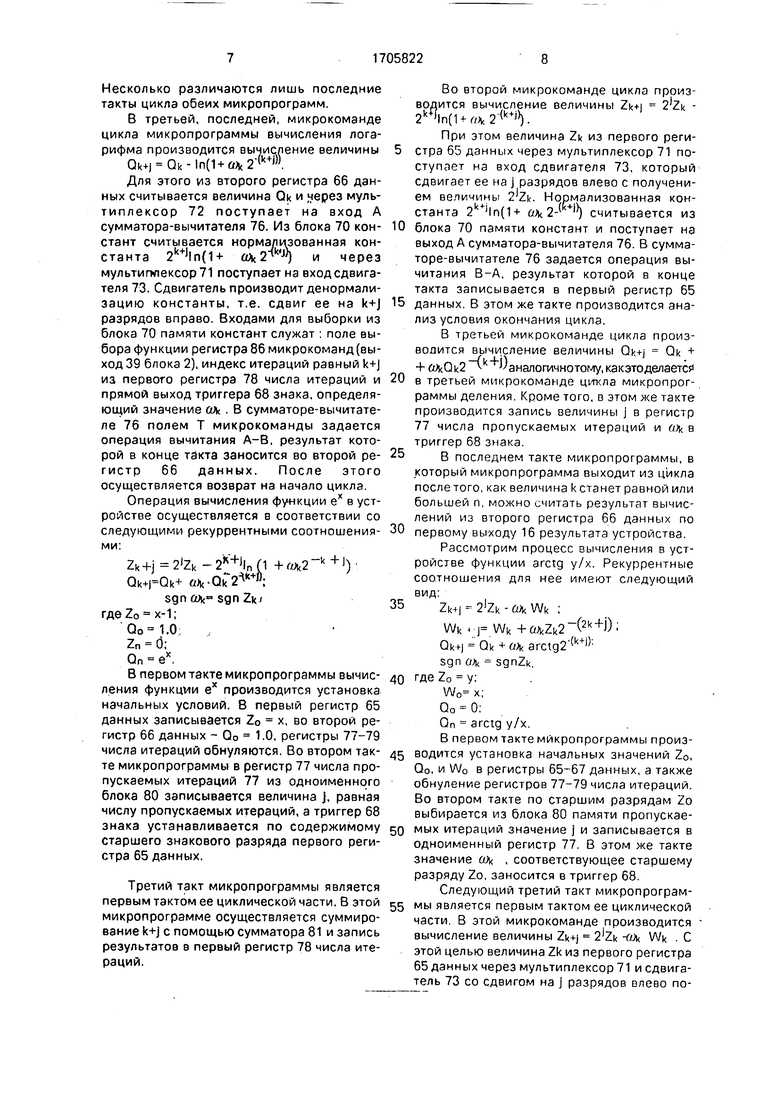

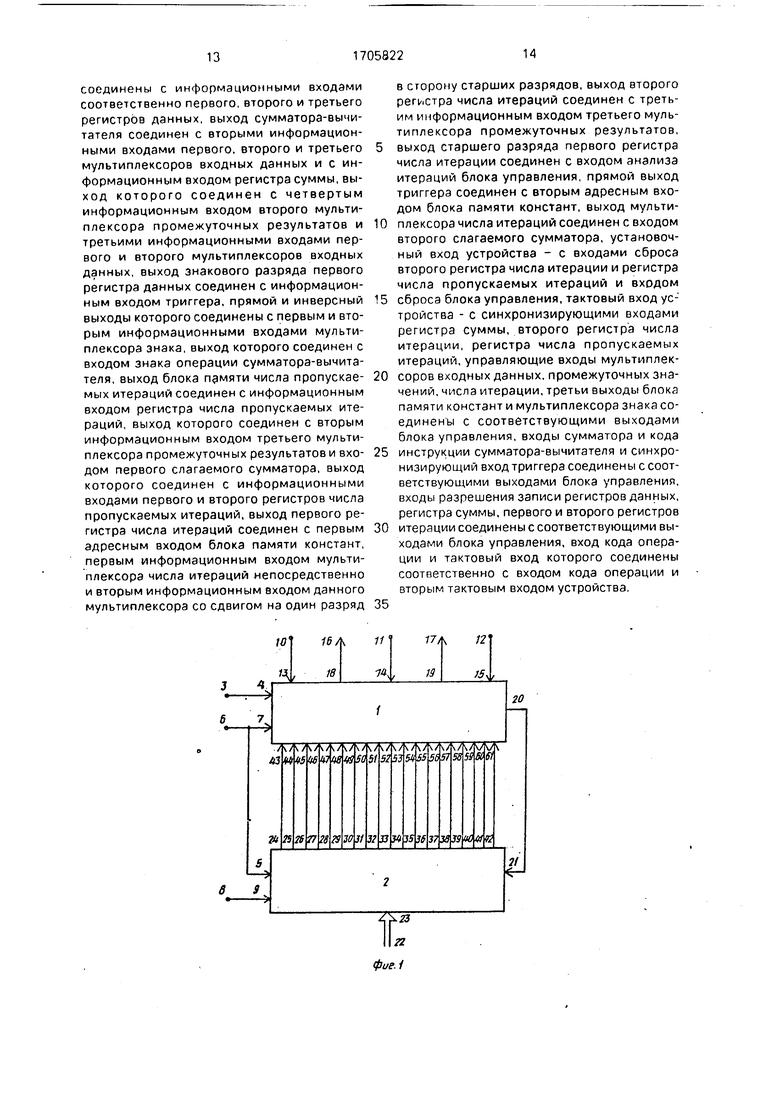

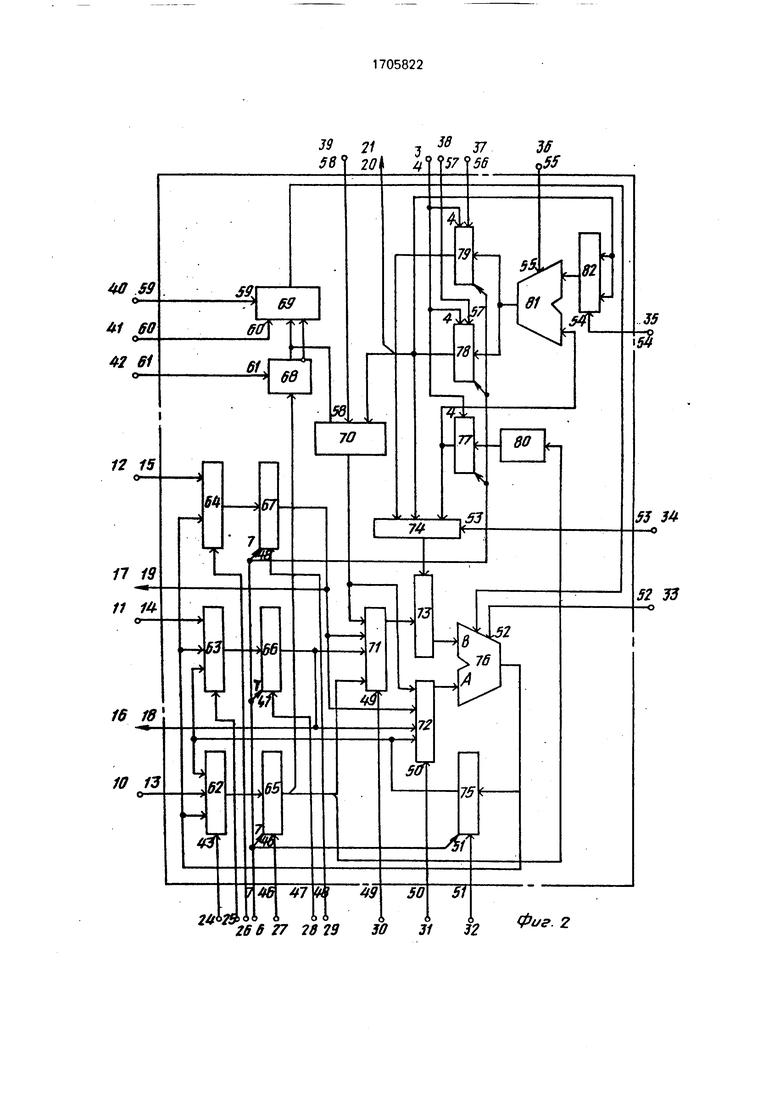

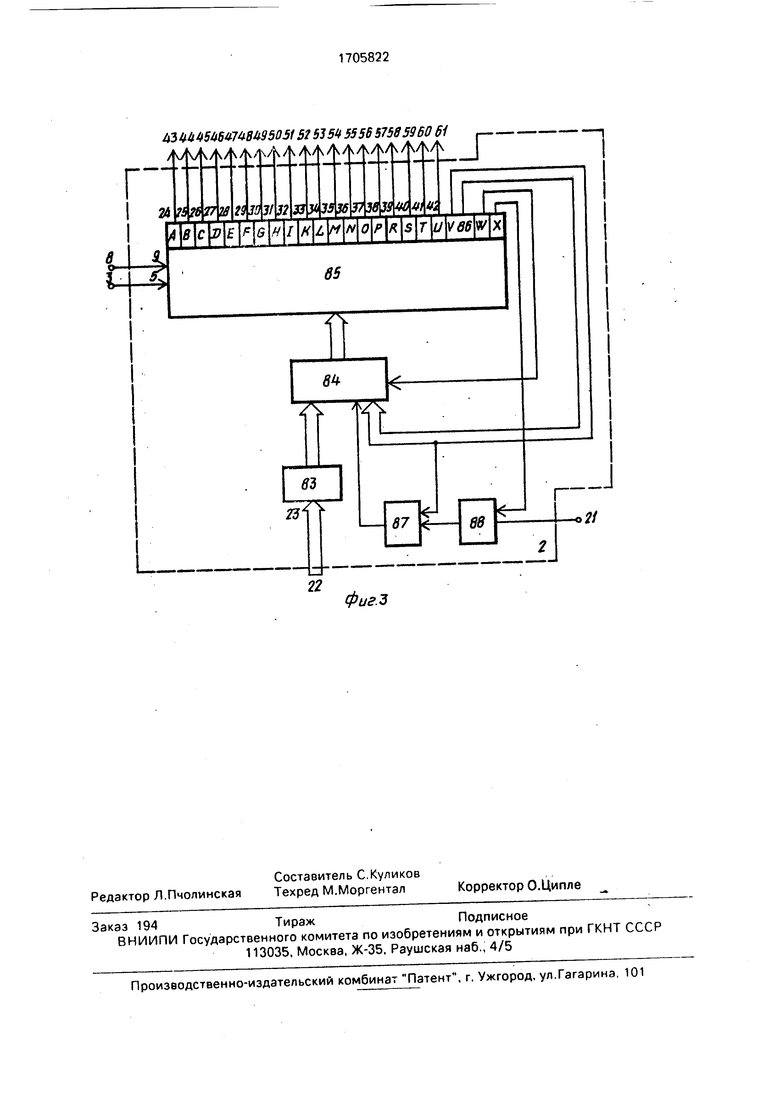

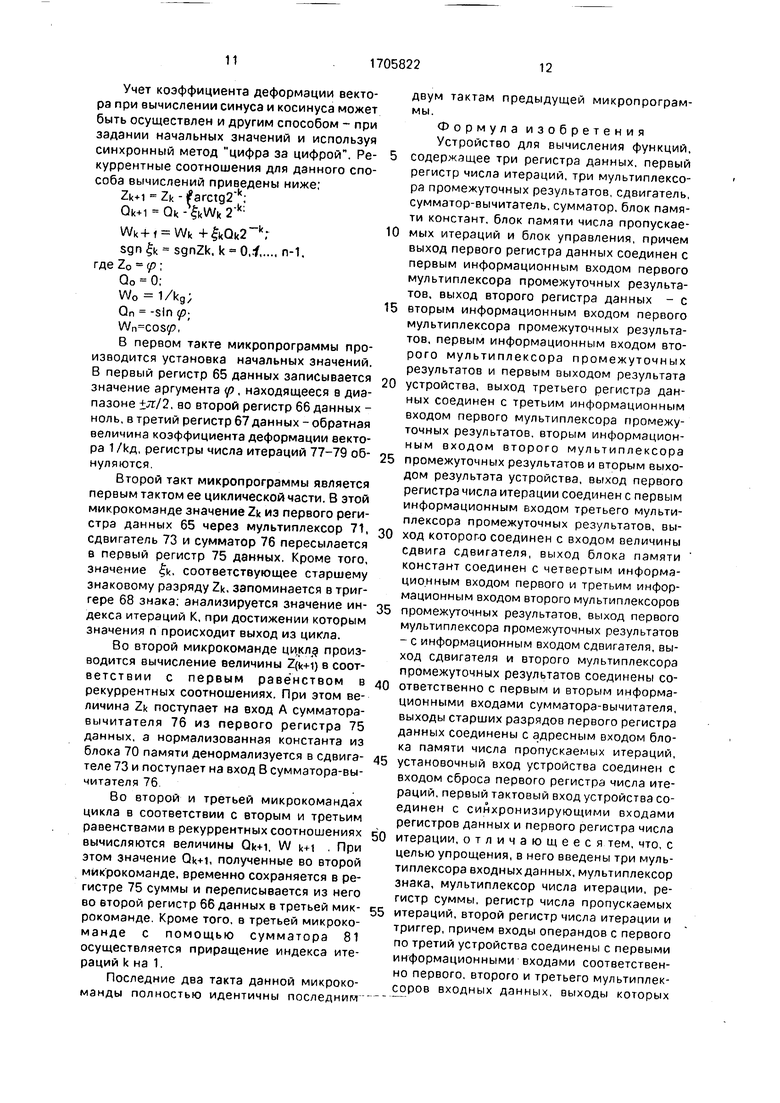

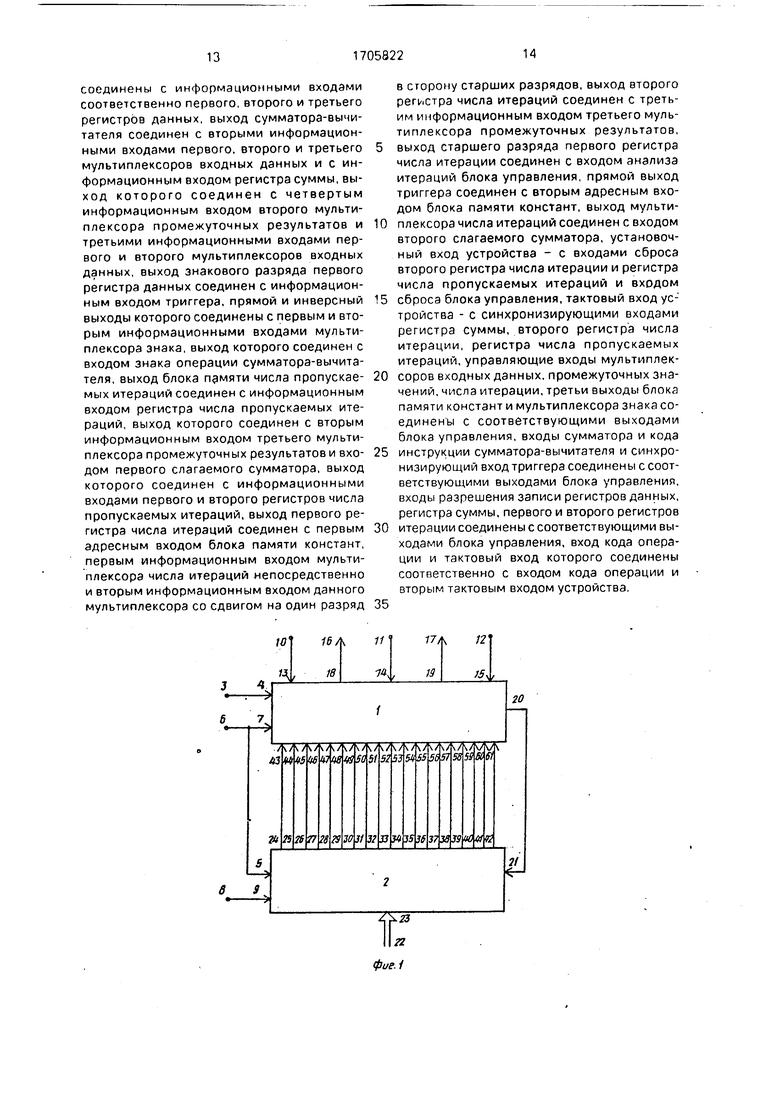

На фиг. 1 представлена структурная схема устройства; на фиг.2 - функциональная схема операционного блока; на фиг.З - схема блока управления.

Устройство содержит операционный блок 1, блок 2 управления, установочный вход 3. установочный вход 4 операционного блока, вход 5 сброса блока управления, первый тактовый вход 6, тактовый вход 7 операционного блока, второй тактовый вход 8, тактовый вход 9 блока управления, входы 10-12 операндов соответственно с первого по третий, входы 13-15 операндов соответственно с первого по третий операционного блока, первый 16 и второй 17 выходы результатов устройства, первый 18 и второй 19 выходы результатов операционного блока, выход 20 анализа числа итерации операционного блока, вход 21 анализа числа итераций блока управления, вход 22 кода операции, вход 23 кода операций блока управления, тактовые выходы 24-42 блока управления, тактовые входы 43--61 операционного блока.

Операционный блок образуют первый 62, второй 63 и третий 64 мультиплексоры входных данных, первый 65. второй 66 и третий 67 регистры, триггер 68, мультиплексор 69 знака, блок 70 памяти констант, муль- типлексоры 71 и 72 промежуточных результатов, сдвигатель 73, мультиплексор 74 промежуточных результатов,регистр 75 суммы, сумматор-вычитатель 76, регистр 77 числа пропускаемых итераций, первый 78 и второй 79 регистры числа итераций, блок 80 памяти числа пропускаемых итераций, сумматор 81 и мультиплексор 82 числа итераций.

Блок2 управления содержит, например, дешифратор 83 кода инструкций, мультиплексор 84 адреса, блок 85 памяти микроел С

vi о

1СЛ ICO

Iго

hO

программ и регистр 86 микрокоманд (А, В, С. D, Е, F. G, Н. I. К, L, M, N, О, Р, R, S, Т. U. V, W. X). элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 87 и элемент И 88.

Блок 70 памяти констант разбит на две части, первая из которых содержит нормализованные константы 2k arctg 2 Л а вторая часть разбита на две зоны в зависимости от знака Uk. т,е, ft 1 соответствуют нормализованные константы вида 2k )1п(1+2(и ), й -1 соответствуют константы вида 2k+)ln(1-2(k+l).

Адресными входами блока 70 памяти констант служит код 0 k+ j n, где n - разрядность устройства, Sgn Wk и еще один разряд для выбора необходимой части блока памяти.

Блок 80 памяти числа пропускаемых итераций служит для хранения величин, означающих количество пропускаемых в процессе вычислений итераций. Адресными входами блока 80 памяти являются старшие разряды, включая знаковый, сводимого к нулю аргумента функции, который хранится в регистре 65.

Рассмотрим работу устройства на примере вычисления следующих функций: у/х, In x, ex, arctg y/x, kgsln pv kgcos f , sin ри cos f.

Операция деления у/х в устройстве осуществляется в соответствии со следующими рекуррентными соотношениями

Zk+r2 Zk+ fiJkO+Z 2 k); ,

QH Qk+WkQk2 (k+J);

p.

Wk

L-1, где20 х-1;

Q0 y;

Zn 0. .

Qn y/x.

В исходном состоянии на установочный вход 3 устройства поступает сигнал, сбрасывающий регистры 77-79 числа итераций 79 операционного блока и регистр 86 микрокоманд,

На вход 22 кода операции блока 2 управления поступает код инструкции операции деления, дешифратор 83 преобразует этот код в адрес первой микрокоманды операции деления. Управляющий сигнал с выхода поля W регистра 86 микрокоманд обеспечивает прохождение адреса с выхода дешифратора 83 через мультиплексор 84 адреса на вход блока 85 памяти микрокоманд. По синхроимпульсу на входе 9 регистра 86 первая микрокоманда микропрограммы деления загружается в регистр 86 микрокоманд. Аналогично осуществляется

установка в исходное состояние и выборка первой микрокоманды и во всех остальных операциях.

В первом такте микропрограммы деления значения делителя х, делимого у и 1.0 с входов 10-12 операционного блока 1 проходят через мультиплексоры 62-64 и записываются в регистры 65-67 данных. Данная микрооперация обеспечивается управляю0 щими сигналами, поступающими с выходов полей А, В, С, D, Е, F регистра микрокоманд на управляющие входы 43-45 мультиплексоров 62-64, и на входы 46-48 разрешения записи в регистры данных 65-67.

5 Переход к следующей микрокоманде осуществляется по адресу перехода, находящемуся в поле V текущей микрокоманды и с помощью задания в поле сигнала, обеспечивающего подключение адреса перехо0 да через мультиплексор 84 адреса к входам блока 85 памяти микрокоманд. Поле V адреса перехода подключено к мультиплексору 84 адреса всеми разрядами, кроме младше- I го. Для обеспечения условных переходов в

5 микропрограмме младший разряд адреса перехода может быть модифицирован признаком на входе 21 анализа числа итерации блока 2 управления при наличии разрешающего сигнала в поле X регистра 86 микроко0 манд. При отсутствии хотя бы одного из этих сигналов младший разряд адреса перехода не меняется.

Во втором такте микропрограммы деления в устройстве производится вычисление

5 величины х-1 и запись ее в регистр 65.

Для этого величина делителя х из первого регистра данных 65 прдается через мультиплексор 71 и сдвигатель 73 (при этом параметр сдвига равен нулю) на вход В сум0 матора-вычитателя 76. На вход А этого же сумматора-вычитателя из третьего регистра 67 через мультиплексор 72 подается величина 1.0. В сумматоре-вычитателе 76 задается операция вычитания В-А, результат кото5 рой с выхода сумматора-вычитателя заносится в конце такта в первый регистр 65 данных. Данная микрооперация обеспечивается управляющими сигналами, поступающими с выходов полей D. G, Н, К L, S, Т

0 регистра 86 микрокоманд. При этом на вход параметра сдвига сдвигателя 73 подается ноль с выходов любого из регистров 77-79 числа итерации через мультиплексоры 74. на вход знака операций сумматора-вычита5 теля 76 подается знак операции (в данном случае - вычитание) с выхода поля Т через мультиплексор 69 знака.

Третий такт микропрограммы является первым тактом циклической части микропрограммы. В этой микрокоманде произвоь

дится вычисление величины 1 + Zv.2 и запись ее в регистр 75 суммы. Величина Zk. хранящаяся в первом регистре 65 данных, считывается из него и через мультиплексор

71 поступает на вход сдвигателя 73. На вход параметра сдвига из первого регистра 78 числа итераций через мультиплексор 74 поступает величина индекса итерации k и сдвигатель производит сдвиг вправо на k разрядов, что обеспечивает получение на входе В сумматора-вычитателя 76 величины Zk2 k. На вход А сумматора-вычитателя 76 из третьего регистра 67 через мультиплексор

72 подается величина 1.0. В сумматоре-вы- читателе 76 с помощью полей микрокоманды К.Т и S задается операция сложения, результат которой сигналом разрешения записи с выхода поля 1 и микрокоманды заносится в регистр 75 суммы. В этом же такте в триггер 68 знака по сигналу разрешения записи с выхода поля микрокоманды U заносится знак величины Zk, а в регистр 77 числа пропускаемых итераций с выхода блока 80 записывается величина J, равная числу пропускаемых итераций. Входом для блока 8СГ памяти числа пропускаемых итераций служат старшие разряды Zk из первого регистра 65 данных.

Кроме того, в этом же такте анализируется значение величины k в первом регистре 78 числа итераций путем подачи старшего разряда этого регистра на вход 21 анализа числа итераций блока 2 управления. Когда величина k в регистре 78 станет равной или большей n-разрядности устройства, на входе анализа числа итераций появляется сигнал, который изменяет младший разряд адреса перехода в поле U и микропрограмма переходит к последнему такту своей работы. Если k n, то микропрограмма переходит к второй микрокоманде цикла.

Во второй микрокоманде цикла производится вычисление величины

Zk4j 2 Zk+ ftJk(HZk2 k) При этом величина Zk из регистра 65 через мультиплексор 71 поступает на вход сдвигателя 73. На вход параметра сдвига сдвигателя с выхода регистра 77 числа пропускаемых итераций через мультиплексор 74 подается величина и сдвигатель производит сдвиг влево на j разрядов.образуя на входе В сумматора вычитателя 76 величину 2 Zk. На вход А сумматора-вычитателя 76 с выхода регистра 75 суммы через мультиплексор 72 подается величина 1 + . Знак операции в сумматоре-вычитателе 76 (сложение или вычитание) определяется подачей с инверсного выхода триггера 68 через мультиплексор 69 на вход знака

операции сумматора-вычитателя. т.е. сум- матор-вычитатель выполняет операцию В А, и ее результат в конце такта загружается в первый регистр 65 данных.

5В этом же такте осуществляется прира. щение величины К в первом регистре 78

числа итераций на величину j. Приращение

осуществляется с помощью сумматора 81,

на первый вход которого из регистра 77

0 числа пропускаемых итераций подается величина j, а на второй вход из первого регистра числа итераций 78 через мультиплексор 82 - величина К. Результат суммирования в конце такта по сигналу раз5 решения из поля Р записывается в первый регистр числа итераций 78.

В последней третьей микрокоманде цикла устройство производит вычисление

величины Qk+j Qk + WkQk2(k +). При этом величина Qk из второго регистра 66 данных через мультиплексор 72 поступает на вход А сумматора-вычитателя 76 и одновременно через мультиплексор 71 - на вход сдвигателя 73. На вход параметра сдвига сдвигателя с выхода первого регистра 78 числа итераций через мультиплексор 74 поступает величина -(k+j) и сдвигатель 73 производит сдвиг вправо на эту величину. Таким образом на вход В сумматорэ-вычи- теля 76 поступает величина . Знак операции в сумматоре-вычитателе определяется инверсным выходом триггера 68. В конце такта результат операции по сигналу разрешения из поля Е микрокоманды записывается в регистр 66.

После третьей микрокоманды цикла осуществляется переход на его начало. По достижении первым регистром 78 числа итераций значения равного или большего n ocy- ществляется условный переход на последний такт микропрограммы, в котором можно по выходу 16 устройства считать результат операции деления у/х, хранящейся во втором регистре 66 данных.

Рекуррентные соотношения для вычисления функции Inx имеют следующий вид:

Zk-H,2 Zk+ Uk(1+Zk2-k);

Qk+| Qk-ln(H Wk 2(k+)), p,

Wk I

L-1, где Z0 x-1; Qo o: Zn 0; Qn Inx.

Микропрограмма операции вычисления функции Inx почти полностью совпадает с предыдущей микропрограммой деления.

0

5

0

5

0

5

0

5

Несколько различаются лишь последние такты цикла обеих микропрограмм.

В третьей, последней, микрокоманде цикла микропрограммы вычисления логарифма производится вычисление величины

Qk+) Qk-ln((k+))).

Для этого из второго регистра 66 данных считывается величина Qk и через мультиплексор 72 поступает на вход А сумматора-вычитателя 76. Из блока 70 констант считывается нормализованная константа 2k+)ln(1 + ) и через мультиплексор 71 поступает на входсдвига- теля 73. Сдвигатель производит денормали- зацию константы, т.е. сдвиг ее на k+J разрядов вправо. Входами для выборки из блока 70 памяти констант служат : поле выбора функции регистра 86 микрокоманд (выход 39 блока 2), индекс итераций равный k+J из первого регистра 78 числа итераций и прямой выход триггера 68 знака, определяющий значение о . В сумматоре-вычитате- ле 76 полем Т микрокоманды задается операция вычитания А-В, результат которой в конце такта заносится во второй регистр 66 данных. После этого осуществляется возврат на начало цикла.

Операция вычисления функции ех в устройстве осуществляется в соответствии со следующими рекуррентными соотношениями:

Zk +j 2 Zx - 0 + ОД2 k + ) ttJk-Qk 2™ sgnctvsgnZk/ где2о х-1;

.0;

Zn d:

Qn ex.

В первом такте микропрограммы вычисления функции ех производится установка начальных условий. В первый регистр 65 данных записывается Zo x, во второй регистр 66 данных - Qo 1.0, регистры 77-79 числа итераций обнуляются. Во втором такте микропрограммы в регистр 77 числа пропускаемых итераций 77 из одноименного блока 80 записывается величина j, равная числу пропускаемых итераций, а триггер 68 знака устанавливается по содержимому старшего знакового разряда первого регистра 65 данных.

Третий такт микропрограммы является первым тактом ее циклической части. В этой микропрограмме осуществляется суммирование k+j с помощью сумматора 81 и запись результатов в первый регистр 78 числа итераций.

Во второй микрокоманде цикла производится вычисление величины Zk+i - 2k4n((k+i)).

При этом величина Zk из первого регистра 65 данных через мультиплексор 71 поступает на вход сдвигателя 73, который сдвигает ее на J разрядов влево с получением величины 2 Zk. Нормализованная константа 2k+iln(1 + ( )) считывается из

блока 70 памяти констант и поступает на выход А сумматора-вычитателя 76. В сумма- торе-вычитателе 76 задается операция вычитания В-А, результат которой в конце такта записывается в первый регистр 65

данных. В этом же такте производится анализ условия окончания цикла.

В третьей микрокоманде цикла производится вычисление величины Qk+j Qk +

+ WkQk2 k аналогичнотому,какэтоделаетс

в третьей микрокоманде цикла микропрограммы деления. Кроме того, в этом же такте производится запись величины j в регистр 77 числа пропускаемых итераций и ед в триггер 68 знака.

в последнем такте микропрограммы, в который микропрограмма выходит из цикла послетого, как величина kстанет равной или большей п, можно считать результат вычислений из второго регистра 66 данных по

первому выходу 16 результата устройства.

Рассмотрим процесс вычисления в устройстве функции arctg y/x. Рекуррентные соотношения для нее имеют следующий вид:

Zk-м. 2JZk ft Wk ;

Wk4 j.Wk +адЛ2(

Qk+j Qk + (Ь arctg2(k+i):

sgn ak sgnZk. где Z0 у:

W0 x;

Qo 0;

Qn arctg y/x.

В первом такте микропрограммы производится установка начальных значений Zo,

Qo, и W0 в регистры 65-67 данных, а также

обнуление регистров 77-79 числа итераций.

Во втором такте по старшим разрядам Zo

выбирается из блока 80 памяти пропускаеМУХ итераций значение j и записывается в

одноименный регистр 77. В этом же такте

значение ад , соответствующее старшему

разряду Zo, заносится в триггер 68.

Следующий третий такт микропрограм- мы является первым тактом ее циклической части. В этой микрокоманде производится вычисление величины Zk+j 2JZk -ад Wk . С этой целью величина Zk из первого регистра 65 данных через мультиплексор 71 исдвига- тель 73 со сдвигом на j разрядов влево поступает на вход В сумматора-вычитателя 76, на вход А которого из третьего регистра 67 данных поступает величина Wk. Знак операции в сумматоре-вычитателе 76 определяется инверсным выходом триггера 68 знака. Результат операции в конце такта записывается в регистр 75 суммы. Одновременно с этим с помощью сумматора 81 производится вычисление величины 2k+j. Для этого величина j из регистра 77 числа пропускаемых итераций поступает на первый вход сумматора, а величина к из первого регистра 78 числа итераций со сдвигом на один разряд влево в мультиплексоре 82 поступает на второй вход этого же сумматора. Результат суммирования в конце такта заносится во второй регистр 79 числа итераций. В этом же такте анализируется значение индекса итераций k в первом регистре 78 числа итераций. При достижении или превышении им значения п микропрограммный цикл заканчивается и микропрограмма переходит, к своему последнему такту, в котором результат счета по первому выходу 16 результата устройства может быть считан из второго регистра 66 данных.

Во второй микрокоманде цикла в соответствии с рекуррентными соотношениями производится вычисление величины

Wkjf J.- Wk При этом величина Zk подается на вход В суммэтора-вычи- -тателя 76 со сдвигом на 2k+j разрядов вправо, а на вход А подается Wk из третьего регистра 67 данных. Знак операции в сумматоре-вычитателе 76 определяется прямым выходом триггера 68. Результат с выхода сумматора-вычитателя в конце такта записывается в третий регистр 67 данных. Одновременно с этим содержимое регистра 75 суммы через мультиплексор 62 в колце такта переписывается в первый регистр 65 данных. В этом же такте с помощью сумматора 81 осуществляется приращение индекса итераций в первом регистре 78 числа итераций на величину j.

В третьей микрокоманде цикла вычисляется величина QH-J Qk+ ft arctg .. Значение Qk поступает на вход А сумматора-вычитателя 76 из второго регистра 66 данных, на вход В сумматора-вычитателя поступает денормализрванная сдвигателем 73 константа arctg2 + из блока 70 памяти констант. Знак операции определяется прямым выходом триггера 68. В конце такта результат операции записывается во второй регистр 66 данных, а величина j из блока памяти 80 - в регистр числа 77 пропускаемых итераций.

Операция вычисления функций kgsln p. kgcostf в устройстве осуществляется в соответствии со следующими рекуррентными соотношениями:

5Zk+ 2}Zk- (Ok 2kVctg2-(k+i): Qk4,Qk- kWk2-(k+J);

Wk - rWk+ft Qk2(k+J).

sgn uv sgnZk, 0 гДе2о У;

Qo 0;

Wo-1.0;

Zn 0;

Qn -kslnV; 5 Wn Kgcosf.

Первые два такта данной микропрограммы аналогичным первым двум тактам микропрограммы вычисления арктангенса, В следующем, третьем, такте осуществляет- Q ся приращение индекса итераций в первом регистре 78 числа итераций на величину j.

Четвертый такт является первым тактом циклической части микропрограммы. В данной микрокоманде производится вычисле- 5 ние величины Zk+j и запись ее в первый регистр 65 данных. В этом же такте анализируется значение индекса итераций, после чего следует продолжение цикла или выход из него. Во второй микрокоманде цикла Q производится вычисление Qk+j и сохранение ее в регистре 75 суммы. Кроме того, величина пропускаемых операций j записывается в регистр 77 числа пропускаемых итераций. В третьей микрокоманде цикла с вычисляется величина Wk+j и записывается в третий регистр 67 данных, содержимое регистра 75 суммы переписывается-ео второй регистр 66 данных, осуществляется приращение индекса итераций в первом Q регистре 78 числа итераций и запись i о триггер 68.

После этого осуществляется возврат на начало цикла.

Так как в конце цикла во втором регист- 5 ре 66 данных находится величина Qn -kgsin (р. то в первой микрокоманде после цикла производится изменение знака Qn с помощью операции инверсии и прибавления входного переноса в сумматоре-вычитателе

0 6.

В последней микрокоманде результаты вычислений могут быть считаны по выходам устройства: kgsin p из второго регистра 66 данных по первому выходу 16 результата: 5 kgcos p из третьего регистра 67 данных по второму выходу 17 результата устройства.

Учет коэффициента деформации вектора kg в полученных соотношениях может .быть проведен с помощью выполнения операции деления и получения функции tg p.

Учет коэффициента деформации вектора при вычислении синуса и косинуса может быть осуществлен и другим способом - при задании начальных значений и используя синхронный метод цифра за цифрой. Рекуррентные соотношения для данного способа вычислений приведены ниже;

Zk-и Zk-tarcig2 k;

Qk+1 Qk - &Wk 2-k;

Wk+t Wk +ЈkQk2 k;

sgn Јk sgnZk, k 0,i,..., n-1, где Z0 tp;

Qo 0;

W0 1/kg;

Qn -sin tpWn cosy,

В первом такте микропрограммы производится установка начальных значений. В первый регистр 65 данных записывается значение аргумента f, находящееся в диапазоне ±ж/2. во второй регистр 66 данных - ноль, в третий регистр 67 данных - обратная величина коэффициента деформации вектора 1 /кд, регистры числа итераций 77-79 обнуляются.

Второй такт микропрограммы является первым тактом ее циклической части. В этой микрокоманде значение Zk из первого регистра данных 65 через мультиплексор 71, сдвигатель 73 и сумматор 76 пересылается в первый регистр 75 данных. Кроме того, значение Јk, соответствующее старшему знаковому разряду Zk, запоминается в триггере 68 знака; анализируется значение индекса итераций К, при достижении которым значения п происходит выход из цикла.

Во второй микрокоманде ци. производится вычисление величины Z(k+i) в соот- ветствии с первым равенством в рекуррентных соотношениях. При этом величина Zk поступает на вход А сумматора- вычитателя 76 из первого регистра 75 данных, а нормализованная константа из блока 70 памяти денормализуется в сдвига- теле 73 и поступает на вход В сумматора-вы- читэтеля 76.

Во второй и третьей микрокомандах цикла в соответствии с вторым и третьим равенствами в рекуррентных соотношениях вычисляются величины Qk-n, W k-м . При этом значение QM-I, полученные во второй микрокоманде, временно сохраняется в регистре 75 суммы и переписывается из него во второй регистр 66 данных в третьей микрокоманде. Кроме того, в третьей микрокоманде с помощью сумматора 81 осуществляется приращение индекса итераций k на 1.

Последние два такта данной микрокоманды полностью идентичны последним

двум тактам предыдущей микропрограммы.

Формула изобретения Устройство для вычисления функций,

содержащее три регистра данных, первый регистр числа итераций, три мультиплексора промежуточных результатов, сдвигатель, сумматор-вычитатель, сумматор, блок памяти констант, блок памяти числа пропускае0 мых итераций и блок управления, причем выход первого регистра данных соединен с первым информационным входом первого мультиплексора промежуточных результатов, выход второго регистра данных - с

5 вторым информационным входом первого мультиплексора промежуточных результатов, первым информационным входом второго мультиплексора промежуточных результатов и первым выходом результата

0 устройства, выход третьего регистра данных соединен с третьим информационным входом первого мультиплексора промежуточных результатов, вторым информационным входом второго мультиплексора

5 промежуточных результатов и вторым выходом результата устройства, выход первого регистра числа итерации соединен с первым информационным входом третьего мультиплексора промежуточных результатов, вы0 ход которого соединен с входом величины сдвига сдвигателя, выход блока памяти констант соединен с четвертым информационным входом первого и третьим информационным входом второго мультиплексоров

5 промежуточных результатов, выход первого мультиплексора промежуточных результатов - с информационным входом сдвигателя, выход сдвигателя и второго мультиплексора промежуточных результатов соединены со0 ответственно с первым и вторым информационными входами сумматора-вычитателя, выходы старших разрядов первого регистра данных соединены с адресным входом блока памяти числа пропускаемых итераций,

5 установочный вход устройства соединен с входом сброса первого регистра числа итераций, первый тактовый вход устройства соединен с синхронизирующими входами регистров данных и первого регистра числа

0 итерации, отличающеес я тем, что, с целью упрощения, в него введены три мультиплексора входныхданных, мультиплексор знака, мультиплексор числа итерации, регистр суммы, регистр числа пропускаемых

5 итераций, второй регистр числа итерации и триггер, причем входы операндов с первого по третий устройства соединены с первыми информационными входами соответственно первого, второго и третьего мультиплексоров входных данных, выходы которых

соединены с информационными входами соответственно первого, второго и третьего регистров данных, выход сумматора-вычи- тателя соединен с вторыми информационными входами первого, второго и третьего мультиплексоров входных данных и с информационным входом регистра суммы, выход которого соединен с четвертым информационным входом второго мультиплексора промежуточных результатов и третьими информационными входами первого и второго мультиплексоров входных данных, выход знакового разряда первого регистра данных соединен с информационным входом триггера, прямой и инверсный выходы которого соединены с первым и вторым информационными входами мультиплексора знака, выход которого соединен с входом знака операции сумматора-вычита- теля, выход блока памяти числа пропускав- мых итераций соединен с информационным входом регистра числа пропускаемых итераций, выход которого соединен с вторым информационным входом третьего мультиплексора промежуточных результатов и вхо- дом первого слагаемого сумматора, выход которого соединен с информационными входами первого и второго регистров числа пропускаемых итераций, выход первого регистра числа итераций соединен с первым адресным входом блока памяти констант, первым информационным входом мультиплексора числа итераций непосредственно и вторым информационным входом данного мультиплексора со сдвигом на один разряд

в сторону старших разрядов, выход второго регистра числа итераций соединен с третьим информационным входом третьего мультиплексора промежуточных результатов, выход старшего разряда первого регистра числа итерации соединен с входом анализа итераций блока управления, прямой выход триггера соединен с вторым адресным входом блока памяти констант, выход мультиплексора числа итераций соединен с входом второго слагаемого сумматора, установочный вход устройства - с входами сброса второго регистра числа итерации и регистра числа пропускаемых итераций и входом сброса блока управления, тактовый вход ycj тройства - с синхронизирующими входами регистра суммы, второго регистра числа итерации, регистра числа пропускаемых итераций, управляющие входы мультиплексоров входных данных, промежуточных значений, числа итерации, третьи выходы блока памяти констант и мультиплексора знака соединена с соответствующими выходами блока управления, входы сумматора и кода инструкции сумматора-вычитателя и синхронизирующий вход триггера соединены с соответствующими выходами блока управления, входы разрешения записи регистров данных, регистра суммы, первого и второго регистров итерации соединены с соответствующими выходами блока управления, вход кода операции и тактовый вход которого соединены соответственно с входом кода операции и вторым тактовым входом устройства.

&МШ6Мви9505152 5354 5556 57585960 61 ,----

L-T

/Ч/Ч/ЧА/ЧЛ/

/ки

1 ,

L-T

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Вычислительное устройство для поворота вектора | 1979 |

|

SU857979A1 |

| Устройство для быстрого преобразования Фурье | 1986 |

|

SU1392577A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

Изобретение относится к вычислительной технике и может быть использовано R специализированных в ы ; и с л и т о г я х . Целью изобретения является упрощение устройства. Устройство содержит операционный блок, блок управления, установочный вход, первый тактовый вход, второй тактовый вход, входы операндов, выходы результатов, вход кода операции, тактовые выходы блока управления. Операционный блок содержит мультиплексоры, регистры, сумматор, сумма-ор-вычитатель. блоки памяти, сдвигатель. 3 ил.

2й &&27Мг9Л}3132ЯХЭ5ЯЯУвЗШ4Ш

В

F 6

н

t

65

II

54

4

23

22

U

V66

WX

г

Tt

87

21

фиг.З

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

Авторы

Даты

1992-01-15—Публикация

1989-11-09—Подача