ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1988 |

|

SU1520515A1 |

| Двухвходовое устройство приоритета | 1988 |

|

SU1589276A1 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1749896A2 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1474649A1 |

| Многоканальное устройство приоритета | 1986 |

|

SU1352487A2 |

| Многоканальное устройство приоритета для подключения к общей магистрали | 1990 |

|

SU1714601A2 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| Устройство для управления обслуживанием запросов | 1984 |

|

SU1185335A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления доступом к общему ресурсу двух активных устройств вычислительной системы. Цель изобретения - расширение функциональных возможностей за счет управления приоритетами запросов. Двухвходовое устройство приоритета содержит элементы ИЛИ-НЕ 1,2, пороговый элемент 3, триггер 6, элемент И 8, элемент И-НЕ 7. Устройство позволяет в зависимости от важности запросов осуществлять бесприоритетную дисциплину их обслуживания либо дисциплину обслуживания с абсолютными приоритетами. Триггер 6 позволяет фиксировать признак более приоритетного входа на текущем этапе работы устройства, а элементы И 8 и И-НЕ 7 коммутируют сигналы прерывания при работе устройства в режиме абсолютного приоритета. 2 ил.

. /

31495

Изобретение относится к вынисли- тельной технике и может быть использовано для управления доступом к общему ресурсу двух активных устройств вычислительной системы и является усовершенствованием устройства по авт.св.. № 1269132.

Цель изобретения - расширение функциональных возможностей устройст- ва за счет управления приоритетом и запросов.

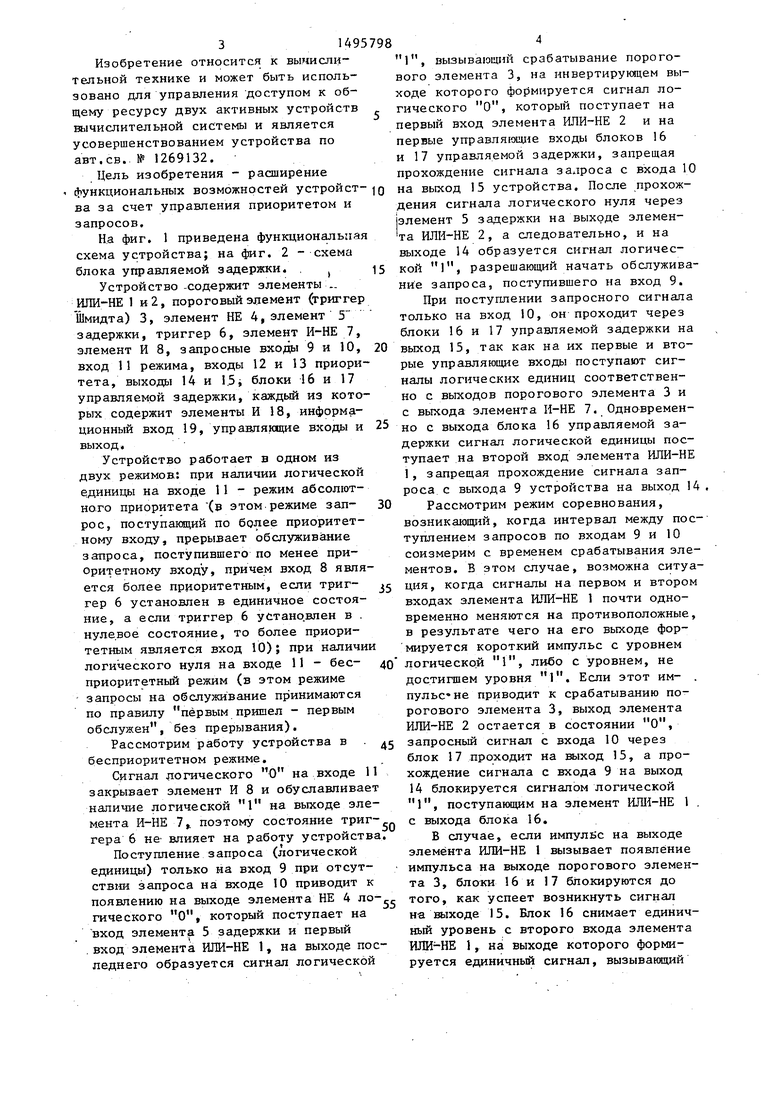

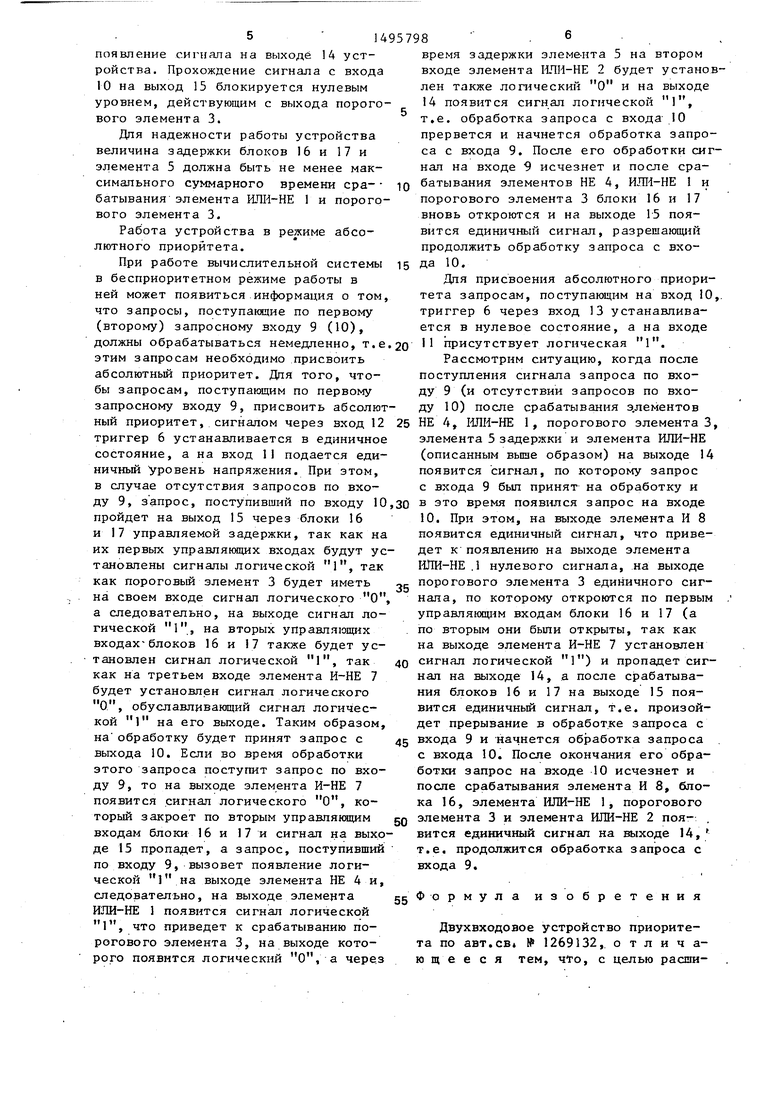

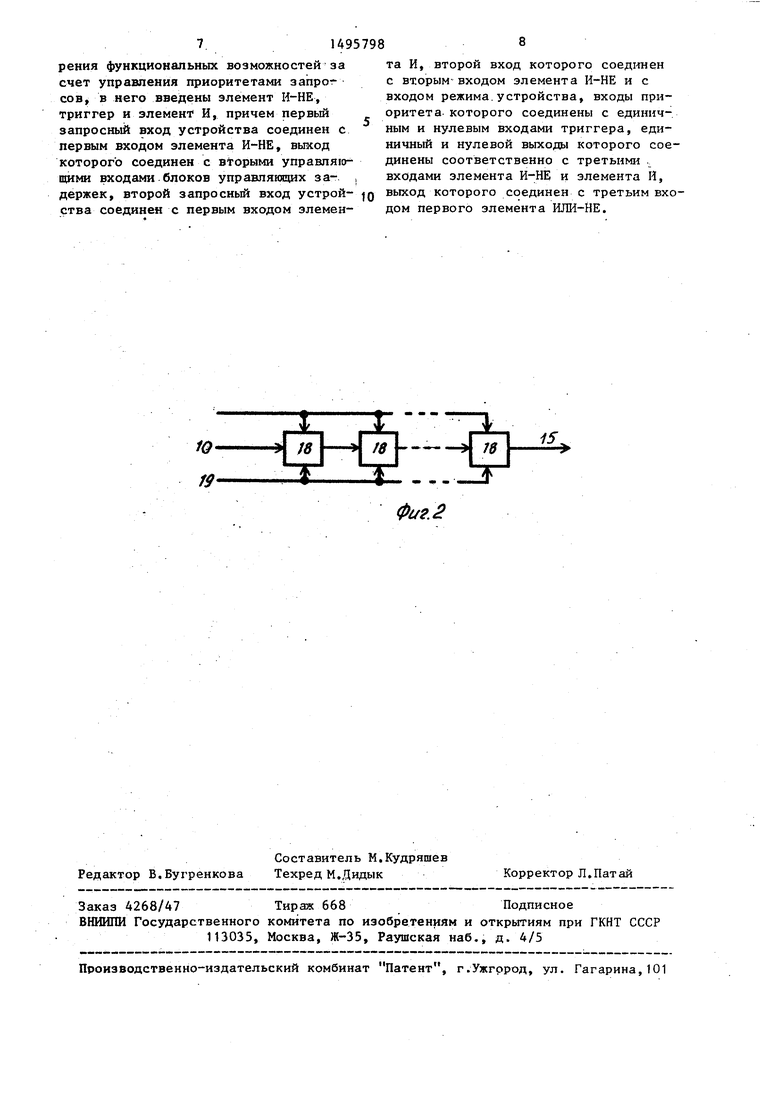

Н,а фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема блока управляемой задержки. ,

Устройство-содержит элементы - ИЛИ-НЕ 1 и 2, пороговый элемент (триггер Шмидта) 3, элемент НЕ 4, элемент 5 задержки, триггер 6, элемент И-НЕ 7, элемент И 8, запросные входы 9 и 10, вход П режима, входы 12 и 13 приоритета, выходы 14 и 1.5 i блоки 16 и 17 управляемой задержки, каждый из которых содержит элементы И 18, информационный вход 19, управляющие входы и выход

Устройство работает в одном из двух режимов: при наличии логической единицы на входе 11 - режим абсолют- но-го приоритета (в этом режиме зал- рос, поступающий по более приоритетному входу, прерывает обслуживание запроса, поступившего по менее приоритетному входу, причем вход 8 является более приоритетным, если триг- гер 6 установлен в единичное состояние, а если триггер 6 устано.влен в . нулевое состояние, то более приоритетным является вход 10); при наличии логического нуля на входе 11 - бес- приоритетный режим (в этом режиме запросы на обслуживание принимаются по правилу первым пришел - первым обслужен, без прерывания).

Рассмотрим работу устройства в . бесприоритетном режиме.

Сигнал логического О на входе 11 закрывает элемент И 8 и обуславливает наличие логической I на выходе элемента И-НЕ 7 поэтому состояние триггера 6 не влияет на работу устройства

Поступление запроса (логической единицы) только на вход 9 при отсутствии запроса на входе 10 приводит к появлению на выходе элемента НЕ 4 логического О, который поступает на вход элемента 5 задержки и первый .вход элемента ИЛИ-НЕ 1, на выходе последнего образуется сигнал логической

Q

5

0 5

0 О

j

5

1, вызывающий срабатывание порогового элемента 3, на инвертирующем выходе которого формируется сигнал логического о, KOTOpbrid поступает на первый вход элемента ИЛИ-НЕ 2 и на первые управля ощие входы блоков 16 и 17 управляемой задержки, запрещая прохождение сигнала залроса с входа 10 на выход 15 устройства. После прохождения сигнала логического нуля через элемент 5 задержки на выходе элемента ИЛИ-НЕ 2, а следовательно, и на выходе 14 образуется сигнал логической 1, разрешающий начать обслуживание запроса, поступившего на вход 9.

При поступлении запросного сигнала только на вход 10, он проходит через блоки 16 и 17 управляемой задержки на выход 15, так как на их первые и вторые управляющие входы поступают сигналы логических единиц соответственно с выходов порогового элемента 3 и с выхода элемента И-НЕ 7. Одновременно с выхода блока 16 управляемой задержки сигнал логической единицы поступает на второй вход элемента ИЛИ-НЕ 1, запрещая прохождение сигнала запроса с выхода 9 устройства на выход 14 .

Рассмотрим режим соревнования, возникающий, когда интервал между поступлением запросов по входам 9 и 10 соизмерим с временем срабатывания элементов. В этом случае, возможна ситуация, когда сигналы на первом и втором входах элемента ИЛИ-НЕ 1 почти одновременно меняются на противоположные, в результате чего на его выходе формируется короткий импульс с уровнем логической 1, либо с уровнем, не достигшем уровня I. Если этот им- . пульс не приводит к срабатыванию порогового элемента 3, выход элемента ИЛИ-НЕ 2 остается в состоянии О, запросный сигнал с входа 10 через блок 17 проходит на выход 15, а прохождение сигнала с входа 9 на выход 14 блокируется сигналом логической 1, поступающим на элемент ШIIi-HE 1 . с выхода блока 16.

В случае, если импулкс на выходе элемента ИЛИ-НЕ 1 вызывает появление импульса на выходе порогового элемента 3, блоки 16 и 17 блокируются до того, как успеет возникнуть сигнал на выходе 15. Блок 16 снимает единичный уровень с второго входа элемента ИЛИ-НЕ 1, на выходе которого формируется единичньй сигнал, вызывающий

появление сигиагга на выходе 14 устройства. Прохождение сигнала с входа 10 на выход 15 блокируется нулевым уровнем, действующим с выхода порогового элемента 3.

Дпя надежности работы устройства величина задержки блоков )6 и 17 и элемента 5 должна быть не менее максимального суммарного времени ера- батывания элемента ИЛИ-НЕ 1 и порогового элемента 3.

Работа устройства в режиме абсолютного приоритета.

При работе вычислительной системы в бесприоритетном режиме работы в ней может появиться информация о том, что запросы, поступакхдие по первому (второму) запросному входу 9 (Ю), должны обрабатываться немедленно, т.е этим запросам необходимо присвоить абсолютньй приоритет. Дпя того, чтобы запросам, поступающим по первому

Рассмотрим ситуацию, когда после поступления сигнала запроса по входу 9 (и отсутствии запросов по входу 10) после срабатывания э.лементов

запросному входу 9, присвоить абсолютный приоритет, сигналом через вход 12 25 НЕ 4, ЮТИ-НЕ 1, порогового элемента 3, триггер 6 устанавливается в единичное элемента 5 задержки и элемента ИЛИ-НЕ состояние, а на вход II подается еди- (описанным выше образом) на выходе 14 ничный уровень напряжения. При этом,появится сигнал, по которому запрос

в случае отсутствия запросов по входу 9, запрос, поступивший по входу 10,30 в это время появился запрос на входе пройдет на выход 15 через блоки 16Ю. При этом, на выходе элемента И 8

и 17 управляемой задержки, так как на их первых управляющих входах будут успоявится единичный сигнал, что приведет к появлению на выходе элемента ИЛИ-НЕ .1 нулевого сигнала, на выходе порогового элемента 3 единичного сигнала, по которому откроются по первым управляюпц1м входам блоки 16 и 17 (а по вторым они были открыты, так как на выходе элемента И-НЕ 7 установлен сигнал логической 1) и пропадет сиг нал на выходе 14, а после с рабатыва- ния блоков 16 и 17 на выходе 15 появится единичный сигнал, т.е. произойдет прерывание в обработке запроса с 45 входа 9 и начнется обработка запроса с входа 10. После окончания его обработки запрос на входе 10 исчезнет и после срабатывания элемента И 8, блока 16, элемента ИЛИ-НЕ 1, порогового элемента 3 и элемента ИЛИ-НЕ 2 поя- вится единичный сигнал на выходе 14, т.е. продолжится обработка запроса с входа 9.

35

40

тановлены сигналы логической 1 , так как пороговый элемент 3 будет иметь на своем входе сигнал логического О, а следовательно, на выходе сигнал логической 1, на вторых управляющих входах блоков 16 и 17 также будет ус- тановлен сигнал логической 1, так как на третьем входе элемента И-НЕ 7 будет установлен сигнал логического О, обуславливающий сигнал логической 1 на его выходе. Таким образом, на обработку будет принят запрос с выхода 10. Если во время обработки этого запроса поступит запрос по входу 9, то на выходе элемента И-НЕ 7 появится сигнал логического О, который закроет по вторым управлягацим входам блоки 16 и 17 и сигнал на выходе 15 пропадет, а запрос, поступивший по входу 9, вызовет появление логической 1 на выходе элемента НЕ 4 и, следовательно, на выходе элемента55

ИЛИ-НЕ 1 появится сигнал логической 1, что приведет к срабатыванию порогового элемента 3, на выходе которого появится логический О, а через

45

50

0

время задержки элемента 5 на втором входе элемента 1ПИ-НЕ 2 будет установлен также логический О и на выходе 14 появится сигнал логической 1, т.е. обработка запроса с входа 10 прервется и начнется обработка запроса с входа 9. После его обработки сигнал на входе 9 исчезнет и после срабатывания элементов НЕ 4, ИЛМ-НЕ 1 и порогового элемента 3 блоки 16 и 17 вновь откроются и на выходе 15 появится единичный сигнал, разрешающ11Й продолжить обработку запроса с вхо- 5 да 10.

Дпя присвоения абсолютного приоритета запросам, поступающим на вход 10,. триггер 6 через вход 13 устанавливается в нулевое состояние, а на входе 11 присутствует логическая 1.

Рассмотрим ситуацию, когда после поступления сигнала запроса по входу 9 (и отсутствии запросов по входу 10) после срабатывания э.лементов

0

5 НЕ 4, ЮТИ-НЕ 1, порогового элемента 3, элемента 5 задержки и элемента ИЛИ-НЕ (описанным выше образом) на выходе 14 появится сигнал, по которому запрос

с входа 9 бып принят на обработку и

появится единичный сигнал, что приведет к появлению на выходе элемента ИЛИ-НЕ .1 нулевого сигнала, на выходе порогового элемента 3 единичного сигнала, по которому откроются по первым управляюпц1м входам блоки 16 и 17 (а по вторым они были открыты, так как на выходе элемента И-НЕ 7 установлен сигнал логической 1) и пропадет сигнал на выходе 14, а после с рабатыва- ния блоков 16 и 17 на выходе 15 появится единичный сигнал, т.е. произойдет прерывание в обработке запроса с входа 9 и начнется обработка запроса с входа 10. После окончания его обработки запрос на входе 10 исчезнет и после срабатывания элемента И 8, блока 16, элемента ИЛИ-НЕ 1, порогового элемента 3 и элемента ИЛИ-НЕ 2 поя- . вится единичный сигнал на выходе 14, т.е. продолжится обработка запроса с входа 9.

Формула изобретения

Двухвходовое устройство приоритета по авт.ев № 1269132, отличающееся тем, что, с целью расши7U95798

рения функциональных возможностей за счет управления приоритетами запрог- сов, в него введены элемент И-НЕ, триггер и элемент И, причем первый запросный вход устройства соединен с первым входом элемента И-НЕ, выход которого соединен с вторыми управпяго- щими входами блоков управляняцих за- , держек, второй запросный вход устрой- ю ства соединен с первым входом злеменД Д. .,

1Q- J8 I4/5 - -И W

fff--«31-Li-1.,. JLi

8

та И, второй вход которого соединен с вторым-входом элемента И-НЕ и с входом режима.устройства, входы приоритета которого соединены с единичным и нулевым входами триггера, единичный и нулевой выходы которого соединены соответственно с третьими входами элемента И-НЕ и элемента И, выход которого соединен с третьим входом первого элемента ИЛИ-НЕ.

Фиг. 2

| Авторское свидетельство СССР № ,1269132, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-15—Подача