Изобретение относится к вычислительной технике, автоматическому контролю и может быть использовано в устройствах прерывания программ, управления потоками данных и формирования исполнительного адреса банков в логических процессорах.

Известно устройство переменного приоритета (авторское свидетельство СССР N 1383353, м.кл. 4 G 06 F 9/46, бюл. N 11, 1988), содержащее триггер, единичный и нулевой входы которого являются входами режима устройства, регистр запросов, разрядные входы которого являются группой запросных входов устройства, первую группу элементов И, первые входы которых объединены и соединены с единичным выходом триггера, второй вход каждого i-го (i=1,2,...,n, где n - число запросных входов) элемента И первой группы соединен соответственно с i - ым (i = 1,2,...,n) разрядным выходом регистра запроса, вторую группу элементов И, первые входы которых объединены и соединены с нулевым выходом триггера, второй вход каждого i - го (i = 1,2,..., n) элемента И второй группы соединен соответственно c j - ым (j=n, n-1,..., 1) разрядным выходом регистра запроса, первую группу элементов ИЛИ, входы которых соединены соответственно с выходами одноименных элементов И первой и второй групп, а выходы - с входами первого элемента ИЛИ, регистр кода приоритета, входы которого являются управляющими входами задания режима устройства, а выходы соединены с одноименными входами дешифратора, третью группу элементов И, инверсные входы которых соединены соответственно с выходами дешифратора, четвертую группу элементов И, первые входы которых соединены с инверсными входами одноименных элементов И третьей группы, вторые входы элементов И четвертой группы объединены и соединены с выходом первого элемента ИЛИ, выход первого элемента И пятой группы соединен с прямым входом второго элемента И третьей группы, выход i - го (i=2,3,...,(n-1)) элемента И пятой группы соединен с прямым входом (i+1) элемента И третьей группы, выход n - го элемента И пятой группы соединен с прямым входом первого элемента И третьей группы, выходы одноименных элементов И четвертой и третьей групп соответственно соединены с входами одноименных элементов ИЛИ второй группы, выходы которых соответственно соединены с первыми входами элементов И шестой группы и прямыми входами элементов И пятой группы, инверсные входы элементов И пятой группы и вторые входы элементов И шестой группы соответственно объединены и соединены с выходами соответствующих одноименных элементов ИЛИ первой группы, выходы элементов И шестой группы соответственно соединены с входами шифратора, выходы которого являются группой информационных выходов устройства.

Признаками аналога, общими с заявляемым техническим решением, являются регистр запросов, шифратор, первая группа элементов И.

Причины, препятствующие достижению требуемого технического результата, заключаются в низкой разрешающей способности при управлении запросами η = 2•C - число разрядов кода маски, N - число входных запросов, при которой каждый запрос (абонент) может иметь только два уровня приоритета и рост аппаратурных затрат при реализации данного устройства.

- число разрядов кода маски, N - число входных запросов, при которой каждый запрос (абонент) может иметь только два уровня приоритета и рост аппаратурных затрат при реализации данного устройства.

Известно устройство переменного приоритета (авторское свидетельство СССР N 1444766, м. кл. 4 G 06 F 9/46, бюл. N 46, 1988), содержащее регистр запросов, две группы элементов И, элемент ИЛИ-НЕ, группу дешифраторов, группу регистров, группу элементов ИЛИ, триггер, первый элемент ИЛИ, элемент И и группу из m блоков формирования максимального кода (m - число запросов), причем группа кодовых входов устройства соединена с группой информационных входов регистров группы, группа входов кода номера абонента устройства соединена с группами входов дешифраторов группы, информационные входы регистра запросов являются запросными устройства, выход каждого дешифратора группы соединен с входом разрешения записи одноименного регистра группы, входы элементов И первой группы являются индикационными выходами устройства, выходы регистра запросов соединены с входами первого элемента ИЛИ, выход которого является сигнальным выходом устройства, отличающееся тем, что с целью расширения области применения за счет обеспечения возможности обслуживания абонентов с абсолютными и относительными приоритетами устройство содержит группы триггеров, элемент ИЛИ- НЕ, второй, третий четвертый элементы ИЛИ-НЕ, причем запросные и ответные входы устройства соединены с элемента ИЛИ-НЕ, ответные входы устройства соединены с входами второго элемента ИЛИ, каждый ответный вход устройства соединен с входом сброса одноименного триггера группы и с одноименным входом сброса регистра запросов, каждый выход которого соединен с входом запуска одноименного блока формирования максимального кода группы, группа выходов каждого регистра группы соединена с первой группой информационных входов одноименного блока формирования максимального кода группы j - й, выход группы выходов каждого из которых (j = 1,2,...,m) соединен с соответствующим входом j - го элемента ИЛИ-НЕ группы, выход которого соединен с j - м входом второй группы информационных входов каждого блока формирования максимального кода группы, индикационный выход каждого блока формирования максимального кода группы соединен с первым входом одноименного элемента И второй группы, выход каждого элемента И второй группы соединен с входом установки в "1" одноименного триггера группы, тактовый вход каждого из триггеров группы соединен с выходом одноименного элемента ИЛИ группы, входы каждого элемента ИЛИ группы соединены с выходами всех триггеров группы, исключая выход одноименного триггера группы, выход элемента ИЛИ-НЕ соединен с вторыми входами всех элементов И второй группы, выход каждого триггера группы соединен с первым входом одноименного элемента И первой группы, выходы элементов И первой группы соединены с входами третьего элемента ИЛИ, выход которого соединен с входом сброса триггера, вход запуска устройства соединен с соответствующим входом второго элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого является первым входом задания режима устройства, выход элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход которого является вторым входом задания режима устройства, выход четвертого элемента ИЛИ соединен с вторыми входами всех элементов И первой группы, информационные входы триггеров группы соединены с входом логического нуля устройства, информационный вход триггера соединен с входом логической единицы устройства.

Признаками аналога, общими с заявляемым техническим решением, являются регистр запроса, группа регистров кода приоритета, триггер, элементы И группы.

Причины, препятствующие достижению требуемого технического результата, заключаются в аппаратурной избыточности в зависимости от роста информационной емкости устройства.

Из известных технических решений наиболее близким по технической сущности к заявляемому объекту является устройство переменного приоритета с шифрацией адреса (авторское свидетельство СССР N 1234837, м. кл. 4 G 06 F 9/46, бюл. N 20, 1986), содержащее регистр запросов, входы которого являются запросными входами устройства, триггер, шифратор, выходы которого являются группой информационных выходов устройства, n регистров приоритета (n - количество источников запросов), группу дешифраторов, группу блоков элементов И, две группы элементов ИЛИ, два блока приоритета, два элемента ИЛИ, m групп элементов И (m - количество кодов приоритета), причем первый блок каждого блока элементов И группы подключен к выходу соответствующего регистра приоритета, вторые входы всех блоков элементов И группы соединены с выходом триггера, группа выходов каждого блока элемента И группы соединена с группой входов соответствующего дешифратора группы, выход i - го  элемента ИЛИ второй группы соединен с i - ым входом второго блока приоритета, группа выходов которого подключена к группе входов шифратора, к группе входов сброса регистра запросов и к группе входов первого элемента ИЛИ, выход которого соединен с входом установки в "О" триггера, вход установки в "1" которого подключен к выходу второго элемента ИЛИ, первый и второй входы которого являются входом сигнала ответа и входом "Пуск" устройства соответственно, при этом третьи входы каждого блока элементов И группы подключены к выходу соответствующего регистра приоритета, входы регистра приоритета являются группой входов кода приоритета устройства.

элемента ИЛИ второй группы соединен с i - ым входом второго блока приоритета, группа выходов которого подключена к группе входов шифратора, к группе входов сброса регистра запросов и к группе входов первого элемента ИЛИ, выход которого соединен с входом установки в "О" триггера, вход установки в "1" которого подключен к выходу второго элемента ИЛИ, первый и второй входы которого являются входом сигнала ответа и входом "Пуск" устройства соответственно, при этом третьи входы каждого блока элементов И группы подключены к выходу соответствующего регистра приоритета, входы регистра приоритета являются группой входов кода приоритета устройства.

В известном устройстве последовательность обслуживания n запросов задается как порядковым номером (i = 1,2,...,n) запроса, так и наделением каждого из n запросов соответствующей кодовой комбинацией из m (m≤n) значений. Не исключена возможность наделения ряда запросов одинаковыми значениями кода приоритета, фиксируемых в регистрах. Определение наиболее приоритетного запроса в момент времени t в известном устройстве реализуется следующим алгоритмом:

1. Единичными запросами выделяются соответствующие им кодовые значения приоритетов.

2. Выделенные кодовые комбинации декодируются дешифраторами, т. е. преобразовываются соответственно в комбинации кода на одно сочетание Сm 1, т.е. в комбинации унитарного кода, положение "1" в комбинации которого отображает десятичный эквивалент (М = 1,2,...,m) декодируемой комбинации кода приоритета. Структура дешифратора соответствует закону кодообразования используемого кода приоритета. Применение других классов кодов для задания приоритета, т. е. для использования данного приоритетного устройства для других ЭВМ потребует применения других дешифраторов, т.е. другого приоритетного устройства.

3. Объединение одноименных выходов дешифраторов логическими элементами ИЛИ в m дизъюнктивных каналов двоичных эквивалентов кодовых значений кодов приоритетов обеспечивает появление единичного сигнала в соответствующих m каналах. Номер канала соответствует номеру комбинации, занимаемой среди m комбинаций.

4. Для выбора наиболее приоритетной комбинации среди декодированных комбинаций кода приоритета предназначен схемно-детерминированный алгоритм приоритетного блока, т.е. отсутствует возможность изменения приоритета.

5. Единичным сигналом с выхода приоритетного блока опрашиваются одноименные выходы всех n дешифраторов посредством элементов И (m групп, в каждой по n элементов), т.е. определяются запросы, имеющие в момент времени t наиболее приоритетное значение (максимальное или минимальное) кодовой комбинации, таких запросов, как уже указывалось, может быть несколько.

6. С помощью приоритетного блока с схемно-заданным приоритетом по значимости порядковых номеров выделяется наиболее приоритетный запрос с последующим кодированием его адреса.

7. Переводом в "0" состояние разрядного триггера, номер разряда которого соответствует номеру выделенного запроса, запросного регистра и триггера управления, осуществляется переход к обслуживанию следующего приоритетного запроса.

Недостатками прототипа являются ограниченность области применения, поскольку структура устройства предназначена для только определенного класса кода приоритета, отсутствие контроля порога прерывания, т.е. связи схемного и программного уровней прерывания ЭВМ, и значительные аппаратурные затраты в связи с избыточностью и сложностью процедуры определения наиболее приоритетной кодовой комбинации (пп 2, 3, 4, 5 вышеперечисленных шагов алгоритма и соответствующих элементов схемы: n дешифраторов, m элементов И, приоритетного блока, mxn элементов И).

Задача, на решение которой направлено заявляемое изобретение, заключается в расширении функциональных возможностей и сокращения аппаратурных затрат за счет параллельно-порязрядного сравнения кодов приоритета.

Технический результат, достигаемый при осуществлении изобретения, заключается в расширении функциональных возможностей, достигаемым повышением на порядок информативности устройства и обеспечением режима маскирования запросов, кроме того, более чем в десять раз понижаются аппаратные затраты и обеспечивается более однородная структура.

Технический результат, который может быть получен при осуществлении изобретения, достигается тем, что в устройство переменного приоритета, содержащее регистр запросов, содержащий группу запросных входов, которые являются группой запросных входов устройства, и два входа задания режима, блок приоритета, содержащий два входа задания режима, соединенные с входами задания режима регистра запросов, и n входов управления, являющихся одноименными входами устройства, две группы элементов ИЛИ и группу элементов И, выходы блока приоритета соединены с входами шифратора, выходы которого являются информационными выходами устройства, с входами сброса регистра запросов и с входами первого элемента ИЛИ, выход которого соединен с нулевым входом триггера, второй элемент ИЛИ, первый и второй входы которого являются входами сигналов "Ответ" и "Пуск" устройства соответственно, n 1- разрядных регистров приоритета (n - количество источников запросов), входы которых являются входами задания кодов приоритета источников запросов устройства, n групп разрядных элементов И по l элементов в каждой группе, первые входы которых погруппно объединены и соединены с соответствующими выходами регистра запросов, вторые входы всех разрядных элементов И групп соединены с единичным выходом триггера, выходы регистров приоритетов поразрядно соединены с третьими входами разрядных элементов И соответствующих групп, дополнительно введены первый элемент И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход первого элемента И соединен с выходом третьего элемента ИЛИ, входы которого соединены соответственно с запросными входами регистра запросов, а выход первого элемента И соединен с единичным входом триггера, n логических блоков, информационные входы которых соответственно разрядам и группам соединены с выходами разрядных элементов И групп, причем каждый логический блок содержит в каждом разряде, кроме первого, вторые элементы И, первые входы которых являются соответствующими (2,3,...l)-информационными входами логического блока, третьи элементы И, первые входы которых поразрядно объединены со вторыми входами вторых элементов И, четвертые элементы ИЛИ, первые входы которых в каждом разряде соединены с выходами вторых элементов И, а вторые входы - с выходами третьих элементов И, выход каждого четвертого элемента ИЛИ i -то разряда (где i=1,2,...,l-1) соединен с объединенными входами второго и третьего элементов И последующего разряда, выход четвертого элемента ИЛИ l разряда является информационным выходом логического блока, в первом разряде каждого логического блока содержится пятый элемент ИЛИ, первый вход пятого элемента ИЛИ является первым информационным входом этого логического блока, выход пятого элемента ИЛИ соединен с объединенными вторым входом второго элемента И и первым входом третьего элемента И второго разряда этого логического блока, входы первого элемента ИЛИ первой группы соединены с первыми информационными входами n логических блоков, нулевой выход первого элемента ИЛИ первой группы соединен с объединенными вторыми входами пятых элементов ИЛИ n логических блоков, входы j - ого (j= 2,3,...l) элемента ИЛИ первой группы соединены с выходами вторых элементов И (j-1)-го разряда n логических блоков, а нулевой выход упомянутого элемента ИЛИ соединен с объединенными вторыми входами третьих элементов И (j- 1)-го разряда n логических блоков, первые входы первой группы элементов И соответственно соединены с единичными выходами элементов ИЛИ первой группы, а вторые входы объединены и соединены с выходом шестого элемента ИЛИ, входы которого соединены с информационными выходами логических блоков, первые входы второй группы элементов И соединены с информационными выходами соответствующих логических блоков, вторые входы упомянутых элементов И объединены, а выходы соответственно соединены с информационными входами блока приоритета, устройство также содержит вторую группу элементов ИЛИ, (n+1)-ый и (n+2)-ой идентичные логические блоки, информационные входы (n+1)-го логического блока соответственно соединены с выходами элементов И первой группы (n+2)-ой логический блок, информационные входы которого соответственно соединены с выходами (n+1)-го регистра приоритета, входы которого являются входами задания кода наивысшего приоритета устройства, входы первого элемента ИЛИ второй группы соединены с первыми информационными входами (n+1)-го и (n+2)-го логических блоков, нулевой выход первого элемента ИЛИ второй группы соединен с объединенными вторыми входами пятых элементов ИЛИ (n+1)-го и (n+2)-го логических блоков, входы j - го (j=2,3,...,l) элемента ИЛИ второй группы соединены с выходами вторых элементов И (j-1)-го разряда (n+1)-го и (n+2)-го логических блоков, а нулевой выход упомянутого элемента ИЛИ соединен с объединенными вторыми входами третьих элементов И (j- 1)-го разряда (n+1)-го и (n+2)-го логических блоков, первые входы четвертого и пятого элементов И объединены и соединены с информационным выходом (n+1)-го логического блока, вторые входы также объединены, причем второй вход четвертого элемента И - инверсный, и соединены с информационным выходом (n+2)-го логического блока, входы седьмого элемента ИЛИ соединены с выходами четвертого и пятого элементов И, а выход соединен с объединенными вторыми входами элементов И второй группы, вход элемента задержки соединен с единичным выходом триггера, а выход с третьими входами элементов И второй группы и с третьими входами четвертого и пятого элементов И.

Наличие отличительных признаков: введение (n+2) логических блоков, трех групп элементов И, шестого элемента ИЛИ, (n+1)-го регистра приоритета, четвертого и пятого элемента И, седьмого элемента ИЛИ и элемента задержки с соответствующими связями обуславливают соответствие заявляемого технического решения критерию "новизна".

В основу работы положен известный метод, основанный на положениях порядковой логики.

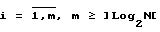

Пусть дана входная последовательность случайных чисел X={x1,x2,...,xn}. Используя некоторые функциональные зависимости, этот ряд необходимо упорядочить, т.е. Y=F(x1,X2,...,xn)=xAdr (1) > xAdr (2) >...> xAdr (n) , причем аргумент x является непрерывным, т. е. xi∈ {a,b} В качестве такой зависимости строятся так называемые порядковые функции, вида:

где r - адрес члена в вариационном ряде

- число сочетаний из i - элементов по N.

- число сочетаний из i - элементов по N.

Построив эти функции, получим вариационный ряд вида Y=x(1) > x(2) >...> x(N).

На практике имеет смысл ставить задачу так: предлагаемое устройство должно реализовывать метод выбора одного или более запросов, имеющих среди n запросов наиболее приоритетное значение кодовой комбинации, с последующим приоритетным кодированием согласно априорно задаваемой приоритетной последовательности.

Этот метод основан на параллельно-поразрядном сравнении кодов приоритета (независимо от класса кода) с выделением только того запроса (либо запросов), имеющего (имеющих) наиболее приоритетное (например, максимальное) значение кодовой комбинации среди кодовых значений приоритетов запросов, имеющих единичное значение на момент анализа в соответствующих разрядах регистра запросов.

Если таким кодовым значением наделен только один единичный запрос, адрес его кодируется непосредственно, если же несколько - выделяется наиболее приоритетный единичный запрос согласно априорно задаваемой последовательности приоритетов. Число возможных вариантов выбора единичного запроса и последовательности кодирования всех единичных запросов задается значениями управляющих сигналов на входах блока приоритета. Число приоритетных уровней, которыми наделяется предлагаемое устройство, может быть определенно как:

M = Cn i2i2(CK i)2,

где n - число кодовых значений приоритета, m=21, m≤n;

l - число единичных векторов в момент времени t, i ∈ {l,n}

К - число единичных запросов, имеющих одинаковые значения кодов приоритета.

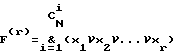

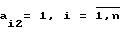

Итак, совокупность кодовых сигналов приоритета запросов, коммутируемых на запросные входы логических блоков, представляется квазиматрицей кодовых значений, логически умноженных на матрицу-столбец сигналов - запросов:

где aij∈ {0,1} - элементы кодовых комбинаций, Ii∈ {0,1} - сигналы запроса в момент времени t,

i=l,...,n, j=l,...l, - номер разрядного коэффициента аij.

Тогда совокупность кодовых сигналов на входах логических блоков в момент времени t отобразится квазиматрицей (если I2 = 1, I5 = 1, I7 = 1, I(n-1) = 1, In = 1).

Примечание: в обозначениях старший разряд нумеруется "1",..., младший l в соответствии с нумерацией элементов матрицы.

Таким образом, число строк и их порядковые номера в квазиматрице определяются порядковыми номерами элементов матрицы-столбца с единичными значениями сигналов запросов на момент времени t. В логических блоках, начиная со старшего разряда, определяется максимальное значение старшего разряда (первых элементов матрицы кодов приоритета)

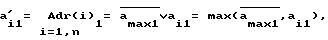

Адреса запросов, имеющих в старшем разряде единичное значение, определяются операцией:

i=l,n (согласно примера i=2,5,7,n-1,n).

Эта операция позволяет также индицировать адреса всех запросов при условии равенства старшего разряда кодов приоритета нулевому уровню.

Таким образом, единичный адрес Adr(Ii) = 1, i=1,...,n будут иметь либо все единичные запросы (Ii=1), т.е. разрядные коэффициенты у которых нулевой уровень  , либо только те, у которых разрядные коэффициенты имеют единичный уровень, т.е.

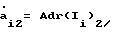

, либо только те, у которых разрядные коэффициенты имеют единичный уровень, т.е.  . На втором шаге реализации метода определяются минимальные значения коэффициентов второго (после старшего) разряда в каждом запросе, относительно значений адресов запросов после первого анализа:

. На втором шаге реализации метода определяются минимальные значения коэффициентов второго (после старшего) разряда в каждом запросе, относительно значений адресов запросов после первого анализа:

т. е. этой операцией определяется адрес единичного запроса, имеющегося в кодовой комбинации аi2 = 1. При  - этот сигнал является адресом соответствующего ему запроса.

- этот сигнал является адресом соответствующего ему запроса.

При условии равенства коэффициентов второго разряда нулевому уровню у всех запросов индицируется адрес запросов на уровне второго разряда, определяется как:

где

Общий адрес запросов по результатам анализа состояния разрядных коэффициентов второго разряда (элементов второго столбца матрицы кодов приоритета) определяется как:

Единичные запросы, у которых первые (старшие разрядные коэффициенты) наделены нулевым уровнем ai1 = 0, имеют адрес  . Следовательно, такие запросы и на втором шаге анализа состояния разрядных коэффициентов независимо уже от их состояния будут иметь вид Adr(Ii)2=0, т.е. даже при условии

. Следовательно, такие запросы и на втором шаге анализа состояния разрядных коэффициентов независимо уже от их состояния будут иметь вид Adr(Ii)2=0, т.е. даже при условии  и т.д. до l - го шага, т.е. единичные сигналы будут на выходах только тех логических блоков, на которые поданы одинаковые коды приоритета, содержащие "1" - цы в старших разрядах.

и т.д. до l - го шага, т.е. единичные сигналы будут на выходах только тех логических блоков, на которые поданы одинаковые коды приоритета, содержащие "1" - цы в старших разрядах.

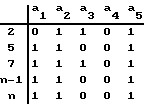

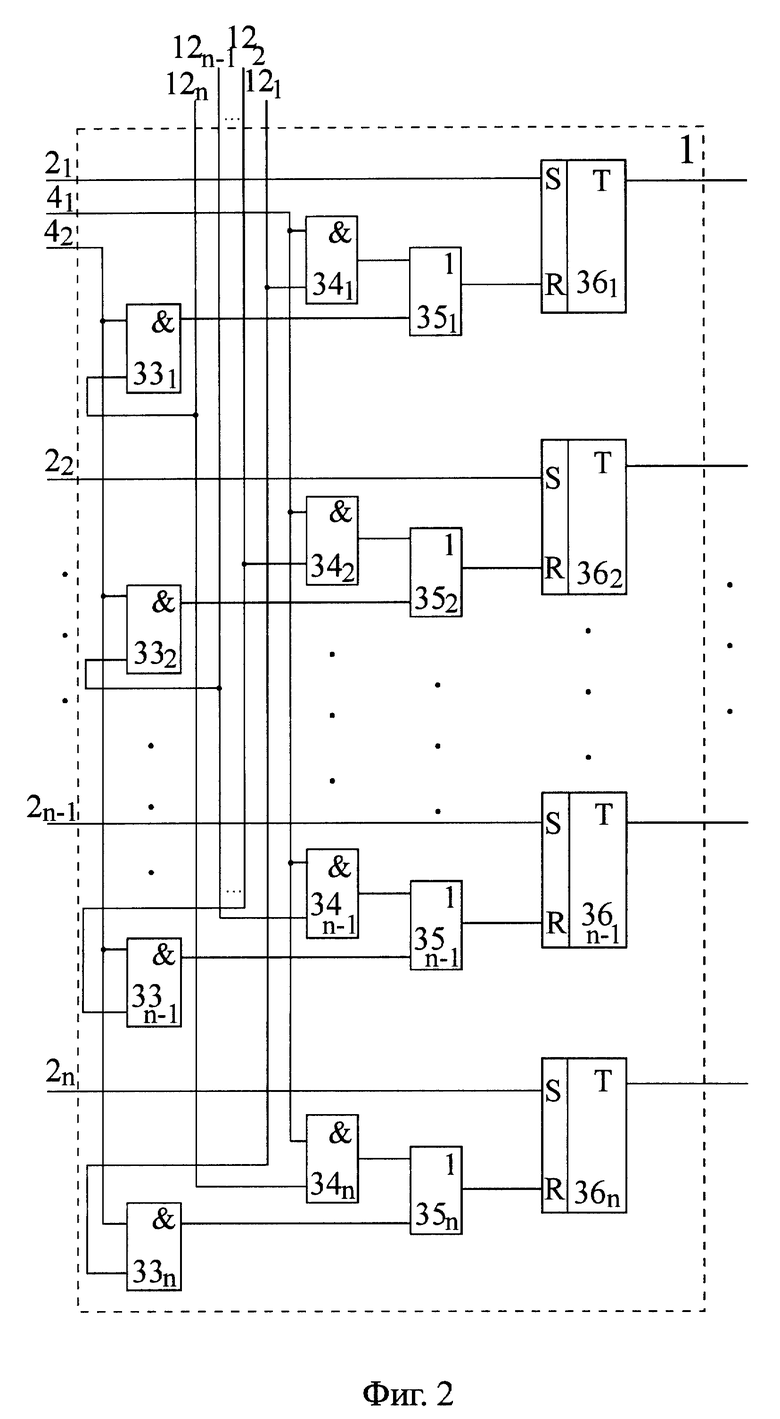

Предполагаемое изобретение поясняется чертежами, где на фиг. 1 приведена структурная схема устройства, на фиг. 2 - структурная схема регистра запросов, на фиг. 3 - структурная схема блока приоритета, на фиг. 4 - таблица функционирования устройства, на фиг. 5 - таблица аппаратных ресурсов.

Устройство содержит (фиг. 1) регистр 1 запросов (РЗ), содержащий запросные входы 2 (21,...,2n), которые являются группой запросных входов устройства, два входа задания режима, блок 3 приоритета (БП), содержащий входы 4 (41;42) задания режима, соединенные с входами задания режима регистра запросов 1, и n входов 5 (51,...,5n) управления, являющихся одноименными входами устройства, две группы элементов ИЛИ (6 и 7 соответственно) и группу элементов И 8, выходы 9 (91,...,9n) блока 3 приоритета соединены с одноименными входами шифратора 10 (ШК), выходы которого являются информационными выходами 11 (111,...,11n) устройства, с входами 12 (121,...,12n) сброса регистра 1 запросов и с входами первого элемента ИЛИ 13, выход которого соединен с нулевым входом триггера 14, второй элемент ИЛИ 15, первый и второй входы (входы 16, 17 соответственно) которого являются входами сигналов "Ответ" и "Пуск" устройства соответственно, а выход соединен с первым входом первого элемента И 18, второй вход которого соединен с выходом третьего элемента ИЛИ 19, входы которого соединены соответственно с запросными входами регистра 1 запросов, а выход первого элемента И 18 соединен с единичным входом триггера 14, n l-разрядных регистров 20 (201-20n) приоритета (РП) (n - количество источников запросов), входы 21 (21,...,21n) которых являются входами задания кодов приоритета источникам запросов устройства, n групп разрядных элементов И 22 (221 1 - 22l 1; - 22l 2 - 22l 2;...,221 n - 22l n) по l элементов в каждой группе, первые входы которых погруппно объединены и соединены с соответствующими выходами регистра 1 запросов, вторые входы всех разрядных элементов И 22 (221 1 - 22l 1; 22l 2 - 22l 2;...,221 n - 22l n) групп соединены с единичным выходом триггера 14, выходы регистров 20 (201,...,20n) приоритетов поразрядно соединены с третьими входами разрядных элементов И 22 (221 1 - 22l 1; . 221 2 - 22l 2;..,221 n - 22l n) соответствующих групп, n - логических блоков 23 (231,...,23n), информационные входы которых соответственно разрядам и группам соединены с выходами разрядных элементов И 22 (221 1 - 22l 1; 221 2 - 22l 2;..,221 n - 22l n) групп, причем каждый логический блок 23 (231,... ,23n) содержит в каждом разряде, кроме первого, вторые элементы И 24 (241 1 - 24l 1, 241 2 - 24l 2, . ..,241 n - 24l n), первые входы которых являются соответствующими (2,3,...,l) информационными входами логических блоков 23 (231,. . . 23n), третьи элементы И 25 (251 1 - 25l 1, 251 2 - 25l 2,...251 n - 25l n), первые входы которых поразрядно объединены со вторыми входами вторых элементов И 24 (241 1 - 24l 1, 241 2 - 24l 2,...,241 n - 24l n), четвертые элементы ИЛИ 26 (261 1 - 26l 1, 261 2 - 26l 2,...,261 n - 26l n), первые входы которых в каждом разряде соединены с выходами вторых элементов И 24(241 1 - 24l 1, 241 2 - 24l 2,...,241 n - 24l n), a вторые входы - с выходами третьих элементов И 25 (251 1 - 25l 1, 251 2 - 25l 2,...251 n - 25l n), выход каждого четвертого элемента ИЛИ 26 i-го разряда (i=2,3,...l-1) соединен с объединенными входами второго и третьего элементов И 24 и И 25 последующего разряда, выход четвертого элемента ИЛИ 26 l - го разряда является информационным выходом логического блока 23 (231, ...,23n), в первом разряде каждого логического блока 23 (231 - 23n) содержатся пятые элементы ИЛИ 27 (271 1,271 2,...,271 n), первый вход каждого пятого элемента ИЛИ 27 (271 1,271 2,...,271 n) является первым информационным входом этого логического блока 23, выход каждого пятого элемента ИЛИ 27 (271 1, 271 2,...,271 n), соединены с объединенным вторым входом второго элемента И 24 (241 1, 241 2, ...,241 n) и первым входом третьего элемента И 25 (251 1, 251 2,...,251 n) второго разряда этого логического блока, входы первого элемента ИЛИ 6, первой группы соединены с первыми информационными входами n логических блоков 23 (231,...,23n), нулевой выход первого элемента ИЛИ 61 первой группы соединен с объединенными вторыми входами пятых элементов ИЛИ 27 (271 1, 271 2, ...,271 n) n логических блоков 23 (231,...,23n), входы j-ого (j=2,3,...,l) элемента ИЛИ 6 (62,63,...,61) первой группы соединены с выходами вторых элементов И 24 (241 1 - 24l 1,241 2 - 24l 2,...,241 n - 24l n) (j-1) - го разряда n логических блоков 23 (231 - 23n), а нулевой выход упомянутого элемента ИЛИ соединен с объединенными вторыми входами третьих элементов И 25 (251 1 - 25l 1, 251 2 - 25l 2,...,251 n - 25l n) (j-1) - го разряда n логических блоков 23 (231,...,23n), первые входы первой группы элементов И 8 (81,..., 8l) соответственно соединены с единичными выходами элементов ИЛИ 6 (61,..., 6l) первой группы, а вторые входы объединены и соединены с выходом шестого элемента ИЛИ 28, входы которого соединены с информационными выходами логических блоков 23, первые входы второй группы элементов И 29 (291,...,29n) соединены с информационными выходами соответствующих логических блоков 23, вторые входы упомянутых элементов И объединены, а выходы соответственно соединены с информационными входами блока 3 приоритета, устройство также содержит вторую группу элементов ИЛИ 7 (71 - 7l), (n+1)-ый и (n+2)-ой идентичные логические блоки (23(n+1) и 23(n+2) соответственно), информационные входы (n+1) -ого логического блока 23n+1 соответственно соединены с выходами элементов И 8 (81,...,8l) первой группы, (n+2) - ой логический блок 23(n+2), информационные входы которого соответственно соединены с выходами (n+1)-го регистра 20(n+1) приоритета, входы 21(n+1) которого являются входами задания кода наивысшего приоритета устройства, входы первого элемента ИЛИ 71, второй группы соединены с первыми информационными входами (n+1) - го и (n+2) - го логических блоков 23(n+1) и 23(n+2), нулевой выход первого элемента ИЛИ 71, второй группы соединен с объединенными вторыми входами пятых элементов ИЛИ 27(n+1) (n+1) - го логического блока и ИЛИ 27(n+1) (n+2) - го логического блока, входы j -ого (j=2,3,...l) элемента ИЛИ 7 (72,73,...,7l) второй группы соединены с выходами вторых элементов И 24 (241 (n+1), 242 (n+1),...,24l (n+1)) и И 24 (241 (n+2), 242 (n+2),...,24l (n+2)) (j-1)-го разряда (n+l) - го и (n+2) - го логических блоков 23(n+1) и 23(n+2), а нулевой выход упомянутого элемента ИЛИ соединен с объединенными вторыми входами третьих элементов И 25 (251 n+1,252 (n+1),...,25l (n+1)) и И 25 (251 (n+2),252 (n+2),...,25l (n+2)) (j-1) -го разряда (n+l) - го и (n+2) - го логических блоков 23(n+1) и 23(n+2), первые входы четвертого и пятого элементов И 301 и И 302 объединены и соединены с информационным выходом (n+l) - го логического блока 23(n+1), вторые входы также объединены, причем второй вход четвертого элемента И 301 - инверсный, и соединены с информационным выходом (n+2) - го логического блока 23(n+2), входы седьмого элемента ИЛИ 31 соединены с выходами четвертого и пятого элементов И 301, и И 302, а выход соединен с объединенными вторыми входами элементов И 29 (291,...,29n) второй группы, вход элемента задержки 32 соединен с единичным выходом триггера 14, а выход - с третьими входами элементов И 29 второй группы и с третьими входами четвертого и пятого элементов И 301 и И 302 соответственно.

Регистр 1 запроса содержит (фиг. 2) первую группу элементов И 33 (331,.. . ,33n), первые входы которых объединены и являются входом 42 задания режима сброса регистра 1 запроса, вторые входы i - го (i- =l,2,...,n) элемента И 33 соответственно соединены с j-ым входом сброса регистра запроса (j=n,n-1,..., 2,1), вторую группу элементов И 34 (341,...,34n), первые входы которых объединены и являются входом 41 задания режима сброса, вторые входы i - го (i - го (i = 1, 2,..., n) элемента И 34 соответственно соединены с j-ым входом сброса регистра запроса (j=1,2,..., n), первую группу элементов ИЛИ 35 (351, . . . , 35n) первые входы которых соединены с соответствующими выходами элементов И 33 первой группы, а вторые входы - с соответствующими выходами элементов И 34 второй группы, выходы элементов ИЛИ 35 первой группы соединены с нулевыми входами триггеров 36 (361,...,36n), единичные входы которых являются запросными входами 2 (21,...,2n) регистра запроса, а выходы являются разрядными выходами регистра запроса.

Блок 3 приоритета содержит (фиг. 3) триггер 37, единичный и нулевой входы которого являются входами 4 (41,;42) задания режима перестраиваемого блока приоритета, первую группу элементов И 38 (381,...,38n), первые входы которых объединены и соединены с единичным выходом триггера 37, второй вход каждого i-го (i= 7,2,..., n) элемента И 38 первой группы является информационным входом 29 (291,...,29n) блока 3 приоритета, вторую группу элементов И 39 (391,...,39n), первые входы которых объединены с нулевым выходом триггера 37, второй вход каждого i-го (i=1,2,...,n) элемента И 39 второй группы соединен соответственно с j (j=n,n-1,...1) - ым информационным входом 29 (291, . ..,29n) блока 3 приоритета, первую группу элементов ИЛИ 40 (401,..., 40n), входы которых соединены соответственно с выходами одноименных элементов И 38 (381,...,38n) и И 39 (391,...,39n) соответственно первой и второй групп, а выходы - с входами первого элемента ИЛИ 41, регистр 42 кода приоритета (РКП), входы которого являются управляющими входами 5 (51,...,5n) блока 3 приоритета, а выходы - соединены с одноименными входами дешифратора 43 кода приоритета (ДКП), третью группу элементов И 44 (441,...,44n), инверсные входы которых соответственно соединены с выходами дешифратора 43, четвертую группу элементов И 45 (451,...,45n, первые входы которых соединены с инверсными входами одноименных элементов И 44 (441,...,44n) третьей группы, вторые входы элементов И 45 (451,..,45n) четвертой группы объединены и соединены с выходом первого элемента ИЛИ 41, выход первого элемента И 461 пятой группы соединен с прямым входом второго элемента И 442 третьей группы, выход i - го (i= 2,3, ...,(n-1)) элемента И 46i, пятой группы соединен с прямым входом (i+1)-го элемента И 44(i+1) третьей группы, выход n - го элемента И 46n, пятой группы соединен с прямым входом первого элемента И 441 третьей группы, выходы одноименных элементов И 45 (451,...,45n) и И 44 (441,...,44n) соответственно четвертой и третьей групп соответственно соединены с входами одноименных элементов ИЛИ 47 (471,...,47n) второй группы, выходы которых соответственно соединены с первыми входами элементов И 48 (481,...,48n) шестой группы и прямыми входами элементов И 46 (461,...,46n) пятой группы, инверсные входы элементов И 46 (461,...,46n) и вторые входы элементов И 48 (481,...,48n) шестой группы соответственно объединены и соединены с выходами соответствующих элементов ИЛИ 40 (401,...,40n) первой группы, выходы элементов И 48 (481,...,48n) шестой группы являются разрядными выходами 6 (61,. ..,6n) перестраиваемого блока приоритета.

Устройство работает следующим образом. По запросным входам 21,...,2n (см. фиг. 1) в произвольные моменты времени поступают единичные сигналы запросов на обслуживание, которые фиксируются в соответствующих разрядах регистра 1 запроса. Разрядность регистра 1 запросов равна числу абонентов n, причем номер разряда регистра 1 запросов определяет его статический приоритет. Коды приоритета, соответствующие каждому запросу, априори задаются управляющей ЭВМ (оператором) и могут быть вычислены, например, на основании статистических данных, таких как частность Pi * появления i - го сигнала запроса, среди n запросов, в определенный промежуток времени. Коды приоритета поступают на входы 21 (211,...,21n) устройства и фиксируются в регистрах 20 (201, . . .,20n) кода приоритета. Принятие решения о выборе наиболее приоритетного запроса среди запросов с одинаковым кодом приоритета также осуществляется управляющей ЭВМ (оператором) и задается в виде единичных сигналов, поданных на входы 4 (41,42) задания режима и на управляющие входы 5 (51,...,5n) блока 3 приоритета.

Для динамической и гибкой перестройки варьирования системой приоритетов в процессе контроля предлагаемое устройство наделено свойством перестраиваемости при минимальных аппаратных затратах, т.е. должно обладать свойством универсальности и практически удовлетворять потребностям ЭВМ различного назначения.

В исходном состоянии триггер 14 находится в нулевом состоянии. В регистрах 20 приоритета приняты коды приоритета, а в регистр 1 - запросы на обслуживание от абонентов. Работа устройства начинается по сигналу "Пуск", поступающему по входу через элемент ИЛИ 15 и элемент И 18, и наличию хотя бы одного запроса на входах регистра 1 запросов, поступающих через элемент ИЛИ 19 и элемент И 18 и устанавливающему триггер 14 в единичное состояние.

Пусть в регистре 1 запросов зафиксированы заявки на обслуживание, пришедшие на второй, пятый, седьмой, (n-1)-ый, n - ый входы регистра 1 запросов. Соответственно в регистрах 202, 205, 207, 20(n-1), 20n кода приоритета зафиксированы коды приоритетов

Единичным сигналом с выхода триггера 14, установленного в единичное состояние сигналом "Пуск" и единичными сигналами второго, пятого, седьмого, (n-1)-то и n - го разрядов регистра 1 указанные коды приоритета, посредством 2, 5, 7, (n-1), n групп разрядных элементов И 22 коммутируются на разрядные входы логических блоков 232,235, 237, 23n-1,23n (см. фиг. 4).

В логических блоках 232, 235, 237, 23n+1, 23n осуществляется операция поразрядного сравнения кодов приоритета, запросы которых поступили на входы регистра 1 запросов. Сравнение начинается со старшего разряда, которому соответствуют первые информационные входы логических блоков (согласно фиг. 4). На первые информационные входы логических блоков 235,237,23n-1,23n поступают сигналы "1", которые одновременно поступают на входы элемента ИЛИ 61, на инверсном входе которого устанавливается сигнал "0". С выходов элементов ИЛИ 275, ИЛИ 277, ИЛИ 27(n-1), ИЛИ 27n единичные сигналы поступают на вторые входы элементов И 241 5, И 241 7, И 241 n-1, И 241 n и на первые входы элементов И 251 5, И 251 7, И 251 n-1 И25n 1в соответствующем логическом блоке 23. На вторые информационные входы (на первые входы элементов И 241 2, И 241 5, И 241 7, И 241 (n-1), И 241 n) поступают единичные сигналы второго по значимости разряда кодов приоритета соответственно во втором, пятом, седьмом, (n-1) - ом, n - ом логических блоков 23. Единичный сигнал с выходов элементов И 241 5, И 241 7, И 241 n-1, И 241 n поступит на входы соответствующих элементов ИЛИ 26 и на вход элемента ИЛИ 62, на инверсном выходе которого установится сигнал "0". На выходах элементов ИЛИ 261 5, ИЛИ 261 7, ИЛИ 261 n-1, ИЛИ 261 n установятся сигналы "1". На третий информационный вход логического блока 237 поступает единичный сигнал. Соответственно на выходе элемента И 242 7 появится сигнал "1", который поступит на входы элемента ИЛИ 63, на инверсном выходе которого появится сигнал "0", поступающий на вторые входы элементов И 252 i (i=7,2,...,n), где i - номер логического блока. Таким образом, единичные сигналы в 5-ом, (n-1)-ом и n-ом логических блоках 23 не имеют возможности дальнейшего "продвижения" по логической цепи к выходам логических блоков 235, 23n-1, 23n. На четвертый информационный вход логического блока 237 поступает "0"-ое значение кодовой комбинации, соответственно на выходе элемента И 243 7 - сигнал "0", на входы элемента ИЛИ 64 поступают сигналы "0", на инверсном выходе которого устанавливается сигнал "1", поступающий на вторые входы элементов И 253 i (i= 1,2,...,n). Т.к. на первый вход элемента И 253 7 подан единичный сигнал с выхода элемента ИЛИ 253 7, а на второй вход - единичный сигнал с инверсного выхода элемента ИЛИ 64, то на выходе элемента ИЛИ 263 7 появится "1". И т.д. согласно вышеописанному алгоритму единичный сигнал появится на выходе седьмого логического блока 237. На прямых выходах элементов ИЛИ 6 (61,...,6l,) будет иметь место экстремальный код седьмого запроса, который через элементы И 8 (81,...,8l) поступает на информационные входы (n+1) - то логического блока 23n+1. Регистр кода приоритета 20n+1 предназначен для приема от ЭВМ (оператора) кода, более приоритетного, чем обрабатываемый, для осуществления в случае необходимости операции прерывания обрабатываемого запроса. Пусть на регистр кода приоритета 20n+1 не поступает код (режим прерывания обрабатываемого запроса или маскирования рассмотрим ниже), вызывающий прерывание обрабатываемого запроса, тогда на выходе логического блока 23n+1 появится единичный сигнал. С выхода триггера 14, установленного в единичное состояние, единичный сигнал через элемент задержки 32 с величиной задержки, равной времени обработки сигнала логическим блоком 23, поступает на входы элементов И 29 (291,..., 29n), И 301 и И 302. Единичный сигнал с выхода элемента ИЛИ 31 разрешает прохождение единичного сигнала с выхода седьмого логического блока 237 на информационные входы блока 3 приоритета, на входы 4 задания режима подаются сигналы задания направления обслуживания (пусть подается единичный сигнал на вход 41 или 42, в данном случае это не имеет значения). Это существенно тогда, когда на информационные входы перестраиваемого блока 3 приоритета поступает два и более единичных сигналов-запросов, а на входы 5 (51,...,5n) управления - код, изменяющий алгоритм обслуживания в диапазоне прямого (при подаче единичного сигнала на вход 41 1 → 2 →...→(n-1) → n или обратного (при подаче единичного сигнала на вход 42 n → (n-1) →...→ 2 → 1 порядков следования приоритетов). (Более подробно о входах задания режима, входах управления и сигналах, на них подаваемых, будет сказано ниже). Единичный сигнал седьмого запроса появится на выходе блока 3 приоритета, далее поступит на входы шифратора 10, на выходе которого он будет представлен в помехозащищенном коде, через элемент ИЛИ 13 установит триггер 14 в нулевое состояние и поступит по входу 127 в регистр 1 запросов, где сбросит 7 разряд в нулевое состояние. Сигнал с входа 127 регистра 1 запроса поступит через элемент И 347, на второй вход которого подан разрешающий единичный сигнал 41, и через элемент ИЛИ 357 на нулевой вход триггера 367, приводя тем самым его в нулевое состояние. Таким образом, на седьмом выходе регистра 1 запроса зафиксируется "0".

В памяти регистра 1 запросов остались зафиксированными второй, пятый, (n-1)-ый и n-ый запросы. Рассмотрим дальнейшее их обслуживание. Как видно из фиг. 4 и опираясь на вышеописанный алгоритм обработки, в отличие от кодов приоритета пятого, (n-7)-го и n-го запросов, код второго запроса в старшем разряде содержит "0", поэтому на данном этапе алгоритма обслуживания участия не принимает. Коды приоритета пятого, (n-1) - го и n - го запросов имеют одинаковые значения, следовательно, на выходах пятого, (n-1) - го и n - го логических блоков 235, 23n-1, 23n появятся сигналы "1", а на прямых выходах элементов ИЛИ 6 - код, соответствующий пятому, (n-1) - му, n - у запросам, который через элементы И 8 поступит на информационные входы (n+1) логического блока 23. Пусть на регистр кода приоритета 20n+1 не поступает код прерывания, тогда на информационные входы блока 3 приоритета будут поданы сигналы "1" пятого, (n- 1)- го и n - го запросов на обслуживания. Подавая сигналы "1" на входы 4 задания режима, можно изменять порядок обработки одновременно поступивших запросов, т.е. подавая сигнал "1" на вход 41, устанавливается порядок обслуживания: 5-ый, (n-1)-ый, n - ый. А подавая сигнал "1" на вход 42: n-ый, (n-1)-ый, 5-ый. Пусть в нашем случае подается сигнал "1" на вход 41 и устанавливается прямой порядок обслуживания запросов. На входы 5 (51,...,5n) управления подаются коды, изменяющие алгоритм обслуживания в диапазоне прямого или обратного следования приоритетов. При прямом следовании приоритетов (путем подачи "1" на вход 41): 5-ый, (n-1) - ый, n - ый возможны случаи варьирования (см. табл. 1), а при обратном диапазоне следования (устанавливается путем подачи "1" на вход 42) (см. табл. 2).

Пусть, в нашем случае код, поданный на входы 51,...,5n управления, задает алгоритм обслуживания приоритетов: (n-1), n, 5. Далее вышеописанный алгоритм обслуживания запросов повторяется, т.е. вначале сигнал (n-7)-го запроса будет представлен в помехозащищенном коде, соответственно сбросится (n-1)-ый разряд регистра 1 запросов. Аналогичная процедура будет осуществлена с сигналом пятого запроса.

Рассмотрим работу перестраиваемого блока 3 приоритета подробнее.

Установим по входам 41,42 блока 3 приоритета сигналы "1,0" соответственно, что определяет режим обслуживания 1 → 2 →...→(n-1) → n, а на входы 5 (51,...,5n) кодовую комбинацию, соответствующую подаче на обслуживание пятого запроса, тем самым задается следующая последовательность опроса: 5 → 6 →...→ (n-1) → n → 1 → 2 → 3 → 4. На 5, n-1 и n входы блока 3 приоритета поданы единичные сигналы с выходов второй группы элементов И 29 (И 295, И 29n-1, И 29n) (соответственно в регистре 20n+1 не зафиксирован маскирующий код приоритета). Единичным сигналом с выхода триггера 37 через первую группу элементов И 38 (И 385, И 38n-1, И 38n) и первую группу элементов ИЛИ 40 (ИЛИ 405, ИЛИ 40n-1, ИЛИ 40n) единичные сигналы с входов блока 3 приоритета поступят на инверсные входы элементов И 46 (И 465, И 46n-1, И 46n), которые соответственно закроются и единичный сигнал поступит выход элемента ИЛИ 41. В дешифраторе 43 на пятом выходе появляется единичный сигнал, который открывает элемент И 455 и закрывает элемент И 445. Таким образом, на пятом выходе блока 3 приоритета появится единичный сигнал.

Последним будет обслужен сигнал второго запроса, код которого наименее приоритетен по сравнению с кодами других запросов, одновременно со вторым поступившим на обслуживание.

Пусть в регистре 20n+1 зафиксировано пороговое значение кода приоритета, а на входы логического блока 23n+1, как отмечалось выше, подано значение экстремального кода прерывания. Согласно логике функционирования логических блоков 23 (см. выше) единичный сигнал появится на выходе блока 23n+1, если значение кода приоритета на его входах будет больше порогового, зафиксированного на входах блока 23n+2 и наоборот. Рассмотрим первый случай. Итак, на выходе логического блока 23n+1 зафиксирован единичный сигнал. Этот сигнал, пройдя через элементы И 30 и элемент ИЛИ 31, откроет элемент И 29i, (i-номер запроса с экстремальным кодом) и сигнал запроса с этого элемента поступит в блок 3 приоритета. Если же единичный сигнал зафиксирован на выходе логического блока 23n+2, а на выходе логического блока 23n+1 - нулевой сигнал, то оба элемента И 30 будут закрыты, а соответственно будет также закрыт и элемент 29i (i - номер запроса с экстремальным кодом) и сигнал запроса не поступит на вход блока 3 прерывания. Таким образом может быть осуществлена операция приоритетного обслуживания только тех запросов, значения кодов приоритета которых превышают уровень, зафиксированный в регистре 20n+1.

После сброса второго разряда регистра 1 запросов устройство переходит в исходное состояние и готово обслуживать запросы, пришедшие за время обработки седьмого, (n-1)-го, n - го, пятого и второго запросов.

Использование совокупности существенных признаков - общих: наличие регистра 1 запросов, блока 3 приоритета, первой группы элементов ИЛИ 6, второй группы элементов ИЛИ 7, первой группы элементов И 8, шифратора 10, элемента ИЛИ 13, триггера 14, элемента ИЛИ 15, n - разрядных регистров 20 приоритета, n групп разрядных элементов И 22, с соответствующими функциональными связями и новых совокупностей существенных признаков: наличие элемента И 18, элемента ИЛИ 19, (n+1) регистра приоритета 20n+1, (n+2) - x логических блоков 23, каждый из которых содержит группу элементов И 24, группу элементов И 25, группу элементов ИЛИ 26, элемент ИЛИ 27 элемент ИЛИ 28, два элемента И 30, элемент ИЛИ 31, элемент 32 задержки с соответствующими им функциональными связями, что позволило: получить устройство, обладающее расширенными функциональными возможностями с сокращением аппаратурных затрат. Оно не привязано к определенному классу кодов (в отличие от известных устройств), кроме того, появилась возможность получить структуру, которая реализует алгоритм определения запроса с наиболее приоритетным кодом, относительно известных устройств данная структура минимальна, в предлагаемом устройстве управляемость обеспечивается тем, что задавая предварительно порог, можно осуществлять выбор группы запросов.

Расширение функциональных возможностей, заключающееся в повышении информационной емкости устройства, достигается путем использования логических блоков 23, кроме того, использование дополнительного регистра кода приоритета позволяет маскировать запросы путем установки порогового значения кода приоритета.

Предложенное устройство также позволяет сократить аппаратные затраты, а следовательно, повысить надежность относительно устройства-прототипа с одинаковым количеством информационных входов. Сравнительный анализ аппаратурных затрат для устройства- прототипа и предлагаемого устройства приведен на фиг. 5. При подсчете количества элементов в качестве блока приоритета группы использовалось устройство параллельного приоритета, при раскрытии дешифраторов группы использовалась матричная схема построения дешифраторов. Регистр запросов 20-входовой и каждая кодовая последовательность значений приоритетов представляется в 16 разрядной сетке. Для наглядности сравнения разнородные блоки устройства-прототипа и предполагаемого устройства сведены к одному базису: двухвходовые элементы И и ИЛИ. Следует отметить, что предлагаемое устройство имеет однородную структуру, что облегчает его реализацию и наращивание информационных входов.

Таким образом, предлагаемое устройство позволяет расширить функциональные возможности за счет введения логических блоков и дополнительного регистра кода приоритета, а также сократить аппаратные затраты, а следовательно, повысить надежность устройства.

Устройство может быть реализовано на элементах вычислительной техники серии К1533.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| СПОСОБ ЦЕНТРАЛИЗОВАННОГО КОНТРОЛЯ N ОБЪЕКТОВ | 2000 |

|

RU2198418C2 |

| Устройство переменного приоритета | 1986 |

|

SU1383353A1 |

| Устройство для поиска экспериментальных значений | 1975 |

|

SU525083A1 |

| Устройство для поиска экстремальных значений | 1975 |

|

SU534762A1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 2000 |

|

RU2182359C2 |

| НЕЧЕТКИЙ ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1995 |

|

RU2110090C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АДАПТИВНЫМ МОБИЛЬНЫМ РОБОТОМ | 1998 |

|

RU2143334C1 |

Изобретение относится к области вычислительной техники и автоматического контроля и может быть использовано в устройствах прерывания программ, управления потоками данных и формирования исполнительного адреса банков данных в логических процессорах. Технический результат, достигаемый при использовании предлагаемого устройства, заключается в расширении области применения и сокращении аппаратурных затрат. Для достижения технического результата, в устройство, содержащее регистр запросов, блок приоритета, две группы элементов ИЛИ, группу элементов И, шифратор, два элемента ИЛИ, триггер, n l - разрядных регистров приоритета, n групп разрядных элементов И, дополнительно введены элемент И, элемент ИЛИ, (n+1) регистр приоритета, (n+2) логических блоков, каждый из которых содержит две группы элементов И, группу элементов И, группу элементов ИЛИ, три элемента, два элемента И, элемент 32 задержки. 6 ил., 2 табл.

Устройство переменного приоритета, содержащее регистр запросов, содержащий группу запросных входов, которые являются группой запросных входов устройства, и два входа задания режима, блок приоритета, содержащий два входа задания режима, соединенные с входами задания режима регистра запросов, и n входов управления, являющихся одноименными входами устройства, две группы элементов ИЛИ и группу элементов И, выходы блока приоритета соединены с входами шифратора, выходы которого являются информационными выходами устройства, с входами сброса регистра запросов и с входами первого элемента ИЛИ, выход которого соединен с нулевым входом триггера, второй элемент ИЛИ, первый и второй входы которого являются входами сигналов "Ответ" и "Пуск" устройства соответственно, n l - разрядных регистров приоритета (n - количество источников запросов), входы которых являются входами задания кодов приоритета источников запросов устройства, n групп разрядных элементов И по l элементов в каждой группе, первые входы которых погруппно объединены и соединены с соответствующими выходами регистра запросов, вторые входы всех разрядных элементов И групп соединены с единичным выходом триггера, выходы регистров приоритетов поразрядно соединены с третьими входами разрядных элементов И соответствующих групп, отличающееся тем, что в него дополнительно введены первый элемент И, первый вход которого соединен с выходом второго элемента ИЛИ, второй вход первого элемента И соединен с выходом третьего элемента ИЛИ, входы которого соединены соответственно с запросными входами регистра запросов, а выход первого элемента И соединен с единичным входом триггера, n логических блоков, информационные входы которых соответственно разрядам и группам соединены с выходами разрядных элементов И групп, причем каждый логический блок содержит в каждом разряде, кроме первого, вторые элементы И, первые входы которых являются соответствующими (2,3...l - информационными входами логического блока, третьи элементы И, первые входы которых поразрядно объединены со вторыми входами вторых элементов И, четвертые элементы ИЛИ, первые входы которых в каждом разряде соединены с выходами вторых элементов И, а вторые входы - с выходами третьих элементов И, выход каждого четвертого элемента ИЛИ i-го разряда (где i = 1,2..., l-1) соединен с объединенными входами второго и третьего элементов И последующего разряда, выход четвертого элемента ИЛИ l разряда является информационным выходом логического блока, в первом разряде каждого логического блока содержится пятый элемент ИЛИ, первый вход пятого элемента ИЛИ является первым информационным входом этого логического блока, выход пятого элемента ИЛИ соединен с объединенными вторым входом второго элемента И и первым входом третьего элемента И второго разряда этого логического блока, входы первого элемента ИЛИ первой группы соединены с первыми информационными входами n логических блоков, нулевой выход первого элемента ИЛИ первой группы соединен с объединенными вторыми входами пятых элементов ИЛИ n логических блоков, входы j-го (j = 2,3. ..l) элемента ИЛИ первой группы соединены с выходами вторых элементов И (j-l)-го разряда n - логических блоков, а нулевой выход упомянутого элемента ИЛИ соединен с объединенными вторыми входами третьих элементов И (j-1)-го разряда n логических блоков, первые входы первой группы элементов И соответственно соединены с единичными выходами элементов ИЛИ первой группы, а вторые входы объединены и соединены с выходом шестого элемента ИЛИ, входы которого соединены с информационными выходами логических блоков, первые входы второй группы элементов И соединены с информационными выходами соответствующих логических блоков, вторые входы упомянутых элементов И объединены, а выходы соответственно соединены с информационными входами блока приоритета, устройство также содержит вторую группу элементов ИЛИ, (n+1)-й и (n+2)-й идентичные логические блоки, информационные входы (n+1)-го логического блока соответственно соединены с выходами элементов И первой группы, (n+2)-й логический блок, информационные входы которого соответственно соединены с выходами (n+1)-го регистра приоритета, входы которого являются входами задания кода наивысшего приоритета устройства, входы первого элемента ИЛИ второй группы соединены с первыми информационными входами (n+1)-го и (n+2)-го логических блоков, нулевой выход первого элемента ИЛИ второй группы соединен с объединенными вторыми входами пятых элементов ИЛИ (n+1)-го и (n+2)-го логических блоков, входы j-го (j=2,3...., l) элемента ИЛИ второй группы соединены с выходами вторых элементов И (j -1)-го разряда (n+1)-го и (n+2)-го логических блоков, а нулевой выход упомянутого элемента ИЛИ соединен с объединенными вторыми входами третьих элементов И (j -1)-го разряда (n+1)-го и (n+2)-го логических блоков, первые входы четвертого и пятого элементов И объединены и соединены с информационным выходом (n+1)-го логического блока, вторые входы также объединены, причем второй вход четвертого элемента И-инверсный, и соединены с информационным выходом (n+2)-го логического блока, входы седьмого элемента ИЛИ соединены с выходами четвертого и пятого элементов И, а выход соединен с объединенными вторыми входами элементов И второй группы, вход элемента задержки соединен с единичным выходом триггера, а выход с третьими входами элементов И второй группы и с третьими входами четвертого и пятого элементов И.

| Устройство переменного приоритета с шифрацией адреса | 1984 |

|

SU1234837A1 |

| Устройство переменного приоритета | 1986 |

|

SU1383353A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| Многоканальное устройство переменного приоритета | 1988 |

|

SU1608662A2 |

| US 4334288 A, 08.06.1992 | |||

| JP 6317434 A, 18.07.1987 | |||

| JP 57121740 A, 29.07.1982. | |||

Авторы

Даты

2000-06-27—Публикация

1999-03-02—Подача