Изобретение относится к цифровой вычислительной технике, в частности к устройствам приоритета, и может быть использовано для обработки запросов на обслуживание от нескольких активных устройств.

Цель изобретения - повьшение быстродействия путем обеспечения минимального времени обслуживания при всех возможных переходах групповых зйпросов.

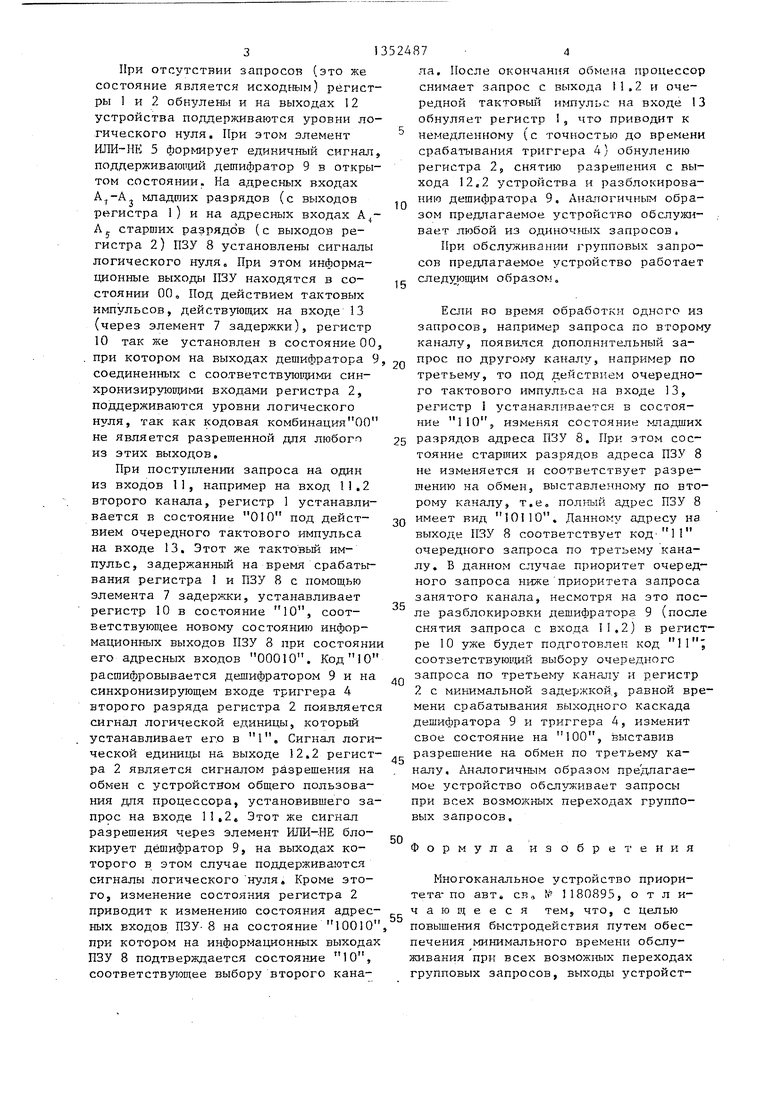

На чертеже приведена функциональная схема предлагаемого многоканального устройства приоритета на три канала,

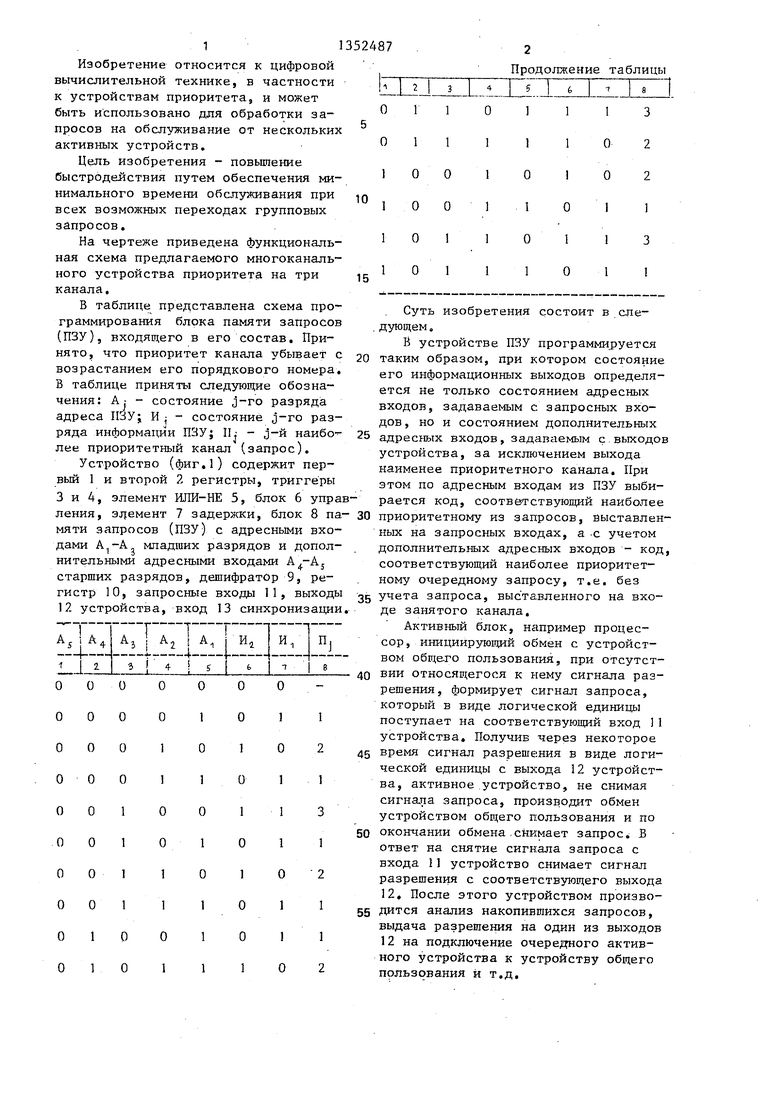

В таблице представлена схема программирования блока памяти запросов (ПЗУ), входящего в его состав. Принято, что приоритет канала убывает с возрастанием его порядкового номера. В таблице приняты следующие обозначения: А; - состояние j-ro разряда

адреса ПЗУ; И - состояние j-ro разряда информации ПЗУ; И,- - j-й наибо- лее приоритетный канал (запрос).

Устройство (фиг.1) содержит первый 1 и второй 2 регистры, триггеры 3 и 4, элемент ИЛИ-НЕ 5, блок 6 управления, 3jjeMeHT 7 задержки, блок 8 па- мяти запросов (ПЗУ) с адресными входами младших разрядов и дополнительными адресными входами старших разрядов, дешифратор 9, регистр 10, запросные входы 11, выходы 12 устройства, вход 13 синхронизации.

Продолжение таблицы

Суть изобретения состоит в следующем ,

В устройстве ПЗУ программируется таким образом, при котором состояние его информационных выходов определяется не только состоянием адресных входов, задаваемым с запросных входов , но и состоянием дополнительных

адресных входов, задаваемым с выходов устройства, за исключением выхода наименее приоритетного канала. При этом по адресным входам из ПЗУ выбирается код, соответствующий наиболее приоритетному из запросов, выставленных на запросных входах, а -с учетом дополнительных адресных входов - код, соответствзпош.ий наиболее приоритетному очередному запросу, т.е. без

учета запроса, выставленного на входе занятого канала.

Активный блок, нгшример процессор , инициирующий обмен с устройством общего пользования, при отсутстВИИ относящегося к нему сигнала разрешения, формирует сигнал запроса, который в виде логической единицы поступает на соответствующий вход 11 устройства. Получив через некоторое

время сигнал разрешения в виде логической единицы с выхода 12 устройства, активное устройство, не снимая сигнапа запроса, производит обмен устройством общего пользования и по

окончании обмена .снимает запрос В ответ на снятие сигнала запроса с входа 1 устройство снимает сигнал разрешения с соответствующего выхода 12, После этого устройством производится анализ накопившихся запросов, выдача разрешения на один из выходов 12 на подключение очередного активного устройства к устройству общего пользования и т.д.

При отсутствии запросов (это же состояние является исходьвым) регистры 1 и 2 обнулены и на выходах 12 устройства поддерживаются уровни логического нуля. При этом элемент ИЛИ-ПК 5 формирует единичный сигнал, поддерживающий дешифратор 9 в открытом состоянии. На адресных входах младших разрядов (с выходов регистра 1) и на адресных входах А J старших разрядов (с выходов регистра 2) ПЗУ 8 установлены сигналы логического нуля. При этом информационные выходы ПЗУ находятся в состоянии 00 о Под действием тактовых импульсов, действующих на входе 13 (через элемент 7 задержки), регистр 10 так же установлен в состояние 00

при котором на выходах дешифратора 9, jr. прос по другому каналу, например по

соединенных с соо.тветствуюггщми син- хронизирующиг-ш входами регистра 2, поддерживаются уровни логического нуля, так как кодовая комбинация 00 не является разрешенной для любого из этих выходов.

При поступлении запроса на один из входов 11, например на вход 11.2 второго канала, регистр 1 устанавливается в состояние 010 под действием очередного тактового импульса на входе 13. Этот же тактовый импульс, задержанный на время срабатывания регистра 1 и ПЗУ 8 с помощью элемента 7 задержки, устанавливает регистр 10 в состояние 10, соот- ветствуюпхее новому состоянию информационных выходов ПЗУ 8 при состоянии его адресных входов 00010. Код 10 расшифровывается дешифратором 9 и на синхронизирующем входе триггера 4 второго разряда регистра 2 появляется сигнал логической единицы, который устанавливает ег.о в 1. Сигнал логитретьему, то под действием очередного тактового импульса на входе 13, регистр I устанавливается в состояние 110, изменяя состояние младших

25 разрядов адреса ПЗУ 8. При этом состояние старших разрядов адреса ПЗУ 8 не изменяется и соответствует разрешению на обмен, выставленному по вто poNry каналу, т.е. полный адрес ПЗУ 8

3Q имеет вид iOllO. Данному адресу на выходе ПЗУ 8 соответствует очередного запроса по третьему каналу, В данном случае приоритет очеред ного запроса ниже приоритета запроса занятого канала, несмотря на это пос ле разблокировки дешифратора 9 (посл снятия запроса с входа П.2) в регис ре 10 уже будет подготовлен код 11 соответствующий выбору очередного запроса по третьему каналу и регистр 2 с минимальной задержкой., равной вр мени срабатывания выходного каскада дешифратора 9 и триггера 4, изменит свое состояние на 100, выставив

35

40

ческой единицы на выходе 12.2 регист- . разрешение на обмен по третьем кара 2 является сигналом разрешения на , налу. Аналогичным образом предлагаемое устройство обслз живает запросы при всех возможных переходах группообмен с устройством общего пользования для процессора, установившего запрос на входе 11,2. Этот же сигнал разрешения через элемент ИЛИ-НЕ блокирует дешифратор 9, на выходах которого в этом случае поддерживаются сигналы логического нуля. Кроме этого, изменение состояния регистра 2 приводит к изменению состояния адресных входов ПЗУ- 8 на состояние 10010, при котором на информационных выходах ПЗУ 8 подтверждается состояние 10, соответствующее выбору второго кана50

55

вых запросов,

ормула изобретения

Многоканальное устройство приоритета- по авт. СБ, № 1180895, отличающееся тем, что, с Целью повышения быстродействия путем обеспечения минимального времени обслуживания при всех возможных переходах групповых запросов, выходы з стройст

ла. После окончания обмена процессор снимает запрос с выхода 11,2 и очередной такторьш импульс на входе 13 обнуляет регистр , что приводит к немедленному (с точностью до времени срабатывания триггера 4) обнулению регистра 2, снят1-по разрешения с выхода 12,2 устройства и разблокированию дешифратора 9. Аналогичным образом предлагаемое устройство обслуживает любой из однночшлх запросов,

При обслуживан1-5и групповых запросов предлагаемое устройство работает следующим образом,

Если во время обработки одного из запросов, например запроса по второму каналу, появился дополнительный за

третьему, то под действием очередного тактового импульса на входе 13, регистр I устанавливается в состояние 110, изменяя состояние младших

5 разрядов адреса ПЗУ 8. При этом состояние старших разрядов адреса ПЗУ 8 не изменяется и соответствует разрешению на обмен, выставленному по вто- poNry каналу, т.е. полный адрес ПЗУ 8

Q имеет вид iOllO. Данному адресу на выходе ПЗУ 8 соответствует очередного запроса по третьему каналу, В данном случае приоритет очередного запроса ниже приоритета запроса занятого канала, несмотря на это после разблокировки дешифратора 9 (после снятия запроса с входа П.2) в регистре 10 уже будет подготовлен код 11 соответствующий выбору очередного запроса по третьему каналу и регистр 2 с минимальной задержкой., равной времени срабатывания выходного каскада дешифратора 9 и триггера 4, изменит свое состояние на 100, выставив

5

0

50

55

вых запросов,

ормула изобретения

Многоканальное устройство приоритета- по авт. СБ, № 1180895, отличающееся тем, что, с Целью повышения быстродействия путем обеспечения минимального времени обслуживания при всех возможных переходах групповых запросов, выходы з стройст513524876

ва, кроме выхода наименее приоритет- но с дополнительными адресными вхо- ного канала, соединены соответствен- рами блока памяти запросов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1984 |

|

SU1180895A1 |

| Программное устройство приоритетного обслуживания запросов | 1985 |

|

SU1355975A1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1793440A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1283765A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Устройство для ввода-вывода информации | 1985 |

|

SU1325489A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

| Устройство приоритета | 1986 |

|

SU1365084A1 |

Изобретение относится к цифровой вычислительной технике, в частности к устройствам приоритета, и может быть использовано для обработки запросов на обслуживание от нескольких активных устройств. Цель изобре//; тения состоит в повьшении быстродействия устройства за счет обеспечения минимального времени обслуживания при всех возможных переходах групповых запросов. Устройство содержит три регистра 1, 2, 10, два триггера 3, 4, элемент ИЛИ-НЕ 5,блок управления 6,элемент задержки 7,блок памяти запросов 8 (ПЗУ), дешифратор 9. В устройстве можно оперативно исключать из даль- нейп1его арбитража обслуженные заявки, обеспечивается оперативное обслуживание групповых запросов не только в случаях переходов к более приоритетным запросам, но и в случаях переходов к менее приоритетным запросам. 1 ил., 1 табл. с S (Л со СП 1чЭ 4 00 vj N

| Многоканальное устройство приоритета | 1984 |

|

SU1180895A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-04-28—Подача