Ю

Ш

Изобретение относится к технике связи и может быть использовано в составе многоканальных систем приема и обработки избирательных сигна- лов.

Цель изобретения - повышение помехоустойчивости .

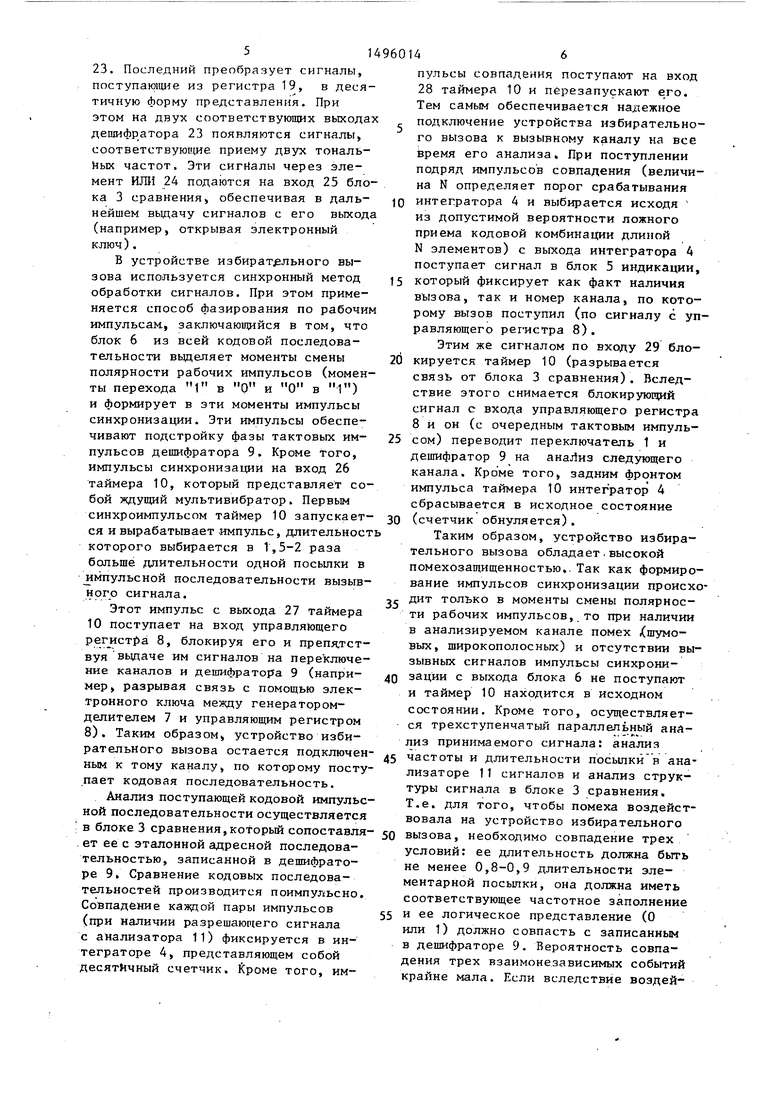

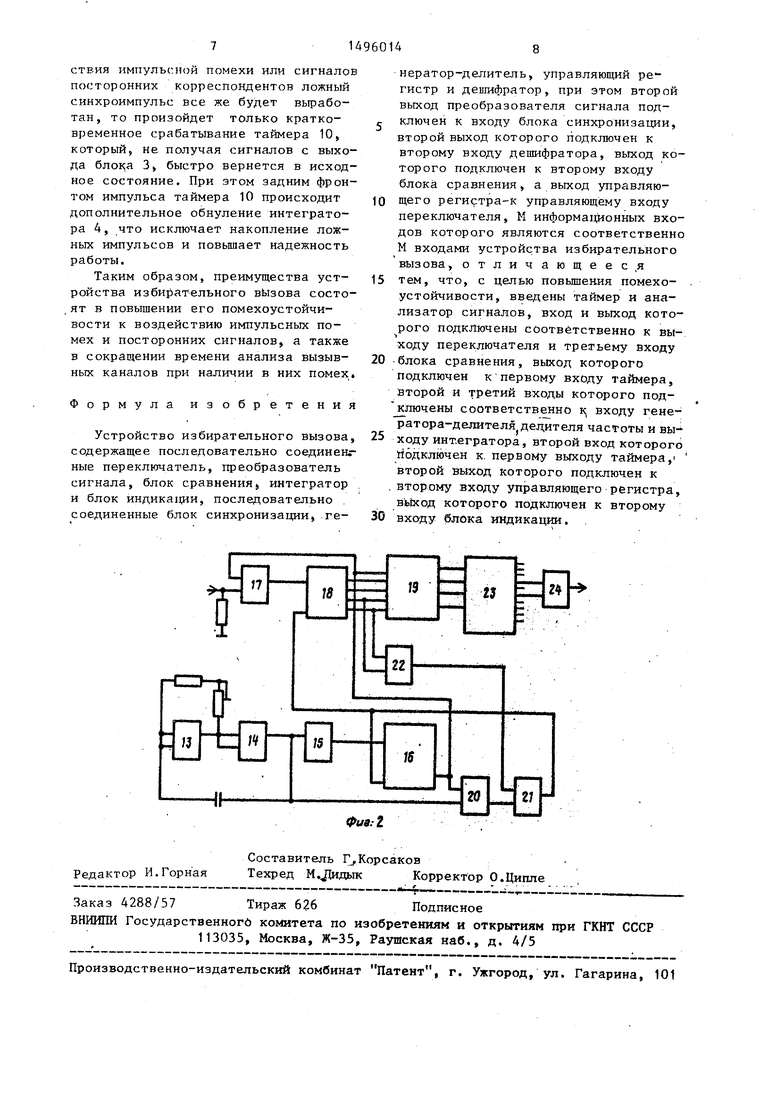

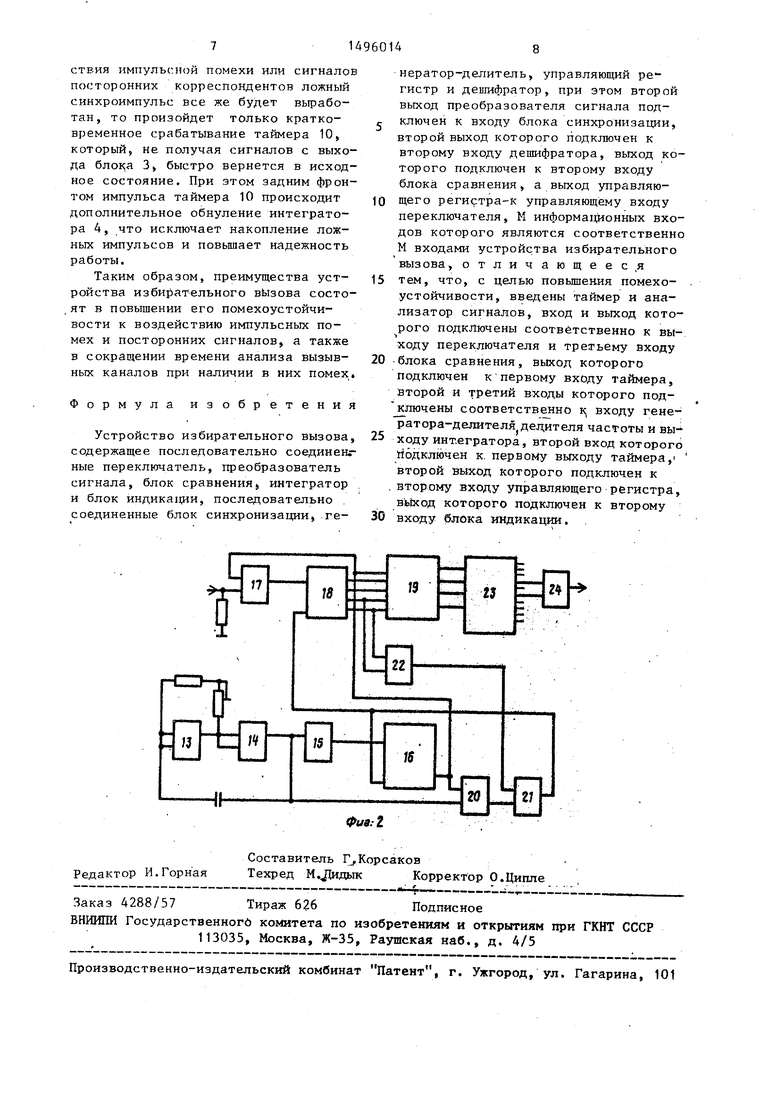

На фиг. 1 приведена блок-схема устройства избирательного вызова; на фиг. 2 - возможная схемотехническая реализация анализатора сигналов. Устройство избирательного вызова содержит переключатель 1, преобразователь 2 сигнала, блок 3 сравнения, интегратор 4, блок 5 индика1щи, блок 6 синхронизации, генератор-делитель 7, управляющий регистр 8, дешифратор 9, таймер 10, анализатор 11 сигналов, вход 12 блока 5, элемен- ты ШШ-НЕ 13 и 14, инвертор 15, счетчик 16, элемент ИЛИ-НЕ 17, счетчик 18, регистр 19, элементы Н-НЕ 20, 21 и 22; дешифратор 23, элемент ИЛИ 24, вход 25 блока 3, вход 26 таймера 10, выход 27 таймера 10, вход 28 таймера 10 и вход 29 таймера 10. .

Принцип работы устройства избирательного вызова основывается на осу- ществлении анализа элементарных посылок кодовой вызывной последовательности и использовании временного различия .истинных и ложных синхроимпульсов, причем временной интервал для анализа синхроимпульсов задается таймером 10.

Устройство работает следующим образом.

В исходном состоянии, когда сигналы вызова не поступают ни по одному из каналов на входы устройства избирательного вызова, переключатель 1 осуществляет поочередное подключение каждого кана.ла к входу преобразова- теля 2 на время, необходимое для анализа наличия сигнала вызоваi Посколь ку каждому каналу соответствует своя вызывная кодовая последовательность, то одновременно с переключением кана лов происходит и смена кодовых последовательностей, записанных в дешифраторе 9 и испсльзуемьгх для анализа принимаемых сигналов. Управление работой переключателя 1 и смена кодовы последовательностей в-дешифраторе 9 обеспечиваются с помощью управляющего регистра 8, тактовые импульсы для которого формируются с помощью гене5

0

5

0 5 д з

ратора-делителя 7. Кроме того, одновременно со сменой канала информация о его номере с выхода управляющего регистра 8 подается на вход 12 блока 5.

При наличии в каком-либо канале сигнала вызова, который представлен кодовой последовательностью двух тональных частот, этот сигнал через переключатель 1 поступает навход преобразователя 2, формирующего соот- ветствуюпще импульсные последовательности. Сформированные импульсные последовательности поступают на вход блока 3 сравнения и на вх од блока 6 синхронизации, который вырабатывает так товые импульсы для дешифратора 9.

Кроме того, последовательность двух тональных частот с выхода переключателя 1 поступает на вход анализатора 11, который представляет собой следящий частотомер, анализирующий наличие или .отсутствие в канале сигналов требуемой частоты. Принцип действия анализатора 11 основан ,

на подсчете числа импульсов за образцовый интервал временк который составляет 0,8-0,9 длительности элементарной посылки.

Анализатор 11 работает следующим образом.

Генерат.ор образцовой частоты, вы- полненный на элементах ИЛИ-НЕ 13 и 14, вырабатывает последовательность

.импульсов, поступающую через инвертор 15 на счетчик 16. Пока на его :i выходе напряжение логического нуля, элемент ИЛИ-НЕ 17 пропускает последовательность выходных импульсов на счетчик 18. По окончании интерна- ла счета фронтом импульса с выхода счетчика 16 происходят блокировка элемента ИЛИ-НЕ 17 и одновременная запись в регистр 19 информации с выходов счетчика 18. Положительным перепадом импульса с выхода элемента ИЛИ-НЕ 14 элементами 20 и 21 формируется импульс сброса счетчиков 16 и 18. Аналогичный импульс сброса-, но без записи в регистр 19, вьфабатыва- ется узлом защиты от переполнения, вьшолненным на элементах И-НЕ .22 и 21. Это происходит при переполнении счетчика 18, когда на входах элемента И-:НЕ 22 одновременно появляется сигнал логической единицы. Узел защиты исключает появление ложной команды на выходе дешифратора

51

23. Последний преобразует сигналы, поступающие из регистра 19, в десятичную форму представления. При этом на двух соответствующих вькодах дешифратора 23 появляются сигналы соответствующие приему двух тональных частот. Эти сигналы через элемент ИЛИ 24 подаются на вход 25 блока 3 сравнения, обеспечивая в даль- нейшем вьщачу сигналов с его выхода (например, открывая электронный ключ).

В устройстве избирательного вызова используется синхронный метод обработки сигналов. При этом применяется способ фазирования по рабочим импульсам., заключающийся в том, что блок 6 из всей кодовой последовательности вьщеляет моменты смены полярности рабочих импульсов (момен- ты перехода 1 в О и О в 1) и формирует в эти моменты импульсы синхронизации. Эти импульсы обеспечивают подстройку фазы тактовых им- пульсов дещифратора 9, Кроме того, импульсы синхронизации на вход 26 таймера 10, который представляет собой ждущий мультивибратор. Первым синхроимпульсом таймер 10 запускает- ся и вырабатывает импульс, длительност которого выбирается в 1,5-2 раза больше длительности одной посылки в 1мпульсной последовательности вызывного сигнала.

Этот импульс с выхода 27 таймера 10 поступает на вход управляющего регистра 8, блокируя его и препятствуя вьщаче им сигналов на переключение каналов и дешифратора 9 (напри- мер разрывая связь с помощью электронного ключа между генератором- делителем 7 и управляющим регистром 8). Таким образом устройство избирательного вызова остается подключен45

ным к тому каналу, по которому поступает кодовая последовательность.

Анализ поступающей кодовой импульсной последовательности осуществляется в блоке 3 сравнения, который сопоставля- 50 ВТ ее с эталонной адресной последовательностью, записанной в дешифраторе 9 Сравнение кодовых последовательностей производится поимпульсно. Совпадение каждой пары импульсов (при наличии разрешающего сигнала с анализатора 11) фиксируется в интеграторе 4, представляющем собой есятичный счетчик. Кроме того, им55

Q

5 20 25 зо

дд

45

50

5

146

пульсы совпадения поступают на вход 28 таймера 10 и перезапускают его. Тем самым обеспечивается надежное подключение устройства избирательного вызова к вызывному каналу на все время его анализа. При поступлении подряд импульсов совпадения (величина N определяет порог срабатывания интегратора 4 и выбирается исходя из допустимой вероятности ложного приема кодовой комбинации длиной N элементов) с выхода интегратора 4 поступает сигнал в блок 5 индикации, который фиксирует как факт наличия вызова, так и номер канала, по которому вызов поступил (по сигналу с управляющего регистра 8).

Этим же сигналом по входу 29 блокируется таймер 10 (разрывается связь от блока 3 сравнения). Вследствие этого снимается блокирующий сигнал с входа управляющего регистра 8 и он (с очередным тактовым импульсом) переводит переключатель 1 и дешифратор 9 на анаЛиз следующего канала. Кроме того, задним фронтом импульса таймера 10 интегратор 4 сбрасывается в исходное состояние (счетчик обнуляется).

Таким образом, устройство избирательного вызова обладает.высокой помехозащищенностью,. Так как формирование импульсов синхронизации происходит только в моменты смены полярности рабочих импульсов, то при наличии в анализируемом канале помех Хшумо- вых, широкополосных) и отсутствии вызывных сигналов импульсы синхронизации с выхода блока 6 не поступают и таймер 10 находится в исходном состоянии. Кроме того, осуществляется трехступенчатый параллельный анализ принимаемого сигнала: анализ частоты и длительности посылки в анализаторе 11 сигналов и анализ структуры сигнала в блоке 3 сравнения. Т.е. для того, чтобы помеха воздействовала на устройство избирательного вызова, необходимо совпадение трех условий: ее длительность должна быть не менее 0,8-0,9 длительности элементарной посылки, она должна иметь соответствующее частотное заполнение и ее логическое представление (О или 1) должно совпасть с записанным в дешифраторе 9. Вероятность совпадения трех взаимонезависимых событий крайне мала. Если вследствие воздействия нмпульс .иой помехи или сигналов посторонних корреспондентов ложный синхроимпульс все же будет выработан, то произойдет только кратко- временное срабатывание таймера 10, который, не получая сигналов с выхода блока 3, быстро вернется в исходное состояние. При этом задним фронтом импульса таймера Ю происходит дополнительное обнуление интегратора 4, что исключает накопление ложных импульсов и повышает надежность работы.

Таким образом, преимущества уст- ройства избирательного вУзова состоят в повышении его помехоустойчивости к воздействию импульсных помех и посторонних сигналов, а также в сокращении времени анализа вызыв- ных каналов при наличии в них помех,.

Формула изобретения

Устройство избирательного вызова, содержащее последовательно соединенг ные переключатель, преобразователь сигнала, блок сравнения, интегратор и блок индикации, последовательно . соединенные блок синхронизации, ге-

нератор-делитель, управляющий регистр и деишфратор, при этом второй выход преобразователя сигнала подключен к входу блока синхронизации, второй выход которого подключен к второму входу дешифратора, выход которого подключен к второму входу блока сравнения, а выход управляющего регистра-к управляющему входу переключателя, М информа1щонных входов которого являются соответственно М входами устройства избирательного вызова, отличающееся тем, что, с целью повышения помехоустойчивости, введены таймер и анализатор сигналов, вход и выход которого подключены соответственно к выЧ

ходу переключателя и третьему входу блока сравнения, выход которого подключен к первому входу таймера, второй и третий входы которого под- ключены соответственно к; входу генератора-делителя дедителя частоты и выходу интегратора, второй вход которого Нодключен к, первому выходу таймера, второй выход которого подключен к . второму входу управляющего регистра которого подключен к второму входу блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА | 2005 |

|

RU2299525C1 |

| Устройство поиска селективного вызова | 1984 |

|

SU1188912A1 |

| Адаптивное вызывное устройство | 1979 |

|

SU809666A1 |

| Устройство для приема адресного вызова | 1978 |

|

SU703920A1 |

| Система селективного вызова | 1985 |

|

SU1309330A1 |

| УСТРОЙСТВО ПРИЕМА АДРЕСНОГО ВЫЗОВА | 1994 |

|

RU2097941C1 |

| Устройство для приема рекуррентных кодовых последовательностей | 1984 |

|

SU1197127A1 |

| Устройство автовыбора радиоканалов | 1978 |

|

SU780230A1 |

| Система адресного вызова с позиционным кодированием | 1980 |

|

SU907871A1 |

| Устройство приема селективного вызова | 1989 |

|

SU1688463A1 |

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости. Устр-во содержит переключатель 1, преобразователь 2 сигнала, блок сравнения 3, интегратор 4, блок индикации 5, блок синхронизации 6, генератор-делитель 7, управляющий регистр 8, дешифратор 9, таймер 10 и анализатор 11 сигналов. Принцип работы устр-ва избирательного вызова основывается на осуществлении анализа элементарных посылок кодовой вызывной последовательности и использовании временного различия истинных и ложных синхроимпульсов. При этом временной интервал для анализа синхроимпульсов задается таймером 10. В устр-ве используется синхронный метод обработки сигналов и применяется способ фазирования по рабочим импульсам. Это обеспечивает надежное подключение устр-ва к вызывному каналу на все время его анализа. Повышение помехоустойчивости к воздействию импульсных помех и посторонних сигналов достигается за счет исключения накопления ложных импульсов и сокращения времени анализа вызывных каналов при наличии в них помех. 2 ил.

Фиа:2

| Адаптивное вызывное устройство | 1979 |

|

SU809666A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-23—Публикация

1987-03-04—Подача