г f

CIO

4

9

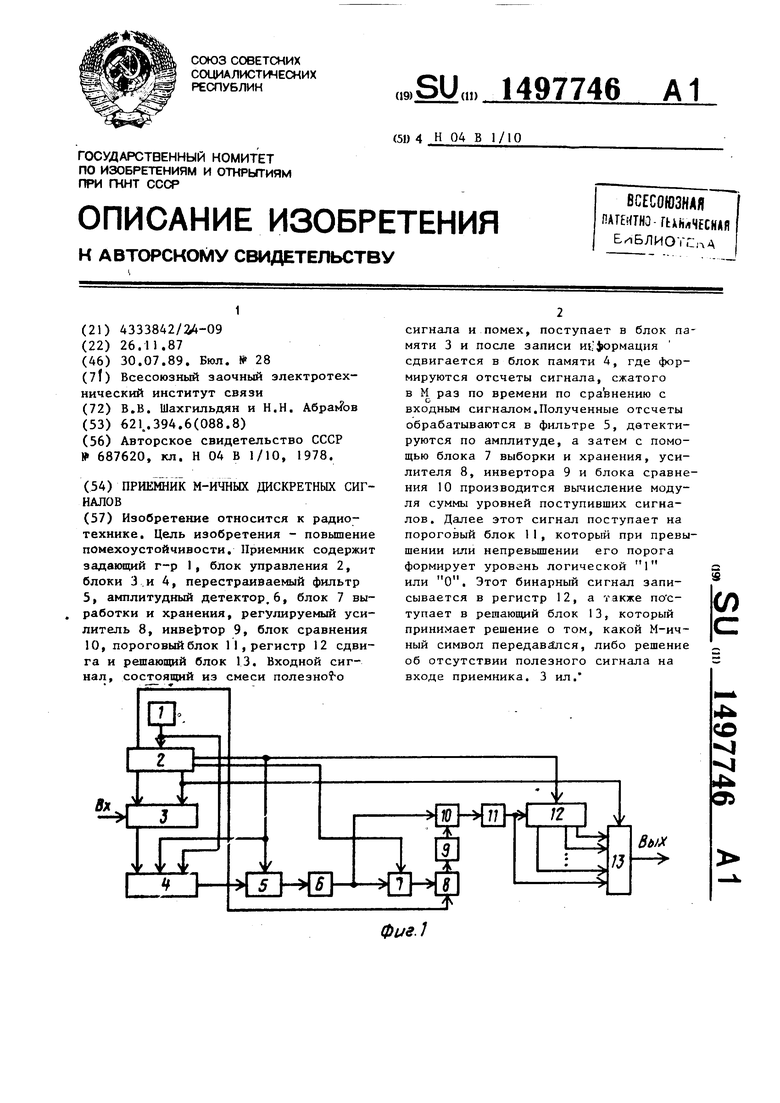

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости. Приемник содержит задающий г-р 1, блок управления 2, блоки памяти 3 и 4, перестраиваемый фильтр 5, амплитудный детектор 6, блок 7 выборки и хранения, регулируемый усилитель 8, инвертор 9, блок сравнения 10, пороговый блок 11, регистр 12 сдвига и решающий блок 13. Входной сигнал, состоящий из смеси полезного сигнала и помех, поступает в блок памяти 3, и после записи информация сдвигается в блок памяти 4, где формируются отсчеты сигнала, сжатого в М раз по времени по сравнению с входным сигналом. Полученные отсчеты обрабатываются в фильтре 5, детектируются по амплитуде, а затем с помощью блока 7 выборки и хранения, усилителя 8, инвертора 9 и блока сравнения 10 производится вычисление модуля суммы уровней поступивших сигналов. Далее этот сигнал поступает на пороговый блок 11, который при превышении или непревышении его порога формирует уровень логической "1" или "0". Этот бинарный сигнал записывается в регистр 12, а также поступает в решающий блок 13, который принимает решение о том, какой М-ичный символ передавался, либо решение об отсутствии полезного сигнала на входе приемника. Дана ил. выполнения блока управления 2. 3 ил.

фиг. }

31497746

Изобретение относится к радиотехнике и может использоваться в циф- рс5вых системах передачи информации.

Цель изобретения - повышение поме- . хоустойчивости.

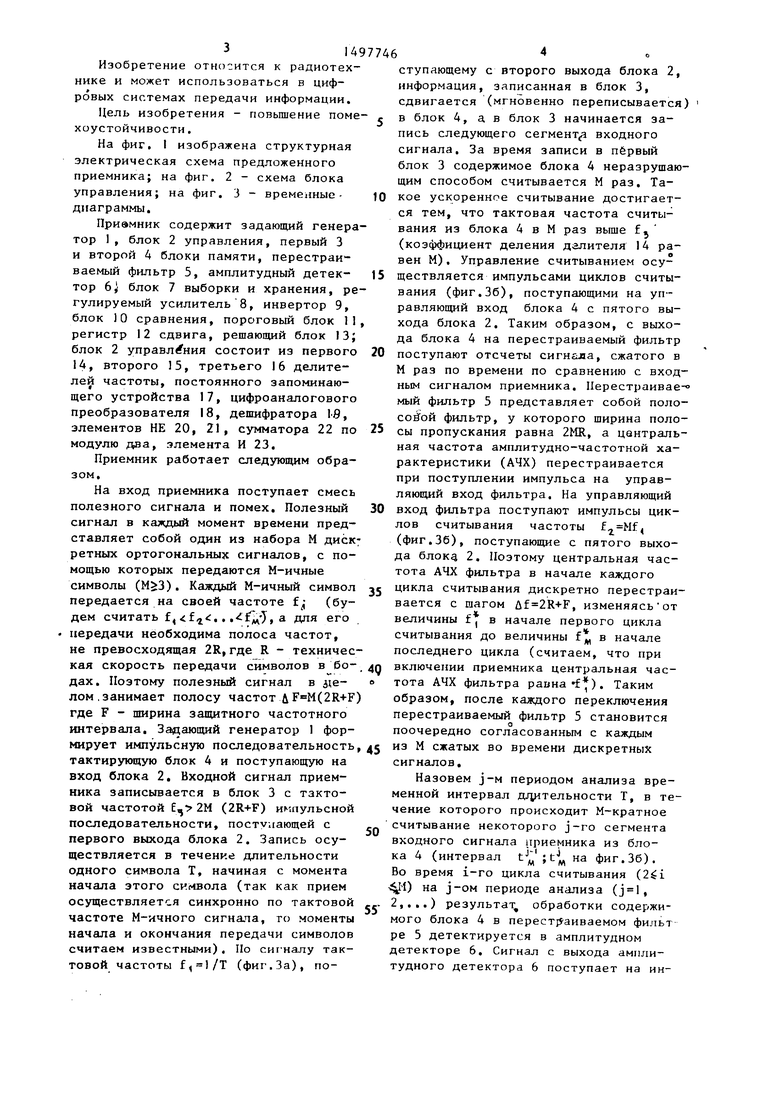

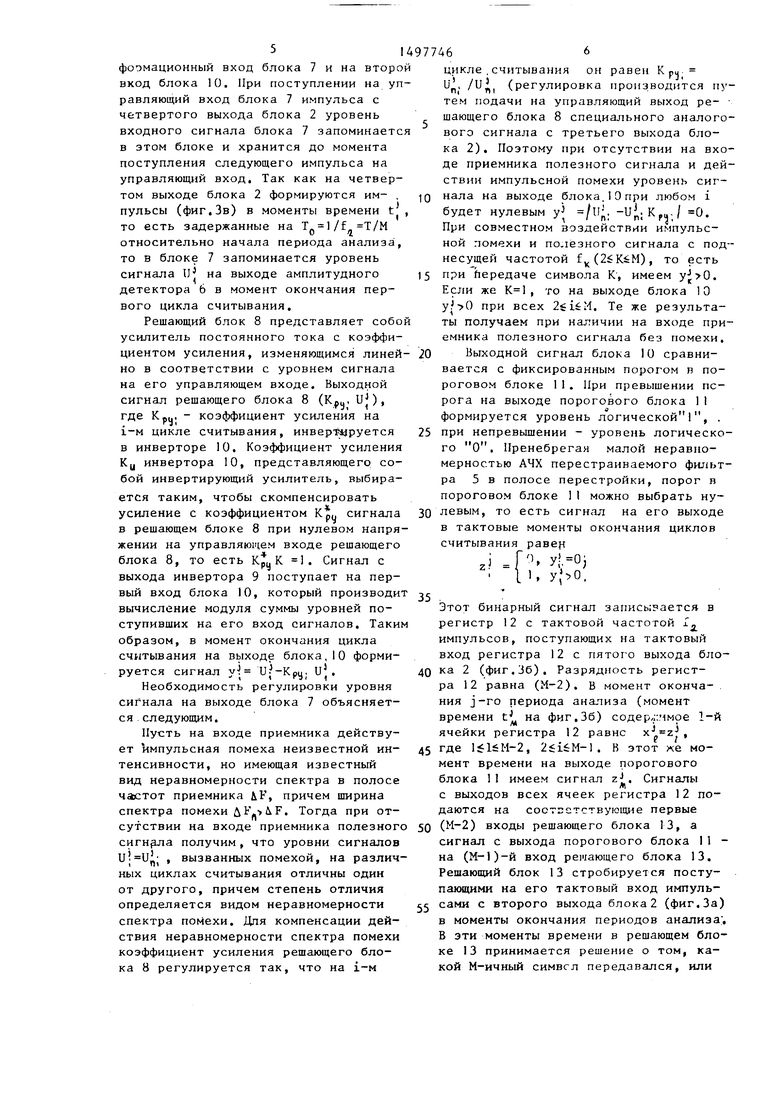

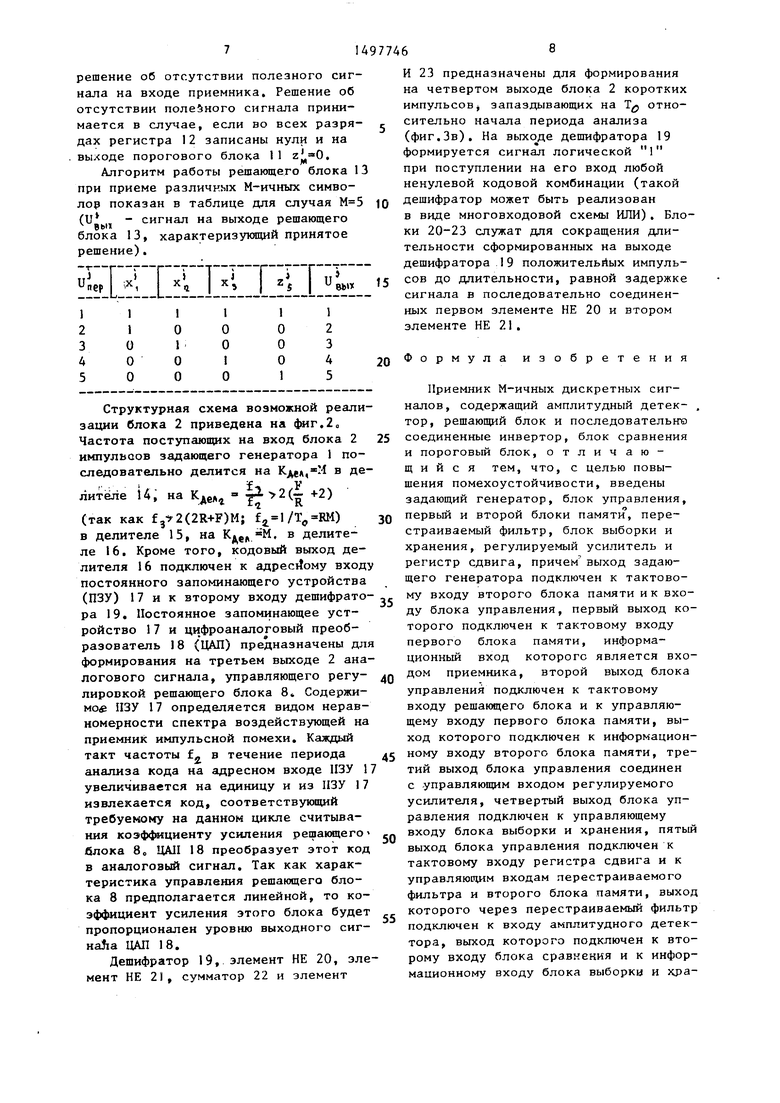

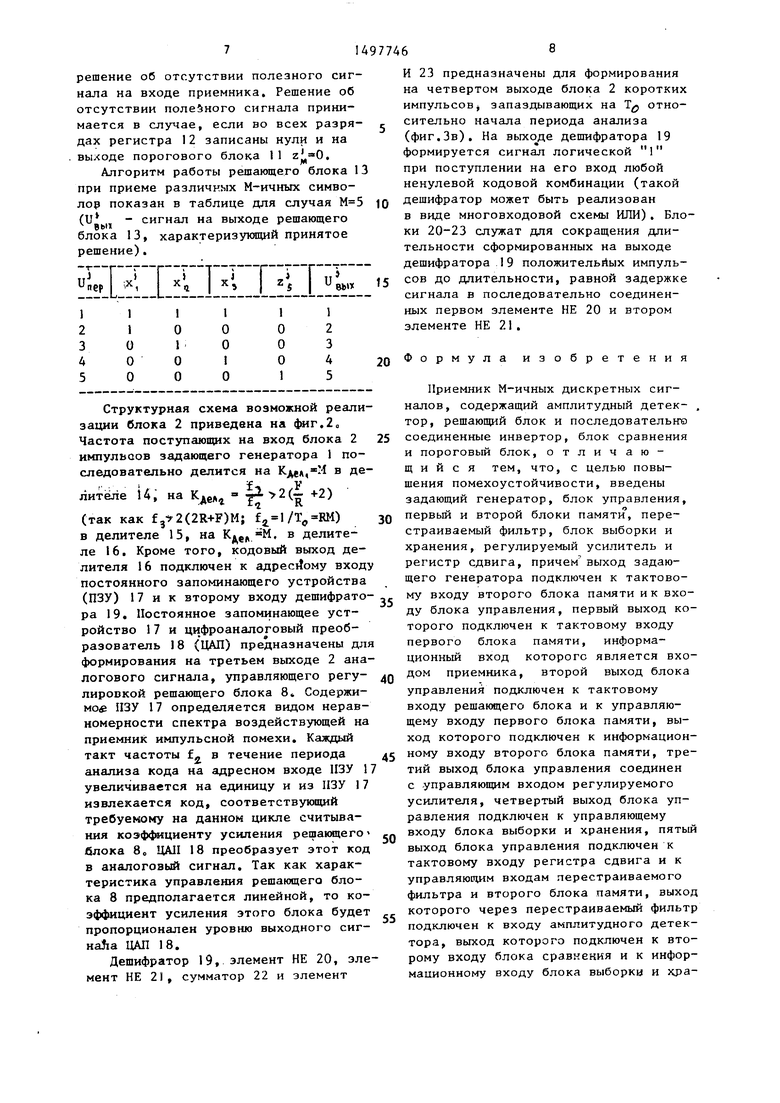

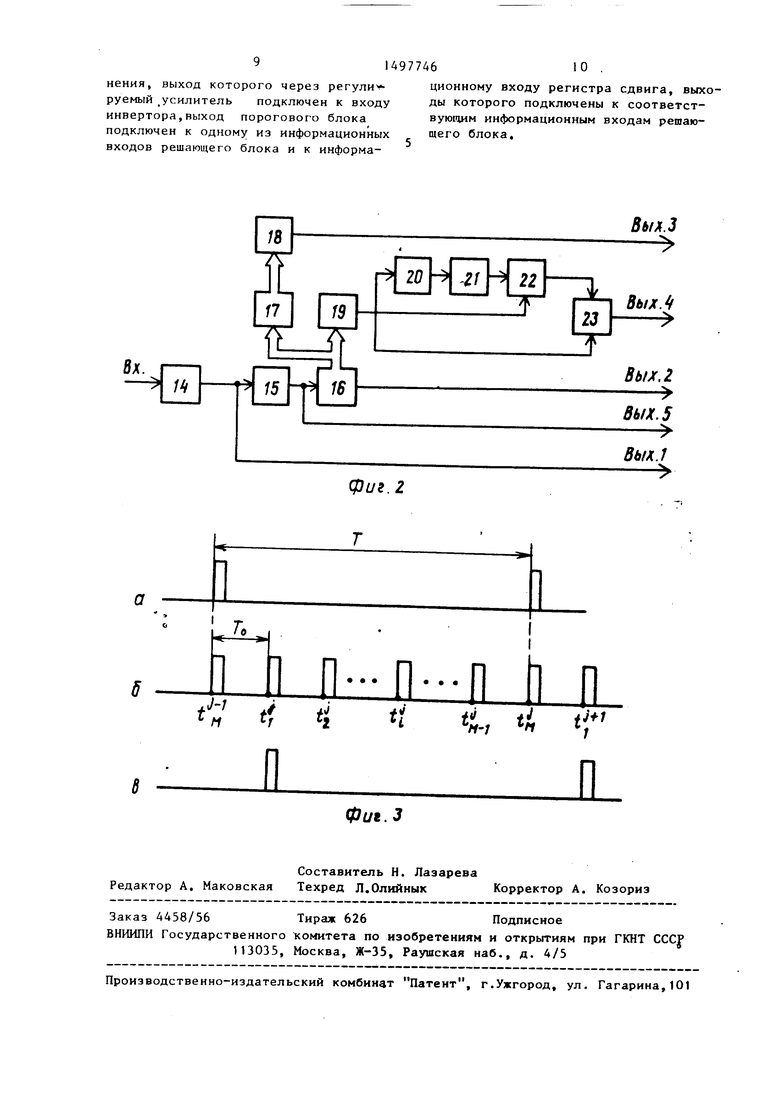

На фиг, 1 изображена структурная электрическая схема предложенного приемника; на фиг. 2 - схема блока управления; на фиг, 3 - временные- Ю диаграммы.

Приемник содержит задающий генератор 1, блок 2 управления, первый 3 и второй 4 блоки памяти, перестраи ваемый фильтр 5, амплитудный детек- 15 тор 6) блок 7 выборки и хранения, регулируемый усилитель 8, инвертор 9, блок 10 сравнения, пороговый блок 11, регистр 12 сдвига, решаюпшй блок )3; блок 2 управления состоит из первого 20 14, второго 15, третьего 16 делителей частоты, постоянного запоминающего устройства 17, цифроаналогового преобразователя 18, дешифратора 19, элементов НЕ 20, 21, сумматора 22 по 25 модулю два, элемента И 23,

Приемник работает следующим образом.

На вход приемника поступает смесь полезного сигнала и помех. Полезный 30 сигнал в каждый момент времени представляет собой один из набора М дискретных ортогональных сигналов, с помощью которых передаются М-ичные символы (), Каждый М-ичный символ 35 передается на своей частоте (будем считать f, f ,, ., а для его передачи необходима полоса частот, не превосходящая 2R,где R - техническая скорость передачи символов в бо- дд дах. Поэтому полезный сигнал в де- в лом,занимает полосу частот (2R+F) где F - ширина запштного частотного интервала. Задающий генератор 1 формирует импульсную последовательность, j сжатых во времени дискретных

тактирующую блок 4 и поступающую на вход блока 2. Входной сигнал приемника записывается в блок 3 с тактовой частотой , 2М (2R+F) импульсной последовательности, поступающей с первого выхода блока 2, Запись осуществляется в течение длительности одного символа Т, начиная с момента начала этого си(чвола (так как прием

50

сигналов.

Назовем J-M периодом анализа вр менной интервал ДJy тeльнocти Т, в чение которого происходит М-кратно считывание некоторого j-ro сегмент входного сигнала приемника из блока 4 (интервал t) на фиг,3б). Во время i-ro цикла считывания (2 ) на J-OM периоде анализа (.

осуществляется синхронно по тактовой .-. 2,,,,) результат обработки содержи- частоте М-ичного сигнала, то моменты мого блока 4 в перест; аиваемом фильт начала и окончания передачи символов считаем известными) . По сиг-налу такре 5 детектируется в амплитудном детекторе 6, Сигнал с выхода амплитудного детектора 6 поступает на интовой частоты f,l/T (фиг.За), поступающему с второго выхода блока 2, информация, записанная в блок 3, сдвигается (мгновенно переписывается) в блок 4, а в блок 3 начинается запись следующего сегменту входного сигнала. За время записи в первый блок 3 содержимое блока 4 неразрушающим способом считывается М раз. Такое ускоренное считывание достигается тем, что тактовая частота считывания из блока 4 в М раз выше f (коэффициент деления делителя 14 равен М), Управление считыванием осуществляется импульсами циклов считывания (фиг,36), поступающими на управляющий вход блока 4 с пятого выхода блока 2, Таким образом, с выхода блока 4 на перестраиваемый фильтр поступают отсчеты сигнала, сжатого в М раз по времени по сравнению с входным сигналом приемника, Иерестраиваемый фильтр 5 представляет собой поло- фильтр, у которого ширина полосы пропускания равна 2MR, а центральная частота амплитудно-частотной характеристики (АЧХ) перестраивается при поступлении импульса на управляющий вход фильтра. На управляющий вход фильтра поступают импульсы циклов считывания частоты (фиг,36), поступающие с пятого выхода блок4 2, Поэтому центральная частота АЧХ фильтра в начале каждого цикла считывания дискретно перестраивается с шагом , изменяясь от

величины f, в начале первого цикла

считывания до величины f в начале последнего цикла (считаем, что при включении приемника центральная частота АЧХ фильтра равна ), Таким образом, после каждого переключения перестраиваемый фильтр 5 становится поочередно согласованным с каждым

0

сигналов.

Назовем J-M периодом анализа временной интервал ДJy тeльнocти Т, в течение которого происходит М-кратное считывание некоторого j-ro сегмента входного сигнала приемника из блока 4 (интервал t) на фиг,3б). Во время i-ro цикла считывания ( ) на J-OM периоде анализа (.

2,,,,) результат обработки содержи- мого блока 4 в перест; аиваемом фильт

ре 5 детектируется в амплитудном детекторе 6, Сигнал с выхода амплитудного детектора 6 поступает на ин5

фоомационный вход блока 7 и на второ вход блока 10. При поступлении на управляющий вход блока 7 импульса с четвертого выхода блока 2 уровень входного сигнала блока 7 запоминаетс в этом блоке и хранится до момента поступления следующего импульса на управляющий вход. Так как на четвертом выходе блока 2 формируются им- ,

.)

пульсы (фиг.Зв) в моменты времени t то есть задержанные на Т/М относительно начала периода анализа то в блоке 7 запоминается уровень сигнала U| на выходе амплитудного детектора 6 в момент окончания первого цикла считывания.

Решающий блок 8 представляет собо усилитель постоянного тока с коэффициентом усиления, изменяющимся линейно в соответствии с уровнем сигнала на его управляющем входе. Выходной сигнал решающего блока 8 (Крц, Uj), где Крц. - коэффициент усилени я на i-M цикле считывания, инверт4}руется в инверторе 10, Коэффициент усиления Кц инвертора 10, представляющего собой инвертирующий усилитель, выбирается таким, чтобы скомпенсировать усиление с коэффициентом Кру сигнала в решающем блоке 8 при нулевом напряжении на управляющем входе решающего

блока 8, то есть КрцК 1, Сигнал с выхода инвертора 9 поступает на первый вход блока 10, который производи вычисление модуля суммы уровней поступивших на его вход сигналов. Таки образом, в момент окончания цикла считывания на выходе блока,10 формируется сигнал yj . и

Необходимость регулировки уровня сигнала на выходе блока 7 объясняется следующим.

Пусть на входе приемника действует {мпульсная помеха неизвестной интенсивности, но имеющая известный вид неравномерности спектра в полосе частот приемника F, причем ширина

спектра помехи uF.F, Тогда при отсутствии на входе приемника полезного получим, что уровни сигналов U Uj||; , вызванных помехой, на различных циклах считывания отличны один от другого, причем степень отличия определяется видом неравномерности спектра поМехи, Для компенсации действия неравномерности спектра помехи коэффициент усиления решающего блока 8 регулируется так, что на i-м

цикле , считывания он равен Кри и, /и, (регулировка производится путем подачи на управляющий выход ре- шающего блока 8 специального аналогового сигнала с третьего выхода блока 2), Поэтому при отсутствии на входе приемника полезного сигнала и действии импульсной помехи уровень сигнала на выходе блока. 10 при любом i

, - п. - niKpy,/ При совместном воздействии импульсбудет нулевым у

0,

ной помехи и полезного сигнала с под-несущей частотой f(25KiM), то есть

при Ьередаче символа К, имеем . Если же , то на выходе блока 10 при всех , Те же результаты получаем при нагтичии на входе приемника полезного сигнала без помехи,

Выходной сигнал блока 10 сравнивается с фиксированным порогом и пороговом блоке 11, При превышении пс- рога на выходе порогового блока 11 формируется уровень логической, .

при непревышении - уровень логического О, Пренебрегая малой неравномерностью АЧХ перестраиваемого фильтра 5 в полосе перестройки, порог в пороговом блоке 1I можно выбрать нулевым, то есть сигнал на его выходе в тактовые моменты окончания циклов считывания раве

Ч У,О;

1, У,ЬО,

Z

j

40

Этот бинарный сигнал записывается в регистр 12 с тактовой частотой 1 импульсов, поступающих на тактовый вход регистра 12 с пятого выхода блока 2 (фиг,36), Разрядность регистра 12 равна (М-2), В момент окончания j-ro периода анализа (момент времени t., на фиг,36) содер г.ммое 1-й

М . 1

ячейки регистра 12 равно х

-;

45 где , , В этот же момент времени на выходе порогового

блока 11 имеем сигнал z{. Сигналы

л

с выходов всех ячеек регистра 12 подаются на состгетствующие первые 50 () входы решающего блока 13, а

сигнал с выхода порогового блока 11 - на (М-1)-й вход ре11шющего блока 13, Решающий блок 13 стробируется поступающими на его тактовый вход импульсу сами с второго выхода блока 2 (фиг,За) в моменты окончания периодов анализа; В эти моменты времени в решающем блоке 13 принимается решение о том, какой М-ичный символ передавался, или

решение об отсутствии полезного сигнала на входе приемника. Решение об отсутствии полезного сигнала принимается в случае, если во всех разрядах регистра 12 записаны нули и на выходе порогового блока 11 ,

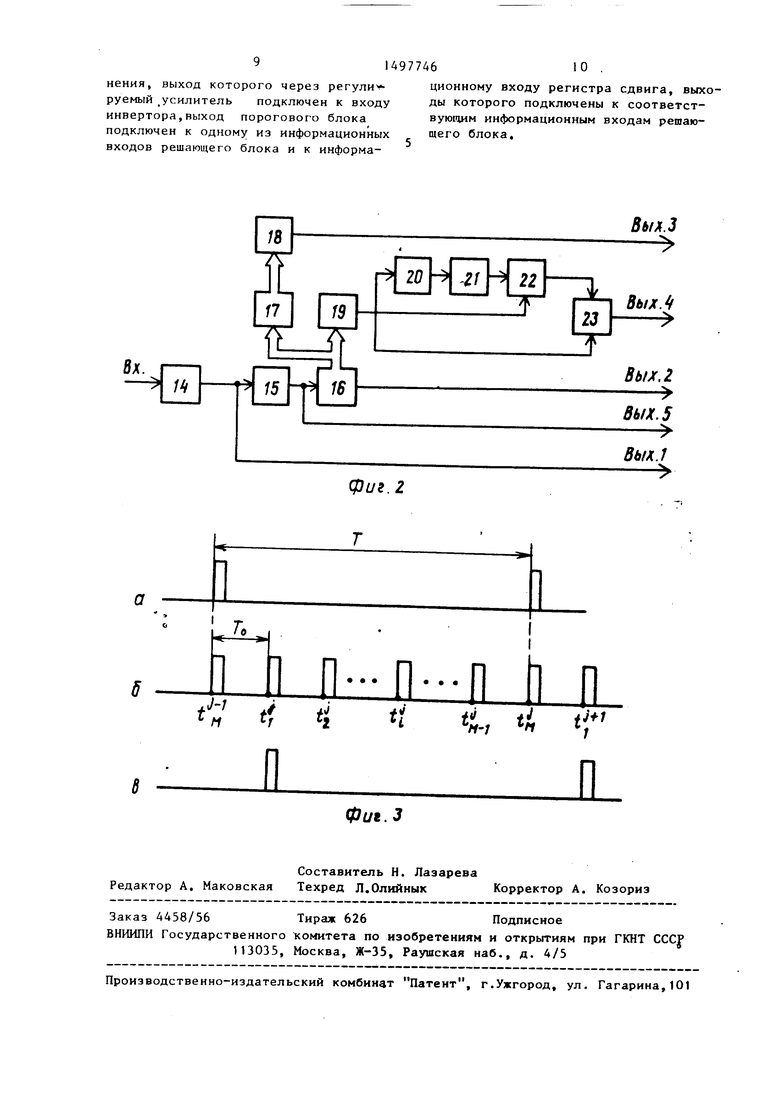

Алгоритм работы решающего блока 13 при приеме различных М-ичных симво- лор показан в таблице для случая

(и „ - сигнал на выходе решающего

О ь

блока 13, характеризующий принятое решение),

Структурная схема возможной реализации блока 2 приведена на фиг.2 Частота поступающих на вход блока 2 импульсов задающего генератора 1 последовательно делится на Кдед,«М в де,, , ,f у

литёле U, на Кдед ( +2)

(так как f 3-: 2(2R+F)M; f ) в делителе 15, на Кд М. в делителе 16, Кроме того, кодовый выход делителя 16 подключен к адресному входу постоянного запоминающего устройства (ПЗУ) 17 и к второму входу дешифрато- ра 19. Постоянное запоминающее устройство 17 и цифроаналоговый преобразователь 18 (ЦАП) предназначены для формирования на третьем выходе 2 аналогового сигнала, управляющего регу- лировкой решающего блока 8 Содержимое ПЗУ 17 определяется видом неравномерности спектра воздействующей на приемник импульсной помехи. Каждый такт частоты f, в течение периода анализа кода на адресном входе ПЗУ 1 увеличивается на единицу и из ПЗУ 17 извлекается код, соответствующий требуемому на данном цикле считывания коэффициенту усиления решающего блока 8 ЦАП 18 преобразует этот код в аналоговый сигнал. Так как характеристика управления решающего блока 8 предполагается линейной, то коэффициент усиления этого блока будет пропорционален уровню выходного сиг- наЛа ЦАП 18.

Дешифратор 19, элемент НЕ 20, элемент НЕ 21, сумматор 22 и элемент

И 23 предназначены для формирования на четвертом выходе блока 2 коротких импульсов запаздывающих на Т относительно начала периода анализа (фиг.Зв), На дешифратора 19 формируется сигнал логической 1 при поступлении на его вход любой ненулевой кодовой комбинации (такой

дешифратор может быть реализован

в виде многовходовой схемы ИЛИ). Блоки 20-23 служат для сокращения длительности сформированных на выходе дешифратора 19 положительйых импульсов до длительности, равной задержке сигнала в последовательно соединенных первом злементе НЕ 20 и втором элементе НЕ 21,

Формула изобретения

5

О , о

5

0

5

Приемник М-ичных дискретных сигналов , содержащий амплитудный детек- . тор, решающий блок и последовательна соединенные инвертор, блок сравнения и пороговый блок, отличающийся тем, что, с целью повышения помехоустойчивости, введены задающий генератор, блок управления, первый и второй блоки памяти, перестраиваемый фильтр, блок выборки и хранения, регулируемый усилитель и регистр сдвига, причем выход задающего генератора подключен к тактовому входу второго блока памяти и к входу блока управления, первый выход которого подключен к тактовому входу первого блока памяти, информационный вход которого является входом приемника, второй выход блока управления подключен к тактовому входу решающего блока и к управляющему входу первого блока памяти, выход которого подключен к информационному входу второго блока памяти, третий выход блока управления соединен с управляющим входом регулируемого усилителя, четвертый выход блока управления подключен к управляющему входу блока выборки и хранения, пятый выход блока управления подключен к тактовому входу регистра сдвига и к управляющим входам перестраиваемого фильтра и второго блока памяти, выход которого через перестраиваемый фильтр подключен к входу амплитудного детектора, выход которого подключен к второму входу блока сравнения и к информационному входу блока выборки и хранения, выход которого через регули руемый усилитель подключен к входу инвертора,выход порогового блока подключен к одному из информационных входов решающего блока и к информационному входу регистра сдвига, выходы которого подключены к соответствующим информационным входам решающего блока.

| Приемник дискретных сигналов | 1978 |

|

SU687620A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-30—Публикация

1987-11-26—Подача