гг

с ю

Изобретение относится к области вычислительной техники, а также может быть использовано в генераторах и цифровых синтезаторах частот (в частности, в дробных синтезаторах частот).

Цель изобретения - расширение области применения путем обеспечения возможности использования в цифровых синтезаторах частот.

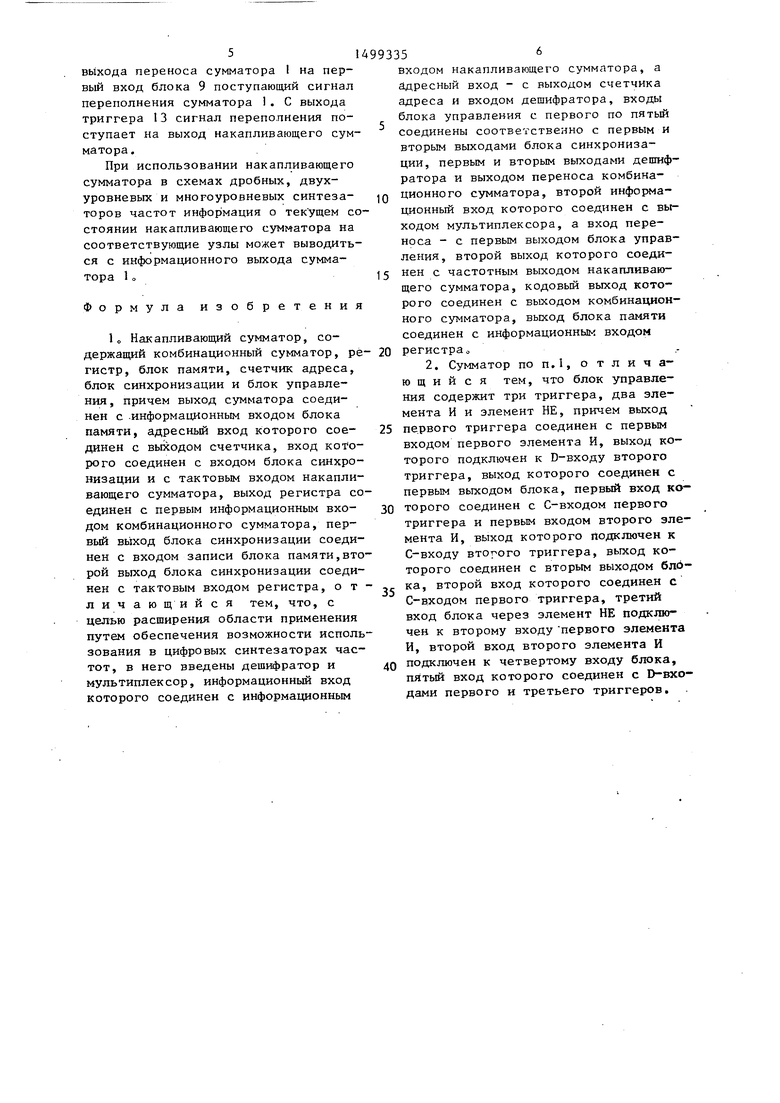

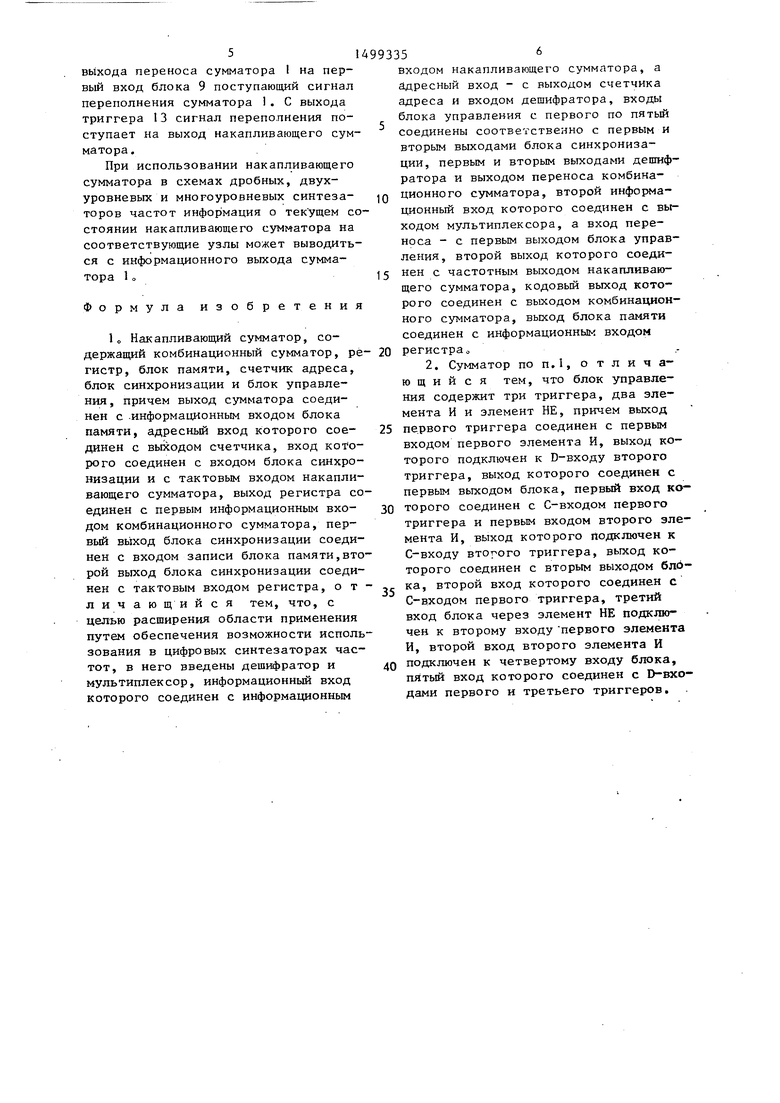

На фиг,1 представлена структурная схема накапливающего сумматора; на фиг.2 - структурная схема блока управления„

Накапливающий сумматор (фиг.О содержит комбинационный сумматор 1, регистр 2, блок 3 памяти, мультиплексор 4, информационный вход 5, дешифратор 6, счетчик 7, тактовый вход 8, блок 9 управления, блок 10 синхронизации.

Блок 9 управления (фиг.2) содержит первый, второй и третий триггеры 11 - 13, элемент НЕ 14, первый и второй элементы И 15 и 16.

Накапливающий сумматор работает следующим образом

На вход счетчика 7 и на вход блока 10 с входа 8 поступают тактовые импульсы„ Каждый входной тактовый импульс переводит счетчик 7 в следующее состояние о Выходной сигнал счетчика 7 в параллельном коде непосредственно управляет .работой мультиплексора 4, блока 3 и дешифратора 6. Блок 10 формирует на выходах несовпадающие во времени импульсы. На вхо мультиплексора 4 подается многоразрядный код.

Рассмотрим работу накапливающего сумматора во время действия одного тактового импульса. С помощью кода на выходе счетчика 7 выбирается соответствующая часть входного кода и со ответствующая часть зоны памяти 3 блока, в который информация была записана в соответствующем такте предыдущего цикла. С приходом от блока 10 импульсов на тактовый вход ре- гистра 2 информация с соответствующей зоны памяти блока 3 переписывается в регистр 2 и ПС ступает на первый информационный вход сумматора 1. На второй информационный вход сумматора 1 через мультиплексор 4 поступает соответствующая чгггь кода. В сумматор 1 осуществляете г арифметическое суммирование трех -шсел: поступающего с

0

5

0

5

0

5

выхода регистра 2 на первый информационный вход сумматора 1, поступающего с мультиплексора 4 на второй информационный вход сумматора I, поступающего с выхода блока 9 на вход переноса сумматора 1 о С приходом на входы записи блока 3 и блока 9 с выхода блока 10 импульса записи в соответствующую зону памяти блока 3,которую определяет поступающий со счетчика 7 параллельный код, записывается код суммы трех чисел, а в триггер 11 блока 9 с выхода переноса сумматора 1 сигнал переполнения Последний сигнал будет использоваться при суммировании чисел в следующем такте работы накапливающего сумматора

С помощью дешифратора 6 опознается начальное и конечное состояния счетчика 7, начало и конец цикла работы накапливающего сумматора. В начале цикла дешифратор 6 опознает нулевое состояние счетчика 7 и выдает на первом выходе сигнал с уровнем логической единицы. В блоке 9 этот сигнал логической единицы инвертируется элементом НЕ 14, блокирует элемент И 15„ Таким .образом, с приходом сигнала на тактовый вход блока 9 в триггер 12 записывается сигнал с уровнем логического нуля.

Во время других тактов цикла де- 5 шифратор 6 на первом выходе выдает сигнал с уровнем логического нуля. Элементом НЕ 14 сигнал инвертируется. Полученный на выходе элемента НЕ 14 сигнал с уровнем логической единицы пропускает через элемент И 15 сигнал с выхода триггера 11 на информа- ционньй вход триггера 12.

Таким образом, с помощью дешифратора 6 и блока 9 на вход переноса сумматора 1 подается сигнал логического нуля в начальном такте цикла и логический сигнал, соответствующий предыдущему состоянию выхода переноса сумматора 1 в последующих тактах цикла работы накапливающего сумматора о

На втором выходе дешифратора 6 появляется сигнал с уровнем логической единицы в последнем такте цикла Этот сигнал пропускает в блоке 9 через г лемент И 16 с выхода блока 10 на вход записи блока 9 поступающий

0

импульс синхронизации, с помощью которого в триггер 13 записывается с

5

выхода переноса сумматора 1 на первый вход блока 9 поступаюпщй сигнал переполнения сумматора 1, С выхода триггера 13 сигнал переполнения поступает на выход накапливающего сумматора.

При использовании накапливающего сумматора в схемах дробных, двухуровневых и многоуровневых синтезаторов частот информация о тек ущем со стоянии накапливающего сумматора на соответствующие узлы может выводиться с информационного выхода сумматора 1 о

Формула изобретения

1о Накапливающий сумматор, содержащий комбинационный сумматор, ре гистр, блок памяти, счетчик адреса, блок синхронизации и блок управления , причем выход сумматора соединен с .информационным входом блока памяти, адресный вход которого соединен с выходом счетчика, вход которого соединен с входом блока синхронизации и с тактовым входом накапливающего сумматора, выход регистра со единен с первым информационным входом комбинационного сумматора, первый выход блока синхронизации соединен с входом записи блока памяти,вто рой выход блока синхронизации соединен с тактовым входом регистра, о т личающий ся тем, что, с целью расширения области применения путем обеспечения возможности испсль зования в цифровых синтезаторах частот, в него введены дешифратор и мультиплексор, информационный вход которого соединен с информационным

10

15

20

993356

входом накапливающего сумматора, а адресный вход - с выходом счетчика адреса и входом дешифратора, входы блока управления с первого по пятьй соединены соответственно с первым и вторым выходами блока синхронизации, первым и вторым выходами дешифратора и выходом переноса комбинационного сумматора, второй информационный вход которого соединен с выходом мультиплексора, а вход переноса - с первым выходом блока управления, второй выход которого соединен с частотным выходом накапливающего сумматора, кодовый выход которого соединен с выходом комбинационного сумматора, выход блока памяти соединен с информационным входом регистра о

2, Сумматор по п.1, о т л и ч а- ю щ и и с я тем, что блок управления содержит три триггера, два элемента И и элемент НЕ, причем выход первого триггера соединен с первым входом первого элемента И, выход которого подключен к D-входу второго триггера, выход которого соединен с первым выходом блока, первый вход которого соединен с С-входом первого триггера и первым входом второго элемента И, выход которого подключен к С-ВХОДУ второго триггера, выход которого соединен с вторым выходом блока, второй вход которого соединен с С-входом первого триггера, третий вход блока через элемент НЕ подключен к второму входу первого элемента И, второй вход второго элемента И подключен к четвертому входу блока, пятый вход которого соединен с D-BXO- дами первого и третьего триггеров.

25

30

35

40

с:

« г

т

1

15

12

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство управления | 1983 |

|

SU1166108A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

Изобретение относится к вычислительной технике, а также может быть использовано в генераторах и цифровых синтезаторах частот (,в частности, в дробных синтезаторах частот). Цель изобретения - расширение области применения за счет возможности использования в цифровых синтезаторах частот. Накапливающий сумматор содержит комбинационный сумматор 1, регистр 2, блок 3 памяти, мультиплексор 4, информационный вход 5, дешифратор 6, счетчик 7, тактовый вход 8, блок 9 управления, блок 10 синхронизации. 1 з.п. ф-лы, 2 ил.

1В

9 С

13

Фш.г

| Патент США № 3735269, кл, 328/14, 1973„ Авторское свидетельство СССР 1335979, кло G 06 F 7/38, 1986. |

Авторы

Даты

1989-08-07—Публикация

1987-06-10—Подача