Изобретение относится к вычислительной технике и может быть использовано в устройствах управления и диагностирования дискретных объектов.

Целью изобретения является сокращение емкости памяти микрокоманд.

В устройстве реализовано обеспечение возможности анализа в одном такте группы логических условий, одновременно сформированных в функциональном блоке, использование блока памяти констант и сумматора, обеспечивающих алгоритмическое определение адреса перехода для любого числа возможных направлений выходов из

точки анализа при любой глубине контроля логических условии без дополнительных затрат на оборудовап)е.

Необходимость проверок групп логических условий может возникать в следующих ситуациях: при контроле параметров, отражающих движение объекта или процесс, где роль проверяемых логических условий выполняют значения контролируемых параметров, число значений параметров в группе определяется функциональными возможностями контролируемого устройства и требует организации ветвления в точках анализа по 2 направлений,

ю

где К - число проверяемых параметров в группе

Необходимость проверки, групп - логических условий, сформированных одновременно, возникает также при анализе состояния устройств по результатам диагностики функциональных блоков методом тестирования При этом число логических условий 01У) в группе, конструктивно заложенное в устройстве, определяет количество адресов переходов а конкретное значение логических условий в группе - значение адреса„ Таким образом, по результатам анализа состояния тестируемого устройства управление будет передано из основной программы на один из возможных адресов или на продолжение основной про- граммыо

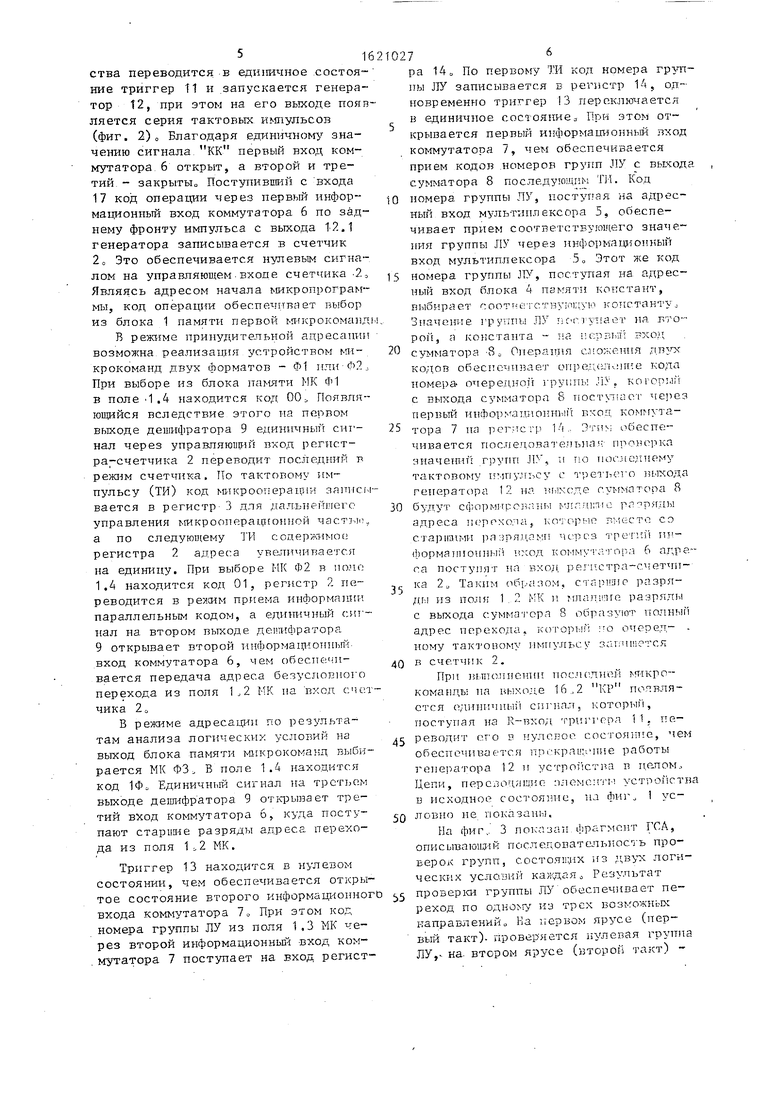

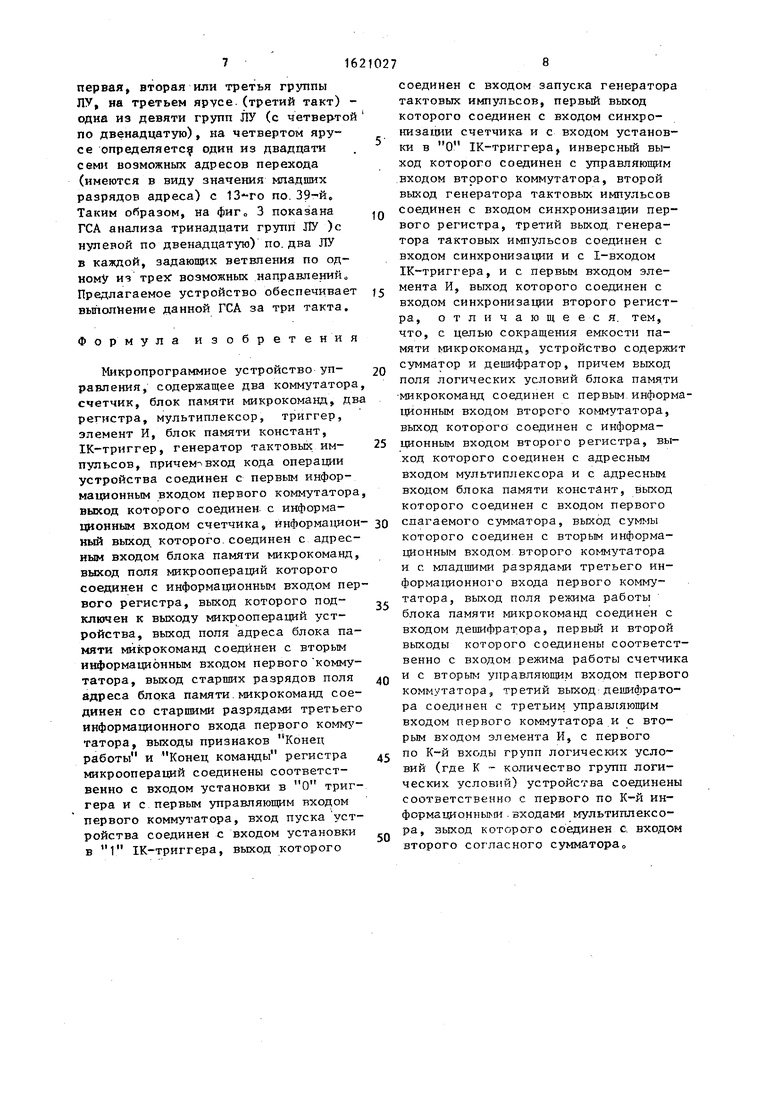

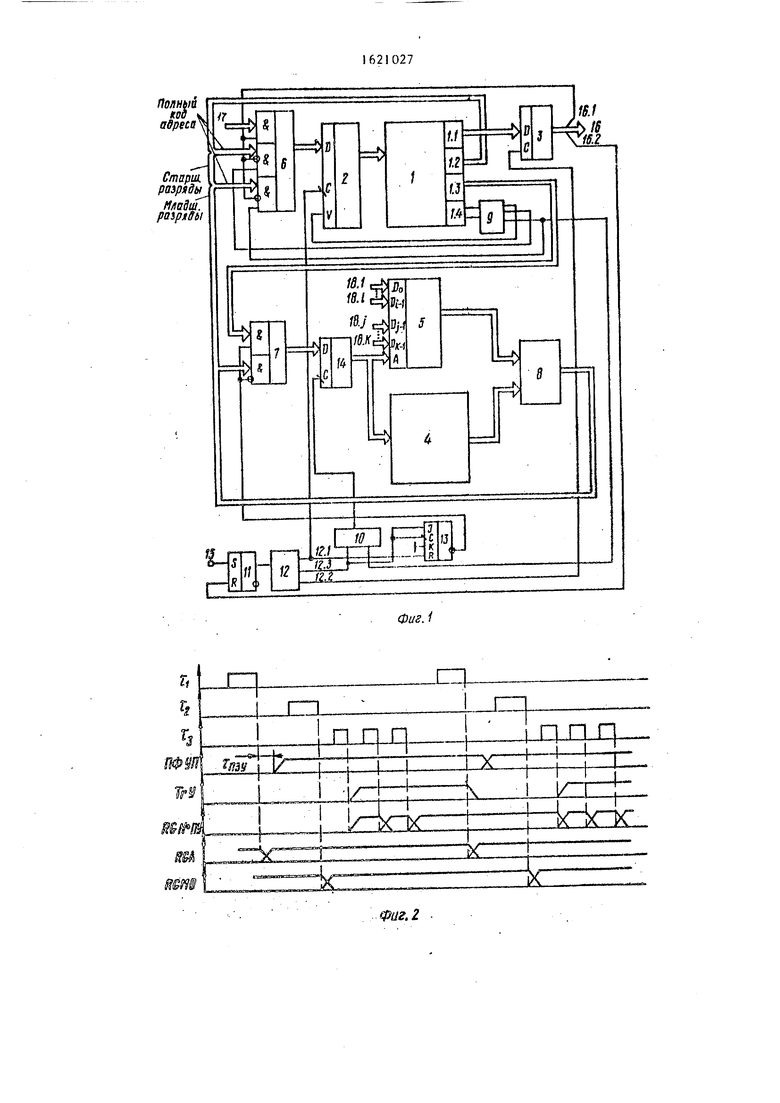

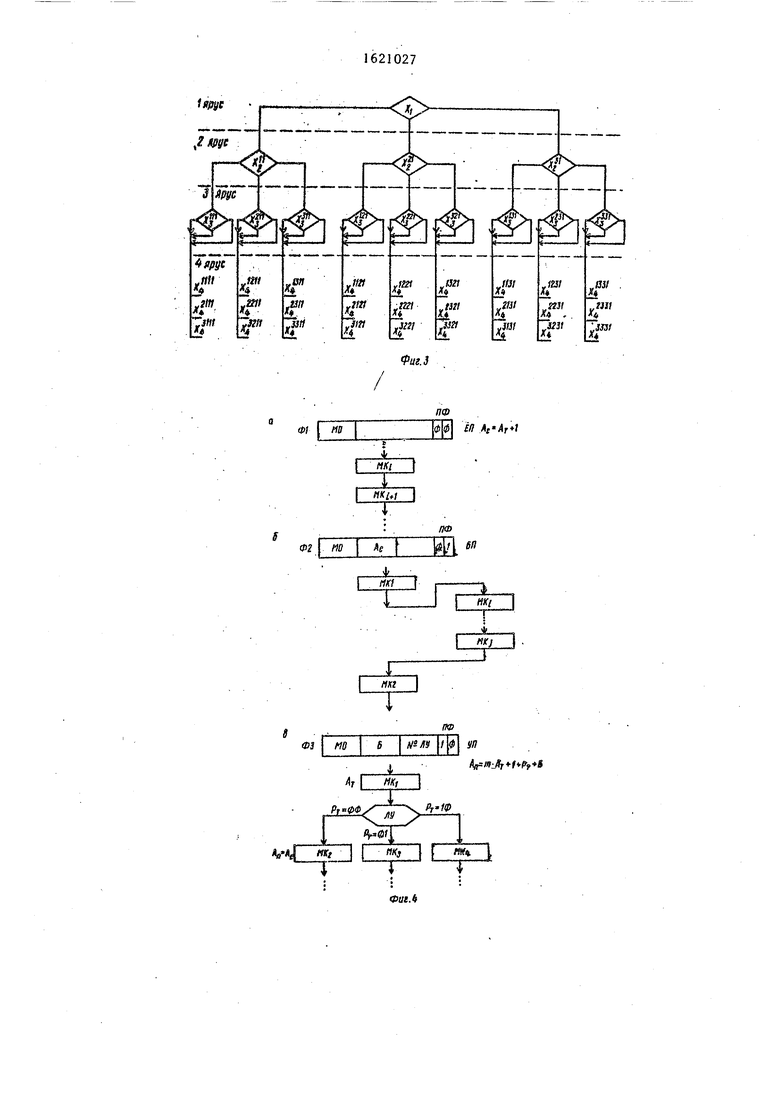

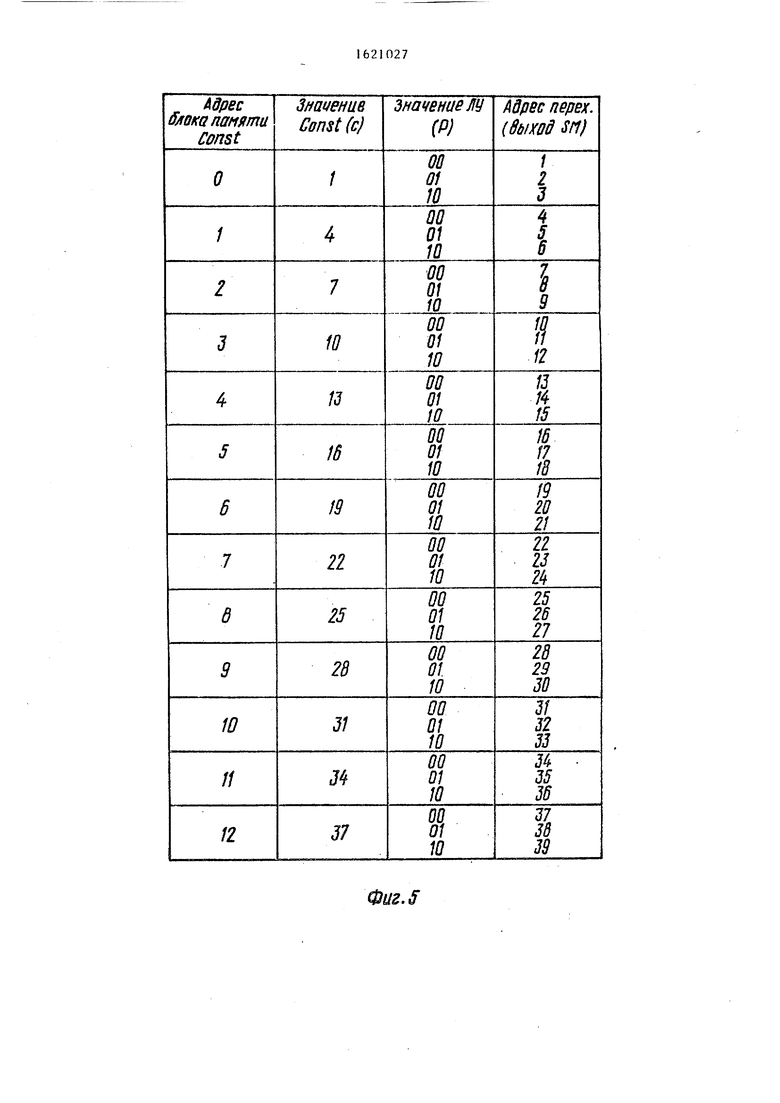

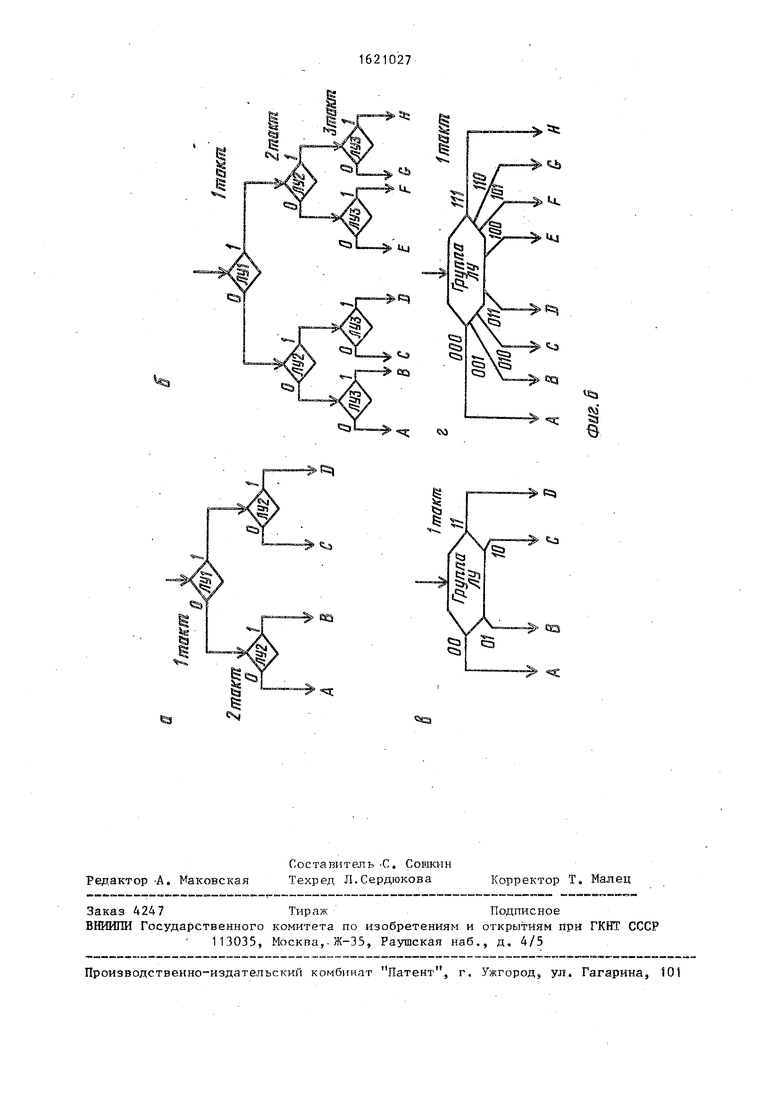

На фиг„ 1 показана функциональная схема микропрограммного устройства управления и диагностирования; на фиг, 2 - временная диаграмма выполнения микрокоманды формата ФЗ; на фиг„ 3 - граф-схема алгоритма проверки логических условий (ЛУ) с трех альтернативных ветвлений для трех ярусов контроля; на фиг„ 4 - форматы микрокоманд (Ж), применяемые в устройстве, и соответствующие им способы формирования адреса перехода; на фиг 5 - таблица, поясняющая принцип формирования адреса перехода на выходе сумматора в соответствии со значением константы, хранимой в блоке памяти констант, и в зависимости от значения группы ЛУ; адрес блока памяти констант задается номером проверяемой группы ЛУ; на фиг о 6 - фрагменты ГСА анализа ЛУ в виде бинарного (а, б) и К-го (в, г) деревьев

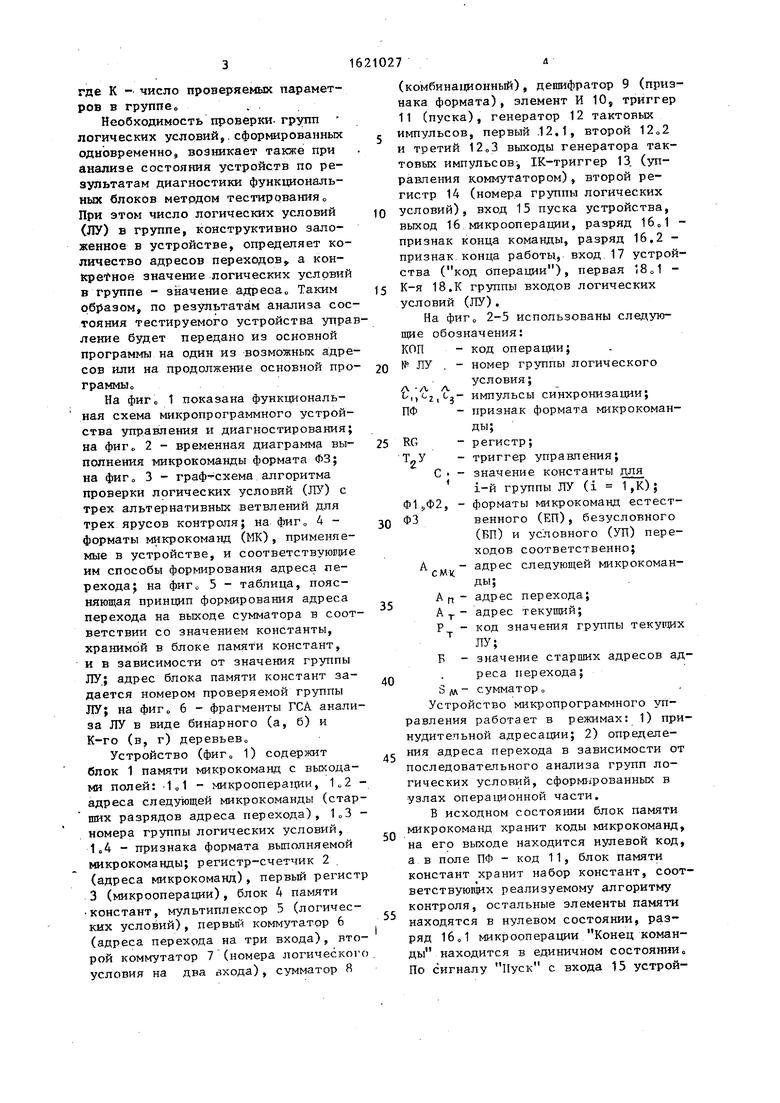

Устройство (фиг о 1) содержит блок 1 памяти микрокоманд с выходами полей: 1„1 - микрооперации, 1„2 - адреса следующей микрокоманды (старших разрядов адреса перехода), 103 - номера группы логических условий, 1„4 - признака формата выполняемой микрокоманды; регистр-счетчик 2 (адреса микрокоманд), первый регистр 3 (микрооперации), блок 4 памяти констант, мультиплексор 5 (логических условий), первый коммутатор 6 (адреса перехода на три входа), второй коммутатор 7 (номера логического условия на два дхода), сумматор 8

0

5

0

5

0

5

(комбинационный), дешифратор 9 (признака формата), элемент И 10, триггер 11 (пуска), генератор 12 тактовых импульсов, первый 12,1, второй 12«2 и третий 1203 выходы генератора тактовых импульсов, 1К-триггер 13 (управления коммутатором), второй регистр 14 (номера группы логических условий), вход 15 пуска устройства, выход 16 микрооперации, разряд - признак конца команды, разряд 16.2 - признак конца работы, вход 17 устройства (код операции), первая 18„1 - К-я 18.К группы входов логических условий (ЛУ).

На фиг0 2-5 использованы следующие обозначения: КОП - код операции; № ЛУ - номер группы логического

условия;

л -л л.

импульсы синхронизации;

ПФ- признак формата микрокоманды;

-регистр;

-триггер управления;

-значение константы для i-й группы ЛУ (i 1,К);

Ф1 .,Ф2, - форматы микрокоманд естест- ФЗ венного (ЕП), безусловного (БП) и условного (УП) переходов соответственно;

-адрес следующей микрокоманды;

А п - адрес перехода;

Ат- адрес текущий;

Р - код значения группы текущих ЛУ;

Б - значение старших адресов адреса перехода;

5 дл сумматор „

Устройство микропрограммного управления работает в режимах: 1) при- нудитепьной адресации; 2) определения адреса перехода в зависимости от последовательного анализа групп логических условий, сформированных в узлах операционной части,

В исходном состоянии блок памяти микрокоманд хранит коды микрокоманд, на его выходе находится нулевой код, а в поле ПФ - код 11, блок памяти констант хранит набор констант, соответствующих реализуемому алгоритму контроля, остальные элементы памяти находятся в нулевом состоянии, разряд 16 о 1 микрооперации Конец команды находится в единичном состоянии. По сигналу Пуск с входа 15 устрой0

5 RG

Т2У

0

5

А

сми.

5 1

ства переводится в единичное состояние триггер И и запускается генератор Т2, при этом на его выходе появляется серия тактовых импульсов (фиг. 2)„ Благодаря единичному значению сигнала КК первый вход коммутатора 6 открыт, а второй и третий - закрыты,, Поступивший с входа 17 код операции через первый информационный вход коммутатора 6 по заднему фронту импульса с выхода 12.1 генератора записывается в счетчик 20 Это обеспечивается нулевым сигналом на управляющем входе счетчика 2.0 Являясь адресом начала микропрограммы, код операции обеспечивает выбор из блока 1 памяти первой микрокоманд

В режиме принудительной адресации возможна реализация устройством микрокоманд двух форматов - Ф1 пли 2 При выборе из блока памяти МК Ф1 в поле 1.4 находится код 00, Появляющийся вследствие этого па первом выходе дешифратора 9 единичный сигнал через управляющий вход регистра-счетчика 2 переводит последний в режим счетчика. По тактовому импульсу (ТИ) код микрооперации записывается в регистр 3 дтя далънРнпего управления микрооперационной часты,-., а по следующему ТИ содержимое регистра 2 адреса увеличивается на единицу. При выборе МК Ф2 в imno 1.А находится код 01, регистр 2 переводится в режим приема информации параллельным кодом, а единичный сит- нал на втором выходе дешифратора 9 открывает второй информационный вход коммутатора 6, чем обеспечивается передача адреса безусловно о перехода из поля ,2 FK на вход c.nei чика 20

В режиме адресации по результатам анализа логических условий на выход блока памяти микрокоманд выбирается МК ФЗ, В поле 1.4 находится код 1Ф, Единичный сигнал на третьем выходе дешифратора 9 открывает третий вход коммутатора 6, куда поступают старшие разряды адреса перехода из поля 1,2 МК.

Триггер 13 находится в нулевом состоянии, чем обеспечивается открытое состояние второго информационного входа коммутатора 70 При этом кол, номера группы ЛУ из поля 1.3 МК через второй информационный вход коммутатора 1 поступает на вход регист10276

ра 14 о По первому ТИ код номера группы ЛУ записывается в регистр 14, одновременно триггер 13 переключается в единичное состояние,, При этом открывается первый информационный вход коммутатора 7, чем обеспечивается прием кодов номеров групп ЛУ с выход сумматора 8 последующим ТП. Код

10 номера группы ЛУ, поступая на адресный вход мультиплексора 5, обеспечивает прием соответствующего значения группы ЛУ через информационный вход мультиплексора 5„ Этот же код

15 номера группы ЛУ, поступая на адресный вход блока 4 памяти констант, выбирает I™OOT -L . о вумкую константу. Значение ipy-iiui ЛУ -Л П чнает на второй, а константа - ил ЧРГЛГ хоц

0 сумматора 8, Операция с.тохонпч лвух кодов обеспечивает oiipev inline кода номера очередной i руппь: Л . коюгы;г с выхода сумматора 8 поступает через первый ииформапионный г.хоп коммут а25 тора 7 па рег-тсгр 1 i л обеспечивается пост1ет.оватечъна проверка значений групп JP, и г HI тюече.пнему тактовому импульсу с трстл-oio выхода генератора 12 и ПРУСТ,о суммгптооа 8

30 будут сформированы р-г трнды адреса nepexoui, ко-, с.рно г ii-сто со старшими pn ФЯЦОУИ мсгсз трепл п-п- формаппоннын вход комму- К 4 пол 6 адреса поступят на вход ре:пстра-счетчика 2., Таким образом, стгрчлю разряды из поля 1 2 УК и млаш Пе разряды с выхода сумматора 8 образ гнгт полный адрес перехода, ко горы ; о очеретт- . ному тактовому импупьсу з..л мнется в счетчик 2.

При шптопношш iiocjii пней NTIKPO-- команды па выходе 16,2 КГ появляется единичный сигнал, который, поступая на R-вход триггера 11. переводят pro Р нулевое состояние, чем обеспечивается прекращение работы генератора 12 и устрш штва в целом, Цепи, переводящие П.ЧОМСНЧР устройства в исходное состояние, на фиг о 1 усQ ловно не показаны.

На фиг. 3 локлзап фрг.гмент ГСА, описывающий послецователыюсч ь проверок групп, состоящих из двух логических условий каядаяо Результат

5 проверки группы ЛУ обеспечивает переход по одному из трех возможных направлений„ Ка первом ярусе (первый такт), проверяется нулевая группа ЛУ на втором ярусе (второй такт) 35

0

5

первая, вторая или третья группы ЛУ, на третьем ярусе.(третий такт) - одна из девяти групп ЛУ (с четвертой по двенадцатую), на четвертом ярусе определяется один из двадцати семи возможных адресов перехода (имеются в виду значения младших разрядов адреса) с по. 39--Й. Таким образом, на фиг0 3 показана

ГСА анализа тринадцати групп ЛУ )с нулевой по двенадцатую) по. два ЛУ в каждой, задающих ветвления по одному из трех возможных направлений Предлагаемое устройство обеспечивает выполнение данной ГСА за три такта.

Формула изобретения

Микропрограммное устройство уп- равления, содержащее два коммутатора счетчик, блок памяти микрокоманд, дв регистра, мультиплексор, триггер, элемент И, блок памяти констант, IK-триггер, генератор тактовых импульсов, причем- вход кода операции устройства соединен с первым информационным входом первого коммутатора выход которого соединен с информационным входом счетчика, информацион ный выход которого соединен с адресным входом блока памяти микрокоманд, выход поля микроопераций которого соединен с информационным входом первого регистра, выход которого под- ключей к выходу микроопераций устройства, выход поля адреса блока памяти микрокоманд соединен с вторым информационным входом первого коммутатора, выход старших разрядов поля адреса блока памяти микрокоманд соединен со старшими разрядами третьего информационного входа первого коммутатора, выходы признаков Конец работы и Конец команды регистра микроопераций соединены соответственно с входом установки в О триггера и с первым управляющим входом первого коммутатора, вход пуска устройства соединен с входом установки в 1 IK-триггера, выход которого

5

5

0 0 5 о $

соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с входом синхронизации счетчика и с входом установки в О IK-триггера, инверсный выход которого соединен с управляющим входом второго коммутатора, второй выход генератора тактовых импульсов соединен с входом синхронизации первого регистра, третий выход генератора тактовых импульсов соединен с входом синхронизации и с 1-входом IK-триггера, и с первым входом элемента И, выход которого соединен с входом синхронизации второго регистра, отличающееся, тем, что, с целью сокращения емкости памяти микрокоманд, устройство содержит сумматор и дешифратор, причем выход поля логических условий блока памяти микрокоманд соединен с первым информационным входом второго коммутатора, выход которого соединен с информационным входом второго регистра, выход которого соединен с адресным входом мультиплексора и с адресным входом блока памяти констант, выход которого соединен с входом первого слагаемого сумматора, выход суммы которого соединен с вторым информационным входом второго коммутатора и с. младшими разрядами третьего информационного входа первого коммутатора, выход поля режима работы блока памяти микрокоманд соединен с входом дешифратора, первый и второй выходы которого соединены соответственно с входом режима работы счетчика и с вторым управляющим входом первого коммутатора, третий выход дешифратора соединен с третьим управляющим входом первого коммутатора к с вторым входом элемента И, с первого по К-й входы групп логических условий (где К количество групп логических условий) устройства соединены соответственно с первого по К-й информационными входами мультиплексора, выход которого соединен с входом второго согласного сумматора.

ПО/IHbltt

код .

affpeca

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1543402A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления и диагностирования дискретных объектов. Цель изобретения - сокращение емкости памяти микрокоманд за счет обеспечения одновременной проверки групп логических условий в одном такте. Устройство содержит два коммутатора, счегчик, блок памяти микрокоманд, два регистра, мультиплексор, триггер, элемент И, регистр, блок памяти констант, TK-ipiinep, генератор тактовых импупьсов, дешифратор и суммчтор. Поль досппается за счет введения в устропстго дешифратора и сумматора. Изобретение позволяет обеспечивать возможность анализа в одном тане группы логических условии, одновременно сформированных в функциональном блоке, 6 чл , (Ј

Старт разряды

НладиГ разрой

„ш 4

ffit

«

X4

УВП

F

ФГ

El

рг g

ФЗ MO

t 7 J

j {|

yffl

&

„ЙЙ

Ј4

/p

л

уда

„w/

it

«

„Ю/

л

«

да/

ЛЯ/

,flj/ 2i

ЖЙЯ x« ,

JB3I

x«

A if

if

фф Ј11 Ле Ат 1

Г

| j

l/l w

ГЖ..-..1

l

w

K,f:mJj+1 Pr &

AT Mf I

Фиг. &

«ss

1

| Майоров С.А , Новиков Г0И„ Принципы организации цифровых маш1н Л.: Машиностроение, 1974, с 432, Авторское свидетельство (ССР № 1117637, кл Г, 06 Т 9/22, 198 о Авторское свидетельство СССР № 1242946, кл G 06 Г 9/22, 1984 |

Авторы

Даты

1991-01-15—Публикация

1988-03-28—Подача