первым информационным входом счетчика адреса, выход третьего блока элементов И соединен со вторым входом шестого блока элементов И и прямым входом седьмого блока элементов И, вькоды которых соединены соответст1вно с входом второго операнда блока контроля и суммирования и первым входом второго блока элементов ИЛИ, выход неисправности блока контроля и суммирования является выходом ошибки устройства и соединен через одновибратор с первым входом элемен ИЛИ, выход которого соединен с нулевым входом триггера пуска, выход результата сзт мирования блока контроля и суммирования соединен с вторым входом второго блока элементов ИЛИ, Bbixcto которого соединен с информационным входом регистра номеро остатков и вторым информационным входом счетчика адреса, первый,второй входы группы входов .кода операций устройства соединены соответственно с вторым входом первого и третьим входом второго блоков элеметов ИЛИ, второй выход счетчика адреса соединен с прямым входом восьмого блока элементов И, выход которого соединен с вторым входом группы входов блока памяти микрокоманд, первый выход генератора импульсов соединен с входами второго и третьего элементов И, выходы которых соединены соответственно со счетным входом и входом синхронизации счетчика адреса, выход третьего элемента И соединен с входом синхронизации р егистра номеров остатков и единичным входом первого триггера управления, выход которого соединен с инверсным входом восьмого блока элементов И и через второй элемент задержки - с прямым входом второго триггера управления, первые (к+2) выходов дешифратора линеек микрокоманд соединены соответственно с первыми входами элементов И с четвертого до (к+4)-и и нулевьм входом второго триггера управления, единичный выход которого соединен с вторым входом второго элемента И, нулевой выход второго триггера управления соединен с вторыми входами первого и третьего элементов И,

(к+2)-и выход дешифратора линеек микрокоманд соединен с вторыми входами первого, второго, третьего, четвертого и пятого блоков элементов И выход конца работы группы выходов которого соединен с вторым входом элемента ИЛИ, второй выход генератора импульсов соединен с нулевым, входом первого триггера управления, счетным входом счетчика линеек микроkoмaнд и с вторыми входами элементов И с четвертого до (к+4)-й, выходы которых соединены соответственно с входом синхронизации регистра остатков микрокоманд и входами синхронизации регистра линеек микрокоманд, выход регистра номеров остатков соединен с входом дешифратора остатков микрокоманд, выходы которого соединены с соответствзпощими управляющими входами коммутатора.

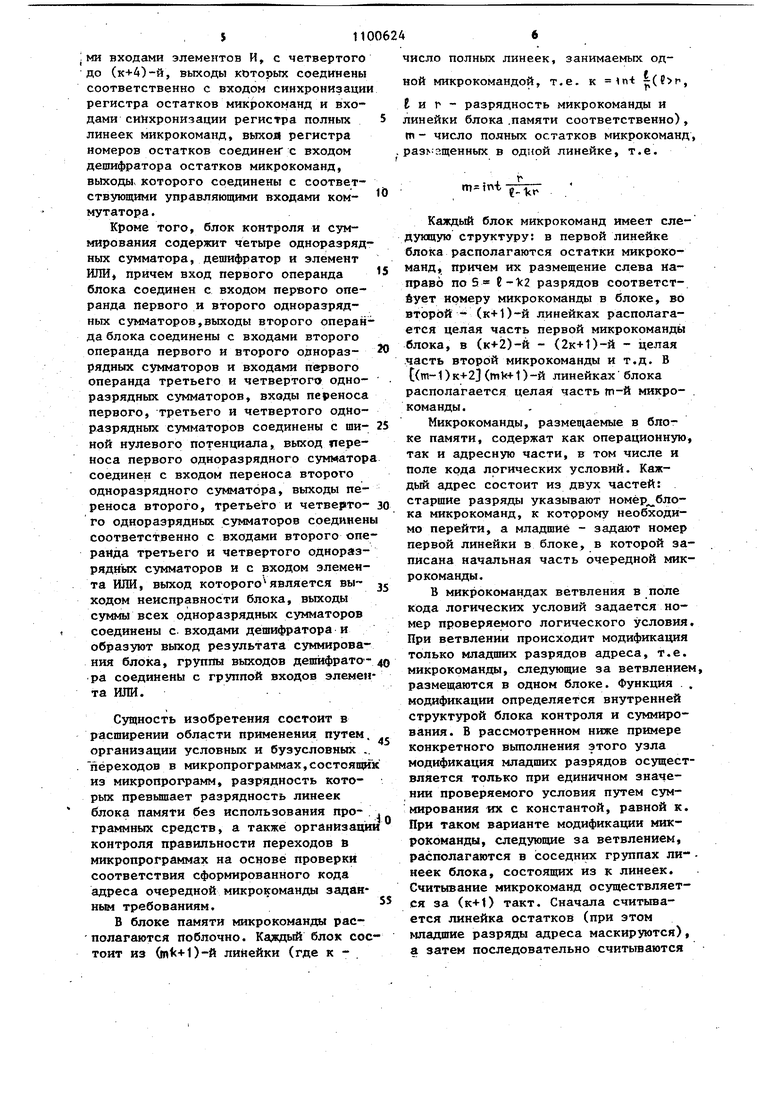

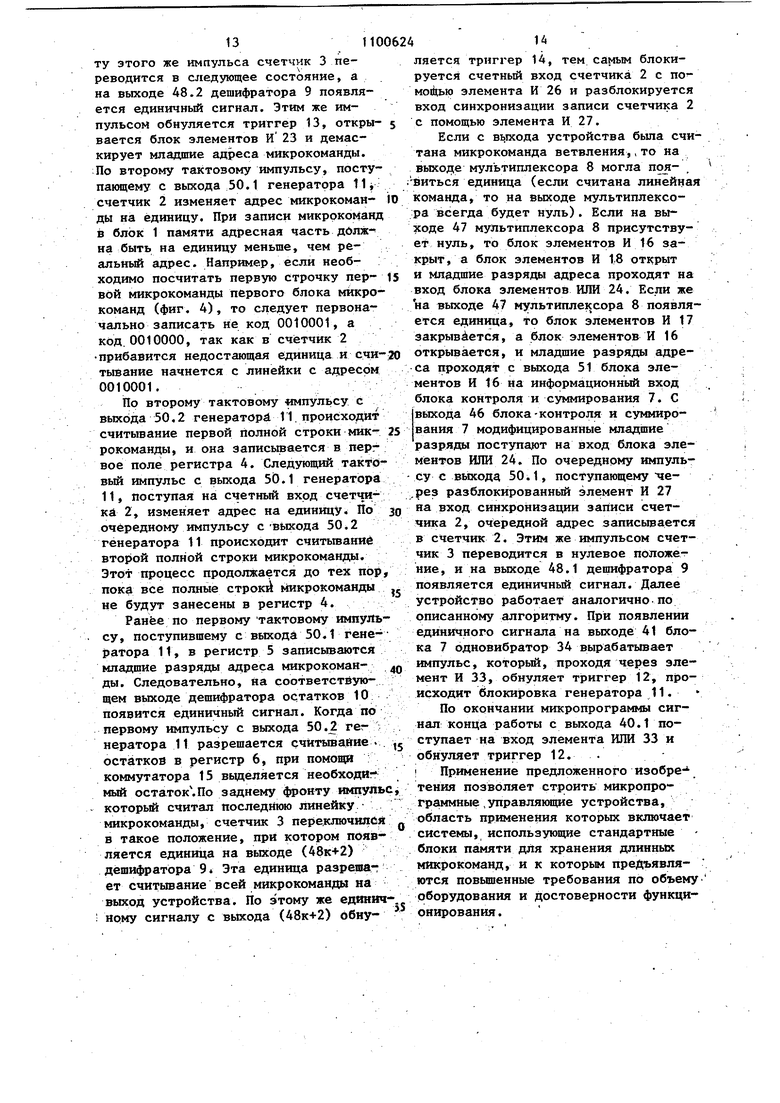

2. Устройство по п. 1, о т л и чающееся тем, что блок контроля и суммирования содержит четыре одноразрядных сумматора, дешифратор и элемент ИЛИ, причем вход первого операнда блока соединен с входами первого операнда первого и второго одноразрядных сумматоров, входы, второго операнда рлока соединены с входами второго операнда первого и второго одноразрядных сумматоров и с входами первого операнда третьего и четвертого одноразрядных сумматоров, входы переноса первого, третьего и четвертого одноразрядных сумматоров соединены с шиной нулевого потенциала, выход переноса первого одноразрядного сз мматора соединен с входом переноса второго одноразрядного сумматора, выходы переноса второго, третьего и четвертого однЬразрядных сумматоров соединены соответственно с входами второго операнда третьего и четвертого одноразрядных сумматоров и с входом элемента ИЛИ, выход которого является выходом неисправности блока, выходы суммы всех одноражрядных сумматоров соединены с входами дешифратора и образуют выход результата суммирования блока, группы, выходов дешифратора соединены с группой входов элемента ИЛИ. 111 Изобретение относится к вьшнслительной технике и автоматике и может быть использовано при. построении микропрограммных устройств управления ЭВМ и цифровых систем. Известно устройство микропрограммного управления, содержащее блок памяти микрокоманд, два счетчика, дешифратора, регистр микрокоманд, генератор импульсов, элементы И и ИЛИ Си. Недостатком этого устройства является низкая экономичность блока памяти, обусловленная тем, что в отдельных его ячейках может храниться толь ко целое число микрокоманд. Известно устройство микропрограммного управления, содержащее блок па мяти микрокоманд, два счетчика, два дешифратора, регистр микрокоманд, два элемента задержки, элементы И, ИЛИ, одновибратор, триггер, генератор импульсов . Недостатком данного устройства является узкая область применения, обусловленная невозможностью реализа ции микропрограмм, состоящих из микрокоманд, разрядность которых больше длины яче;ек блока памяти. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является микропрограммное устройство управления, содержащее блок памяти микрокомайд, счетчик адреса, счетчик линеек микрокоманд, дешифратор линеек микрокоманд, генератор импульсов, триггер пуска, .коммутатор, элементы И, ИЛИ, одновибратор, первьй и второй элементы задержки, причем вход пуска устройств-а соединен с единичным входом триггера пуска, выход которого соединен с вхо дом генератора импульсов, первый выход генератора импульсов соединен с первым бходом первого элемента И, вы ход которого соединен с входом первого элемента задержки, первая группа выходов счетчика адресов соединена с входами старших разрядов грзгппы входов блока памяти микрокоманд, группа выходов которого соединена с группой информационных входов регистра остатков микрокоманд, .первый - к-й, где к - число полных линеек, занимаемых одной микрокомандой, выходы группы выходов блока памяти микрокоманд соединены соответственно с первым - к-м информационными входами регистра полных линеек микрокоманд, первьй - четвертьй выходы группы выходов которого соединены с первыми входами первого - четбертого блоков элементов. И, первый Ш-й, где tn - число полных остатком микрокоманд, размещаемых в одной линейке, вьпсоды регистра остатков микрокоманд соединены соответственно с первым -m-м информационными входами коммутатора, въшод которого соединен с первым входом пятого блока элементов И, выходы четвертого и пятого блоков элементов И соединены с соответствующими выходами группы выходов микроопераций устройства, выход счетчика линеек микрокоманд соединен с входом дешифратора линеек микрокоманд 3. Недостатком указанного устройства является узкая область применения в связи с возможностью реализай(ии только линейных последовательностей операционных микрокоманд без обращения к памяти команд системы, большой избыточностью блока памяти микрокоманд, вызванной тем, что в нем допускается хранение линейных последовательностей только с естественной адресацией микрокоманд, а следовательно большой избыточностью запоминающих устройств для хранения программ, использующих прототип в качестве управлякицего устройства, нижнего уровня по той же причине система, в которой используется устройство-прототип, имеет низкое быстродействие вследствие большого числа обращений к памяти команд при выполнении микропрограмм с ветвлениями) , низкой достоверностью фу1 кционирования, обусловленной отсутствием средств контроля правильности вы- полнения микропрограмм. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, Что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, счетчик адреса, счетчик линеек микрокоманд, регистр полных линеек микрокоманд, регистр остатков микрокоманд, дешифратор линеек микрокоманд, коммутатор, триггер пуска, генератор импульсов, восемь блоков элементов И, первый и второй блоки элементов ИЛИ, (к4-4) элемента И, где к - число полных линеек, занимаемых .микрокомандой элемента И, первый и второй элементы задержки, одновибратор, причем вход пуска устройства соединен с единичным входом триггера пуска, выход которого соединен с входом генератора импульсов, первый выход генератора импульсов соединен с первым входом первого элемента И,выход Которого соединен с входом первого элемента задержки,первая информационная группа выходов счетчика адресов соединена с входами старших разрядов группы информационных входов блока памяти микрокоманд, выходы которого (Соединены с группой информа ционных входов регистра остатков микрокоманд, выходы с первого по к-й группы выходов блока памяти микрокоманд соединены с соответствующими информационными входами регистра полных линеек микрокоманд, первьй,второй, третий и четвертый выходы группы выходов которого соединены с первыми входами соответственно первого, второго, третьего и четвертого блоко элементов И, первые in выходов регистра остатков микрокоманд (где гп - чисЛо полных остатков микрокоманд, размещаемых в одной линейке) соединены соответственно с первыми m информационными входами коммутатора, вьпсод которого соединен с первым входом пятого блока элементов И, вьпсоды четвертого и пятого блоков элеменяов И соединены с соответствующими выходами группы вьгходов микроопераций устройства, выход счетчика линеек микрокоманд соединен с входом дешифратора линеек микрокоманд, дополнительно введены блок контроля и суммирования, регистр номеров остатков, дешифратор остатков микрокоманд, мультиплексор, первый и второй триггеры управления, причем вход логических УСЛОВИЙ уст{)ойства и выход первого блока элементов И соединены соответственно с информационным и адрес ным входами мультиплексора, выход которого соединен с входом первого операнда блока контроля и суммирования , первым входом шестого блока элементов И и инверснымI входом седьмого блока элементов И, выход второго блока элементов И соединен с первым входом первого блока элементов ИЛИ, выход которого соединен с первым информационным входом счетчика адреса, выход третьего блока элементов И соединен со вторым входом шестого блока элементов И и с прямым входом седьмого блока элементов И, выкоды

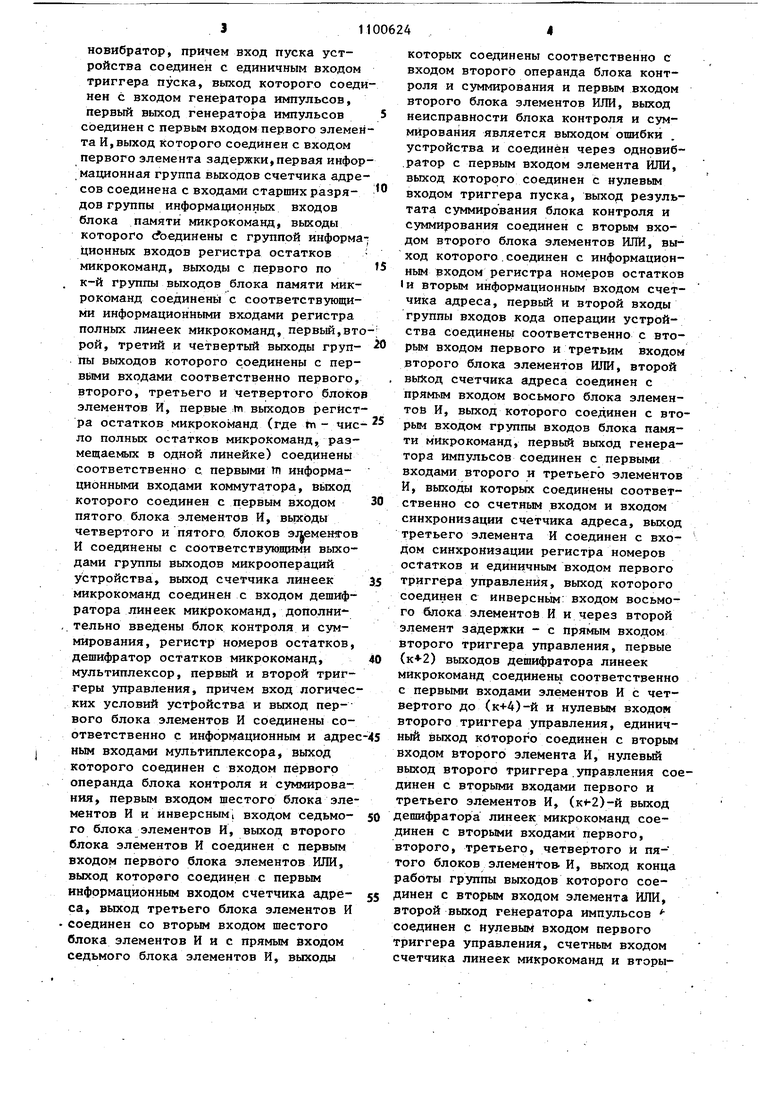

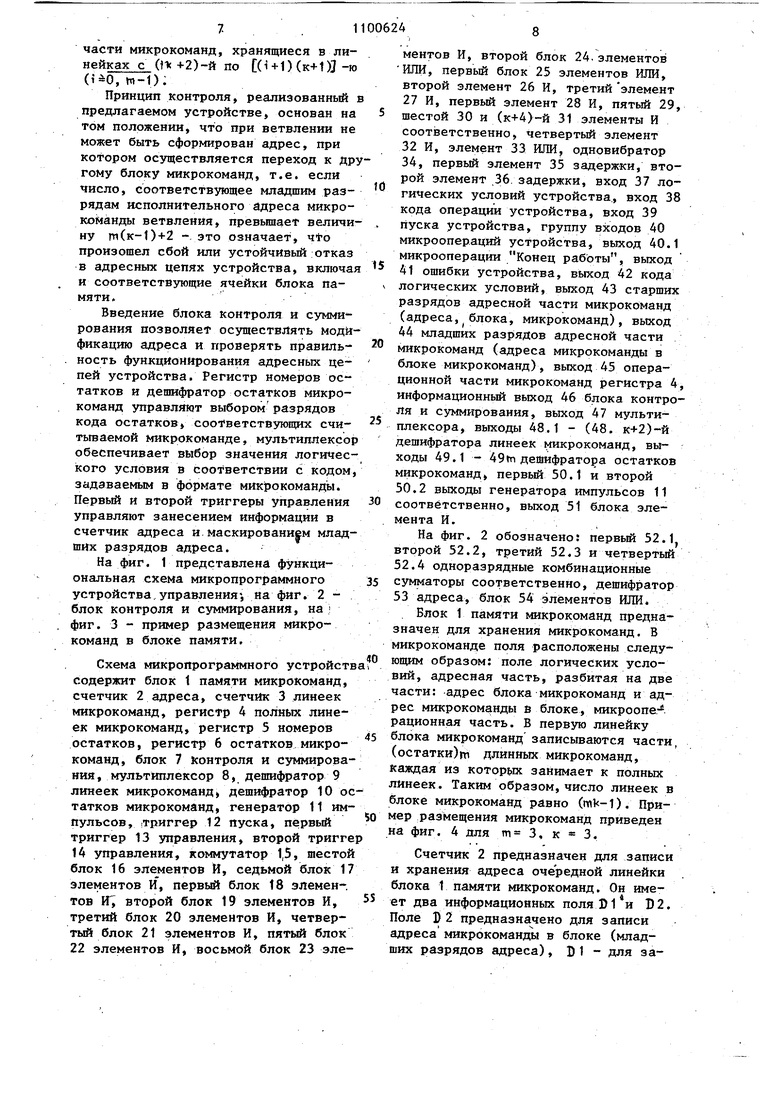

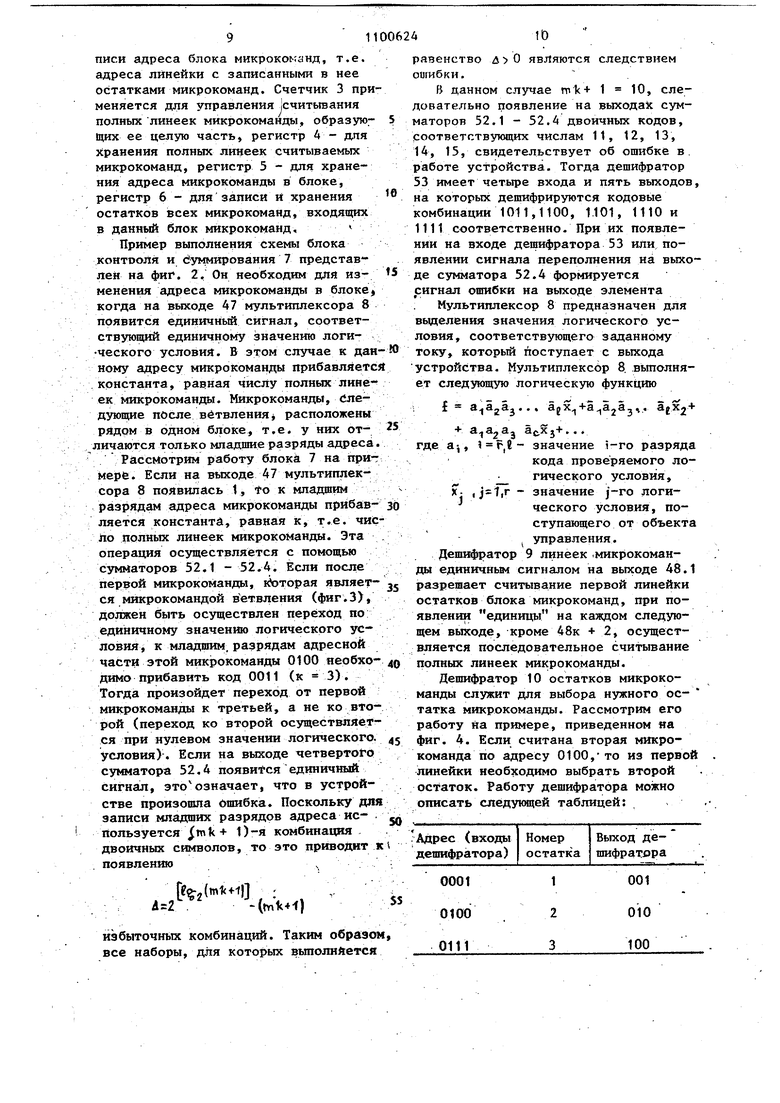

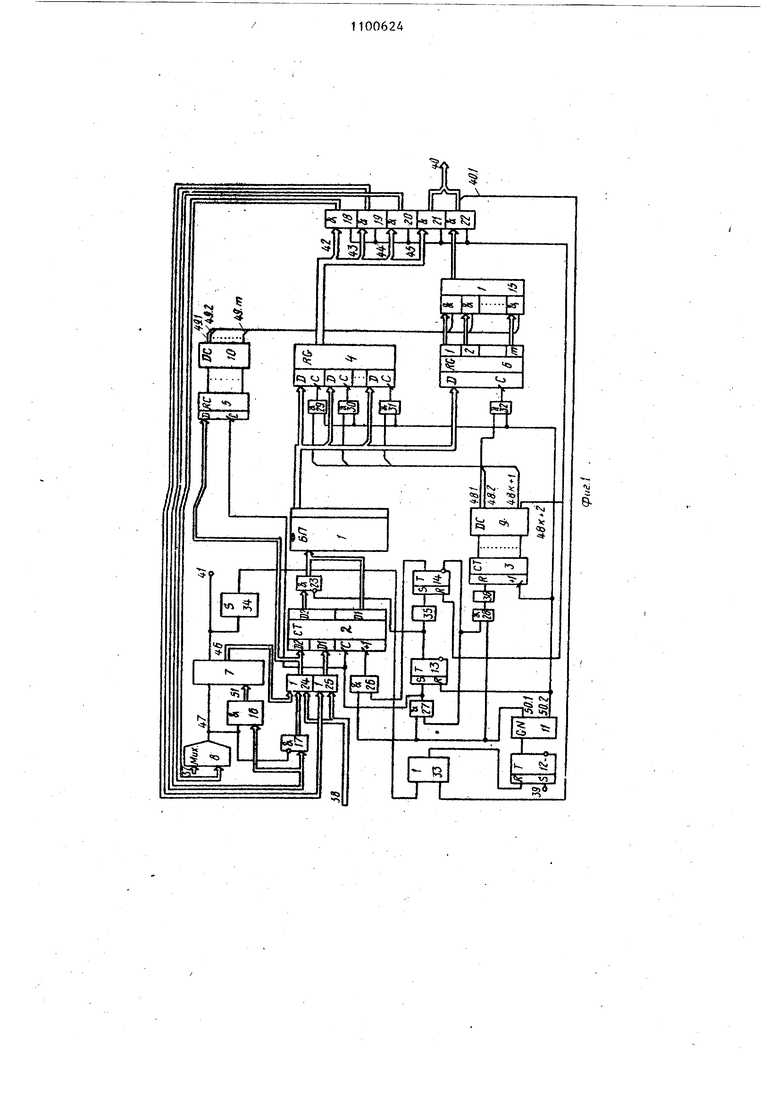

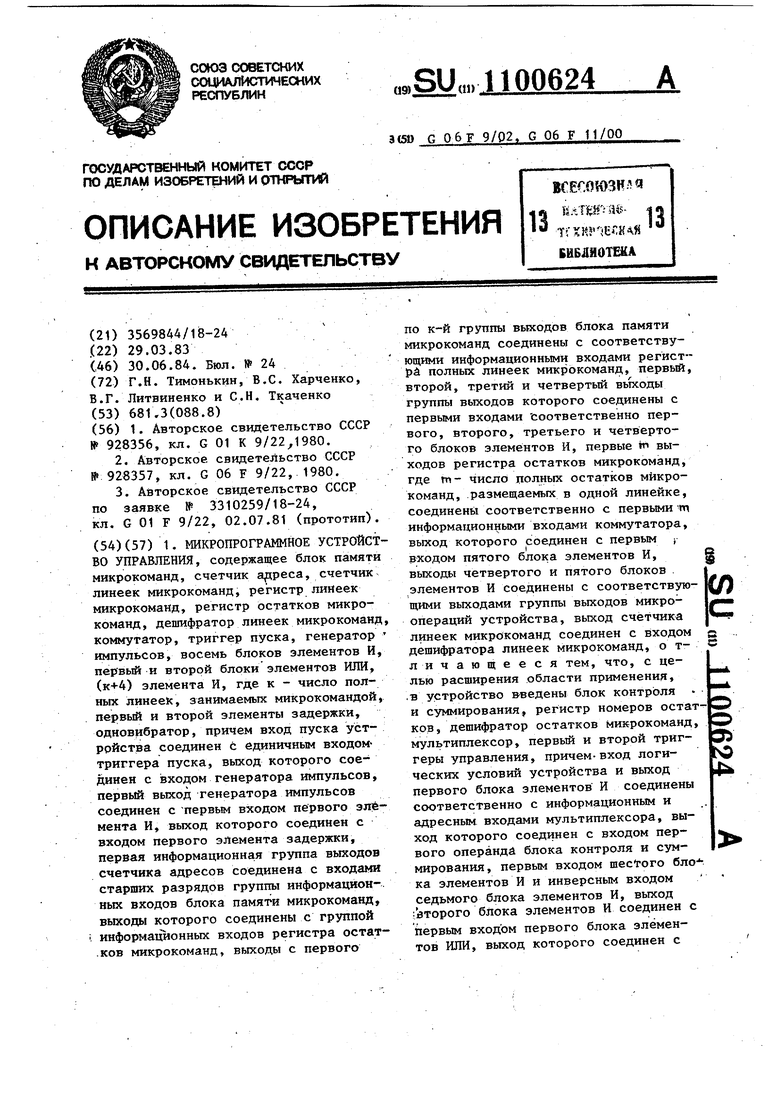

которых соединены соответственно с входом второго операнда блока контроля и суммирования и первым входом второго блока элементов ИЛИ, выход неисправности блока контроля и суммирования является выходом ошибки . устройства и соединён через одновиб.ратор с первым входом элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, выход результата суммирования блока контроля и суммирования соединен с вторым входом второго блока элементов ИЛИ, выход которого.соединен с информационным входом регистра номеров остатков 1и Вторым информационным входом счетчика адреса, первьй и второй входы группы входов кода операции устройства соединены соответственно с вторым входом первого и третьим входом второго блока элементов ИЛИ, второй выход счетчика адреса соединен с прямым входом восьмого блока элементов И, выход которого соединен с вторым входом группы входов блока памяти микрокоманд, первый выход генератора импульсов соединен с первыми входами второго и третьего элементов И, выходы которых соединены соответственно со счетным входом и входом синхронизации счетчика адреса, выход третьего элемента И соединен с входом синхронизации регистра номеров остатков и единичным входом первого триггера управления, выход которого соединен с инверснь1м: входом восьмого блока элементов И и через второй элемент задержки - с прямым входом второго триггера управления, первые ) выходов дешифратора линеек микрокоманд соединены соответственно с первыми входами элементов И с четвертого до (к+4)-й и нулевым входом второго триггера управления, единичный выход которого соединен с вторым входом второго элемента И, нулевый выход второго триггера управления содинен с вторыми входами первого и третьего элементов И, ()-й выход дешифратора линеек микрокоманд соединен с вторыми входами первого, второго, третьего, четвертого И пятого блоков элементов- И, выход конца работы группы выходов которого соединен с вторым входом элемента ИЛИ, второй выход генератора импульсов соединен с нулевым входом первого триггера управления, счетным входом счетчика линеек микрокоманд и вторыjми входами элементов И, с четвертого до (к+4)-й, выходы которых соединены соответственно с входом синхронизаци регистра остатков микрокоманд и входами синхронизации регистра полных линеек микрокоманд, выход регистра номеров остатков соединен с входом дешифратора остатков микрокоманд, выходы которого соединены с соответствующими управляющими входами коммутатора. Кроме того, блок контроля и суммирования содержит четьфе одноразряд ных сумматора, дешифратор и элемент ИЛИ, причем вход первого операнда блока соединен с входом первого операнда первого и второго одноразрядных сумматоров,выходы второго операн да блока соединены с входами второго операнда первого и второго одноразрядных сумматоров и входами первого операнда третьего и четвертого одноразрядных сумматоров, входы переноса первого, Третьего и четвертого одноразрядных сумматоров соединены с шиной нулевого потенциала, выход переноса первого одноразрядного сумматор соединен с входом переноса второго одноразрядного сумматора, выходы переноса второго, третьего и четвертого одноразрядных сзгмматоров соединен соответственно с входами второго опе ранда третьего и четвертого одноразрядных сумматоров и с входом элемечта Или, выход которогоявляется выходом неисправности блока, выходы . всех одноразрядных сумматоров соединены с. входами дешифратора и образуют выход результата суммирования блока, груптл выходов дешифратора соединены с группой входов элеме та ИЛИ. Сущность изобретения состоит в расширении области применения путем. организации условных и бузусловных . . переходов в микропрограммах,состоящи из микропрограмм, разрядность которых превышает разрядность линеек блока памяти без использования программных средств, а также организаци контроля правильности переходов в микропрограммах на основе проверки соответствия сформированного кода адреса очередной микрокоманды заданным требованиям. В блоке памяти микрокоманды располагаются поблочно. Каддый блок сос тоит из ()-й линейки (где к число полных линеек, занимаемых одной микрокомандой, т.е. к ln-t (, Е и г - разрядность микрокоманды и линейки блока .памяти соответственно), m- число полных остатков микрокоманд, .щенных в одной линейке, т.е. / Каждый блок микрокоманд имеет следующую структуру: в первой линейке блока располагаются остатки микроко манд, причем их размещение слева направо по 5 - 8-1(2 разрядов соответствует номеру микрокоманды в блоке, во второй - (к+1)-й линейках располагается целая часть первой микрокоманды блока, в (к+2)-й - (2к+1)-й - целая .часть второй микрокоманды и т.д. В C(m-1)K+2J ()-й линейках блока располагается целая часть fn-й микро- . команды. . Микрокоманды, размев1аемые в блоке памяти, содержат как операционную, так и адресную части, в том числе и поле кода логических условий. Каждый адрес состоит из двух частей: старшие разряды указывают номёр блока микрокоманд, к которому необходимо перейти, а младшие - задают номер первой линейки в блоке, в которой записана начальная часть очередной микрокоманды. В микрокомандах ветвления в поле кода логических условий задается номер проверяемого логического условия. При ветвлении происходит модификация только младших разрядов адреса, т.е. микрокоманды, следующие за ветвлением, размещаются в одном блоке. Функция . . модификации определяется внутренней структурой блока контроля и суммирования. В рассмотренном ниже примере конкретного вьшолнения этого узла модификация младших разрядов осуществляется только при единичном значении проверяемого условия путем суммирования их с константой, равной к. При таком варианте модификации микрокоманды, следующие за ветвлением, располагаются в соседних группах ли- неек блока, состоящих из к линеек. Считывание микрокоманд осуществляется за (к+1) такт. Сначала считывается линейка остатков (при зтом шaдщиe разряды адреса маскируются), а затем последовательно считьшаются части микрокоманд, хранящиеся в линейках с рк +2)-и по (i+1) (к+1)1-ю (, m-l); Принцип контроля, реализованный предлагаемом устройстве, основан на том положении, что при ветвлении не может быть сформирован адрес, при котором осзпдествляется переход к дру гому блоку микрокоманд, т.е. если число, соответствующее младшим разрядам исполнительного адреса микрокоманды ветвления, превьшает величину п1(к-1)+2 - это означает, чТо произошел сбой или устойчивый отказ в адресных цепях устройства, включая и соответствующие ячейки блока памяти. Введение блока контроля и суммирования позволяет осуществлять модификацию адреса и проверять правильность функционирования адресных цепей устройства. Регистр номеров остатков и дешифратор остатков микрокоманд управляют выбором разрядов кода остатков соответствующих считьгеаемой микрокоманде, мультиплексор обеспечивает выбор значения логического условия в соответствии с кодом задаваемым в формате микрокоманды. Первый и второй триггеры управления управляют занесением информации в счетчик адреса и маскированием младших разрядов адреса. На фиг. 1 представлена функциональная схема микропрограммного ycтpoйcтвa,yпpaвлeнияv на фиг. 2 блок контроля и суммирования, на; фиг. 3 - пример размещения микрокоманд в блоке памяти. Схема микропрограммного устройств содержит блок 1 памяти микрокоманд, счетчик 2 адреса, счетчик 3 линеек микрокоманд, регистр 4 полных линеек микрокоманд, регистр 5 номеров остатков, регистр 6 остатков микрокоманд, блок 7 контроля и суммирования, мультиплексор 8, дешифратор 9 линеек микрокоманд дешифратор 10 ос татков микрокоманд, генератор 11 импульсов, (Триггер 12 пуска, первый триггер 13 управления, второй тригге 14 управления, коммутатор 1,5, шестой блок 16 элементов И, седьмой блок 17 элементов И, первый блок 18 элементов If, второй блок 19 элементов И, третий блок 20 элементов И, четвертый блок 21 элементов И, пятый блок 22 элементов И, восьмой блок 23 элементов И, второй блок 24.элементов ИЛИ, первый блок 25 элементов ИЛИ, второй элемент 26 И, третийэлемент 27 И, первьй элемент 28 И, пятый 29, шестой 30 и (к+4)-й 31 элементы И соот)зетственно, четвертый элемент 32 И, элемент 33 ИЛИ, одновибратор 34, первый элемент 35 задержки, второй элемент 36. задержки, вход 37 логических условий устройства, вход 38 кода операции устройства вход 39 пуска устройства, группу входов 40 микроопераций устройства, выход 40.1 микрооперации Конец работы, выход 41 ошибки устройства, выход 42 кода логических условий, выход 43 старших разрядов адресной части микрокоманд (адреса,блока, микрокоманд), выход 44 младших разрядов адресной части микрокоманд (адреса микрокоманды в блоке микрокоманд), выход 45 операционной части микрокоманд регистра 4, информационный выход 46 блока контроля и суммирования, выход 47 мультиплексора, выходы 48.1 - (48. к+2)-й дешифратора линеек микрокоманд, выходы 49.1 - 49т дещифратора остатков микрокоманд, первый 50.1 и второй 50.2 выходы генератора импульсов 11 соответственно, выход 51 блока элемента И. На фиг. 2 обозначено: первый 52.1 второй 52.2, третий 52.3 и четвертый 52.4 одноразрядные комбинационные сумматоры соответственно, дешифратор 53 адреса, блок 54 элементов ИЛИ. Блок 1 памяти микрокоманд предназначен для хранения мик:рокоманд. В микрокоманде поля расположены следующим образом: поле логических условий, адресная часть, разбитая на две части: адрес блока микрокоманд и адрес микрокоманды в блоке, микроопе- рационная часть. В первую линейку блока микрокоманд записываются части, (остатки)п1 длинных микрокоманд, каждая из которьк занимает к полных инеек. Таким образом, число линеек в блоке микрокоманд равно (). Приер размещения микрокоманд приведен на фиг. 4 для т 3, к 3. Счетчик 2 предназначен для записи и хранения адреса очередной линейки блока 1 памяти микрокоманд. Он имеет два информационных поля1) 1)2. Поле I) 2 предназначено для записи адреса микрокоманды в блоке (младших разрядов адреса), D1 - для за91писи адреса блока микрокоманд, т.е. адреса линейки с записанными в нее остатками микрокоманд. Счетчик 3 при меняется для управления 1считьгаания полных линеек микрокоманды, образую щих ее целую часть, регистр 4 - дпя хранения полных линеек считываемых микрокоманд, регистр 5 - для хранения адреса микрокоманды в блоке, регистр 6 - для записи и хранения остатков всех микрокоманд, входящих в данный блок микрокоманд, Пример выполнения схемы блока контооЛя и Суммирования 7 представлен на фиг. 2, Он необходим для изменения адреса микрокоманды в блоке когда на выходе 47 мультиплексора 8 появится единичный сигнал, соответствующий единичному значению логического условий. В этом случае к дан ному адресу микрокоманды прибавляетс константа, равная числу полных линеек микрокоманды. Микрокоманды, следующие после ветвленияj расположены рядом в одном блоке, т.е. у них отличаются только младшие разряды адреса Рассмотрим работу блока 7 на примере. Если на выходе 47 мультиплексора 8 появились I, to к младшим разрядам адреса микрокоманды прйба:вляется константй, равная к, т.е. чис ло полных линеек микрокоманды. Эта операция осуществляется с помощью сумматоров 52.1 - 52.4. Если после первой микрокоманды, к оторая является микрокомандой ветвления (фиг.З), должен быть осуществлен переход по: единичному значению логического условия, к младшим, разрядам адресной части этой микрокоманды 0100 необкодимо прибавить код 0011 (к 3). Тогда произойдет переход от первой микрокоманды к третьей, а не ко второй (переход ко второй осуществляется при нулевом значении логического, условия)-. Если на выходе четвертого суьшатора 52.4 появится единичный сигнал, это означает, что в устройстве произошла ошибка. Поскольку для записи младших разрядов адреса не- пользуется tnk + 1)-я комбинация двоичных символов, то это приводит к появлению,

-(tYl1c l)

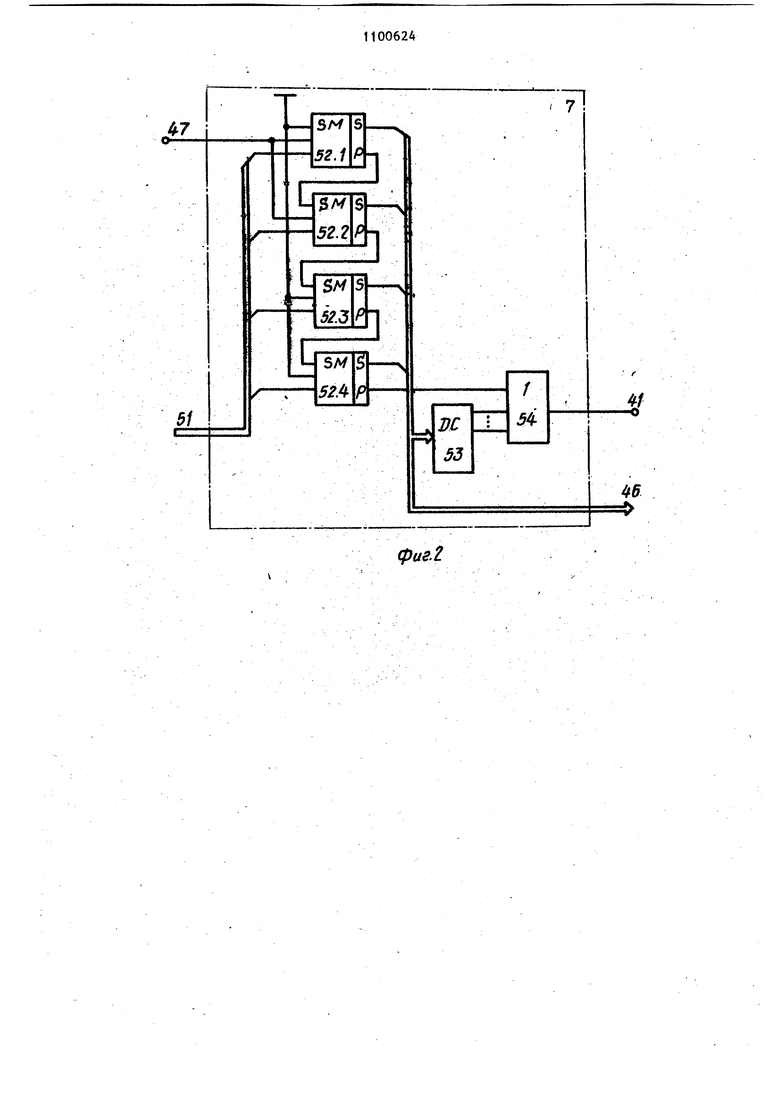

иэбыточньпс комбинаций. Таким обраэом, все наборы, для которых вьтолнйется 4 равенство Л О являются следствием ошибки. В данном случае m k + 1 10, следовательно появление на выходах сумматоров 52.1 - 52.4 двоичных кодов, соответствующих числам 11, 12, 13, 14, 15, свидетельствует об ошибке в работе устройства. Тогда дешифратор 53 имеет четыре входа и пять выходов, на которых дешифрируются кодовые комбинации 1011,1100, 1101, 1110 и 1111 соответственно. При их появлении на входе дешифратора 53 или появлении сигнала переполнения на выходе сумматора 52.4 формируется сигнал ошибки на выходе элемента Мультиплексор 8 предназначен для вьщеления значения логического условия, соответствующего заданному току, который поступает с выхода устройства. Мультиплексбр 8. вьтолняет следующую логическую функцию , ai,x-+a. У - + ac.xj+... где а, F,e- значение i-ro разряда кода проверяемого ло гического условия, х- ,,r - значение j-ro логического условия, поступающего от объекта J управления. Деш1 ратор 9 линеек .микрокоманды единичным сигналом на выходе 48.1 разрешает считывание первой линейки остатков блока микрокоманд, при появлении единицы на каждом следующем выходе, кроме 48к + 2, осуществляется последовательное считывание полных линеек микрокоманды. Дешифратор 10 остатков микрокоманды служит для выбора нужного остатка микрокоманды. Рассмотрим его работу на примере, приведенном на фиг. 4. Если считана вторая микрокоманда по адресу 0100, то из первой линейки необходимо выбрать второй остаток. Работу дешифратора можно описать слёдукнцей таблицей:

Генератор 11 предназначен для выдачи двух серий тактовых импульсов, триггер 12 - для разблокировки генератора по команде Пуск и блокировки его работы при появлении сигнала 5 Ошибка или Конец работы. Триггеры 13 и 14 осуществляют управление считыванием и формированием адреса. Кроме того триггер 13 осуществляет управление маскированием младших О разрядов адреса при считывании первой линейки блока микрокоманд. Элемент И 27 управляет синхронизацией записи адреса в счетчик 1 и регистр 5. Триггер 14 разрешает прохождение им- 5 пульсов на счетный вход счетчика 1 и считывание полных Линеек микрокоманды, а также управляет обнулением счетчика 3. Коммутатор 15 предназначен для управления считы- 20 ванием из регистров соответствующего остатка микрокоманды. Блоки элементов И 16 и И 17 осуществляют управление передачей младших разрядов адреса микрокоманды в счетчик 2, а блоки 5 элементов И 18 и И 22 управляют вьщачей сформировавшейся микрокоманды из регистров 4 и 6.

Блок элементов И 23 осуществляет маскирование младших разрядов микро- 30 команды, преобразуя полный адрес микрокоманды в адрес блока микрокоманд, т.е. в адрес первой линейки линейки остатков. Блок элементов И 24 предназначен для передачи на j информационный вход D 2 счетчика 2 младших разрядов исходного адреса, младших разрядов адреса следующей микрокоманды, либо преобразованный при ветвлении младших разрядов адре 40 са. Блок элементов ИЛИ 25 предназначен для передачи старших разрядов исходного адреса, либо адреса следущей микрокоманды.

Элемент И 28 обнуляет счетчик 3 45 о единичному сигналу с инверсного ыхода триггера 14 и тактовому имульсу генератора. Элементы И 29, 0 и 31 управляют считыванием полых линеек микрокоманд. Элемент И 32 JQ азрещает считывание первой линейки (линейки остатков) блока микрокоманд. Элемент ИЛИ 33 вьщает сигнал на обнуление триггера пуска 12 при подаче на него сигналов Ошибки или Конец работы. Одновибратор 34 служит для формирования сигнала Ошиб- , ка при появлении на выходе 41 еди- . ничного потенциала.

Элемент задержки 35 необходим для обеспечения надежной записи адреса в счетчик 2, причем его время задерж определяется вьфажением

SotA M S-irS-i4

где tj, - длительность синхроимпульса;

f-|- 2 - время задержки (переключения) триггера 13; т время задержки триггера 1 Элемент 36 задержки необходим для того, чтобы обеспечить надежную запись нового адреса, поступающего в счетчик 2. Отсутствие этого элемента может привести к тому, что при обнулении счетчика 3 снимается единица с выхода (48к +2) дешифратора 9, и адрес, не успевает записаться в счетчик 2 через блоки элементов И 19 и 20.

Устройство работает следующим образом.

В исходном состоянии все триггеры находятся в нулевом состоянии.

Вьпсоды установки в исходное состояние на чертеже условно не показаны. На вход 39 подается сигнал Пуск, триггер 12 разблокирует генератор 11 и первый синхроимпульс, проходя через элемент И 27, разрешает запись начального адрЪса с входа 38 через элементы ИЛИ 24 и ИЖ 23 в счетчик 2 и запись младших разрядов в регистр 5, Этим же импульсом триггер 13 переводится в единичное состояние. Сигнал с прямого выхода триггера 13 поступает на элемент И 23, обеспечивая тем самым маскирование младших раз рядов адреса. Следовательно, на вход блока 1 будет поступать адрес первой линейки блока микрокоманд -, линейки остатков. Этот же сигнал, пройдя.через элемент 35 задержки, переводит триггер 14 в единичное состояние. Сигнал с инверсного выхода триггера 14 блокирует элемент И 27, прекращая тем самым прохождение импульсов на вход синхронизации счетчика 2 и регистра 5.

Счетчик 3 в исходном состоянии . находится в нулевом состоянии, на выходе 48.1 дешифратора 9 присутствует единичный сигнал. По первому тактовому импульсу с выхода 50.2 генератора 11 открьгоается элемент И 32 и производится считьшание линейки остатков микрокоманд. По заднему фронту этого же импульса счетчик 3 переводится в следующее состояние, а на выходе 48.2 дешифратора 9 появляется единичный сигнал. Этим же импульсом обнуляется триггер 13, открывается блок элементов И 23 и демаскирует младпте адреса микрокоманды. По второму тактовому импульсу, поступающему с вькода 50.1 генератора 11. счетчик 2 изменяет адрес микрокоманды на единицу. При записи микрркоИанд в блок 1 памяти адресная часть дблжна быть на единицу меньще, чем реальный адрес. Например, если необ- : ходимо посчитать первую строчку пер вой микрокоманды первого блока микрокоманд (фиг. 4), то следует первона чально записать не код 0010001, а код. 0010000, так как в счётчик 2 прибавится недостающая единица и считывание начнется с линейки с адресом 0010001. По второму тактовому «мпульсу с выхода 50.2 генератор 11. происходит считывание первой полной строки микрокоманды, и она записывается в перг вое поле регистра 4. Следующий такто вый импульс с выхода 50.1 генератора 11, поступая на счетный вход счетчиKd 2, изменяет адрес на единицу. По очередному импульсу с-вькода 50.2 генератора 11 происходит считьтаниё второй полной строки микрокоманды. Этот процесс продолжается до тех пор пока все полные строки ьгакрокоманды не будут занесены в регистр 4. Ранее по первому тактовому импуяь су, поступившему с выхода 50,1 генератора 11, в регистр 5 записьгоаются младшие разряды адреса микрокоманды. Следовательно, йа соответствующем выходе дешифратора остатков 10 появится единичный сигнал. Когда по первому импульсу с выхода 50. геч- : нератора 11 разрешается счйтьгоайие . остатков в регистр 6, при помояр : коммутатора 15 вьщеляется необходим мый остаток По заднему фронту импуль который считал последнюю линейку микрокоманды, счетчик 3 переключился в такое положение, при котором появляется единица на выходе (48к+2) дешифратора 9 Эта единица разрешаг ет считывание всей микрокоманды на выход устройства. По этому же едянич нрму сигналу с выхода (48к+2) обнуляется триггер 14, тем саълм блокируется счетный вход счетчика 2 с по Moiiibio элемента И 26 и разблокируется вход синхронизации записи счетчика 2 с помощью элемента И 27. ЕСЛИ с вьпсода устройства была считана микрокоманда ветвления,,то на выходе мультиплексора 8 могла ВИТЬСЯ единица (если считана линейная команда, то на выходе мультиплексора всегда будет нуль). Если на выходе 47 мультиплексора 8 присутствует нуль, то блок элементов И 16 закрыт, а блок элементов И 1,8 открыт и младщие разряды адреса проходят на вход блока элементов ИЛИ 24. Если же на выходе 47 мультиплексора 8 появляется единица, то блок элементов И 17 закрывается, а блок элементов И 16 открывается, и младшие разряды адреса проходят с выхода 51 блока элементов И 16 на информационный вход блока контроля и суьошрования 7. С выхода 46 блока-контроля и суммирования 7 модифицированные млддшие разряды поступают на вход блока элементов ШШ 24. По очередному импульсу с выхода 50.1, поступающему через разблокированный элемент И 27 на вход синхрониэахщи записи счетчика 2, очередной адрес записывается в счетчик 2. Этим же импульсом счетчик 3 переводится в нулевое положе-г ние, и на выходе 48.1 дещифратора 9 появляется единичный сигнал. Далее устройство работает аналогичнопо описанному алгоритму. При появлении единичного сигнала на выходе 41 блока 7 одновибратор 34 вырабатывает импульс, который, проходя через элемент И 33, обнуляет триггер 12, происходит блоки ровка генератора 11. По окончании микропрограммы сигнал конца работы с выхода 40.1 поступает на вход элемента ИЛИ 33 и обнуляет триггер 12. . Применение предложенного изобретения позволяет стр1оить микропрограммные.. управлянщие устройства, область применения которых включает системы, использующие стандартные блоки памяти для хранения длинных микрокоманд, и к которым предъявляются повьш1енные требования по объему оборудования и достоверности функционирования.

cpu8.2

/rropu/UA

jaapjtffbi

/уоаря ы OOi

0000 000

IHK

0010 0011

0100

Zf K0101

OllfJ

out

Змк

woo

1001

0000

010

0001

/f4K .

0011 0100

0/10

0111

3Mf. /000

lOOf

1 2 3 I

Jfnof

г 3

JfSjTOK

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1984 |

|

SU1265776A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1310816A1 |

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, счетчик a tpeca, счетчик линеек микрокоманд, регистр линеек микрокоманд, регистр остатков микрокоманд , дешифратор линеек микрокоманд, коммутатор, триггер пуска, генератор ш пульсов, восемь блоков элементов И, первый и второй блоки элементов ИЛИ, (к+4) элемента И, где к - число полных линеек, занимаемых микрокомандой, первый и второй элементы задержки, одновибратор, причем вход пуска устройства соединен с единичным входомтриггера пуска, выход которого соединен с входом генератора импульсов, первый вьЕсод генератора импульсов соединен с первым входом первого эл ёмента И, выход которого соединен с входом первого элемента задержки, первая информационная группа выходов счетчика адресов соединена с входами старших разрядов группы информационных входов блока памяти микрокоманд, выходы которого соединены с группой информационных входов регистра остат.ков микрокоманд, выходы с первого по к-й группы выходов блока памяти микрокоманд соединены с соответствующими информационными входами регистрй полных линеек микрокоманд, первый, второй, третий и четвертый вьЬсоды группы выходов которого соединены с первыми входами соответственно первого, второго, третьего и четвертого блоков элементов И, первые ю выходов регистра остатков микрокоманд, где 1Т1- число полных остатков микрокоманд, размещаемых в одной линейке, соединены соответственно с первыми т информационными входами коммутатора выход которого соединен с первым ; входом пятого блока элементов И, выходы четвертого и пятого блоков (Л элементов И соединены с соответствующими выходами группы выходов микроопераций устройства, выход счетчика линеек микрокоманд соединен с входом § дешифратора линеек микрокоманд, о тличающееся тем, что, с целью расширения области применения, .в устройство введены блок контроля - о и суммирования, регистр номеров остато ков, дешифратор остатков микрокоманд, 35 SD 4 мультиплексор, первый и второй триггеры управления, причем-вход логических условий устройства и выход первого блока элементов И соединены соответственно с информационным и адресным входами мультиплексора, выход которого соединен с входом первого операнда блока контроля и суммирования, первым входом шестого бло ка элементов И и инверсным входом седьмого блока элементов И, выход iBTOporo блока элементов И соединен с первым входом первого блока элементов ИЛИ, выход которого соединен с

NS/rof

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1980 |

|

SU928356A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-06-30—Публикация

1983-03-29—Подача