N{;

со со

4:

00

со

314

Изобретение относится к импульсно и информационно-измерительной технике и может быть использовано в различной микропроцессорной радиоэлектронной аппаратуре.

Целью изобретения является расши рение диапазона формируемых временных интервалов при обеспечении заданной точности (дискретности) фор- мирования.

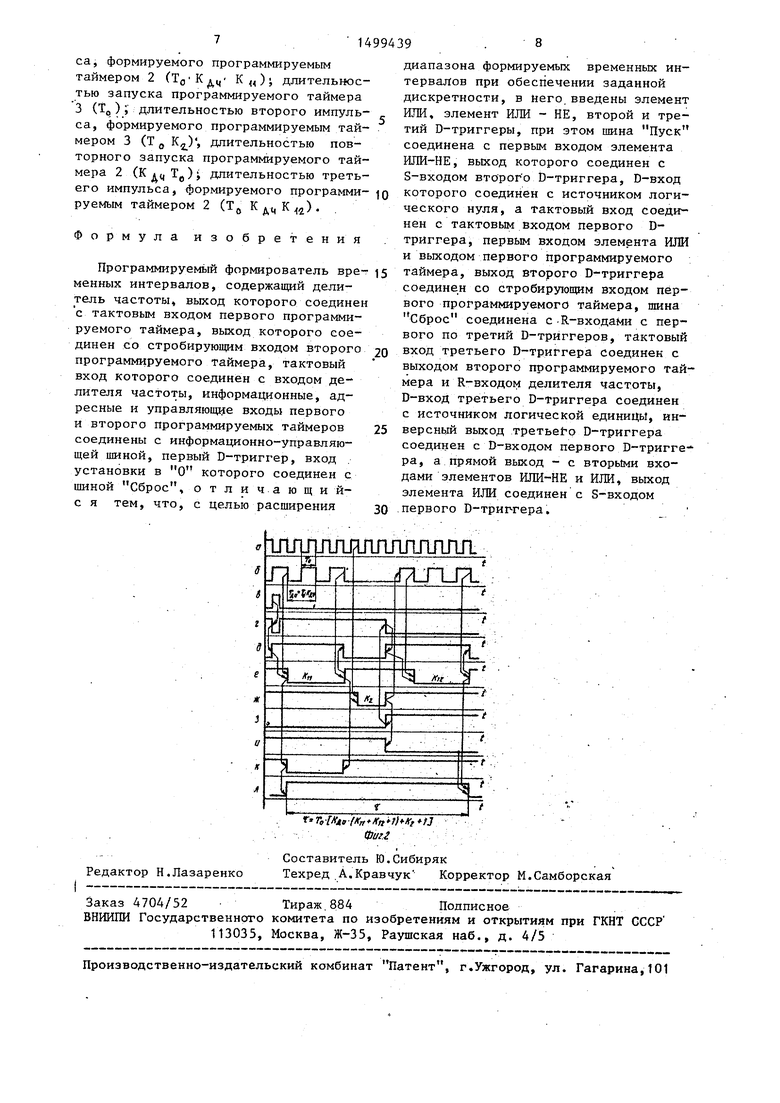

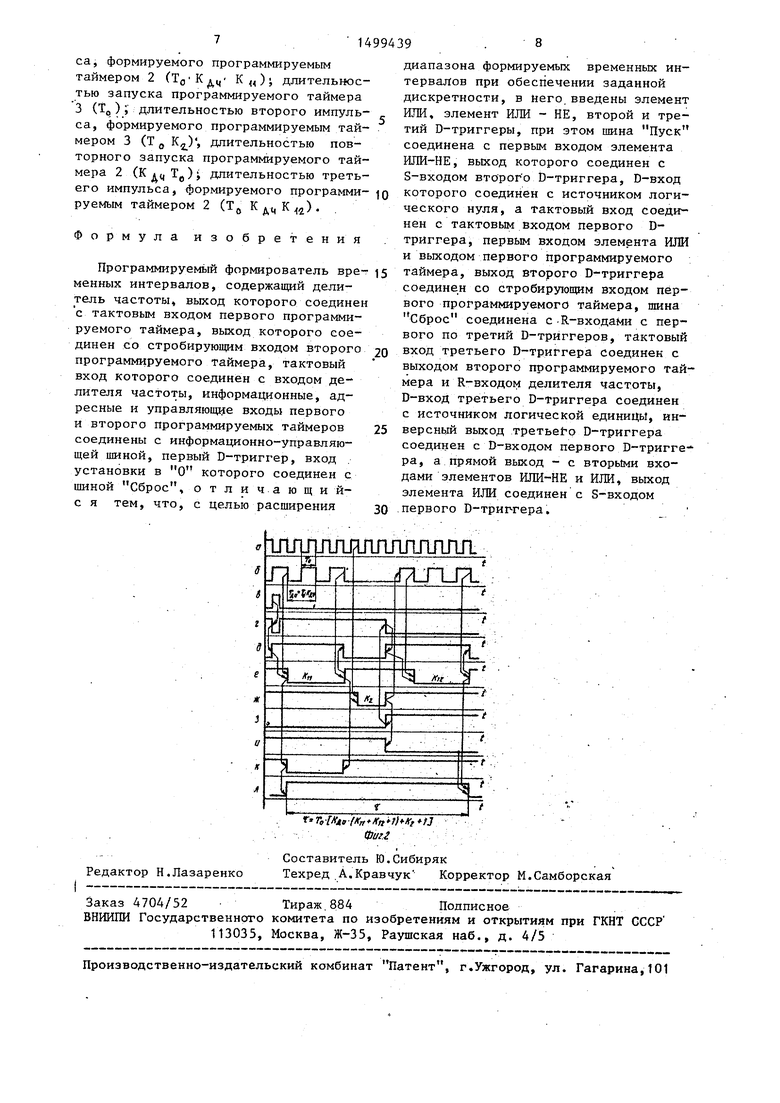

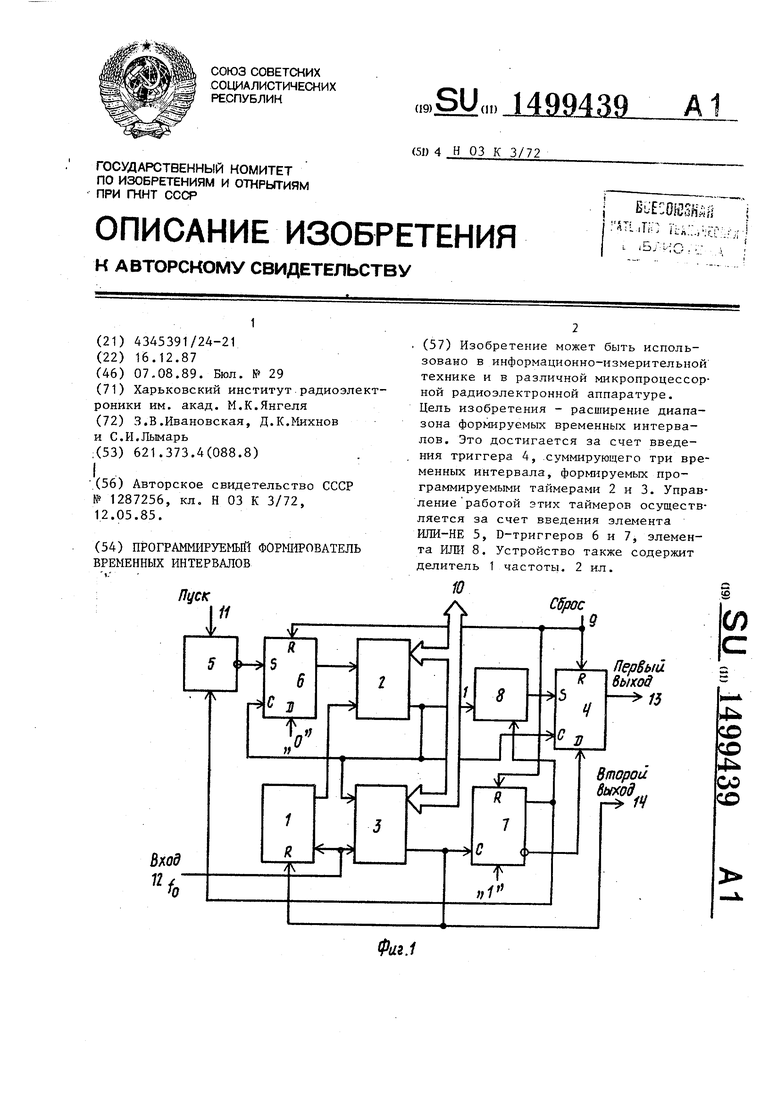

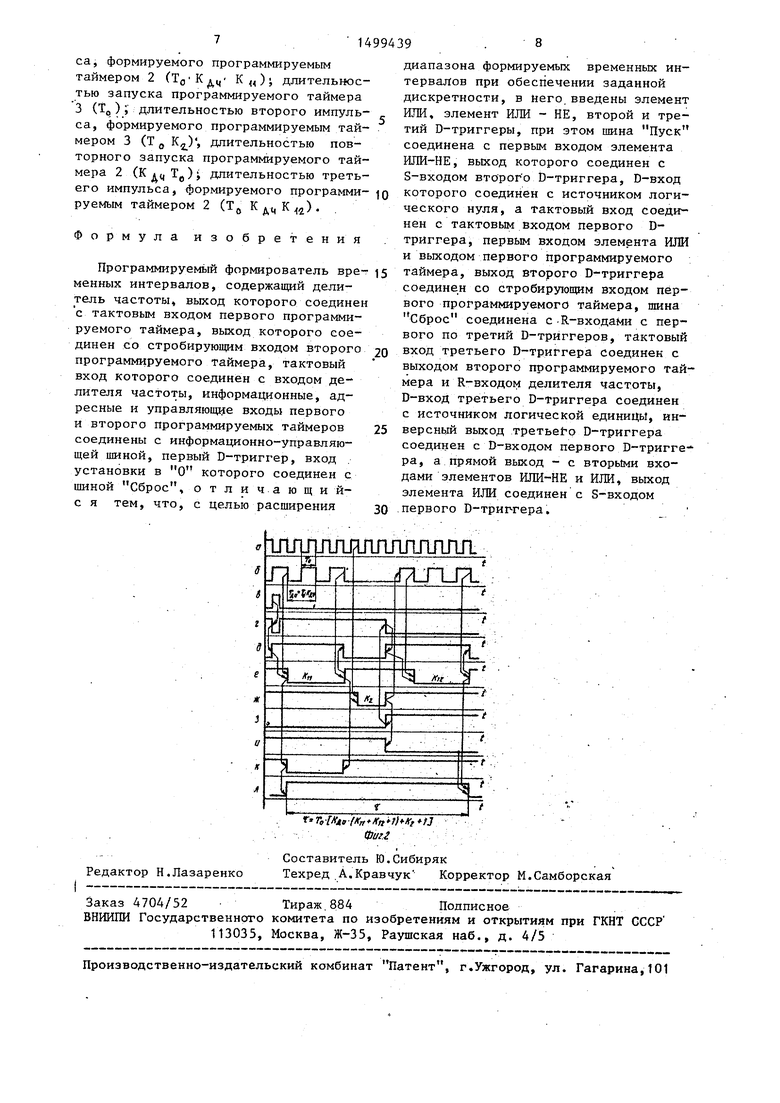

На фиг. 1 представлена функциональная схема программируемого формирователя временных интервалов; на фиг. 2 - временные диаграммы, пояс- няющие его работу.

Программируемый формирователь временных интервалов содержит делитель 1 частоты, программируемые таймеры 2 и 3, D-триггер 4, элемент ИЛИ-НЕ 5, D-триггеры 6 .и 7. элемент ИЛИ 8, шин 9 Сброс, информационно-управляющую шину 10, шину 11 Пуск, входную шину 12 импульсной последовательности, выходы 13 и 14.

Входная шина 12 импульсной последовательности соединена с тактовым входом программируемого таймера 3 и входом делителя 1 частоты, выход которого соединен с тактовым входом программируемого таймера 2. Шина 9 Сброс соединена с R-входами D-триг геров 4, 6, 7. ЧЧина 11 Пуск соединена с первым входом элемента ШИ-. НЕ 5, выход которого соединен со стробирующим входом программируемого таймера 2. выход которого соединен с тактовым входом D-триггера 6, стробирующим входом программируемого таймера 3, первым входом элемента ИЛИ 8 и тактопым входом D-триггера 4, выход которого является выходом 13 устройства, D-триггера 4 соединен с выходом элемента ИЛИ 8, а D- вход - с инверсным выходом D-тригге- pa 7. Прямой вькод D-триггера 7 соеднен с вторым входом элемента ИЛИ 8 и вторым входом элемента ИЛИ-НЕ 5, а тактовый вход - с выходом программи- .руемого таймера 3, R-входрм делителя

1частоты и выходом 14 устройства. Информационные, адресные и управляющие программируемых таймеров

2и 3 соединены с информационно-управляющей шиной 10 №1кропроцессОрной системы. На D-вход D-триггера 6 пода уровень логического нуля, на D-вход D-триггера 7 - уровень логической единицы.

ношения

Формирователь работает следующим образом.

В исходном состоянии D-триггеры 4, 6 и 7 сброшены кра тковременным импульсом по шине 9 Сброс и на их прп прямых выходах устанавливается уровень логического нуля, а на инверсном выходе О-триггера 7 - уровень логической единицы. Делитель 1 частоты находится в режиме счета импульсов частоты внешнего генератора. Программируемые таймеры 2 и 3 запрограммированы по информационным, адр еснмм и управляющим шинам 10 микропроцессорной системы дпя работы в режиме од- новибрафора, при этом вводимые в них коэффициенты К„ , и К. определяющие длительность выходного импульса устройства, определяются из соот

(К+ К

г

1) +

(1)

где

0 0 ,c t

Тл А4

0

5

длительность формируемого временного интервала , период частоты внешнего генератора импульсовi коэф(1)ициент деления делителя 1 частоты/

К, ,. числа,заносимые в счетчик программируемого таймера 2 для формирования первого и третьего импульсов устройства

К число, заносимое в счетчик программируемого таймера 3 для формирования второго импульса устройства.

При этом возможны два варианта программирования программируемого таймера 2,

При первом значение коэффициента, занесенного в счетчик таймера, не изменяется в процессе работы устройства, а при втором в счетчик таймера первоначально заносится коэффициент K. , а затем в процессе формирования второго импульса устройства К заменяется (программируется) на К . Микропроцессорная система получает сигнал о готовности формирователя к приему коэффициента Kj с выхода 14 устройства. Если в процессе работы программируемого таймерй 3 перепрограммирование программируемого таймеpa 2 не выполняется, то К К

К

выражение (1) принимает вид

То(Кд,

(2К + 1) + К, + 1).(2)

Работа устройства начинается по приходу по шине 11 Пуск рабочего (положительного) фронта импульса на первый вход элемента ИЛИ-НЕ 5 (фиг. 2в), Отрицательный перепад с выхода элемента ИЛИ-НЕ 5 (фиг.2г) переводит по S-ВХОДУ Р-триггер 6 в единичное состояние (фиг. 2д), в результате чего на стробиругащем входе программируемого таймера 2 устанавливается высокий логический уровень. В момент прихода первого рабочего (отрицательного) фронта импульса с выхода делителя 1 частоты (фиг. 26) на тактовый вход программируемого таймера 2 на его выходе устанавливается низкий логический уровень (фиг. 2е), который поступает на первый вход элемента ИЛИ 8. Поскольку и на второй вход элемента ИЛИ 8 подан низкий логический уровень с прямого выхода D- триггера 7 (фиг. 2д), то на выходе элемента ИЛИ 8 установится уровень логического нуля (фиг. 2к), который переводит D-триггер 4 в единичное состояние по S-БХОДУ (фиг. 2л). По окончании формирования первого импульса на выходе программируемого таймера 2 устанавливается высокий логический уровень и положительным перепадом, поступающим на стробирую- дий вход программируемого таймера 3, разрешается формирование второго од

99-439

таймер 2 незадействован, становится

)

10

20возможным его перепрограммирование микропроцессор ;ой системой (при необходимости) , т.е. замена коэффициента К , на коэффициент К ,, . С этой целью выход 14 устройства можат подключаться к входам запроса прерывания микропроцессорной системы.

Во время формирования второго импульса на выходе программируемого таймера 3 устанявл 1вается низкий логический уровень., который подается на R-вход делителя 1 частоты и уста- 15 навливает его в исходное (нулевое) состояние (фиг. 25). Таким образом, при повторном запуске программируемого таймера 2 (начало формирования третьего импульса) длительность задержки его включения является величиной постоянной и равной периоду следования импульсов с выхода делителя 1 частоты (фиг. 2е).

По окончании второго импульса по- 25 ложительным перепадом с выхода программируемого таймера 3 в D-триггер 7 по С-входу записывается логическая единица, которая устанавливается на прямом выходе D-триггера 7 (фиг. 2з), а на инверсном его выходе - уровень логического нуля (фиг. 2и). С прямого выхода D-триггера 7 уровень логической единицы заводится на второй вход элемента ИЛИ-НЕ 5, на выходе которого вновь устанавливается уровень логического нуля (фиг. 2г), в результате чего D-триггер 6 повторно пере-. ходит в единичное состояние по S-вхо- ДУ (фиг. 2д). Далее повторяется цикл

30

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый формирователь временных интервалов | 1985 |

|

SU1287256A1 |

| МИКРОПРОЦЕССОРНЫЙ ЭЛЕКТРОПРИВОД | 1998 |

|

RU2141164C1 |

| Устройство для формирования временных интервалов | 1988 |

|

SU1584090A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1575295A1 |

| Устройство для формирования временных интервалов | 1989 |

|

SU1691936A2 |

| Устройство для измерения частоты и периода гармонического сигнала | 1991 |

|

SU1797714A3 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Программируемый формирователь периодических сигналов | 1990 |

|

SU1746513A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2003 |

|

RU2248089C1 |

Изобретение может быть использовано в информационно- измерительной технике и в различной микропроцессорной радиоэлектронной аппаратуре. Цель изобретения - расширение диапазона формируемых временных интервалов. Это достигается за счет введения триггера 4, суммирующего три временных интервала, формируемых программируемыми таймерами 2 и 3. Управление работой этих таймеров осуществляется за счет введения элемента ИЛИ-НЕ 5, Д-триггеров 6 и 7, элемента ИЛИ 8. Устройство также содержит делитель 1 частоты. 2 ил.

нократного импульса устройства. Кроме 40 Работы програм№1руемого таймера 2, того, на выходе элемента ИЛИ 8 уста- на выходе которого формируется третий

импульс устройства (фиг. 2е), причем передний фронт формируемого импульса

навливается уровень логической единицы, который поступает на S-вход D- триггера 4 и разрешит работу триггера

задерживается относительно заднего

по С-входу. Формирование второго им- 5 импульса, сформированного пульса устройства начинается по при- программируемым таймером 3, на велиК

ходу на тактовый вход программируемого таймера 3 по входной шине 12 рабочего (отрицательного) фронта импульса частоты внешнего генератора, при, этом передний фронт формируемого импульса задерживается относительно заднего фронта импульса, сформированного програг-1мируемым таймером 2, на величину Тд, которая входит в общую длительность получаемого временного интервала (фиг. 2ж).

Поскольку за время работы программируемого таймера 3 программируемый

50

55

чину Тд Кд(, которая входит в общую длительность получаемого временного интервала. По окончании третьего импульса положительным перепадом с выхода программируемого таймера 2 в D-триггер 4 заносится логический ноль с С-входа. Таким образом, на вы ходе D-триггера 4 (выход 13 устройства) формируется временной интервал длительностью с в- соответствии с выражением (1) и (2) (фиг. 2л) как сумма временных интервалов, опреде- ляемых: длительностью первого импуль

задерживается относительно заднего

К

0

5

чину Тд Кд(, которая входит в общую длительность получаемого временного интервала. По окончании третьего импульса положительным перепадом с выхода программируемого таймера 2 в D-триггер 4 заносится логический ноль с С-входа. Таким образом, на выходе D-триггера 4 (выход 13 устройства) формируется временной интервал длительностью с в- соответствии с выражением (1) и (2) (фиг. 2л) как сумма временных интервалов, опреде- ляемых: длительностью первого импульУШШЛЛПЛППЛ.

Редактор Н.Лазаренко

f Teii t,(()3

Фи.1

Составитель Ю.Сибиряк

Техред А.Кравчук Корректор М.Самборская

гП-ГШ-.

| Программируемый формирователь временных интервалов | 1985 |

|

SU1287256A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-16—Подача