1

Изобретение относится к импульс- , ной технике и может использоваться в автоматике5 вычислительной технике, контрольно-испытдтельных системах.

Цель изобретения - повышение быс- тродействия и распшрение функциональных возможностей за счет обеспечения программируемого изменения временных параметров формируемых импульсов в каждом канале,

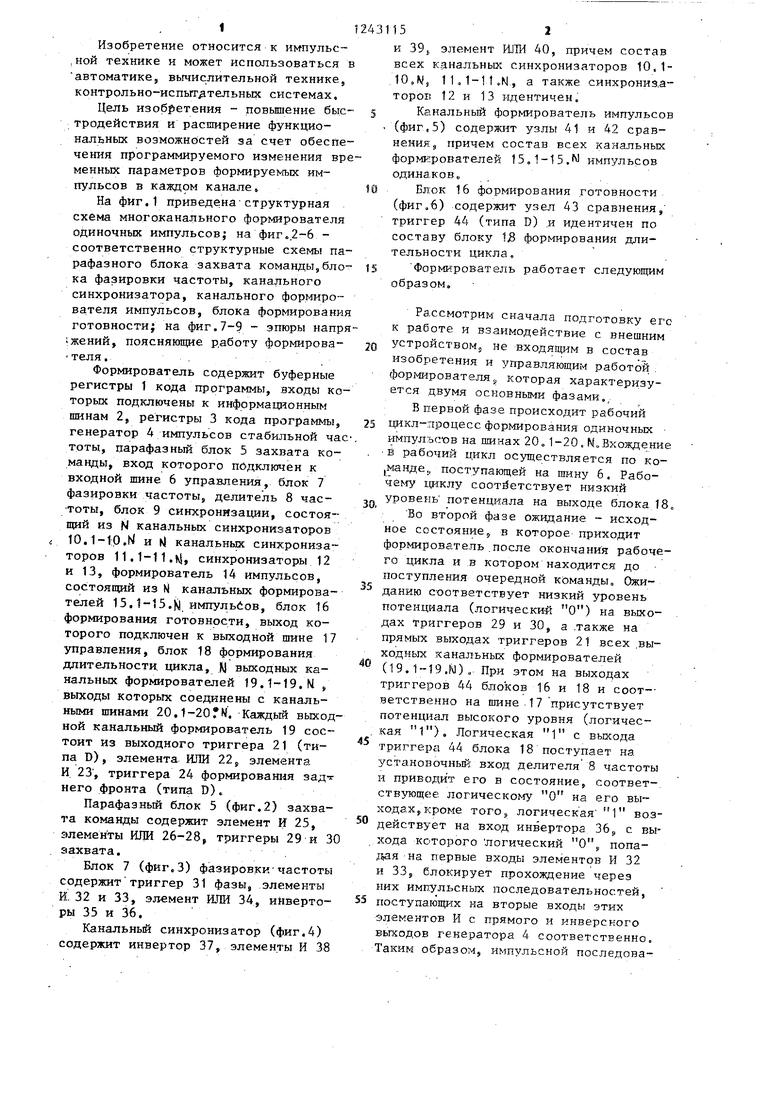

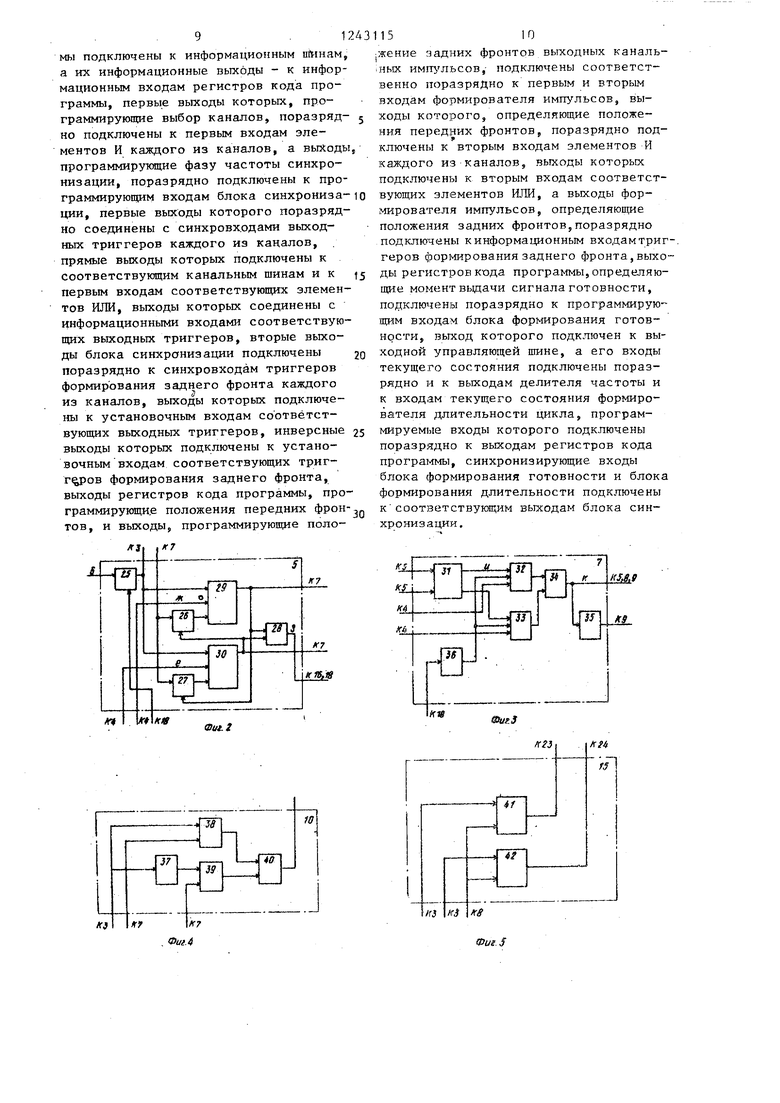

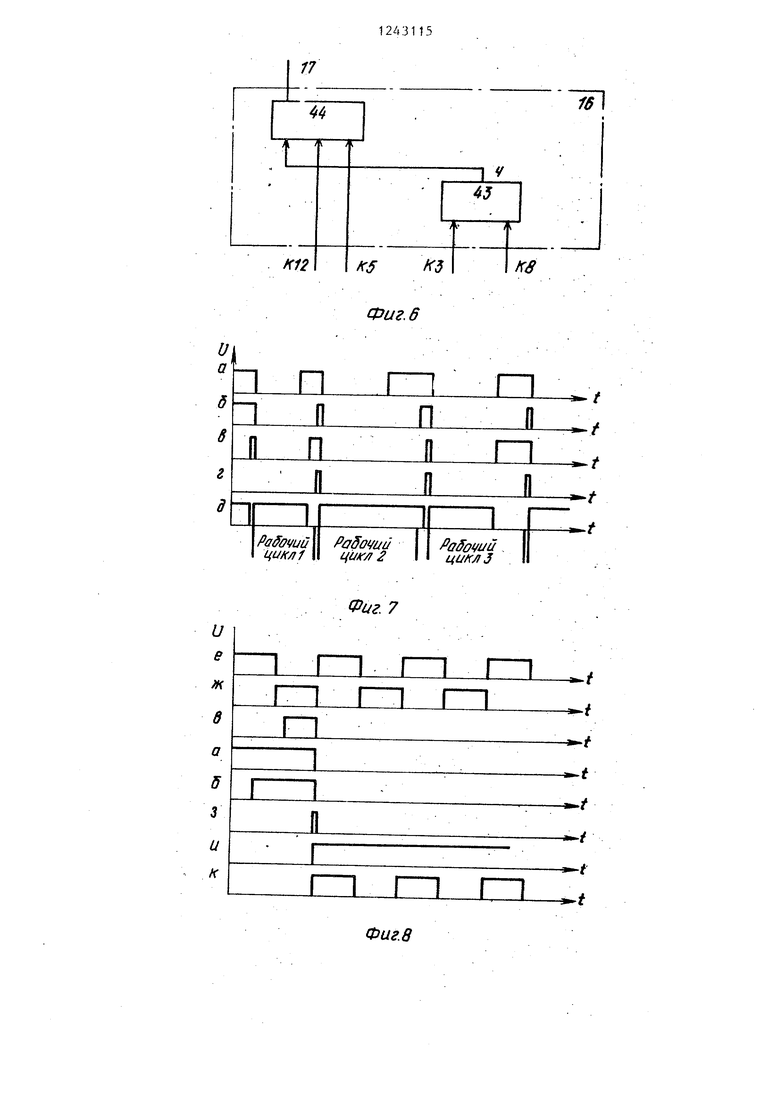

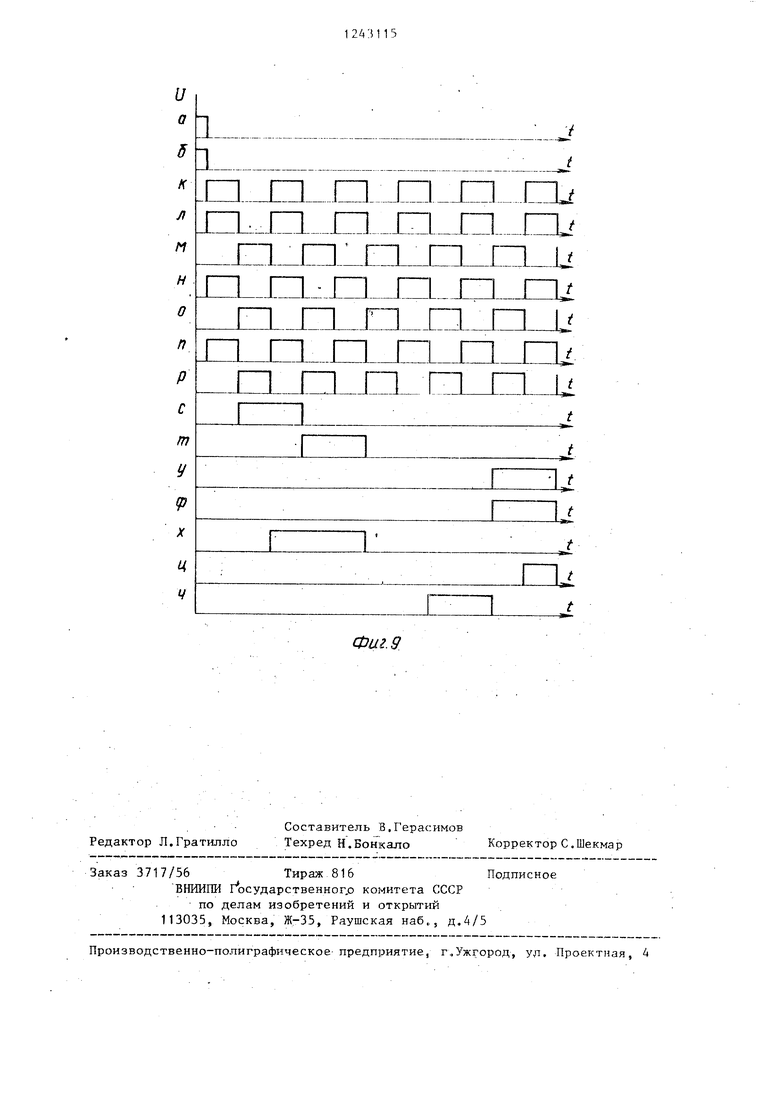

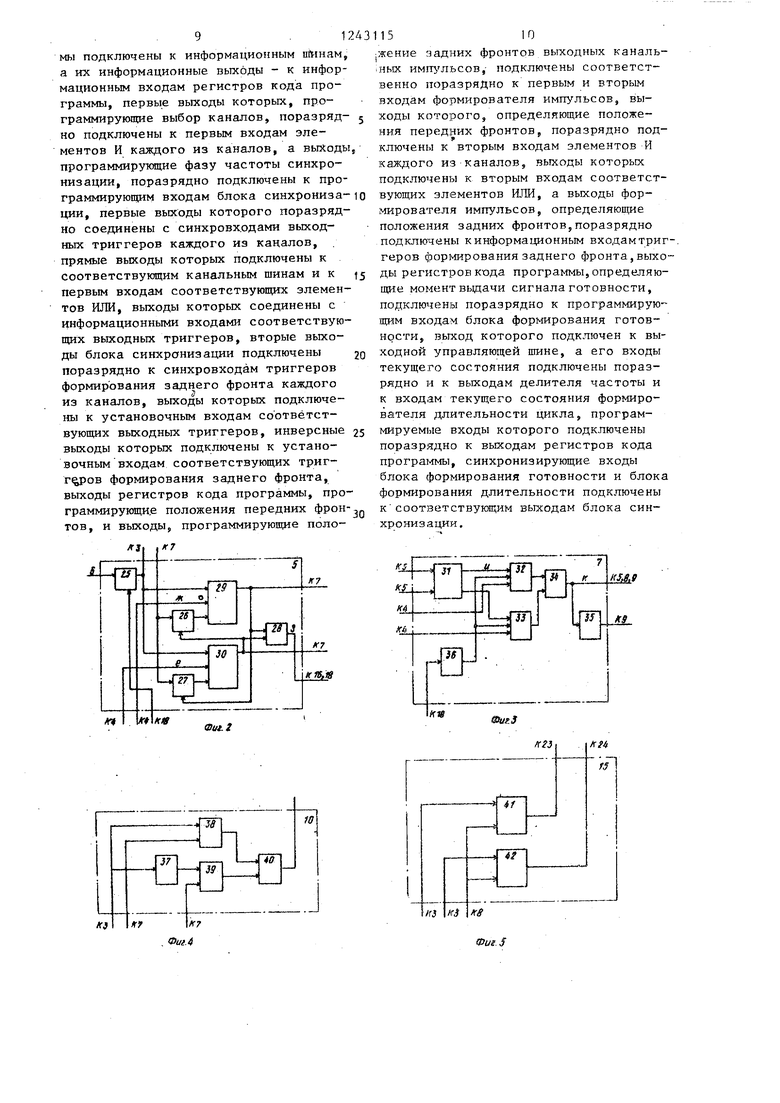

На фиг.1 приведена-структурная схема многоканального формирователя одиночных импульсов,- на фиг..2-6 - соответственно структурные схемы па- рафазного блока захвата командыябло- ка фазировки частоты, канального синхронизатора, канального формирователя импульсов, блока формирования ГОТОВНОСТИ на фиг. 7-9 - эпюры напря :жений, поясняющие работу формирова- теля, .

Формирователь содержит буферные регистры 1 кода программы, входы которых подключены к информационным шинам 2, регистры 3 кода программы, генератор 4 импульсов стабильной час тоты, парафазный блок 5 захвата команды, вход которого подключен к входной шине 6 управления, блок 7 фазировки частоты, делитель 8 час- тоты, блок 9 синхронизации, состоящий из М канальных синхронизаторов 10,1-1:0,h/ и М канальных синхронизаторов 11,1-11,к|, синхронизаторы 12 и 13, формирователь 14 импульсов, сос;тоящий из Ч канальных формирователей 15,1-15,j импульбов, блок 16 формирования готовности, выход которого подключен к выходной шине 17 управления, блок 18 формирования длительности, цикла, М выходных канальных формирователей 19,1-19, М , выходы которых соединены с канальными шинами 20,1-20fW, Каждый вьгеод- ной канальный формирователь 19 состоит из выходного триггера 21 (типа D), элемента ИЖ 22, элемента И 23, триггера 24 формирования задт него фронта (типа D).

Парафазный блок 5 (фиг,2) захвата команды содержит элемент И 25, элементы ИЛИ 26-28, триггеры 29 и 30 захвата.

Блок 7 (фиг.З) фазировки-частоты содержит триггер 31 фазы, элементы И. 32 и 33, элемент ИЛИ 34, ийверто- ры 35 и 36,

Канальньй синхронизатор (фиг.4) содерзкит инвертор 37, элементы И 38

§ 10

ts -- 20

25-, jg

55

35

40

45

152

и 39J, элемент ИЛИ 40, причем состав всех канальньос синхронизаторов 10,1- .10.MS ri,1-1t.M,, а также синхрониз.а- Topoi 12 и 13 идентичен.

Какальньй формирователь импульсов (фиг,5) содержит узлы 41 и 42 сравнения: причем состав всех канальных формр рователей 15,1-15. импульсов одинаков .

Блок 16 формирования готовности (фиг,6) содер:жит узел 43 сравнения, триггер 44 (типа D) .и идентичен по составу блоку 1j8 формирования длительности цикла,

Форми рователь работает следующим образом.

Рассмотрим сначала подготовку его к работе и взаимодействие с внешним устройством не входящим в состав изобретения и управляющим работой . формирователя, которая характеризуется двумя основными фазами,,

В первой фазе происходит рабочий цикл-:г1роцесс формирования одиночных : мпул;ьспв на шинах 20.1-20. N. Вхождение В рабочий цикл осуществляется по ко- манде., поступающей на шину 6. Рабо- чеьгу 1 }гкпу соответствует низкий уровень потенциала на выходе блока 18.

Во второй фазе ожидание - исходное состояние, в которое приходит формирователь .после окончания рабочего цикла и в котором находится до поступления очередной команды. Ожиданию соответствует низкий уровень потенциала (логический О) на выходах тр:нггеров 29 и 30, а .также на прямых выходах триггеров 21 всех .выходных канальных формирователей (19,1-19,10), При этом на выходах триггеров 44 блоков 16 и 18 и соот-- ветственно на шине . 17 присутствует потенциал высокого уровня (логичес- :кая 1), Логическая 1 с выхода триггера 44 блока 18 поступает на установочный вход делителя 8 частоты н приводит его в состояние, соответ-. ствующее логическому О на его выходах, кроме TorOj логическая 1 воздействует на вход инвертора, 36,, с выхода которого логический 0 попадая на первые входы элементов И 32 и 33, блокирует прохождение через них имп:ульсных последовательностей, поступающ1 х на вторые входы этих элементов И с прямого и инверсного выходов генератора 4 соответственно. Таким образом, импульсной последова3

тельности, т.е. тактовой частоты, нет на счетном входе делителя 8 частоты и на тактовых входах блока 9 синхронизации - первых входах элементов И 38 и первых входах элемен- тов И 39, а также на первых входах элементов 26 и 27 блока 5.

Логическая 1 с выхода триггера 44 также поступает на первый вход элемента И 25 к создает условия для прохождения через него команды, когда она поступит на второй вход элемента И 25 с шины 6. Наличию команды соответствует потенциал высокого уровня. В течение рабочего цикла в регистрах 3 хранится код программы, который задает на время данного рабочего цикла значения изменяемых параметров формирователя, которые определяют:

1.Комбинацию тех каналов из общего числа N, которые должны сформировать одиночные импульсы в данном рабочем цикле. Этот параметр задается кодом на выходах регистров 3, программирующих выбор каналов.

2.Фронты (передний или задний) импульсов тактовой частоты, которыми определяются моменты переключения выходных триггеров 21, формирую- щих импульсы на выходе каждого из каналов. Этот параметр задается кодом на выходах регистров 3, программирующих фазу частоты синхронизации.

3.Положение передних фронтов импульсов на выходе каждого из каналов относительно момента начала рабочего цикла и в пределах данного рабочего цикла. Этот параметр задается кодом

на выходах регистров 3, программирующих положение передних фронтов.

4„ Положение задних фронтов импульсов на выходе каждого из каналов относитепьно момента начала рабочего цикла. Этот параметр задается кодом на- выходах регистров 3, программирующих положение задних фронтов. Причем программирование положения заднего фронта допускает возможность формирования импульсов 5 длительность-ко- торык охватывает несколько рабочих циклов,

5, Момент появления сигнала Готовность (логическая 1) на шине 1 относительно начала рабочего цикла, Сигнал Готовность разрешает внешнему устройству выдачу очередной команды и информирует его об окончании

1154

процессов, которые инициируются импульсами с выходов формирователя. Этот параметр задается кодом на выходах программирующих момент выдачи готовности. Пропадание сигнала Го-. тоЕНость (лог ический О) свидетельствует о том, что команда принята формирователем.

6. Длительность рабочего цикла, момент окончания которого свидетельствует о готовности формирователя к приему очередной команды. Этот параметр задается выходом регистров 3 программирующим длительность цикла.

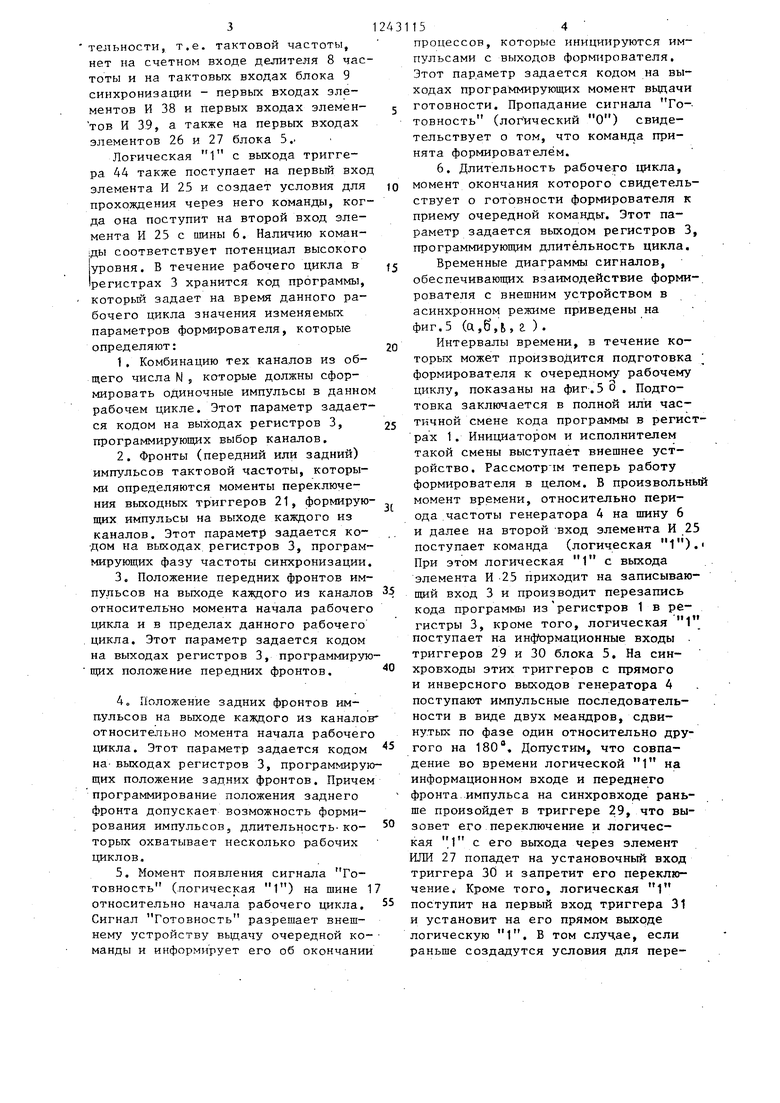

Временные диаграммы сигнапов, обеспечивающих взаимодействие формирователя с внешним устройством в асинхронном режиме приведены на фиг.5 (а,б,Ь г ) .

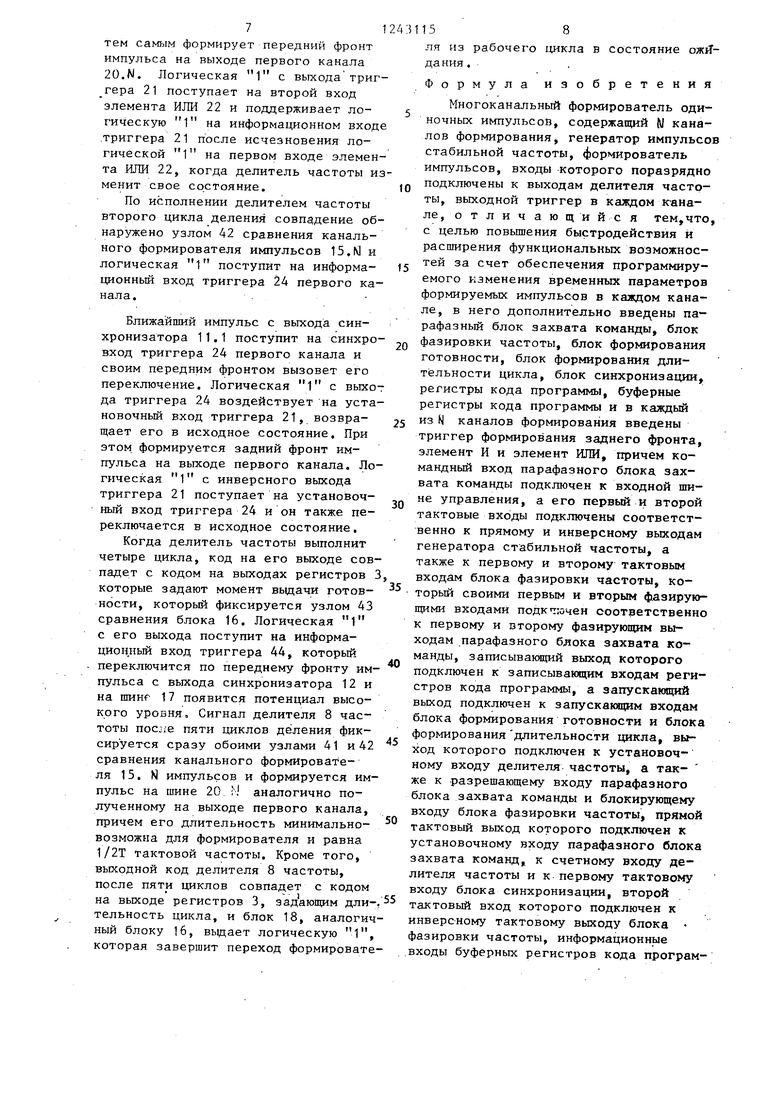

Интервалы времени, в течение которых может производится подготовка формирователя к очередному рабочему циклу, показаны на фиг.5 о . Подготовка заключается в полной или частичной смене кода программы в регистрах 1. Инициатором и исполнителем такой смены выступает внешнее устройство. Рассмотрим теперь работу формирователя в целом. В произвольны момент времени, относительно периода частоты генератора 4 на шину 6 и далее на второй -вход элемента И 25 поступает команда (логическая 1). При этом логическая 1 с выхода элемента И 25 приходит на записывающий вход 3 и производит перезапись кода программы из регистров 1 в регистры 3, кроме того, логическая 1 поступает на инф ормационные входы . триггеров 29 и 30 блока 5, На син- хровходы этих триггеров с прямого и инверсного выходов генератора А поступают импульсные последовательности в виде двух меандров, сдвинутых по фазе один относительно другого на 180, Допустим, что совпадение во времени логической 1 на информационном входе и переднего фронта импульса на синхровходе раньше произойдет в триггере 29, что вызовет его переключение и логическая .1 с его выхода через элемент ИЛИ 27 попадет на установочный вход триггера 30 и запретит его переключение. Кроме того, логическая 1 поступит на первый вход триггера 31 и установит на его прямом выходе логическую 1. В том случае, если раньше создадутся условия для переключения на входах триггера 30, то логическая 1 с его выхода запретит переключение триггера 29 и установит логическую 1 на инверсном выходе триггера 31, Таким образом происходит захват команды и запоминание фазы частоты в момент захвата Логическая 1 с выхода одного из триг,геров 29 и 30 через элемент ИЛИ 28 поступит на установочный вход триггера 44 блока 16 и аналогичньш триггер блока 18 и вызовет изменение уровня сигналов на их выходах, что соответствует снятию сигнала Готовность с шины 17 и началу рабочего цикла формирователи. С появлением логического О на выходе блока 18 снимается сигнал сброса с делителя 8 частоты, блокируется командный вход блока 5 логическим О на первом входе элемента .И 25 и устанавливается разрешающий потенциал (логическая 1) на первых входах элементов И 32 и 33, один из них в зависимости от состояния триггера 31, связанного с вторьеда входами элементов И 32 и 33, пропускает на свой выход импульсную последовательность, по- ступаклцую на ее третий вход с соответствующего выхода гене ратора 4, Таким образом происходит фазировка тактовьрс частот на прямом и инверсном выходах блока 7, которые синхронизируют работу других блоков формирователя.. Первый импульс с прямого выхода блока 7 через элементы ИЛИ 26 и 27 поступает на установочные входы триггеров 29 и 30 и возвращает один из них в исходное состояние (логический О на выходе). Работа блоков 5 и 7 иллюстрируется временными диаграммами на фиг.6,. .

Импульсы тактовой частоты с прямого выхода блока 7 и импульсная последовательность, сдвинутая относительно нее по фазе на 180 (сдвинутая тактовая частота), с инверсного выхода блока 7 поступают соответственно на. первый и второй тактовые входы блока 9 и далее на соответствующие первые входы элементов И 38 и 39 синхронизаторов 10,1-10.W, 11.4-11,М, 12 и 13. На вторые входы элементов 38 и через инверторы 37 на вторые входы элементов 38, и через инверторы 37 на вторые входы элементов 39 поступает программирующая информация с соответ5 0 0 5

5

5

0

ствующих выходов блока 3, которая обеспечивает прохождение в зависимости от конкретного кода программы тактовой частоты на выходы элементов И 38 или сдвинутой тактовой частоты на выходе элементов И 39, Таким образ ом, формируется набор определенных -импульсных последовательностей;, которые с выходов синхронизаторов 10,1-10.М поразрядно распределяются по синхровходам триггеров 21 соответствующих каналов. Положения передних фронтов импульсов этих последовательностей определяют возможные моменты переключения этих триггеров при формировании передних фронтов импульсов на выходах каналов.

Аналогичную задачу выполняют синхронизаторы 11.1-11,, выходы которых, воздействуя на сипхровходы триггеров 21 каждого из каналов, определяют возможные положения задних фронтов импульсов на выходах каналов, Выходы синхронизаторов 12 и 13 оп-. ределяют возможные моменты появления сигнала Готовность (шина 17) и окончания рабочего цикла.

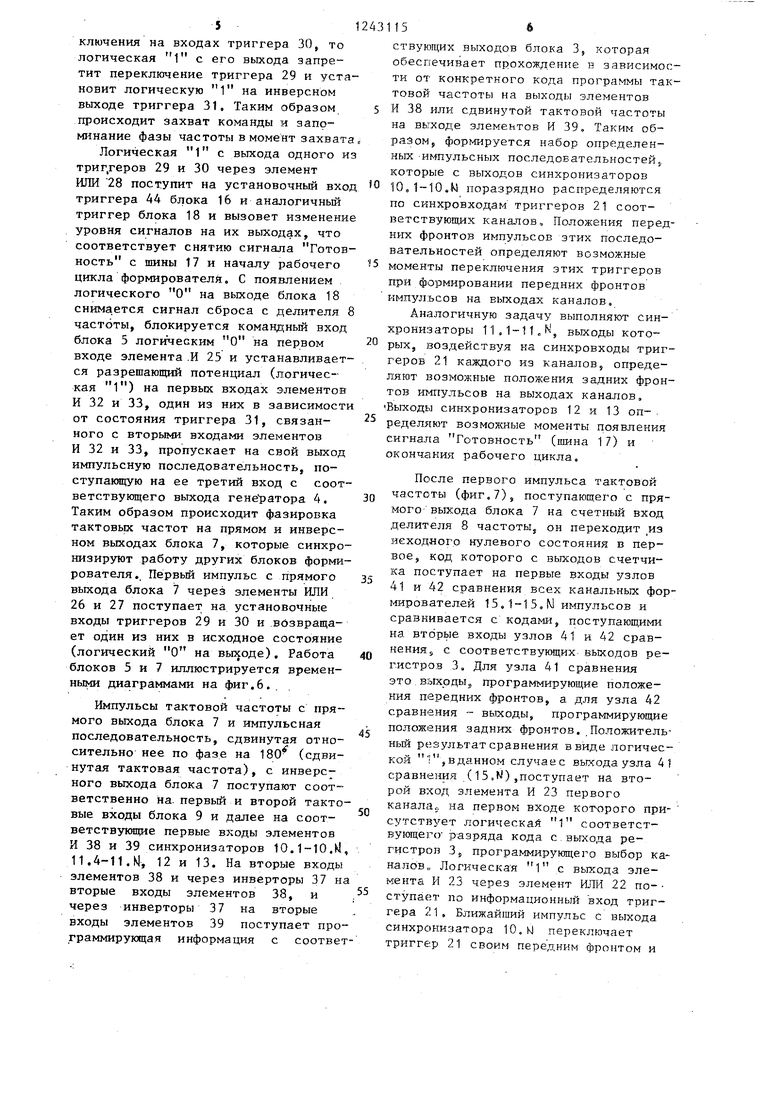

После первого импульса тактовой частс ты (фиг, 7), поступающего с прямого вьвсода блока 7 на счетный вход делителя 8 частоты, он переходит ,из исходного нулевого состояния в первое, код которого с выходов счетчика поступает на первые входы узлов 41 и 42 сравнения всех канальных формирователей 15,1-15, W импульсов и сравнивается с кодами, поступающими на вторые входы узлов 41 и 42 сравнения с соответствующих выходов регистров 3. Для узла 41 сравнения это,выходы, программирующие положения передних фронтов, а для узла 42 сравнения - выходы, программирующие положения задних фронтов..Положительный результат сравнения в виде логической 1, в данном ел уча в с выхода узла 4| сравнения (15.N) ,поступает на второй вход элемента И 23 первого канала{. на первом входе кот-орого присутствует логическай 1 соответствующего )разряда кода с . вьгкода регистров 3j программирующего выбор каналов,, Логическая 1 с выхода элемента И 23 через элемент ИЛИ 22 по- ступает по информационный вход триггера 21, Ближайший импульс с выхода синхронизатора 10. К1 переключает триггер 21 своим передним фронтом и

71

тем самым формирует передний фронт импульса на выходе первого канала 20,N. Логическая 1 с выхода триг- гера 21 поступает на второй вход элемента ИЛИ 22 и поддерживает ло- гическую 1 на информационном входе .триггера 21 после исчезновения логической 1 на первом входе элемента ИЛИ 22, когда делитель частоты изменит свое состояние.

По исполнении делителем частоты второго цикла деления совпадение обнаружено узлом 42 сравнения канального формирователя импульсов 15.W и логическая 1 поступит на информа- ционный вход триггера 24 первого канала.Ближайший импульс с выхода синхронизатора 11.1 поступит на синхро- вход триггера 24 первого канала и своим передним фронтом вызовет его переключение. Логическая 1 с выхот да триггера 24 воздействует на установочный вход триггера 21, возвра- щает его в исходное состояние. При этом формируется задний фронт импульса на выходе первого канала. Логическая 1 с инверсного выхода триггера 21 поступает на установочный вход триггера 24 и он также переключается в исходное состояние.

Когда делитель частоты выполнит четыре цикла, код на его выходе совпадет с кодом на выходах регистров 3 которые задают момент выдачи готов- ности, который фиксируется узлом 43 сравнения блока 16. Логическая 1 с его выхода поступит на информа- ционньй вход триггера 44, который переключится по переднему фронту импульса с выхода синхронизатора 12 и на шинг 17 появится потенциал высокого уровня. Сигнал делителя 8 частоты nocj;e пяти циклов деления фиксируется сразу обоими узлами 41 и 42 сравнения канального формирователя 15. N импульсов и формируется импульс на шине 20 М аналогично полученному на выходе первого канала, причем его длительность минимально- возможна для формирователя и равна 1/2Т тактовой частоты. Кроме того, выходной код делителя 8 частоты, после пяти циклов совпадет с кодом на выходе регистров 3, задающим длительность цикла, и блок 18, аналогичный блоку 16, выдает логическую 1, которая завершит переход формировате

5 O

5

Q 5

5

0

0

158

ля из рабочего цикла в состояние ож1Т

да ния.

Формула изобретения

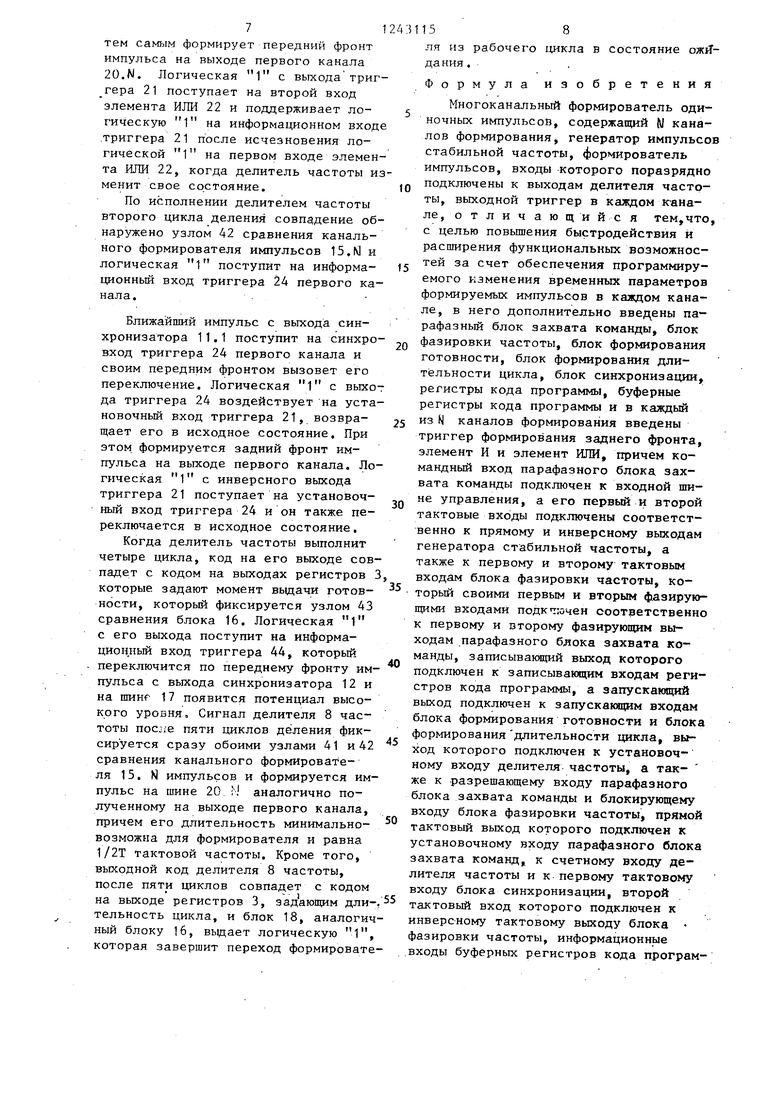

Многоканальный формирователь одиночных импульсов, содержащий W каналов формирования, генератор импульсов стабильной частоты, формирователь импульсов, входы которого поразрядно подключены к выходам делителя частоты, выходной триггер в каждом юана- ле,о тлич ающийс я тем,что, с целью повьшения быстродействия и расширения функциональных возможностей за счет обеспечения программируемого изменения временных параметров формируемых импульсов в каждом канале, в него дополнительно введены па- рафазный блок захвата команды, блок фазировки частоты, блок формирования готовности, блок формирования длительности цикла, блок синхронизации, регистры кода программы, буферные регистры кода программы и в каждый из N каналов формирования введены триггер формирования заднего фронта, элемент И и элемент РШИ, причем командный вход парафазного блока, захвата команды подключен к входной шине управления, а его первый и второй тактовые входы подключены соответственно к прямому и инверсному выходам генератора стабильной частоты, а также к первому и второму тактовым входам блока фазировки частоты, который своими первым и вторым фазирующими входами подключен соответственно к первому и второму фазирующим выходам парафазного блока захвата команды, записываклций выход которого подключен к записывающим входам регистров кода программы, а запускающий выход подключен к запускающим входам блока формирования готовности и блока формирования длительности цикла, выход которого подключен к установочному входу делителя частоты, а также к разрешающему входу парафазного блока захвата команды и блокирующему входу блока фазировки частоты, прямой тактовый выход которого подключен к установочному входу парафазного блока захвата команд, к счетному входу делителя частоты и к первому тактовому входу блока синхронизации, второй тактовый вход которого подключен к инверсному тактовому выходу блока фазировки частоты, информационные входы буферных регистров кода програм9 . 1 мы подключены к информационным н(инам, а их информационные вькоды - к информационным входам регистров кода программы, первые выходы которых, программирующие выбор каналов, поразряд- но подключены к первым входам элементов И каждого из каналов, а выходы программирующие фазу частоты синхронизации, поразрядно подключены к про- граммируюисим входам блока синхронизации, первые выходы которого поразрядно соединены с синхровх.одами выходных триггеров каждого из каналов, прямые выходы которых подключены к соответствующим канальным шинам и к первым входам соответствующих элементов РШИ, выходы которых соединены с информационными входами соответствующих выходных триггеров, вторые выходы блока синхронизации подключены поразрядно к синхровходам триггеров формирования заднего фронта каждого из каналов, выходы которых подключены к установочным входам соответствующих выходных триггеров, инверсные выходы которых подключены к установочным входам соответствующих триг- г%ров формирования заднего фронта, выходы регистров кода программы, программирующие положения передних фронтов, и выходы, программирующие поло11510

|Жение ;)адних фронтов выходных каналь- Ных имщ льсов,- подключены соответственно поразрядно к первым и вторым входам формирователя импульсов, выходы которого, определяющие положения передних фронтов, поразрядно подключены к вторым входам элементов И каждого из каналов, выходы которых подключены к вторым входам соответствующих элементов ИЛИ, а выходы формирователя импульсов, определяющие положения задних фронтов,поразрядно подключены к информационным входамтриггеров фор1чирования заднего фронта, выходы регистров кода про граммы, определяющие моментвьщачи сигнала готовности, подключены поразрядно к программирую- входам блока формирования готовности, выход которого подключен к выходной управляющей шине, а его входы текущего состойния подключены поразрядно и к выходам делителя частоты и к входам текущего состояния формирователя длительности цикла, программируемые входы которого подключены поразрядно к выходам регистров кода nporpajviMbi, синхронизирующие входы блока формирования готовности и блока формированиуг длительности подключены к соот)зетствукяп;им выходам блока синхронизации.

SM.i

M&f

.S

JS

W

К)

ff

К

, .й

К23

Фиг. 6

Фиг. 7

./

/ t

Фиг.в

Редактор Л.Гратилло

Составитель В,Герас:имов Техред Н.Бонкало

Заказ 3717/56Тираж 816Подписное

ВНИИПИ Государственног,о комитета СССР

по делам изобретений и открьт-гй 113035, Москва, Ж-35, Раушская наб.., д,4/5

Производственно-полиграфическое- предприятие, г.Ужгород, ул. Проектная, А

Фиг. 9

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1987 |

|

RU1612956C |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

Изобретение может быть использовано в автоматике, вычислительной технике, контрольно-испытательных системах. Цель изобретения - повышение быстродействия и расширение функциолальных возможностей устройства. Формирователь содержит генератор 4 импульсов стабильной частоты, делитель 8 частоты, синхронизаторы 12 и 13, формирователь 14 импульсов и D-триггер 21. Введение в устройство буферных регистров 1 кода программы, регистров 3 кода-программы, парафазт- ного блока 5 захвата команды, блока 7 фазировки частоты, блока 9 синхронизации, состоящего из N канальных синхронизаторов 10. 1-10.N и 11.1-11.N, блока 16 формирования готовности, блока 18 формирования длительности цикла, элемента ЩИ 22, элемента И 23 и D-триггера 24 формирования заднего фронта обеспечивает программируемое изменение временных параметров импульсов, формируемых в каждом канале . 9 ил .. с С/) to li оо ел

| Устройство для формирования импульсной последовательности | 1980 |

|

SU938414A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальный формирователь одиночных импульсов | 1976 |

|

SU694979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Примечание: изменения в формуле изобретения носят редакционный ха рактер.. | |||

Авторы

Даты

1986-07-07—Публикация

1985-01-04—Подача