(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Формирователь длительности импульсов | 1984 |

|

SU1213525A1 |

| Устройство для ввода информации | 1983 |

|

SU1091147A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| Устройство для ввода информации | 1984 |

|

SU1223219A1 |

| Блок адресации для процессора быстрого преобразования Фурье | 1984 |

|

SU1223247A1 |

| Устройство коррекции кода | 1986 |

|

SU1490720A1 |

Программируемый формирователь периодических сигналов может быть использован в качестве формирователя эталонной временной диаграммы для измерительных устройств и контрольно-испытательной аппаратуры, Преобразователь содержит регистр 1 длительности импульса, регистр 3 длительность паузы, мультиплексоры 5, 2, 12, 14, 16, D-триггеры 8, 18, Т-триггер 10, задающий генератор 7, формирователь 6 ряда частот, логический преобразователь 9, счетчики 4, 15, регистр 11 дребезга импульса, регистр 13 дребезга паузы, элемент И 17, сумматор 19 по модулю два с соответствующими связями 1 з.п.ф-лы, 2 ил.

VI

Оч

ел

О)

Изобретение относится к контрольно- измерительной технике и может быть использовано в качестве формирователя эталонной временной диаграммы для измерительных устройств и контрольно-измерительной аппаратуры.

Целью изобретения является расширение диапазона временных параметров и расширение функциональных возможностей за счет формирования периодической последовательности с эффектами дребезга импульса и паузы.

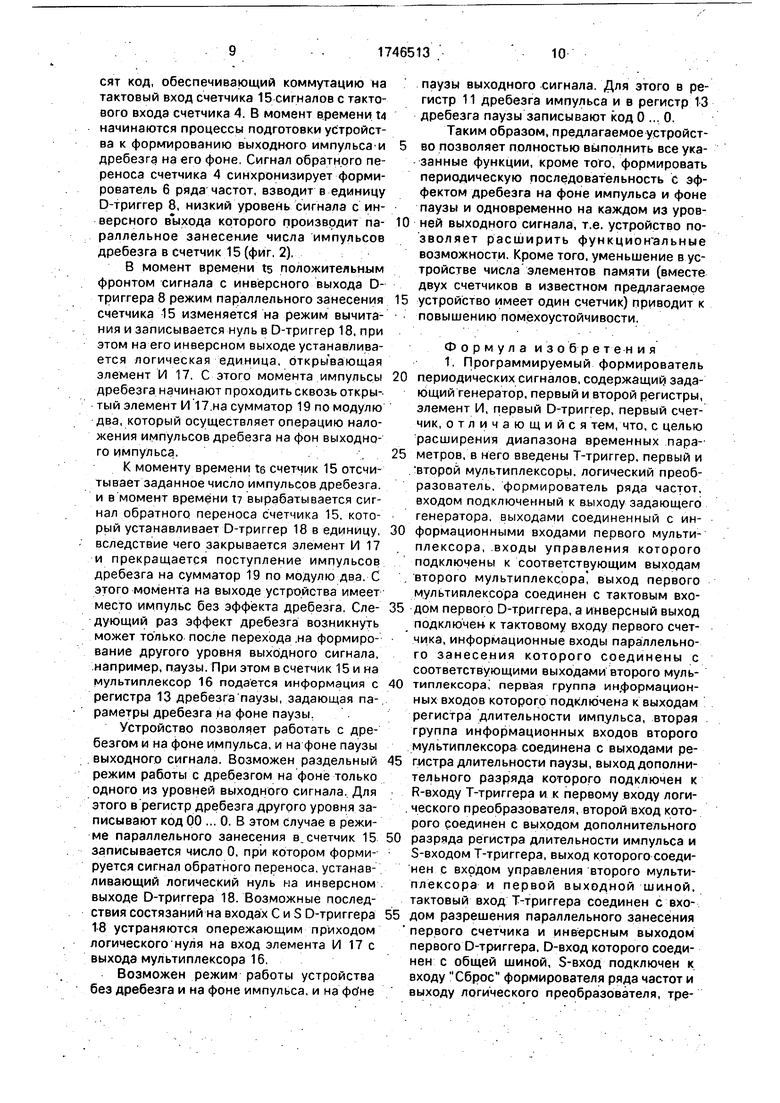

На фиг, 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства.

Устройство состоит из регистра 1 длительности импульса, выходы которого соединены с первой группой информационных входов второго мультиплексора 2, вторая группа информационных входов которого соединена с выходами регистра 3 длительности паузы. Соответствующие выходы второго мультиплексора 2 подключены к информационным входам параллельного занесения первого счетчика 4 и входам управления первого мультиплексора 5, инверсный выход которого соединен с тактовым входом первого счетчика 4. Информационные входы первого мультиплексора 5 подключены к выходам формирователя 6 ряда частот, тактовый вход которого соединен с выходом задающего генератора 7, а вход Сброс подключен к S-входу первого D- триггера 8 и выходу логического преобразователя 9, первый вход которого соединен с выходом обратного переноса первого счетчика 4.

Второй вход логического преобразователя 9 соединен с выходом дополнительного разряда регистра 1 импульса и S-входом Т-триггера 10, третий вход логического преобразователя 9 подключен к вых оду дополнительного разряда регистра 3 паузы и R-входу Т-триггера 10, выход которого соединен с первой выходной шиной и входом управления второго мультиплексора 2. Выход первого мультиплексора 5 соединен с тактовым входом первого D-триггера 8, информационный вход которого соединен с общей шиной, а инверсный выход первого D-триггера 8 подключен к тактовому входу Т-триггера 10 и входу размещения параллельного занесения первого счетчика 4.

Устройство содержит регистр 11 дребезга импульса, первая группа выходов которого подключена к первой группе информационных входов третьего мультиплексора 12, вторая группа информационных входов которого соединена с первой группой выходов регистра 13 дребезга паузы, вторая группа выходов регистра 13 дребезга паузы подключена к первой группе входов четвертого мультиплексора 14, вторая группа информационных входов которого соединена с второй группой выходов регистра 11 дребезга импульса, вход управления четвертого мультиплексора 14 подключен к входам управления второго 2 и третьего 12 мультиплексоров, выходы по0 следнего соответственно соединены с информационными входами параллельного занесения второго счетчика 15, тактовый вход которого подключен к инверсному выходу пятого мультиплексора 16, входы уп5 равления которого соединены с выходами четвертого мультиплексора 14, информационные входы пятого мультиплексора 16 подключены соответственно к тактовому входу и соответствующим выходам первого счет0 чика 4, выход пятого мультиплексора 16 соединен с первым входом элемента И 17, второй вход которого подключен к инверсному выходу второго D-триггера 18, S-вход которого соединен с выходом обратного пе5 реноса второго счетчика 15, D-вход подключен к общей шине, тактовый вход соединен с входом разрешения параллельного занесения второго счетчика 15 и инверсным выходом первого D-триггера 8, а выход

0 элемента И 17 соединен с первым входом сумматора 19 по модулю два, второй вход которого подключен к выходу Т-триггера 10, а выход сумматора 19 по модулю два соединен с второй выходной шиной.

5Регистр 1 импульса задает длительность импульса выходной последовательности устройства. Несколько разрядов регистра 1 импульса кодируют период следования импульсов заполнения, остальные

0 разряды кодируют число импульсов заполнения, требуемое для получения нужной длительности импульса выходной последовательности. Дополнительный разряд регистра 1 импульса предназначен для

5 удержания устройства в режиме ожидания в состоянии выдачи импульса. Логический нуль на выходе дополнительного разряда удерживает устройство в состоянии выдачи импульса. В момент записи единицы в до0 полнительный разряд импульс на выходе устройства заканчивается и начинается генерация периодической последовательности и формирования паузы, Аналогично происходит запуск устройства из состояния

5 паузы на выходе.

Мультиплексор 2 предназначен для поочередной выдачи на информационные входы счетчика 4 и входы управления мультиплексора 5 данных или с выходов регистра 1 импульса, или с выходов регистра

3 паузы в зависимости от значения сигнала на выходе устройства.

Регистр -3 паузы задает длительность паузы в выходной периодической последовательности, Несколькими разрядами реги- стра паузы кодируется период следования импульсов заполнения, остальные разряды кодируют число импульсов заполнения, требуемое для получения нужной длительности паузы в периодической последовательно- сти. Дополнительный разряд регистра 3 паузы предназначен для удержания устройства в состоянии паузы. В момент записи единицы в дополнительный разряд паузы на выходе устройства заканчивается и начи- нается импульс выходной периодической последовательности.

Счетчик 4 производит подсчет числа импульсов заполнения, определяющих длительность выходного импульса или паузы. Во время последнего импульса заполнения счетчик 4 выдает сигнал на изменение уровня выходной последовательности. Мультиплексор 5 обеспечивает поступление на счетчик 4 одной из ряда частот, оптималь- ной для формирования времени импульса или паузы

Формирователь б ряда частот представляет собой делитель частоты и выполняет функции формирования ряда частот. Синх- ронизируется делитель частоты по входу сброса. Задающий генератор 7 предназначен для генерации стабилизированной во времени эталонной частоты. D-триггер 8 предназначен для регистрации факта по- ступления последнего импульса заполнения при формировании временного интервала импульса или паузы.

Логический преобразователь 9 формирует сигнал приведения устройства в исход- ное состояние по признакам окончания времени импульса или паузы, а также по одному из признаков режима ожидания. Т- триггер 10 формирует выходной сигнал устройства, Регистр 11 дребезга импульса предназначен для хранения информации о числе импульсов дребезга на фоне выходного импульса и их периоде.

Мультиплексор 12 предназначен для поочередной подачи на информационные входы счетчика 15 данных о числе импульсов дребезга либо от регистра 11 дребезга импульса, либо от регистра 13 дребезга паузы. Регистр 13 дребезга паузы предназначен для хранения информации о числе импульсов дребезга на фоне паузы выходного сигнала и их периоде.

Мультиплексор 14 поочередно подает на входы управления мультиплексора 16 данные о периоде следования импульсов

дребезга либо из регистра 11 дребезга импульса, либо из регистра 13 дребезга паузы. Счетчик 15 ведет подсчет импульсов дребезга на фоне выходного импульса или паузы и после последнего импульса дребезга выдает сигнал на запрет наложения импульсов дребезга на фон выходного сигнала,

Мультиплексор 16 предназначен для выбора в качестве импульсов дребезга одной из частот, равной или кратной частоте заполнения временного интервала выходного импульса или паузы. Элемент И 17 выполняет роль ключа, пропускающего или не пропускающего на фон выходной последовательности импульсы дребезга.

D-триггер 18 предназначен для регистрации факта выдачи последнего импульса дребезга, после чего он с инверсного выхода выдает логический нуль на вход элемента И 17, который прерывает дребезг выходного сигнала. Сумматор 19 по модулю два обеспечивает наложение эффекта дребезга на фон выходного сигнала.

Фильтр работает следующим образом.

Период выходной последовательности состоит из времени импульса и времени паузы. В устройстве длительности каждого уровня выходного сигнала задается период следования импульсов заполнения и их числом. Длительность импульса и паузы определяется управляющими словами, хранящимися в регистрах 1 и 3 импульса и паузы соответственно.

Примерная структура регистров 1 и 3 импульса и паузы может быть следующей. Разряды 0-11 предназначены для хранения числа импульсов заполнения, содержимое разрядов 12-14 определяет период следования импульсов заполнения, а разряд 15 обеспечивает режим ожидания,-Логический нуль в разряде 15 регистра 1 импульса удерживает выходной сигнал в состоянии единицы, логический нуль в разряде 15 регистра 3 паузы - выходной сигнал на низком уровне до тех пор, пока в указанных разрядах не появляются логические единицы.

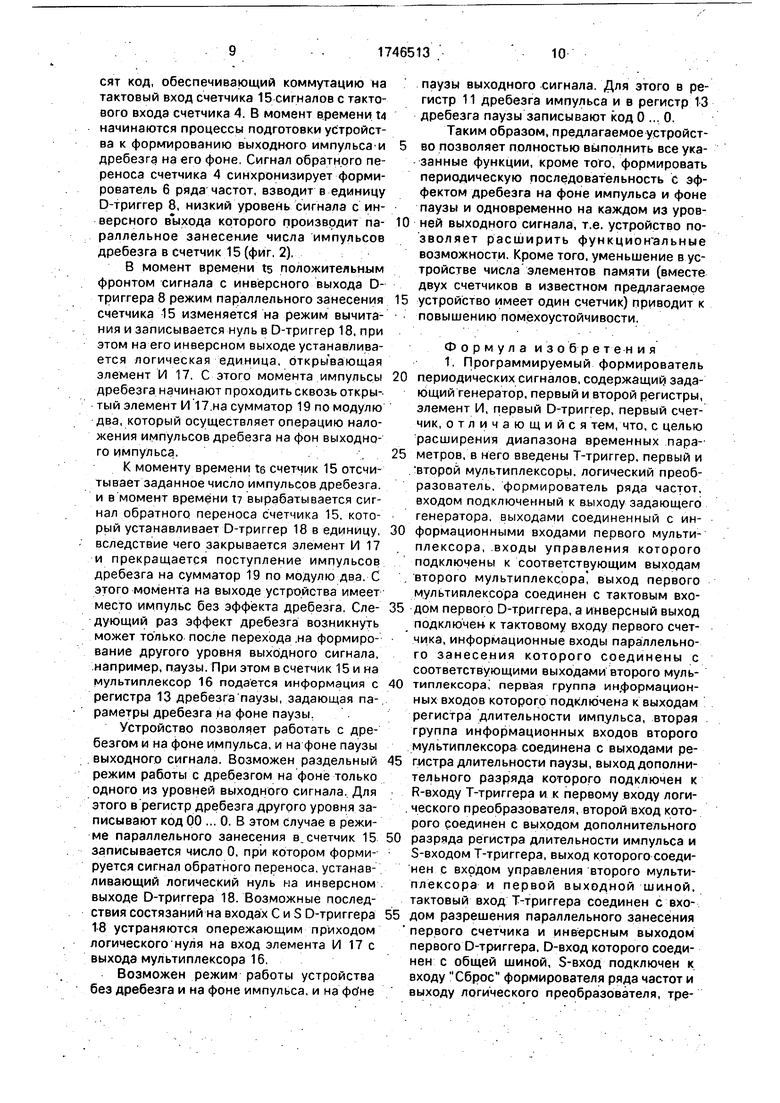

Работу программируемого формирователя периодических сигналов рассмотрим на примере запуска устройства из исходного состояния высокого уровня (фиг. 2).

В исходном состоянии разряд 15 регистра 1 импульса находится в нуле, удерживая в состоянии единицы Т-триггер 10, создает логический нуль на выходе логического преобразователя 9, который формирует низкий уровень сигнала на инверсном выходе D-триггера 8, и удерживает в исходном состоянии формирователь 6 ряда частот. Логическая единица на выходе Т-триггера 10 обеспечивает подачу через

мультиплексор 2 на входы параллельной записи счетчика А информации из регистра 3 паузы, которая в режиме параллельного занесения записывается в счетчик 4 логическим нулем с инверсного выхода D-триггера 8. Наличие двух нулей одновременно в разрядах 15 регистра 1 импульса и регистра 3 паузы является в предлагаемом устройстве недопустимым.

Процесс запуска устройства происхо- дит в момент времени ti (фиг. 2) записью единицы в разряд 15 регистра 1 импульса, которая снимает режим удержания в единице с триггеров 8 и 10 и разрешает работу формирователя б ряда частот, Не позже, чем через один период частоты задающего гене- ратораУ (момент ta), на выходе мультиплексора 5 появится положительный фронт импульса заполнения паузы выходного сигнала, который записывает нуль в D-триггер 8. Положительный фронт сигнала на инверсном выходе D-триггера снимает режим параллельного занесения со счетчика 4, переводя его в режим вычитания, изменяет состояние триггера 10 из единицы в нуль, что соответствует началу процесса формирования временного интервала паузы выходного сигнала.

Содержимое счетчика 4 равно при этом исходному числу импульсов заполнения па- узы. Логический нуль на выходе Т-триггера 10 обеспечивает поступление на входы управления мультиплексора 5 информации тех разрядов регистра 3 паузы, которые вы- бирают из ряда частот оптимальный период следования импульсов заполнения. В момент времени t3 положительным фронтом импульса заполнения содержимое счетчика 4 уменьшается на единицу. Этот процесс продолжается до тех пор, пока счетчик 4 не отсчитает число; импульсов заполнения, определяющих длительность паузы.

При состоянии 00 ... О счетчика 4 в момент времени ц низкий уровень сигнала обратного переноса приводит в исходное состояние (синхронизирует) формирователь б ряда частот и устанавливает в единицу D-триггер 8. Логический нуль с инверсного выхода D-триггера 8 устанавливает режим параллельного занесения счетчику 4, в про- цессе которого в счетчик 4 записывается число импульсов заполнения, задающих длительность выходного импульса.

. После1 параллельного занесения информации в счетчик 4 снимается низкий уро- вень сигнала с собственного выхода обратного переноса. В момент времени ts очередным положительным фронтом сигнала задающего генератора 7 на выходе мультиплексора 5 инициируется положительный

фронт сигнала, который записывает нуль в D-триггер 8. Вследствие этого положительный фронт сигнала на инверсном выходе D-триггера 8 снимает режим параллельного занесения со счетчика 4 и. изменяет состояние триггера 10, высокий сигнал на выходе которого является выходным импульсом предлагаемого устройства. Содержимое счетчика 4 при этом равно исходному числу импульсов заполнения, которое определяет длительность выходного импульса,

Логическая единица на выходе Т-триггера 10 обеспечивает поступление на счетчик 4 частоты заполнения выбранной для формирования длительности выходного импульса. Процесс-формирования длительности выходного импульса аналогичен указанному процессу формирования паузы. В момент времени ts повторяются все процессы для момента t2.

Аналогично наличие логического нуля в дополнительном разряде регистра 3 паузы удерживает выходной сигнал устройства в состоянии паузы. Перевод устройства в режим автогенерации происходит аналогично. Таким образом, предлагаемое устройство позволяет давать длительность интервалов времени не только число импульсов заполнения, но и их периодом, что расширяет диапазон формируемых интервалов времени.

Работу устройства рассмотрим также на примере наложения эффекта дребезга на фон выходного импульса.

В качестве периода импульсов дребезга в предлагаемом устройстве используется либо период основной частоты импульсов заполнения, поступающей на тактовый вход счетчика 4, либо период, кратный периоду заполнения данного интервала времени. Сигнал дребезга снимается с определенных разрядов счетчика 4.

Параметры дребезга и паузы определяются информацией, хранящейся в регистрах дребезга импульса 11 и дребезга паузы 13 соответственно. Структура этих регистров может быть следующей. Разряды 0-5 предназначены для хранения числа импульсов дребезга, содержимое разрядов 6 и 7 определяет период следования импульсов дребезга.

Наложение импульсов дребезга на фон выходного сигнала происходит следующим образом. Предположим, что на фон выходного импульса необходимо наложить один импульс дребезга, период которого равен частоте импульсов заполнения временного интервала выходного импульса. Для этого в разряды 0-5 регистра 11 дребезга импульса записывают число 1, а в разряды 6 и 7 заносят код, обеспечивающий коммутацию на тактовый вход счетчика 15 сигналов с тактового входа счетчика 4. В момент времени t4 начинаются процессы подготовки устройства к формированию выходного импульса и дребезга на его фоне Сигнал обратного переноса счетчика 4 синхронизирует формирователь 6 ряда частот, взводит в единицу D-триггер 8, низкий уровень сигнала с инверсного выхода которого производит параллельное занесение числа импульсов дребезга в счетчик 15 (фиг. 2).

В момент времени ts положительным фронтом сигнала с инверсного выхода D- триггера 8 режим параллельного занесения счетчика 15 изменяется на режим вычитания и записывается нуль в D-триггер 18. при этом на его инверсном выходе устанавливается логическая единица, открывающая элемент И 17. С этого момента импульсы дребезга начинают проходить сквозь открытый элемент И 17 на сумматор 19 по модулю два, который осуществляет операцию наложения импульсов дребезга на фон выходного импульса.

К моменту времени t6 счетчик 15 отсчитывает заданное число импульсов дребезга. и в момент времени t вырабатывается сигнал обратного переноса счетчика 15. который устанавливает D-триггер 18 в единицу, вследствие чего закрывается элемент И 17 и прекращается поступление импульсов дребезга на сумматор 19 по модулю два. С этого момента на выходе устройства имеет место импульс без эффекта дребезга. Следующий раз эффект дребезга возникнуть может только после перехода на формирование другого уровня выходного сигнала, например, паузы. При этом в счетчик 15 и на мультиплексор 16 подается информация с регистра 13 дребезга паузы, задающая параметры дребезга на фоне паузы

Устройство позволяет работать с дребезгом и на фоне импульса, и на фоне паузы выходного сигнала. Возможен раздельный режим работы с дребезгом на фоне только одного из уровней выходного сигнала. Для этого в регистр дребезга другого уровня записывают код 00 ... 0. В этом случае в режиме параллельного занесения в. счетчик 15 записывается число 0, при котором формируется сигнал обратного переноса, устанавливающий логический нуль на инверсном выходе D-триггера 18. Возможные последствия состязаний на входах С и S D-триггера 18 устраняются опережающим приходом логического нуля на вход элемента И 17 с выхода мультиплексора 16,

Возможен режим работы устройства без дребезга и на фоне импульса, и на фо не

паузы выходного сигнала. Для этого в регистр 11 дребезга импульса и в регистр 13 дребезга паузы записывают код 0 .. 0. Таким образом, предлагаемое устройст5 во позволяет полностью выполнить все указанные функции, кроме того, формировать периодическую последовательность с эффектом дребезга на фоне импульса и фоне паузы и одновременно на каждом из уров0 ней выходного сигнала, т.е. устройство позволяет расширить функциональные возможности. Кроме того, уменьшение в устройстве числа элементов памяти (вместе двух счетчиков в известном предлагаемое

5 устройство имеет один счетчик) приводит к повышению помехоустойчивости.

Формула изобретения

0 периодических сигналов, содержащий задающий генератор, первый и второй регистры, элемент И, первый D-триггер, первый счетчик, отличающийся тем, что, с целью расширения диапазона временных пара5 метров, в него введены Т-триггер, первый и второй мультиплексоры, логический преобразователь, формирователь ряда частот, входом подключенный к выходу задающего генератора, выходами соединенный с ин0 формационными входами первого мультиплексора, входы управления которого подключены к соответствующим выходам второго мультиплексора выход первого мультиплексора соединен с тактовым вхо5 дом первого D-триггера, а инверсный выход подключен к тактовому входу первого счетчика, информационные входы параллельного занесения которого соединены с соответствующими выходами второго муль0 типлексора, первая группа информационных входов которого подключена к выходам регистра длительности импульса, вторая группа информационных входов второго мультиплексора соединена с выходами ре5 гистра длительности паузы, выход дополнительного разряда которого подключен к R-входу Т-триггера и к первому входу логического преобразователя, второй вход которого соединен с выходом дополнительного

0 разряда регистра длительности импульса и S-входом Т-триггера, выход которого соединен с входом управления второго мультиплексора и первой выходной шиной, тактовый вход Т-триггера соединен с вхо5 дом разрешения параллельного занесения первого счетчика и инверсным выходом первого D-триггера. D-вход которого соединен с общей шиной, S-вход подключен к входу Сброс формирователя ряда частот и выходу логического преобразователя, третий вход которого соединен с выходом обратного переноса первого счетчика.

2 Формирователь по п. 1,отличающий с я тем, что, с целью расширения функциональных возможностей за счет фор- мирования периодической последовательности с эффектами дребезга импульса и паузы, оно дополнительно содержит второй D-триггер, элемент И, второй счетчик, сумматор по модулю два, третий, четвертый и пятый мультиплексоры, регистр дребезга паузы, регистр дребезга импульса, первая группа выходов которого подключена к первой группе информационных входов третьего мультиплексора, вторая группа информационных входов которого соединена с первой группой выходов регистра дребезга паузы, вторая группа которого подключена к первой группе входов четвертого мультиплексора, вторая группа инфор- мационных входов которого соединена с второй группой выходов регистра дребезга импульса, вход управления четвертого мультиплексора подключен к входу управления второго мультиплексора, входууправ-

tiu/нн.fW tfuMH. + 4Гз.г.е.ту„, ТЬа&ч А/юуг,+ 4Tt.r.

ления третьего мультиплексора, выходы которого соответственно соединены с информационными входами параллельного занесения второго счетчика, тактовый вход которого подключен к выходу пятого мультиплексора, входы управления которого соответственно соединены с выходами четвертого мультиплексора, информационные входы пятого мультиплексора подключены соответственно к тактовому входу и соответствующим выходам первого счетчика, выход пятого мультиплексора соединен с первым входом элемента И, второй вход которого подключен к инверсному выходу второго D-триггера, S-вход которого соединен с выходом обратного переноса второго счетчика, D-вход подключен к общей шине, тактовый вход соединен с входом разрешения параллельного занесения второго счетчика и инверсным выходом первого D-трмггера, а выход элемента И соединен с первым входом сумматора по модулю два, второй вход которого подключен к выходу Т-триггера, а выход сумматора по модулю два соединен с второй выходной шиной.

А;

А

| Регулируемый генератор импульсов | 1978 |

|

SU773911A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-07-07—Публикация

1990-05-29—Подача