7i FTl f

-

CD ( 4 O5

i/7 j

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1987 |

|

SU1515359A1 |

| Преобразователь разности фаз в постоянное напряжение | 1986 |

|

SU1422176A1 |

| НИЗКОЧАСТОТНЫЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1992 |

|

RU2024028C1 |

| Преобразователь перемещения в напряжение | 1986 |

|

SU1681383A1 |

| Устройство для измерения коэффициента глубины амплитудной модуляции | 1984 |

|

SU1269053A1 |

| Устройство автоматической стабилизации скорости движения носителя магнитной записи | 1983 |

|

SU1115102A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Устройство для преобразования разности частот двух электрических сигналов в постоянное напряжение | 1983 |

|

SU1185607A1 |

| Преобразователь перемещения в напряжение | 1987 |

|

SU1803979A1 |

Изобретение относится к области импульсной техники и может быть использовано в системах приема и передачи информации с фазовой и частотно-фазовой автоподстройкой частоты. Цель изобретения - повышение точности и помехоустойчивости работы фазового детектора путем увеличения времени выборки и введения плоского участка напряжения интегратора. Она достигается введением ключа 6, управляющий вход которого соединен с вторым выходом формирователя 1 импульсов управления и управляющим входом блока 4 выборки-хранения, выход которого через ключ 6 подключен к второму входу интегратора 3. Фазовый детектор содержит также ключ 5 и источник 2 опорного напряжения. В описании изобретения даны электрические схемы интегратора 3 и блока 4 выборки-хранения. 2 ил.

срцг.7

Изобретение относится к импульсной технике и может быть использовано в системах приема и передачи информации о фазовой и частотно-фазовой авто подстройкой частоты. . Целью изобретения является повьше- ние точности.и помехоустойчивости работы устройства путем увеличения времени выборки и введения плоского уча- стка напряжения интегратора.

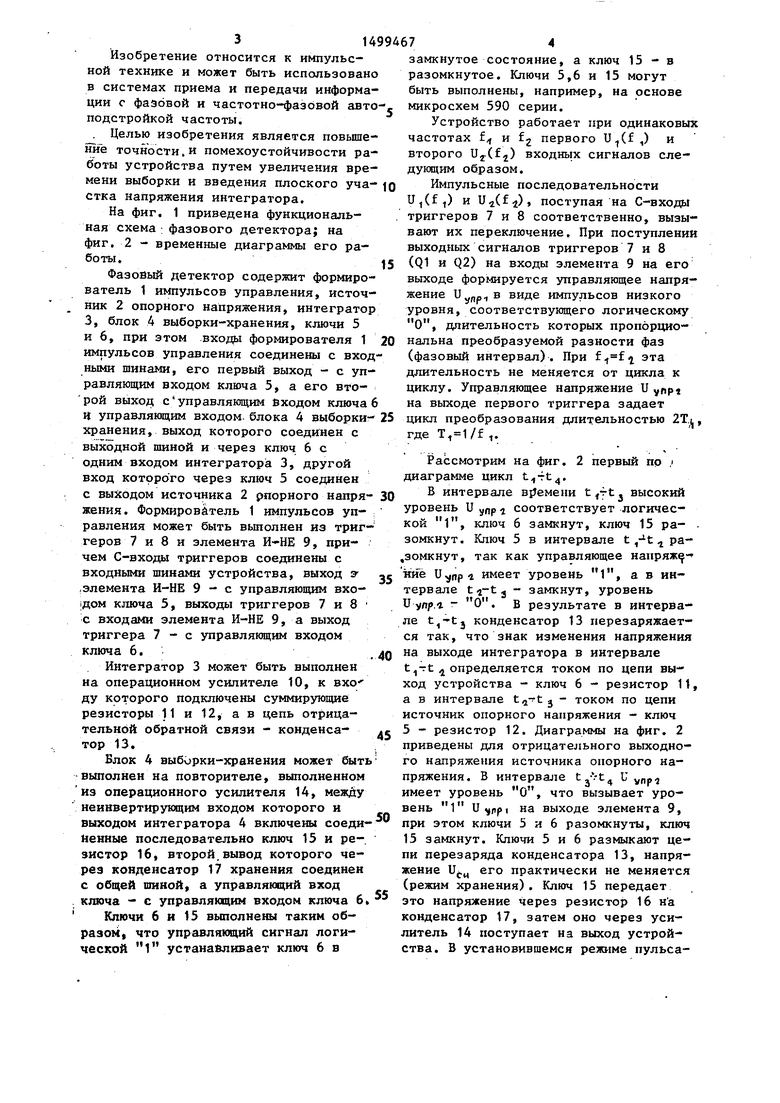

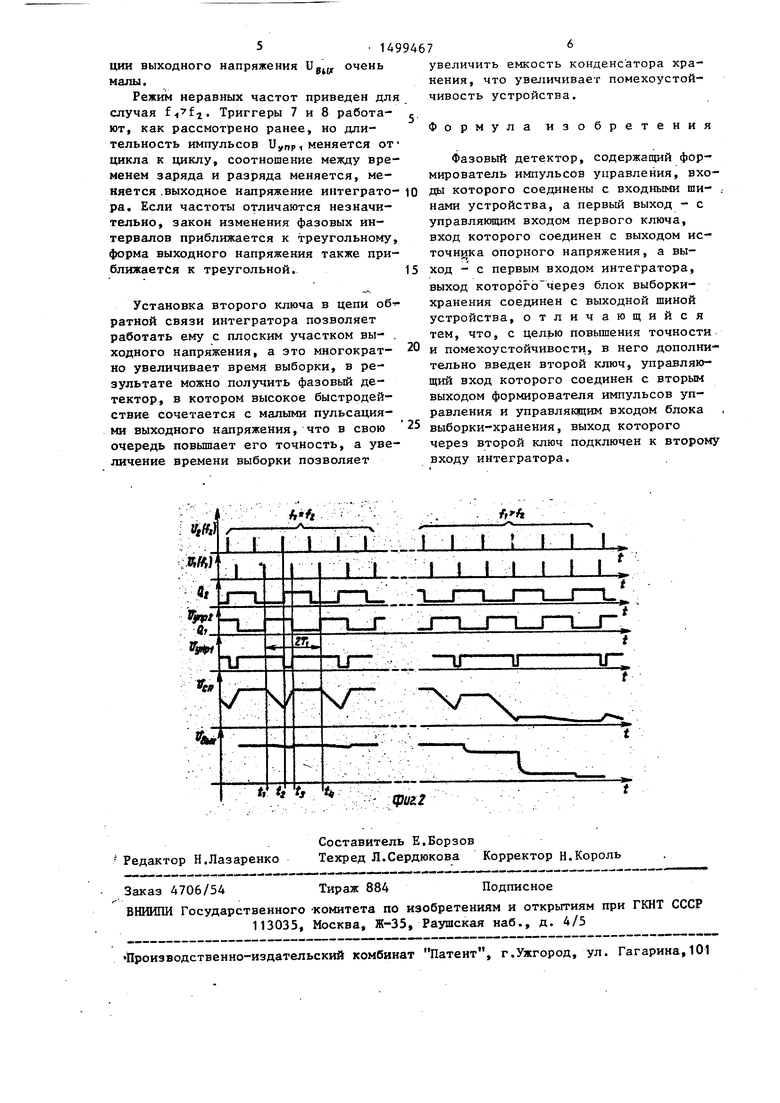

На фиг. 1 приведена функциональная схема : фазового детектора; на фиг. 2 - временные диаграммы его работы.

Фазовый детектор содержит формирователь 1 импульсов управления, источник 2 опорного напряжения, интегратор 3, блок А выборки-хранения, ключи 5 и 6, при этом входа формирователя 1 импульсов управления соединены с входными шинами, его первый выход - с управляющим входом ключа 5, а его вто

Импульсные последовательности и,(,) и ), поступаш на С-входа . триггеров 7 и 8 соответственно, вызывают их переключение. При поступлении выходных сигналов триггеров 7 и 8 15 (Q1 и Q2) на входы элемента 9 на его выходе формируется управляющее напряжение и „PI в виде импульсов низкого уровня, соответствующего логическому о, длительность которых пропорциональна преобразуемой разности фаз (фазовый интервал). При эта длительность не меняется от цикла к циклу. Управляющее напряжение U ynpi на выходе первого триггера задает

рой выход с управляющим бходом ключа 6 И управляющим входом блока 4 выборки-25 цикл преобразования длительностью 2Т., хранения, выход которого соединен с где ,. выходной шиной и через ключ 6 с одним входом интегратора 3, другой вход которого через ключ 3 соединен

с выходом источника 2 рпорного напря- 30 интервале В1 емени высокий жения. Формирователь 1 импульсов уп- ; уровень Uynpt соответствует логичес- равления может быть выполнен из триггеров 7 и 8 и элемента И-НЕ 9, приРассмотрим на фиг. 2 первый пр .i диаграмме цикл .

кой

чем С-входы триггеров соединены с

Ч, ключ 6 замкнут, ключ 15 разомкнут. Ключ 5 в интервале t ,- t ра- .зомкнут, так как управляющее напряж -

входными шинами устройства, выход э- ,, ние имеет уровень 1, а в ин- ,элемента И-НЕ 9 - с управляющим вхо- тервале - замкнут, уровень ДОМ ключа 5, выходы триггеров 7 и 8 с входами элемента И-НЕ 9, а выход триггера 7 - с управляющим входом

40

ключа 6.

Интегратор 3 может быть выполнен на операционном усилителе 10, к вхо ду которого подключены суммирующие резисторы 11 и 12, а в цепь отрицательной обратной связи - конденсатор 13,

Блок 4 выборки-хранения может быть выполнен на повторителе, выполненном

45

и уг;.а - О . В результате в интервале конденсатор 13 перезаряжается так, что знак изменения напряжения на выходе интегратора в интервале t -t определяется током по цепи выход устройства - ключ 6 - резистор 11, а в интервале t/j-t j - током по цепи источник опорного напряжения - ключ 5 - резистор 12. Диаграммы на фиг. 2 приведены для отрицательного выходного напряжения источника опорного напряжения. В интервале U у„рэ имеет уровень О, что вызывает урои уг;.а - О . В результате в интервале конденсатор 13 перезаряжается так, что знак изменения напряжения на выходе интегратора в интервале t -t определяется током по цепи выход устройства - ключ 6 - резистор 11 а в интервале t/j-t j - током по цепи источник опорного напряжения - ключ 5 - резистор 12. Диаграммы на фиг. 2 приведены для отрицательного выходного напряжения источника опорного напряжения. В интервале U у„рэ имеет уровень О, что вызывает уро из операционного усилителя 14, межДу неинвертирующим входом которого и вень 1 , на выходе элемента 9, выходом интегратора 4 включены соеди-- при этом ключи 5 и 6 разомкнуты, ключ Пенные последовательно ключ 15 и ре- 15 замкнут. Ключи 5 и 6 размыкают це- зистор 16, второй,вывод которого че- реэ конденсатор 17 хранения соединен с общей шиной, а управляющий вход ключа - с управляющим входом ключа 6

Ключи 6 и 15 выполнены таким образом, что управляющий сигнал логической 1 устанавливает ключ 6 в

пи перезаряда конденсатора 13, напряжение V его практически не меняется (режим хранения). Ключ 15 передает это напряжение через резистор 16 н а конденсатор 17, затем оно через усилитель 14 поступает на выход устройства. В установившемся режиме пульса

замкнутое состояние, а ключ 15 - в разомкнутое. Ключи 5,6 и 15 могут быть выполнены, например, на основе микросхем 590 серии.

Устройство работает при одинаковых частотах f и fg первого U(f ,) и второго ) входньгх сигналов следующим образом.

Импульсные последовательности и,(,) и ), поступаш на С-входа триггеров 7 и 8 соответственно, вызывают их переключение. При поступлении выходных сигналов триггеров 7 и 8 (Q1 и Q2) на входы элемента 9 на его выходе формируется управляющее напряжение и „PI в виде импульсов низкого уровня, соответствующего логическому о, длительность которых пропорциональна преобразуемой разности фаз (фазовый интервал). При эта длительность не меняется от цикла к циклу. Управляющее напряжение U ynpi на выходе первого триггера задает

цикл преобразования длительностью 2Т., где ,.

цикл преобразования длительностью 2 где ,.

Рассмотрим на фиг. 2 первый пр .i диаграмме цикл .

инт уровень

кой

Ч, зомкнут. .зомкнут,

ние имеет уровень 1, а в ин- тервале - замкнут, уровень

и уг;.а - О . В результате в интервале конденсатор 13 перезаряжается так, что знак изменения напряжения на выходе интегратора в интервале t -t определяется током по цепи выход устройства - ключ 6 - резистор 11, а в интервале t/j-t j - током по цепи источник опорного напряжения - ключ 5 - резистор 12. Диаграммы на фиг. 2 приведены для отрицательного выходного напряжения источника опорного напряжения. В интервале U у„рэ имеет уровень О, что вызывает уровень 1 , на выходе элемента 9, при этом ключи 5 и 6 разомкнуты, ключ 15 замкнут. Ключи 5 и 6 размыкают це-

вень 1 , на выходе элемента 9, при этом ключи 5 и 6 разомкнуты, ключ 15 замкнут. Ключи 5 и 6 размыкают це-

пи перезаряда конденсатора 13, напряжение V его практически не меняется (режим хранения). Ключ 15 передает это напряжение через резистор 16 н а конденсатор 17, затем оно через усилитель 14 поступает на выход устройства. В установившемся режиме пульса5 1499467

ции выходного напряжения иjj(, очень малы.

Режим неравных частот приведен для случая . Триггеры 7 и 8 работают, как рассмотрено ранее, но длительность импульсов Uynp 1 меняется от цикла к циклу, соотношение между временем заряда и разряда меняется, меняется .выходное напряжение интеграто- ра. Если частоты отличаются незначительно, закон изменения фазовых интервалов приближается к треугольному, форма выходного напряжения также приближается к треугольной.

Установка второго ключа в цепи об- ратной связи интегратора позволяет работать ему с плоским участком вы- . ходного напряжения, а это многократно увеличивает время выборки, в результате можно получить фазовый детектор, в котором высокое быстродействие сочетается с малыми пульсациями выходного напряжения, что в свою очередь повышает его точность, а увеличение времени выборки позволяет

I

Л /х

III

f,ft

I Г I

11 It I I I

в

Щ1Ф1

гпffeif

%«

увеличить емкость конденсатора хранения, что увеличивает помехоустойчивость устройства.

5

0

5

Формула изобретения

Фазовый детектор, содержащий формирователь импульсов управления, входы которого соединены с входными ши- . нами устройства, а первый выход - с управляющим входом первого ключа, вход которого соединен с выходом источника опорного напряжения, а выход - с первым входом интегратора, выход котор6го через блок выборки- хранения соединен с выходной шиной устройства, отличающийся тем, что, с целью повышения точности и помехоустойчивости, в него дополнительно введен второй ключ, управляющий вход которого соединен с вторым выходом формирователя импульсов управления и управлякщим входом блока выборки-хранения, выход которого через второй ключ подключен к второму входу интегратора.

f,ft

I Г I

11 L

JJ

| Частотно-фазовый детектор | 1977 |

|

SU661769A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Мартяшин А.И.и др | |||

| Преобразователи электрических параметров для систем контроля и измерения | |||

| - М.: Энергия, 1976, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-08-07—Публикация

1987-06-30—Подача