4

со со сд

о

СлЭ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в кодовой комбинации | 1986 |

|

SU1324089A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1991 |

|

SU1830616A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1986 |

|

SU1363485A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1977 |

|

SU634469A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1980 |

|

SU944130A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1990 |

|

SU1811007A2 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство содержит усилитель 1 с регулируемым коэффициентом усиления, усилитель 2 с постоянным коэффициентом усиления, компаратор 3, ключи 4 и 9, сумматор 5, блок 6 сравнения,пороговые блоки 7 и 8, элементы ИЛИ 10 и 15, накопитель 11, сумматоры 12 и 14 по модулю два, элемент И 13 и блок 16 обнаружения ошибок. При обнаружении ошибок формируется и передается сигнал переспроса на повторную передачу. Для уменьшения числа потерь, возникающих в случае искажения двух повторений, обеспечивается исправление ошибки во втором повторении комбинации путем формирования сигналов "стирания". Устройство по п.2 формулы отличается выполнением порогового блока 8.1 з.п.ф-лы, 3 ил.

К)

Изобретение относится к электросвязи, может быть использовано в системах передачи дискретной информации с решающей обратной связью и является усовершенствованием изобретения по авт.св. № 1324089.

Целью изобретения является повышение помехоустойчивости.

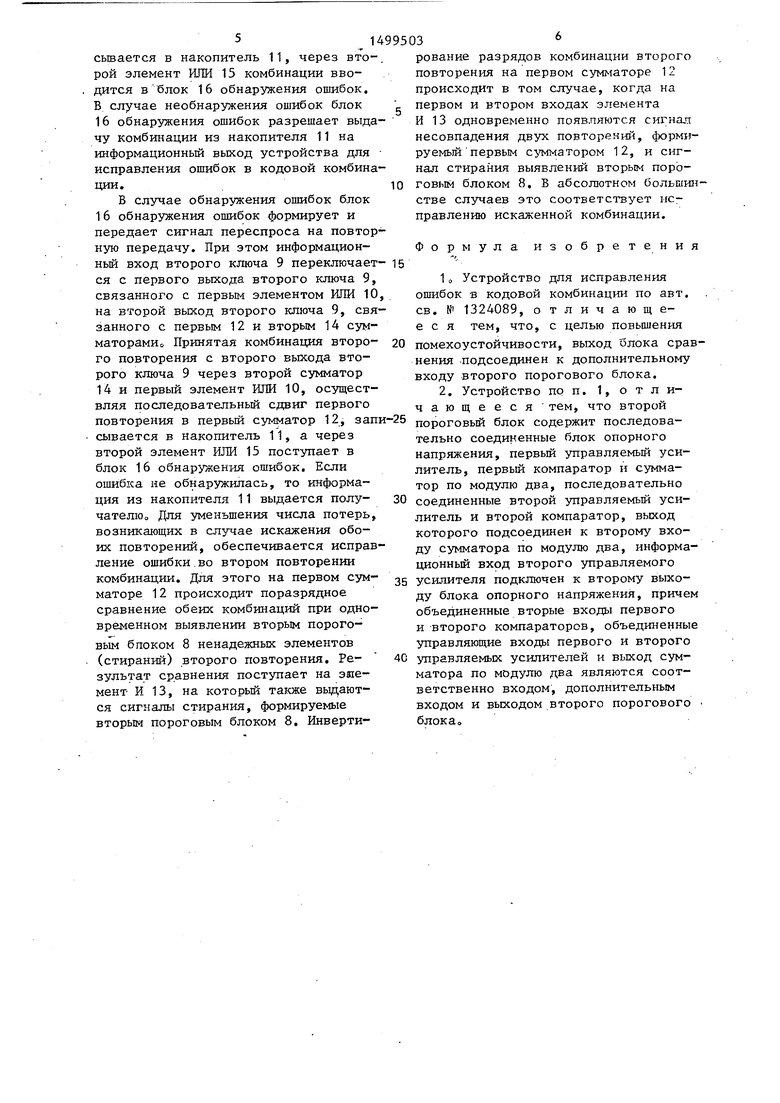

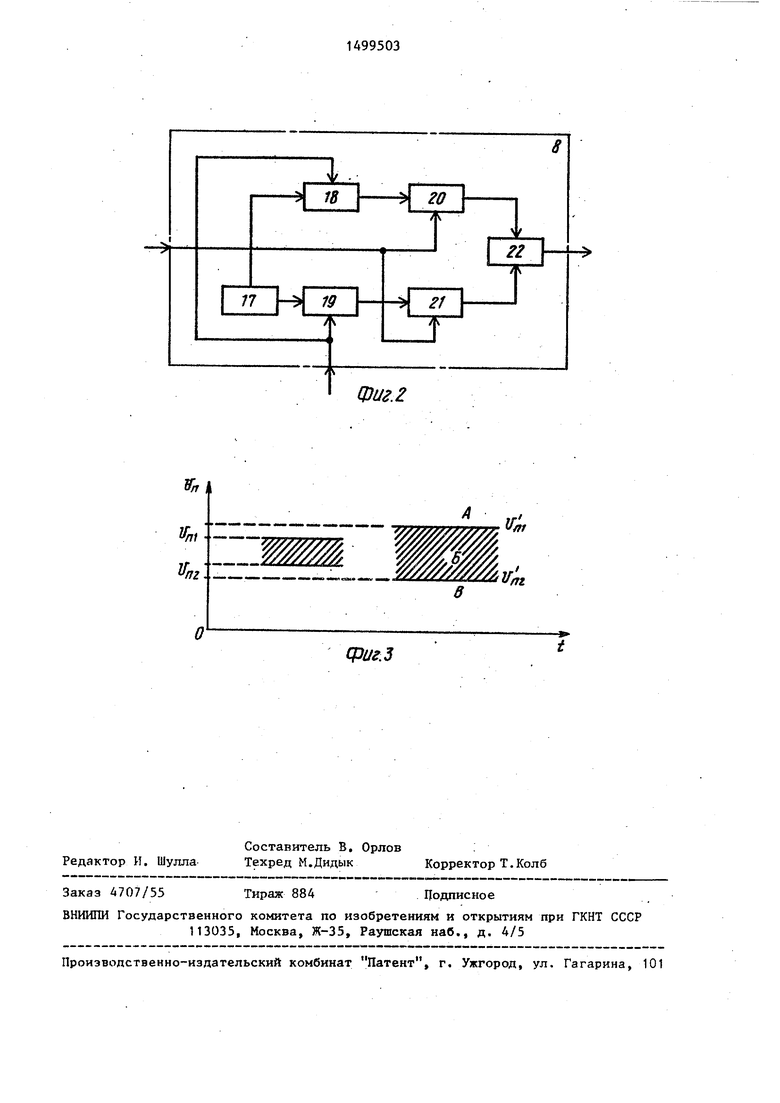

На фиг. 1 представлена структур- ная электрическая схема устройства для исправления ошибок в кодовой комбинации; на фиг. 2 - структурная электрическая схема второго порогового блока; на фиг..З - временные диаграммы сигналов, поясняющие работу устройства для исправления ошибок в кодовой комбинации.

Устройство для исправления ошибок в кодовой комбинации содержит усили- тель 1 с регулируемым коэффициентом усиления, усилитель 2 с постоянным коэффициентом усиления, компаратор 3, первьй ключ 4, сзт матор 5, блок 6 сравнения, первый 7 и второй 8 поро- говые блоки, второй ключ 9, первый элемент ИЛИ 10, накопитель 11, первый сумматор 12 по модулю два, элемент И 13, второй сумматор 14 по модулю два, второй элемент ИЛИ 15, блок 16 обнаружения ошибок.

Второй пороговый блок. 8 содержит блок 17 опорного напряжения, первый 18 и второй 19 управляемые усилители, первый 20 и второй 21 компарато- ры и сумматор 22 по модулю два.

Устройство для исправления ошибок в кодовой комбинации работает следующим образом.

Принимаемая кодовая комбинация подается на первьй 7 и второй 8 пороговые блоки и усилители 1 и 2 (фиг, 1). Усиленный в W раз с выхода усилителя сигнал Y(n)W(n) поступает на вход компаратора 3, где произво- дится сравнение произведений Y(n)W(n с опорным сигналом. По результатам сравнения компаратор 3 управляет ключом 4, разрешая прохождение сиг- нала pf,Y(n) с выхода усилителя 2, либо инверсно, либо неинверсно, т.е. определяет знак произведения (n). Полученный сигнал одновре.менно с сигналом с выхода усилителя 1 поступают соответственно на первьй и вто- рой входы сумматора 5, на вьсходе которого в зависимости от знака произведения (n) получается разность или сумма Y(n)W(n) (n), которая

поступает на блок 6 сравнения, где сравнивается .с сигналом, поступающим на него с выхода усилителя 1. На выходе блока 6 сравнения в случае действия в канале связи нестационарной помехи получается уровень, который пропорционален интенсивности помех.

Напряжение на выходе блока 6 сравнения регулирует коэффициент усиления усилителя 1, уровень порога в первом пороговом блоке 7 и посту- пает на дополнительный вход второго порогового блока 8.

Блок 8 работает следующим образом

С дополнительного входа второго порогового блока 8 (фиг. 2) сигнал управления поступает на управляющие входы первого 18 и второго 19 управляемых усилителей 18 и 19, на информационные входы которых подаются опоные напряжения U, и U, (фиг. 3) с выходов блока 17 опорного напрйже- ния. На выходах первого 18 и второго 19 управляемых усилителей, уровни и и и f, изменены в соответствии . с управляющим сигналом Св данном случае ширина полосы стираний увеличена) .

Далее уровни U и U подаются на первый 20 и второй 21 компараторы, где сравниваются с входным сигналом. Работа компараторов пояснена в таблице, где А, Б, В - уровни сигнала (фиг. 3).

Таким образом, на выходе второго порогового блока 8 сигнал появляется только тогда, когда при сравнении уровней порогов и сигнала последний находится в интервале стираний, что соответствует о некачественно принятом символе,

С выхода первого порогового бло- - ка 7 комбинация в виде последовательности нулей и единиц через второй ключ 9 и первый.элемент ИЛИ 10 записьтается в накопитель 11, через второй элемент ИЛИ 15 комбинации вводится в блок 16 обнаружения ошибок. В случае необнаружения ошибок блок 16 обнаружения ошибок разрешает выдачу комбинации из накопителя 11 на информационный выход устройства для исправления ошибок в кодовой комбинации.

В случае обнаружения ошибок блок 16 обнаружения ошибок формирует и передает сигнал переспроса на повторную передачу. При этом информацион- ньй вход второго ключа 9 переключает- ся с первого выхода второго ключа 9, связанного с первым элементом ИЛИ 10, на второй выход второго ключа 9, связанного с первым 12 и вторым 14 сум- маторамио Принятая комбинация второ- го повторения с второго выхода второго ключа 9 через второй сумматор 14 и первый элемент ИЛИ 10, осуществляя последовательный сдвиг первого

тельно соединенные блок опорного напряжения, первый управляемый уси литель, первый компаратор и суммаповторения в первый сумматор 12, запи-25 пороговый блок содержит последова- сывается в накопитель 11, а через второй элемент ИЛИ 15 поступает в блок 16 обнаружения ошибок. Если ошибка не обнаружилась, то информация из накопителя 11 выдается получате лю Для уменьшения числа потерь, возникающих в случае искажения обоих повторений, обеспечивается исправление ошибки.во втором повторении

30

тор по модулю два, последовательно соединенные второй управляемый усилитель и второй компаратор, выход которого подсоединен к второму входу сумматора по модулю два, информа ционный вход второго управляемого

комбинации. Для этого на первом сумматоре 12 происходит поразрядное сравнение обеих комбинаций при одновременном выявлении вторым пороговым бпоком 8 ненадежнь1х элементов (стираний) второго повторения. Результат сравнения поступает на эие- мент И 13, на который также выдаются сигналы стирания, формируемые вторым пороговым блоком 8, Инвертирование разрядов комбинации второго повторения на первом сумматоре 12 происходит в том случае, когда на первом и втором входах элемента И 13 одновременно появляются сигнал несовпадения двух повторен}, форми- руемьй первым c TviHaтором 12, и сигнал стирания выявлений вторым пороговым блоком 8. В абсолютном большинстве случаев это соответствует исправлению искаженной комбинации.

Формула изобретения

1 о Устройство для исправления ошибок в кодовой комбинации по авт. св. № 1324089, отличающееся тем, что, с целью повьш1ения помехоустойчивости, выход блока сравнения -подсоединен к дополнительному входу второго порогового блока.

пороговый блок содержит последова-

тельно соединенные блок опорного напряжения, первый управляемый усилитель, первый компаратор и суммапороговый блок содержит последова-

пороговый блок содержит последова-

тор по модулю два, последовательно соединенные второй управляемый усиитель и второй компаратор, выход которого подсоединен к второму входу сумматора по модулю два, информационный вход второго управляемого

усилителя подключен к второму выходу блока опорного напряжения, причем объединенные вторые входы первого и второго компараторов, объединенные управляющие входы первого и второго

управляемых усилителей и выход суматора по модулю два являются соответственно входом, дополнительным входом и выходом второго порогового блока

Vn j

Vm - M

Редактор И. Шулла

Составитель В, Орлов

Техред М.Дидык Корректор Т.Колб

Заказ 4707/55

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг.г

сриг.З

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-07—Публикация

1987-06-15—Подача