Изобретение относится к электросвязи и может быть использовано в atma. ратуре передачи - приема дискретной информации. Известно устройство для исправления ошибок в кодовой комбинации, содержащее последовательно соединенные первый пороговый блок, первый ключ, первый сумматор по модулю два, элемент И, второй сумматор по модулю даа, первый элемент ИЛИ и блок обнаруженияошибок, а также второ й пороговый блок и последовательно соединенные второйэлемент ИЛИ и накопитель, при этом входы первого и второго пороговьк блоков обье динены, а выход второго блока подключен к второму Bxoty эшмента И, первый и второй выходы первого ключа подсоединены соответственно к вторым входам второго сумматора по модулю два и первого элемента ИЛИ l. Однако известное устройство характеризуется низкой помехоустойчивостью. .Цель изобретения - повышение помех о устойчивости. Поставленная цель достигается тем, что в устройство для исправления ошибок в кодсйой последовательности, содержащее последовательно соединенные первый пороговый блок, первый ключ, первый сумматор по модулю два, элемент И, второй сумматор по модулю два, первый элемент ИЛИ и блок обнаружения ошибок, а также второй пороговый блок и последовательно соединенные второй элемент ИЛИ и накопитель, при этом входы первого и второго пороговых блоков объединены, а выход второго порогового блока подключен к второму входу элемента И, первый и второй выходы первого ключа подсоединены соответственно к вторым входам второго сумматора по модулю два и пе даого элемента ИЛИ, введены второй ключ и последовательно, соединенные третий сумматор по модулю дав Н элемент ЗАПРЕТ ,, выхоа которого подключен к первому входу вто-

3944

рого элемента ИЛИ, к второму входу которого подключен первый выход блока обнаружения ошибок, второй выход которого подключен к второму входу первого ключа, второму входу элемента ЗАПРЕТ, тре- $ тьему Bxotv второго элемента ИЛИ и управл5аощему вхо{ второго ключа, к информационному ккору которого подключен выход накопителя, а выходы второго ключа подключены соответственно к третьему Ю вхору первого элемента ИЛИ и второму входу первого сумматора по модулю два, при этом к входам третьего сумматора по модулю два подключены выходы первого и второго пороговых блоков.15

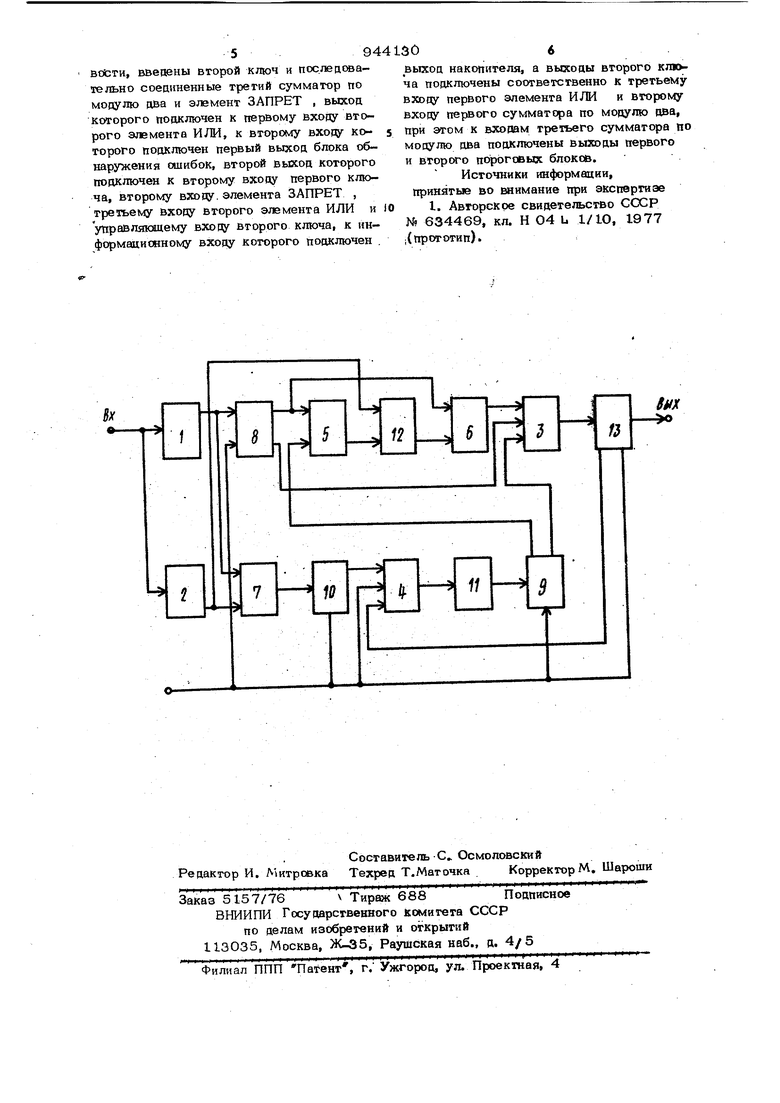

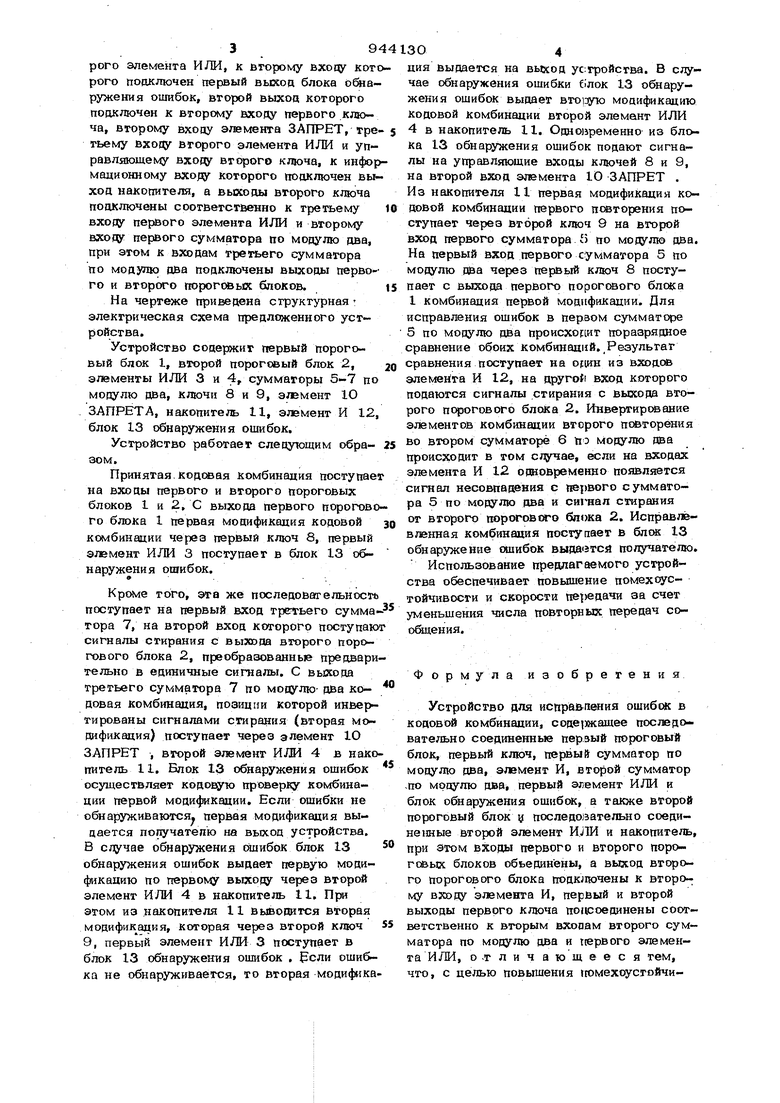

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство содержит первый пороговый блок I, второй пороговый блок 2, 20 элементы ИЛИ 3 и 4, сумматоры 5-7 по модулю два, ключи 8 и 9, эшмент 1О ЗАПРЕТА, накопитель 11, элемент И 12, блок 13 обнаружения ошибок.

Устройство работает следующим обра- 25 аом.

Принятая.кодовая комбинация поступает на входы первого и второго пороговых блоков 1 и 2, С выхода первого порогового блока 1 первая модификация кодовой зо комбинации через первый ключ 8, первый элемент ИЛИ 3 поступает в блок 13 обнаружения ошибок.

Кроме того, эта же последовательность поступает на первый вход третьего сумматора 7, на второй вход которого поступают сигналы стирания с выхода второго порогового блока 2, преобразованные предварительно в единичные сигналы. С выхода третьего сумматора 7 по модулю- два ко- довая комбинация, позиции которой инве тированы сигналами стирания {вторая Mtvдификадия) поступает через элемент 1О ЗАПРЕТ , второй элемент ИЛИ 4 в накопитель 11. Блок 13 обнаружения ошибок осуществляет кодовую проверку комбинации первой моди кации. Если ошибки не обнаруживаются, первая модификация выдается попучатепю на выход устройства. В случае обнаружения сшибок блок 13 50 обнаружения ошибок выдает первую модификацию по первому выходу через второй элемент ИЛИ 4 в накопитель 11. При этом из накопителя 11 выводится вторая модифик ация, которая через второй ключ 55 9, первый элемент ИЛИ 3 поступает в блок 13 обнаружения ошибок . рели ошибка не обнаруживается, то вторая модифяка304

ция выдается на вьссод устройства. В случае обнаружения ошибки €1лок 13 обнаружения ошибок выдает BTOIDUTO модификацию кодовой комбинации второй элемент ИЛИ

4в накопитель 11. Одно1феменно из блока 13 обнаружения ошибок подают сигналы на управляющие входы ключей 8 и 9, на второй вход элемента 10 ЗАПРЕТ . Из накопителя 11 первая модификация кодовой комбинации первого повторения поступает через второй ключ 9 на второй вход первого сумматора 5 по модулю два. На первый вход первого сумматора 5 по модулю два через первый кгаоч 8 поступает с выхода первого порогового блсяса

1 комбинация первой модификации. Для исправления ошибок в первом сумматоре

5по модулю дэа происходит поразрядное равнение обоих комбинаций.,Результат равнения поступает на ояин из входов лемента И 12, на другой: вход которого подаются сигналы стирания с выхода второго порогового блока 2. Инвертирсеание элементов комбинации второго повторения о втором сумматоре 6 по модулю два происходит в том случае, если на входах элемента И 12 одновременно появляется игнал несовпадения с первого сумматора 5 по модулю два и сигнал стирания

от второго пороговеяо блока 2. Исправлевленная комбинация поступает в блок 13 обнаружение ошибок выдаитсй получателю.

Использование предлагаемого устройства обеспечивает повышение помехоустойчивости и скорости пе юдачи за счет уменьшения числа повторных передач .

Формула изобретения

Устройство для испра&пения ошибок в кодовой комбинации, соде| кащее последовательно соединенные перзый пороговый блок, первый ключ, первы сумматор по модулю два, элемент И, второй сумматор ,по модулю два первый элемент ИЛИ и блок обнаружения ошибсж, а также второй пороговый блок у последо)зательно соедине1шые второй элемент ИЛИ и накопитель, при этом входы первого и второго пороговых блоков объединены, а выход второго порогового блока подключены к второму входу элемента И, первый и второй выходы первого ключа подсоединены соответственно к вторым вхооам второго сумматора по модулю два и ttepBoro элемента ИЛИ, о-тличающееся тем, что, с целью повышения помехоустойчивоьти, в&еоены второй ключ и последовательно соединенные третий сумматор по модулю два и элемент ЗАПРЕТ , выход которого подключен к первому входу второго элемента ИЛИ, к второму вхоцу которого подключен первый выход блока обнаружения ошибок, второй выход которого подключен к второму входу первого ключа, второму входу, элемента ЗАПРЕТ , третьему вхору второго элемента ИЛИ и управлягющему входу второго ключа, к информационному входу которого подключен

выход накопителя, а выходы второго ключа подключены соответственно к третьему входу первого элемента ИЛИ и второму входу первого сумматора по модулю два, при этом к входам третьего сумматора по модулю два подключены выходы первого и второго пфогсеых блоков.

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР № 634469, кл. Н 04 L I/IO, 1977 i( прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в кодовой комбинации | 1991 |

|

SU1830616A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1977 |

|

SU634469A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1987 |

|

SU1499503A2 |

| Устройство для исправления и обнаружения ошибок | 1980 |

|

SU921106A2 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1976 |

|

SU604170A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1986 |

|

SU1324089A2 |

| Устройство для обнаружения ииСпРАВлЕНия ОшибОК B КОдОВОйКОМбиНАции | 1979 |

|

SU801283A2 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1974 |

|

SU540389A1 |

Авторы

Даты

1982-07-15—Публикация

1980-12-29—Подача