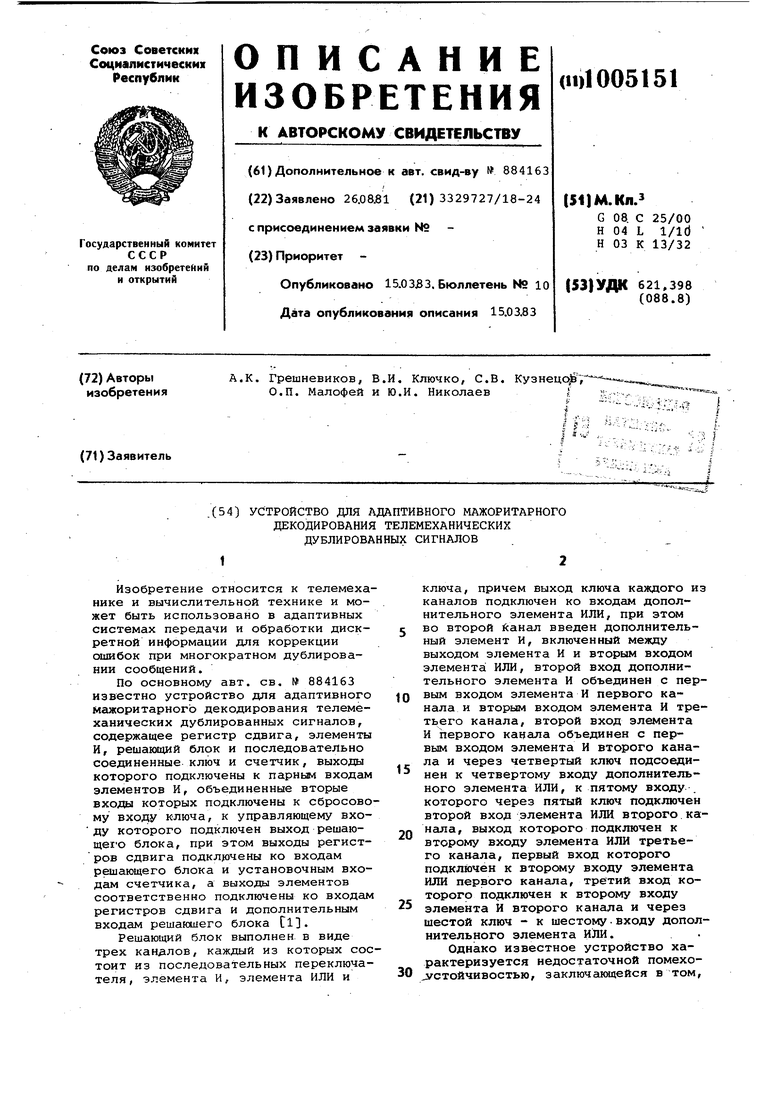

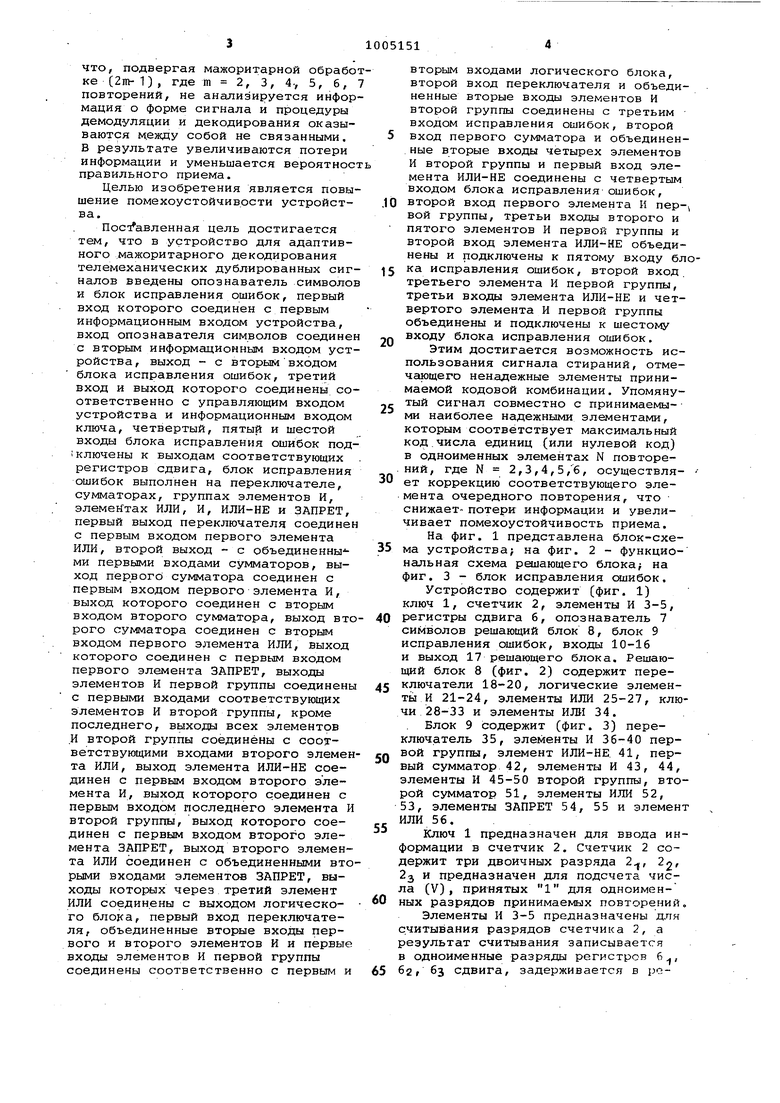

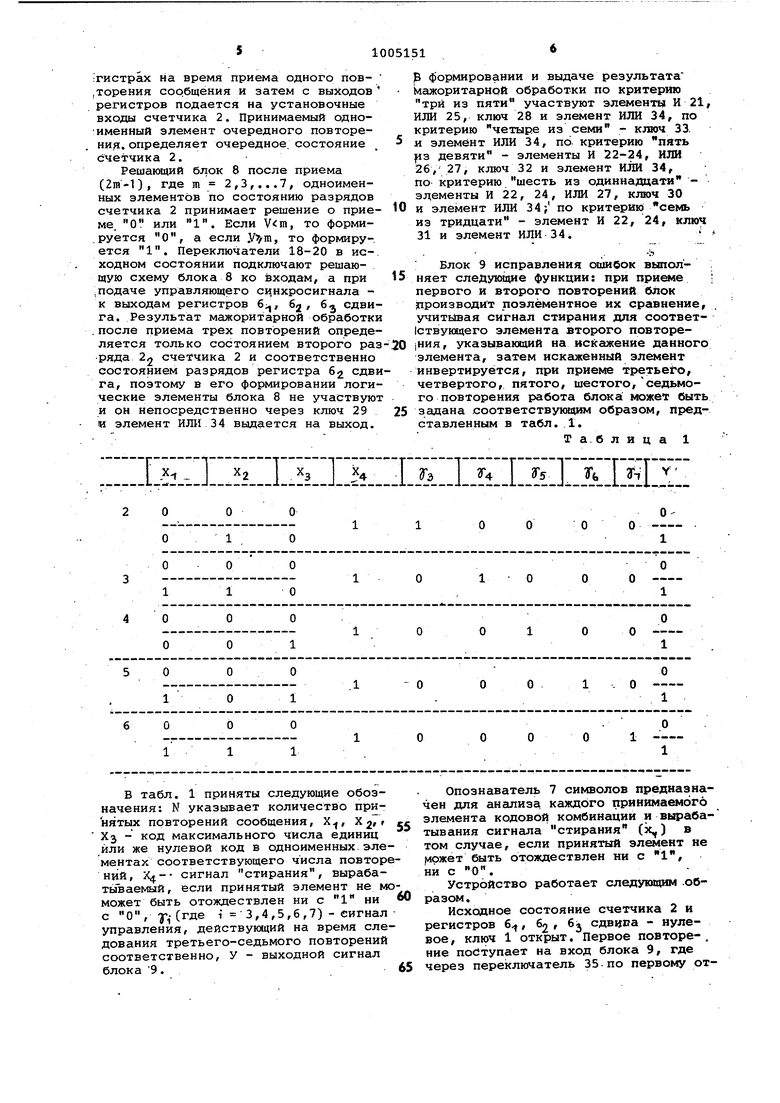

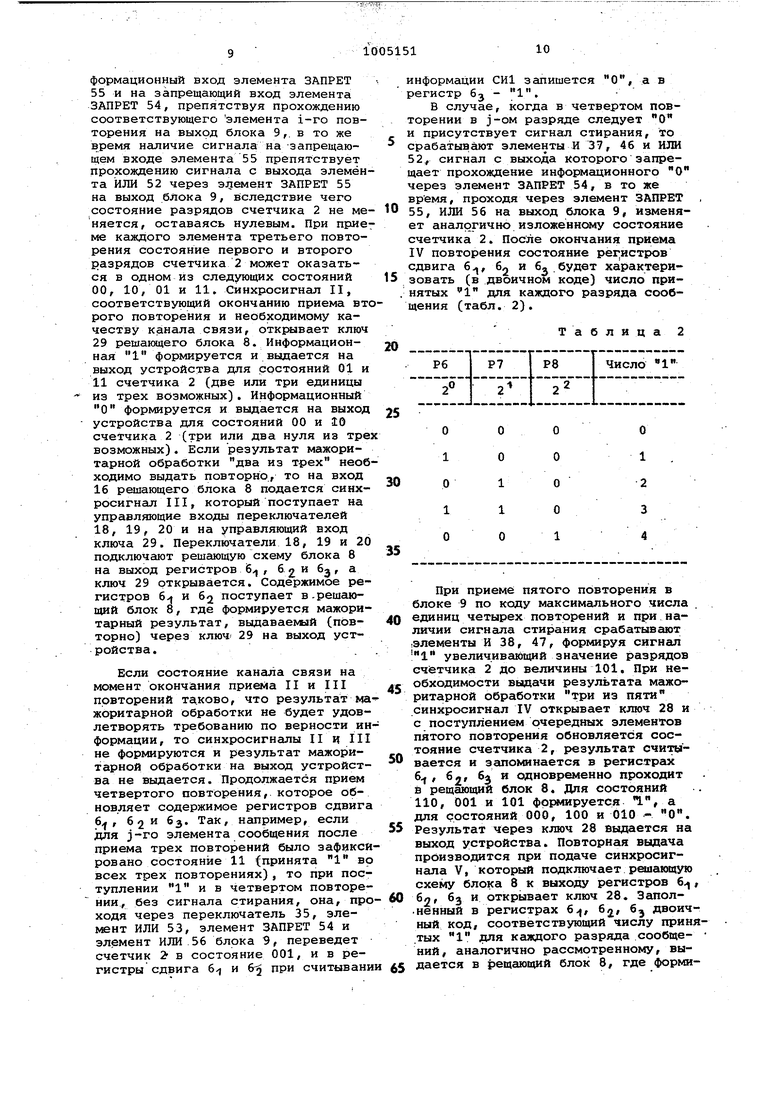

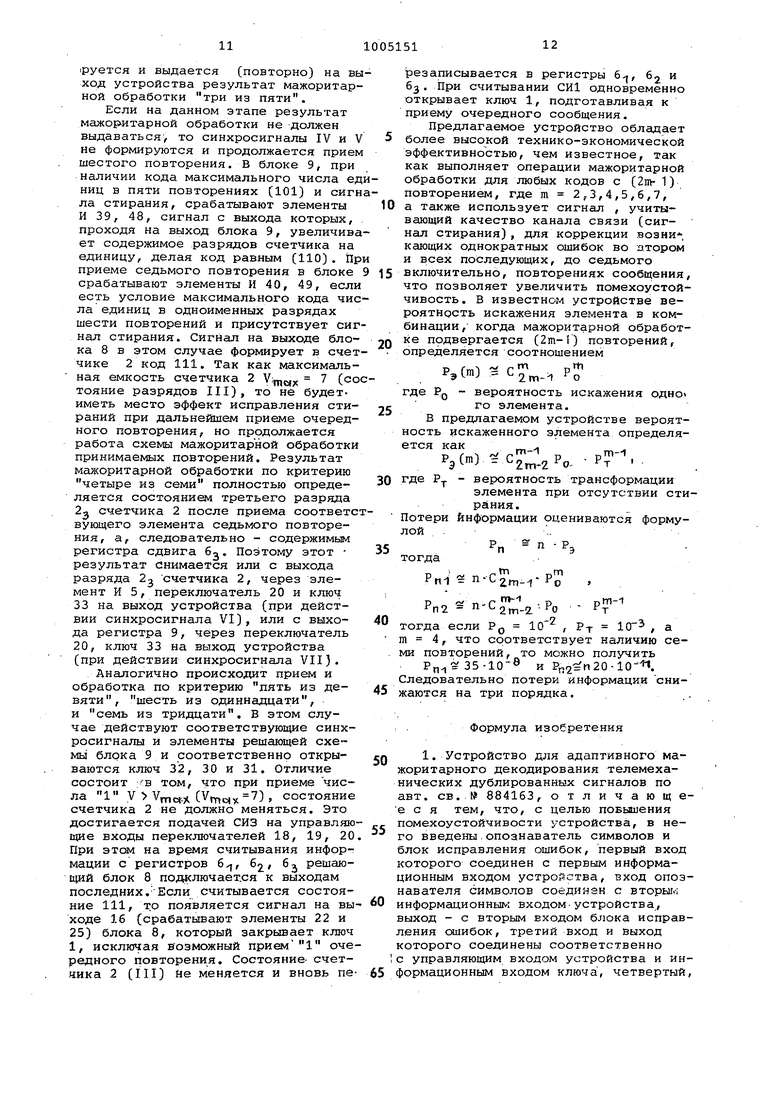

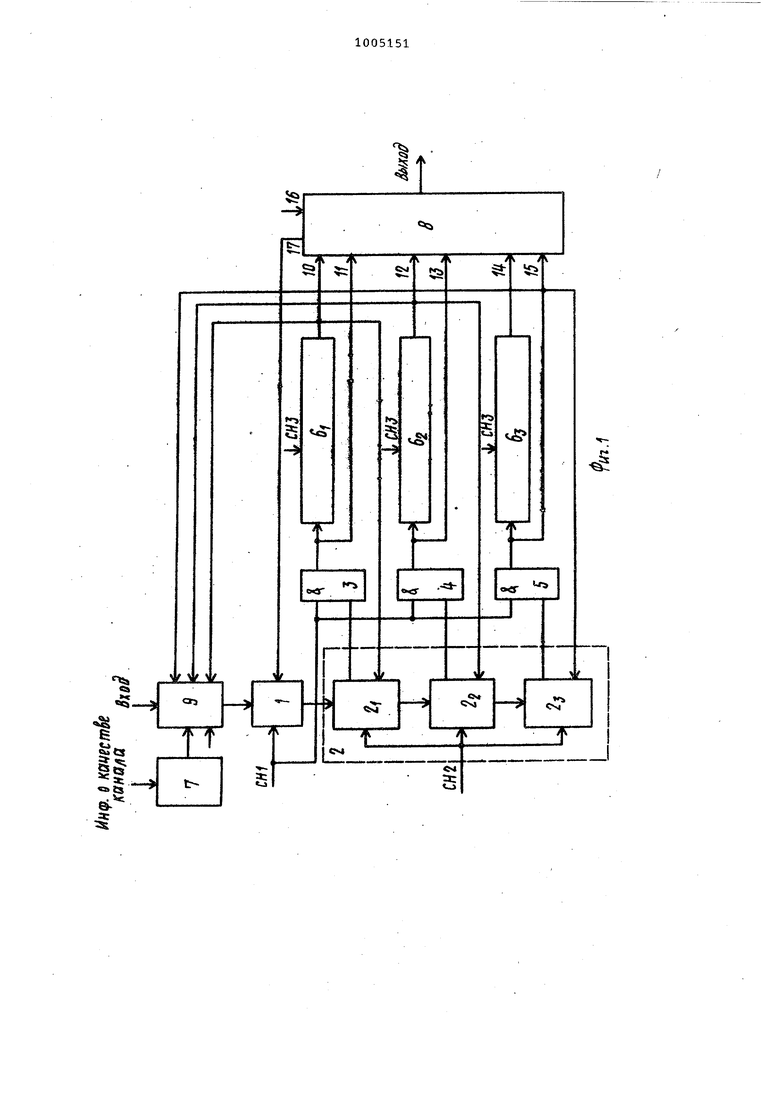

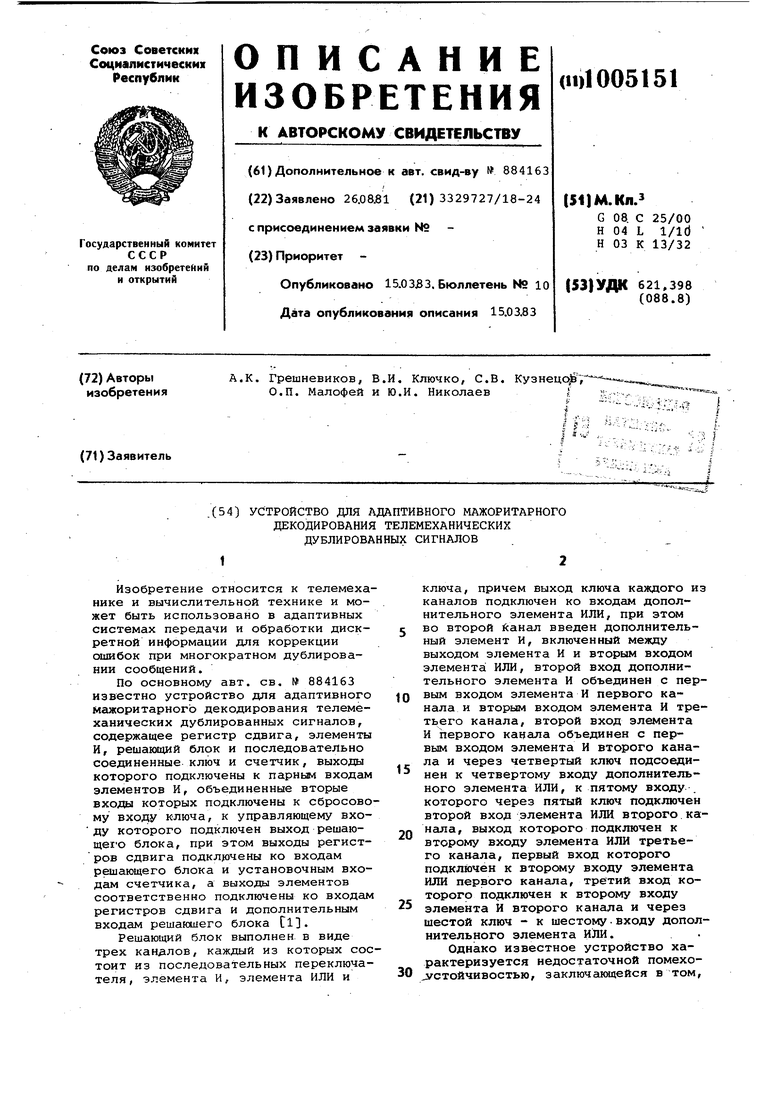

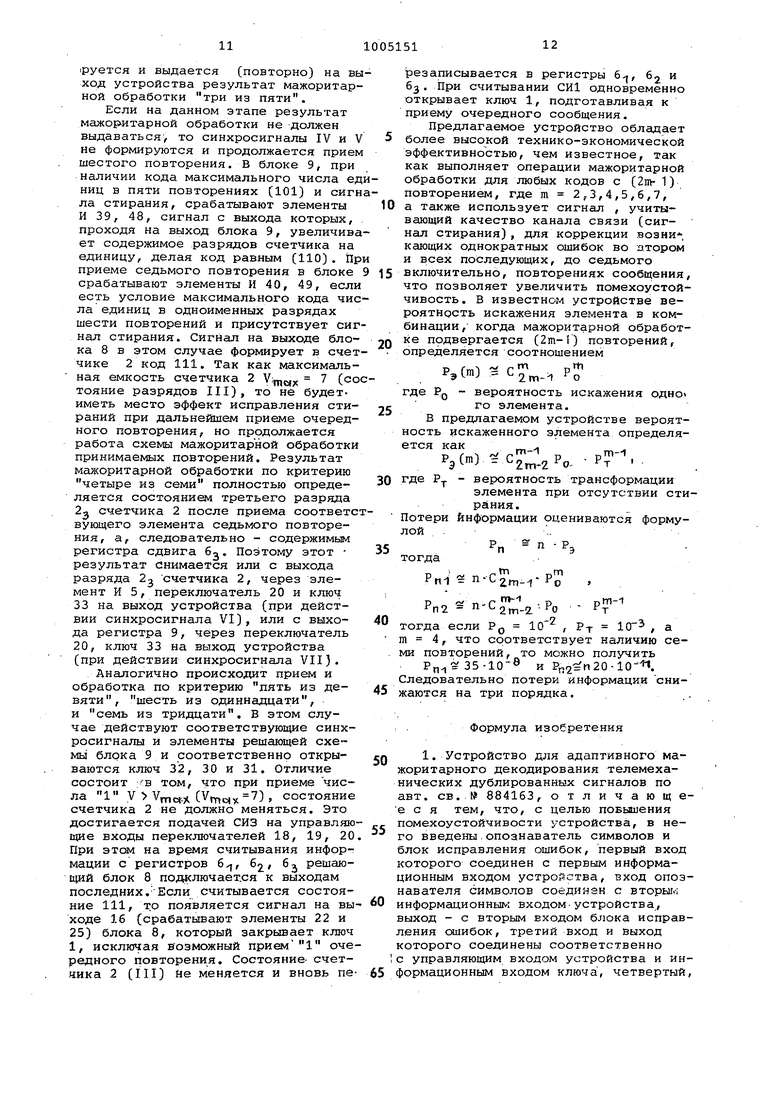

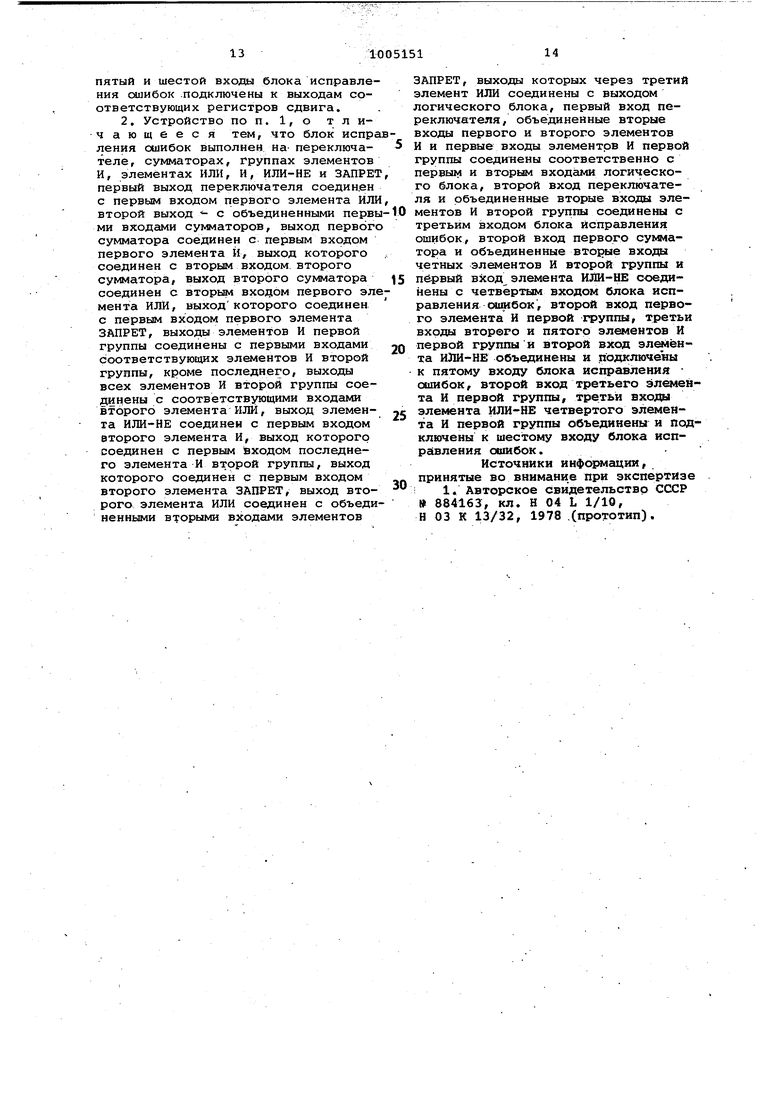

что, подвергая мажоритарной обраб ке (2т- 1 ), где m 2, 3, 4-, 5, б, повторений, не анализируется инфо мация о форме сигнала и процедуры демодуляции и декодирования оказы ваются между собой не связанными. В результате увеличиваются потери информации и уменьшается вероятно правильного приема. Целью изобретения является повы шение помехоустойчивости устройства. Пост авленная цель достигается тем, что в устройство для адаптивного мажоритарного декодирования телемеханических дублированных сиг налов введены опознаватель символо и блок исправления ошибок, первый вход которого соединен с первым информационным входом устройства, вход опознавателя символов соедине с вторым информационным входом уст ройства, выход - с вторымвходом блока исправления ошибок, третий вход и выход которого соединены со ответственно с управляющим входом устройства и информационным входом ключа, четвертый, пятый и шестой входы блока исправления ошибок под ключены к выходам соответствующих регистров сдвига, блок исправления ошибок выполнен на переключателе, сумматорах, группах элементов И, элементах ИЛИ, И, ИЛИ-НЕ и ЗАПРЕТ первый выход переключателя соедине с первым входом первого элемента ИЛИ, второй выход с объединенными первыми входами сумматоров, выход первого сумматора соединен с первым входом первого элемента И, выход которого соединен с вторым входом второго сумматора, выход вт рого сумматора соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом первого элемента ЗАПРЕТ, выходы элементов И первой группы соединен с первыми входами соответствующих элементов И второй группы, кроме последнего, выходы всех элементов И второй группы соединены с соответствующими входами второго элеме та ИЛИ, выход элемента ИЛИ-НЕ соединен с первым входом второго элемента И, выход которого соединен с первым входом последнего элемента второй группы, выход которого соединен с первым входом второго элемента ЗАПРЕТ, выход второго элемен та ИЛИ соединен с объединенными вт рыми входами элементов ЗАПРЕТ, выходы которых через третий элемент ИЛИ соединены с выходом логического блока, первый вход переключателя, объединенные вторые входы первого и второго элементов И и первы входы элементов И первой группы соединены соответственно с первым вторым входами логического блока, второй вход переключателя и объединенные вторые входы элементов И второй группы соединены с третьим входом исправления ошибок, второй вход первого сумматора и объединенные вторые входы четырех элементов И второй группы и первый вход элемента ИЛИ-НЕ соединены с четвертым входом блока исправления ошибок, второй вход первого элемента И nep-j вой группы, третьи входы второго и пятого элементов И первой группы и второй вход элемента ИЛИ-НЕ объединены и подключены к пятому входу блока исправления ошибок, второй вход третьего элемента И первой группы, третьи входы элемента ИЛИ-НЕ и четвертого элемента И первой группы объединены и подключены к шестому входу блока исправления ошибок. Этим достигается возможность использования сигнала стираний, отмечающего ненадежные элементы принимаемой кодовой комбинации. Упомянутый сигнал совместно с принимаемыми наиболее надежными элементами, которым соответствует максимальный ко.числа единиц (или нулевой код) в одноименных элементах N повторений, где N 2,3,4,5/6, осуществля- - ет коррекцию соответствующего элемента очередного повторения, что снижает- потери информации и увеличивает помехоустойчивость приема. На фиг. 1 представлена блок-схема устройства; на фиг. 2 функциональная схема раиающего блока; на фиг. 3 - блок исправления ошибок. Устройство содержит (фиг. 1) ключ 1, счетчик 2, элементы И 3-5, регистры сдвига б, опознаватель 7 символов решающий блок 8, блок 9 исправления ошибок, входы 10-16 и выход 17 решающего блока. Решающий блок 8 (фиг. 2) содержит переключатели 18-20, логические элементы И 21-24, элементы ИЛИ 25-27, ключи 28-33 и элементы ИЛИ 34. . Блок 9 содержит (фиг. 3) переключатель 35, элементы И 36-40 первой группы, элемент ИЛИ-НЕ 41, первый сумматор 42, элементы И 43, 44, элементы И 45-50 второй группы, второй сумматор 51, элементы ИЛИ 52, 53, элементы ЗАПРЕТ 54, 55 и элемент ИЛИ 56. Ключ 1 предназначен для ввода информации в счетчик 2. Счетчик 2 содержит три двоичных разряда 2, 22, 2з и предназначен для подсчета числа (V), принятых 1 для одноименных разрядов принимаемых повторений. Элементы И 3-5 предназначены для считывания разрядов счетчика 2, а результат считывания записывается в одноименные разряды регистров 6, б2г 6з сдвига, задерживается в рогистрах на время приема одного пов|Торения сообщения и затем с выходов регистров подается на установочные входы счетчика 2. Принимаемый одноименный элемент очередного повторения, определяет очередное, состояние счетчика 2.

Решакяций блок 8 после приема (Zm-l), где m 2,3,,..7, одноименных элементов по состоянию разрядов счетчика 2 принимает решение о приеме. О или 1. Если , то форми.руется О, а если , то формируется 1. Переключатели 18-20 в ис-. ходном состоянии подключают решающую схему блока 8 ко входам, а при

подаче управляющего синхросигнала к выходам регистров 6, 6, 6 сдвига. Результат мажоритарной обработки

.после приема трех повторений определяется только состоянием второго разряда 2 счетчика 2 и соответственно состоянием разрядов регистра 6 сдвига, поэтому в его формировании логические элементы блока 8 не участвуют и он непосредственно через ключ 29 и элемент ИЛИ 34 выдается на выход.

Э формировании и выдаче результата Мажоритарной обработки по критерию три из пяти участвуют элементы И 21, ИЛИ 25, ключ 28 и элемент ИЛИ 34, по критерию четыре из семи - ключ 33. и элемент ИЛИ 34, по критерию пять рз девяти - элементы И 22-24, ИЛИ 26, 27, ключ 32 и элемент ИЛШ 34, по критерию шесть из одиннадцати элементы И 22, 24, ИЛИ 27, ключ 30 и элемент ИЛИ 34; по критерию семь из тридцати - элемент И 22, 24, ключ 31 и элемент ИЛИ-34.

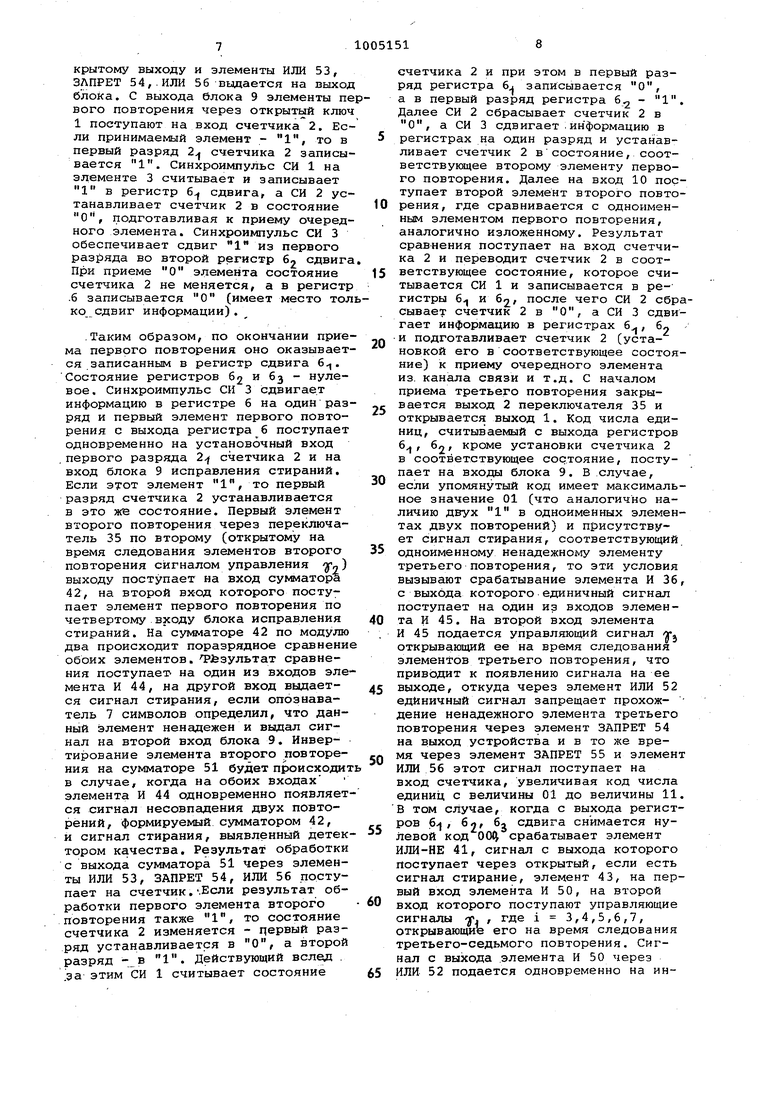

; Блок 9 исправления ошибок выполняет следующие функции: при приеме | первого и второго повторений блок :производит поэлёментное их сравнение, учитывая сигнал стирания для соответствую1цего элемента второго повторе{Ния, указывающий на искажение данного элемента, затем искаженный элемент инвертируется, при приеме TpeTbeiro, четвертого, пятого, шестого,седьмого повторения работа блока может быть задана соответствующим образом, представленным в табл..1.

Т а. блица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Устройство для приема и мажоритарного декодирования информации | 1981 |

|

SU980114A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Устройство для мажоритарного декодирования | 1982 |

|

SU1073788A1 |

| Устройство для приема и мажоритарного декодирования информации | 1988 |

|

SU1562977A2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ СИГНАЛА СТИРАНИЯ | 2001 |

|

RU2208907C2 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

В табл. 1 приняты следующие обозначения: N указывает количество принятых повторений сообщения, Х, 55 Хз - код максимального числа единиц или же нулевой код в одноименных, элементах соответствующего числа повторений, ХФ-- сигнал стирания, вырабатыЪаемый, если принятый элемент не моможет быть отождествлен ни с 1 ни оО с О, т -Сгде i 3,4,5,6,7) - сигнал управления, действующий на время следования третьего-седьмого повторений соответственно, У - выходной сигнал блока 9.65

Опознаватель 7 символов предназначен для анализа каждого принимаемого элемента кодовой комбинации и вырабатывания сигнала стирания (х,) в том случае, если принятый элемент не (14ржет быть отождествлен ни с 1,

О

ни с

Устройство работает следующим .образом.

Исходное состояние счетчика 2 и регистров 6, 2 3 - нулевое , ключ 1 открыт. Первое повторе- , ние поступает на вход блока 9, где через переключатель 35.по первому открытому выходу и элементы ИЛИ 53, ЗАПРЕТ 54,.ИЛИ 56 выдается на выход блока. С выхода блока 9 элементы певого повторения через открытый ключ 1 поступают на вход счетчика 2. Если принимаемый элемент - 1, то в первый разряд 2 счетчика 2 записывается 1. Синхроимпульс СИ 1 на элементе 3 считывает и записывает 1 в регистр 6 сдвига, а СИ 2 устанавливает счетчик 2 в состояние О, подготавливая к приему очередного элемента. Синхроимпульс СИ 3 обеспечивает сдвиг 1 из первого разряда во второй регистр б, сдвига При приеме О элемента состояние счетчика 2 не меняется, а в регистр .6 записывается О (имеет место толко, сдвиг информации).

.Таким образом, по окончании приема первого повторения оно оказывается записанным в регистр сдвига 6. Состояние регистров 62 и 63 - нулевое. Синхроимпульс СИ 3 сдвигает информацию в регистре 6 на один разряд и первый элемент первого повторения с выхода регистра 6 поступает одновременно на установочный вход

,первого разряда 2 счетчика 2 и на вход блока 9 исправления стираний. Если этот элемент 1, то первый разряд счетчика 2 устанавливается в это же состояние. Первый элемент второго повторения через переключатель 35 по второму (открытому на время следования элементов второго повторения сигналом управления у„) выходу поступает на вход сумматора 42, на второй вх-сд которого поступает элемент первого повторения по четвертому входу блока исправления стираний. На сумматоре 42 по модулю два происходит поразрядное сравнение обоих элементов.Фйзультат сравнения поступает на один из входов элемента И 44, на другой вход вьщается сигнал стирания, если опознаватель 7 символов определил, что данный элемент ненадежен и выдал сигнал на второй вход блока 9. Инвертирование элемента второго повторения на сумматоре 51 будет происходит в случае, когда на обоих входах элемента И 44 одновременно появляется сигнал несовпадения двух повторений, формируемый сумматором 42, и сигнал стирания, выявленный детектором качества. Результат обработки с выхода сумматора 51 через элементы ИЛИ 53, ЗАПРЕТ 54, ИЛИ 56 поступает на счетчик..Если результат обработки первого элемента второго повторения также 1, то состояние счетчика 2 изменяется - первый разряд устанавливается в О, а второй разряд - в 1. Действующий вслед

эа этим СИ 1 считывает состояние

счетчика 2 и при этом в первый разряд регистра 6а записывается О, а в первый разряд регистра б. - 1 Далее СИ 2 сбрасывает счетчик 2 в О, а СИ 3 сдвигает . информацию в регистрах на один разряд и устанавливает счетчик 2 в состояние, соответствукнцее второму элементу первого повторения. Далее на вход 10 поступает второй элемент второго повторения, где сравнивается с одноименным элементом первого повторения, аналогично изложенному. Результат сравнения поступает на вход счетчика 2 и переводит счетчик 2 в соответствующее состояние, которое считывается СИ 1 и записывается в регистры 6 и 62/ после чего СИ 2 сбрсывает счетчик 2 в О, а СИ 3 сдвигает информацию в регистрах б, 6,, и подготавливает счетчик 2 (установкой его в соответствующее состояние) к приему очередного элемента из. канала связи и т.д. С началом приема третьего повторения закрывается выход 2 переключателя 35 и открывается выход 1. Код числа единиц, считываемый с выхода регистров 6, 62/ кроме установки счетчика 2 в соответствующее состояние, поступает на входы блока 9. В случае, если упомянутый код имеет максимальное значение 01 (что аналогично наличию двух 1 в одноименных элементах двух повторений) и присутств.ует сигнал стирания, соответствующий одноименному ненадежному элементу третьего повторения, то эти условия вызывают срабатывание элемента И 36 с выхода которого единичный сигнал поступает на один из входов элемента И 45. На второй вход элемента И 45 подается управляющий сигнал -j-j открывающий ее на время следования элементов третьего повторения, что приводит к появлению сигнала на ее выходе, откуда через элемент ИЛИ 52 единичный сигнал запрещает прохождение ненадежного элемента третьего повторения через элемент ЗАПРЕТ 54 на выход устройства и в то же время через элемент ЗАПРЕТ 55 и элемен ИЛИ 56 этот сигнал поступает на вход счетчика, увеличивая код числа единиц с величины 01 до величины 11 В том случае, когда с выхода регистров 6-J , б-, б, сдвига снимается нулевой код 00( срабатывает элемент ИЛИ-НЕ 41, сигнал с выхода которого поступает через открытый, если есть сигнал стирание, элемент 43, на первый вход элемента И 50, на второй вход которюго поступают управляющие сигналы f. , где i 3,4,5,6,7, открывающие его на время следования третьего-седьмого повторения. Сигнал с выхода .элемента И 50 через ИЛИ 52 подается одновременно на информационный вход элемента ЗАПРЕТ 55 и на запрещающий вход элемента ЗАПРЕТ 54, препятствуя прохождению соответствующего элемента i-ro повторения на выход блока 9,. в то же время наличие сигнала на -запрещающем входе элемента 55 препятствует прохождению сигнала с выхода элемен та ИЛИ 52 через sJieMeHT ЗАПРЕТ 55 на выход блока 9, вследствие чего состояние разрядов счетчика 2 не ме няется, оставаясь нулевым. При прие ме каждого элемента третьего повторения состояние первого и второго разрядов счетчика 2 может оказаться в одном из следующих состояний 00, 10, 01 и 11, СГинхросигнал II, соответствующий окончанию приема вт рого повторения и необходимому качеству канала связи, открывает ключ 29 решающего блока 8. Информационная 1 формируется и выдается на выход устройства для состояний 01 и 11 счетчика 2 (две или три единицы из трех возможных). Информационный О формируется и выдается на выход устройства для состояний 00 и 10 счетчика 2 (три или два нуля из тре возможных). Если результат мажоритарной обработки два из трех необ ходимо выдать повторно., то на вход 16 решающего блока 8 подается синхросигнал III, который поступает на управляющие входы переключателей 18, 19, 20 и на управляющий вход ключа 29. Переключатели 18, 19 и 20 подключают решающую схему блока 8 на выход регистров 6,, , 6 и 6, а ключ 29 открывается. Содержимое регистров б( и б2 поступает в.решающий блок 8, где формируется мажоритарный результат, выдаваелий (повторно) через КЛЮЧ 29 на выход устройства. Если состояние канала связи на момент окончания приема II и III повторений та.ково, что результат ма жоритарной обработки не будет удовлетворять требованию по верности ин формации, то синхросигналы II и III не формируются и результат мажоритарной обработки на выход устройства не выдается. Продолжается прием четвертого повторения, которое обновляет содержимое регистров сдвига 6- , б2 и 63. Так, например, если для j-ro элемента сообщения после приема трех повторений было зафикси ровано состояние 11 принята 1 во всех трех повторениях), то при пос туплении 1 и в четвертом повторении, без сигнала стирания, она, про ходя через переключатель 35, элемент ИЛИ 53, элемент ЗАПРЕТ 54 и элемент ИЛИ.56 блока 9, переведет счетчик 2- в состояние 001, и в регистры сдвига 6-J и 6-2 при считывани информации СИ1 запишется О, а в регистр БЗ В случае, когда в четвертом повторении в J-OM разряде следует О и присутствует сигнал стирания, то срабатывают элементы И 37, 46 и ИЛИ 52 сигнал с выхода которого запрещает прохождение информационного О через элемент ЗАПРЕТ 54, в то же время, проходя через элемент ЗАПРЕТ 55, ИЛИ 56 на выход блока 9, изменяет аналогично изложенному состояние счетчика 2. После окончания приема IV повторения состояние рег.истров сдвига 6, 6 и 6 будет характеризовать (в двоичном коде) число принятых 1 для каждого разряда сообщения (табл. 2). Таблица 2 При приеме пятого повторения в блоке 9 по коду максимального числа единиц четырех повторений и при наличии сигнала стирания срабатывают элементы И 38, 47, формируя сигнал увеличивайщий значение разрядов счётчика 2 до величины 101. При необходимости выдачи результата мажоритарной обработки три из пяти синхросигнал IV открывает ключ 28 и с поступлением очередных элементов пятого повторения обновляется состояние счетчика 2, результат считывается и запоминается в регистрах 6, б-г 6j и одновременно проходит в рещающий блок 8. Для состояний 110, 001 и 101 формируется 1, а для состояний 000, 100 и 010 - О. Результат через ключ 28 выдается на выход устройства. Повторная выдача производится при подаче синхросигнала V, который подключает роиающую схему блока 8 к выходу регистров б-, 2, 63 и открывает ключ 28. Запол ненный в регистрах 6-(, 62 6j двоичный код, соответствующий числу приня тых 1 для каждого разряда сообщений, аналогично рассмотренному, выдается в рещающий блок 8, где формиipyeTCH и выдается (повторно) на вы ход устройства результат мажоритар ной обработки три из пяти. Если на данном этапе результат мажоритарной обработки не должен выдаваться то синхросигналы IV и V не формируются и продолжается прием шестого повторения. В блоке 9, при наличии кода максимального числа ед ниц в пяти повторениях (101) и сиг ла стирания, срабатывают элементы И 39, 48, сигнал с выхода которых, проходя на выход блока 9, увеличива ет содержимое разрядов счетчика на единицу, делая код равным (110). Пр приеме седьмого повторения в блоке срабатывают элементы И 40, 49, если есть условие максимального кода чис ла единиц в одноименных разрядах шести повторений и присутствует сиг нал стирания. Сигнал на выходе блока 8 в этом случае формирует в счет чике 2 код 111. Так как максимальная емкость счетчика 2 Vi..- 7 (со тояние разрядов III), то не будет иметь место эффект исправления стираний при дальнейшем приеме очередного повторения, но продолжается работа схемы мажоритарной обработки принимаемых повторений. Результат мажоритарной обработки по критерию четыре из семи полностью определяется состоянием третьего разряда 2 счетчика 2 после приема соответс вующего элемента седьмого повторения, а, следовательно - содержимьам регистра сдвига б. Поэтому этот результат снимается или с выхода разряда 2 счетчика 2, через элемент И 5, переключатель 20 и ключ 33 на выход устройства (при действии синхросигнала VI), или с выхода регистра 9, через переключатель 20, ключ 33 на выход устройства (при действии синхросигнала VII). Аналогично происходит прием и обработка по критерию пять из девяти, шесть из одиннадцати, и семь из тридцати. В этом случае действуют соответствующие синхросигналы и элементы решающей схе Mbi блока 9 и соответственно открываются ключ 32, 30 и 31. Отличие состоит В том, что при приеме числа 1 V Vmwx состояние счетчика 2 не должно меняться. Это достигается подачей СИЗ на управляю щие входы переключателей 18, 19, 20 При этсал на время считывания информации с регистров 6, 62 62 решающий блок 8 подключается к выходам последних. Если считывается состояние 111, т.о появляется сигнал на вы ходе 16 (срабатывают элементы 22 и 25) блока 8, который закрывает ключ 1, исключая возможный прием оче редного повторения. Состояние- счетаика 2 (III) Не меняется и вновь пе резаписывается в регистры б-j, 62 и 63. При считывании СИ1 одновременно открывает ключ 1, подготавливая к приему очередного сообщения. Предлагаемое устройство обладает более высокой технико-экономической эффективностью, чем известное, так как выполняет операции мажоритарной обработки для любых кодов с (2т- 1) повторением, где m 2,3,4,5,6,7, а также использует сигнал , учитывающий качество канала связи (сигнал стирания), для коррекции возни-, кающих однократных ошибок во втором и всех последующих, до седьмого включительно, повторениях сообщения, что позволяет увеличить помехоустойчивость. В известном устройстве вероятность искажения элемента в комбинации , когда мажоритарной обработке подвергается (2т-Г) повторений, определяется соотношением Р fml с Р ijl.mj - о где PQ - вероятность искажения одно го элемента. В предлагаемом устройстве вероятность искаженного элемента определяется как р,(ш),Р, -Ргде Р - вероятность трансформации элемента при отсутствии стирания. Потери информации оцениваются формулой . п -Р, Рп1 n-cJ. .-1 гр2 .2. 0 - т тогда если Р 10 , РТ 10 , а m 4, что соответствует наличию семи повторений, то можно получить Рп 35-10в и Рп2 п20-10-Ч Следовательно потери информации снижаются на три порядка.. Формула изобретения 1. Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов по авт. св. № 884163, отличающее с я тем, что, с целью повышения помехоустойчивости устройства, в него введены.опоанаватель символов и блок исправления ошибок, первый вход которого соединен с первым информационным входом устройства, вход опознавателя символов соединан с вторы -; информационным входом-устройства, выход - с вторым входом блока исправения сшибок, третий вход и выход которого соединены соответственно управляющим входом устройства и инормационным входом ключа, четвертый, пятый и шестой входаа блока исправления сшибок .подключены к выходам соответствующих регистров сдвига. 2. Устройство по п. 1, о т л ичающбеся тем, что блок испр ления ошибок выполнен на- переключателе, сумматорах, группах элементов И, элементах ИЛИ, И, ИЛИ-НЕ и ЗАПРЕ первый выход переключателя соединен с первым входом первого элемента ИЛИ второй выход - с объединенными перв ми входами сумматоров, выход первог сумматора соединен с. первым входом первого элемента И, выход которого соединен с вторым входом, второго сумматора, выход второго сумматора соединен с вторым входом первого эл мента ИЛИ, выход которого соединен с первым входом первого элемента ЗАПРЕТ, выходы элементов И первой группы соединены с первыми входами соответствующих эло« ентов И второй группы, кроме последнего, выходы всех элементов И второй группы соединены с соответствующими входами второго элементаИЛ}, выход элемента ИЛИ-НЕ соединен с первым входом второго элемента И, выход которого соединен с первым входом последнего элемента И второй группы, выход которого соединен с первым входом второго элемента ЗАПРЕТ, выход второго элемента ИЛИ соединен с объеди ненными вторыми входами элементов ЗАПРЕТ, ВЫХОДЫ которых через третий элемент ИЛИ соединены с выходом логического блока, первый вход переключателя, объединенные вторые входы первого и второго элементов И и первые входы элементов И первой группы соединены соответственно с первым и вторым входами логического блока, второй вход переключателя и объединенные вторые входы элементов И второй группы соединены с третьим лвходом блока исправления ошибок, второй вход первого сумматора и объединенные вторые входы четных элементов И второй группы и первый вход элемента ИЛИ-НЕ соединены с четвёртым входом блока исправления ришбок, второй вход первого элемента И первой группы, третьи входы второго и пятого элементов И первой группы и второй вход элемента иШ-НБ объединены и С1одключены к пятому входу блока исправления шшбок, второй вход третьего элемента И первой группы, третьи входы элемента ИЛИ-НЕ четвертого элемента И первой группы объединены и подключены к шестому входу блока испРс1вления ошибок. Источники информации, принятые во внимание при экспертизе i 1. Авторское свидетельство СССР 884163, кл. Н 04 L 1/10, Н 03 К 13/32, 1978 .(прототип).

с5

CS

Sf

IS

5

сэ У

с

г

Авторы

Даты

1983-03-15—Публикация

1981-08-26—Подача