ел

4; д

00 IS9

Изобретение относится к электротехнике и может быть использовано при построении систем управления вентильных электроприводов и инверторов,

Цель изобретения - повышение стабильности амплитуды и уменьшение нелинейных искажений выходных сигналов.

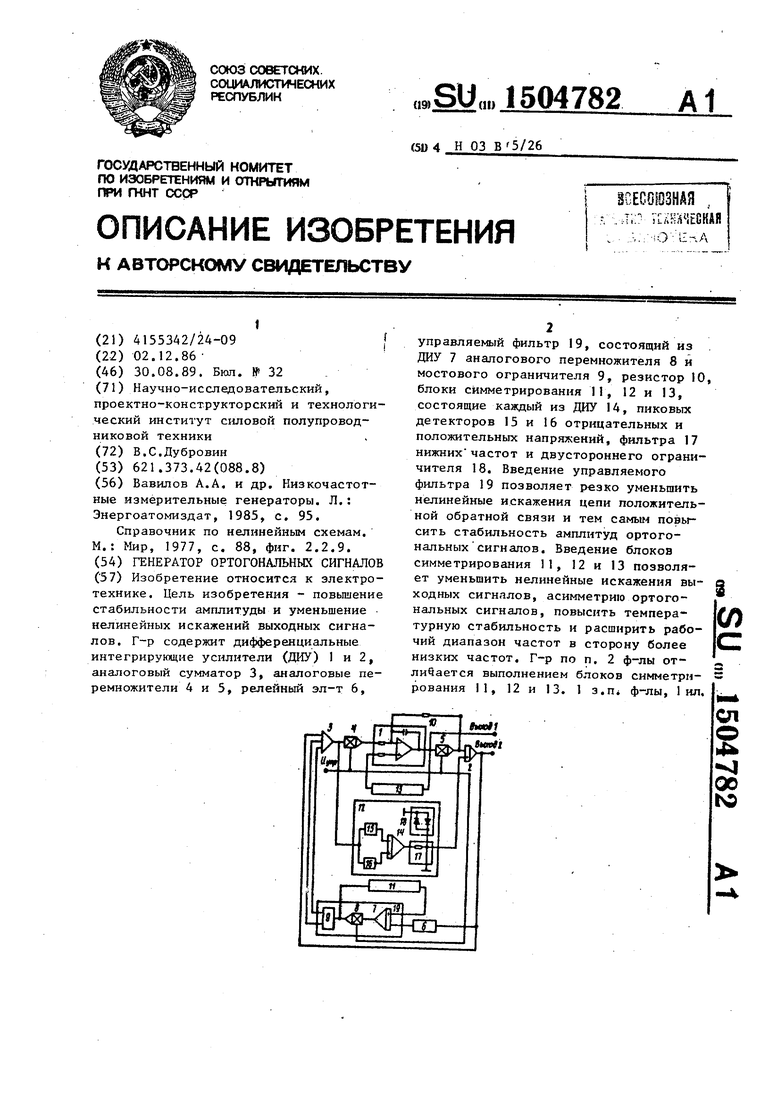

На чертеже приведена структурная электрическая схема генератора ортогональных сигналов.

Генератор ортогональных сигналов содержит первый 1 и ,рторой 2 диффе-. ренциальные интегрирующие усилители, аналоговый сумматор 3, первый 4 и второй 5 аналоговые перемножители, релейный элемент 6, дифференциальный интегрирующий усилитель 7, третий аналоговый перемножитель 8, мостовой ограничитель 9, резистор 10, первый, второй и третий блоки 11-13 симметрирования, каждый из которых содержит дифференциальный интегрирующий усилитель 14, пиковый детектор 15 отрицательных напряжений, пиковый детектор

16положительных напряжений, фильтр

17нижних частот, двусторонний ограничитель 18.

Третий дифференциальный интегрирующий усилитель 7, третий аналоговьш перемножитель 8 и мостовой органичи- тель 9 образуют управляемый фильтр 19

Генератор ортогональных сигналов работает следующим образом.

Первьй 1 и второй 2 дифференциаль ные интегрирующие усилители, охваченные общей отрицательной обратной связью через аналоговьй сумматор 3, образуют линейное колебательное звено, перестраиваемое по частоте с помощью первого 4 и второго 5 аналоговых пе- ремнолителей.

Для обеспечения требуемой стабильности параметров колебательного звена используется внутренняя отрицательная обратная связь - подача сигнала с выхода второго аналогового перемножителя 5 через резистор 10 на дополни- тельньй вход первого дифференциального интегрирующего усилителя 1, Внут ренняя обратная связь, вносит в звено затухание и бнижает за счет этого влияние неидеал ности первого 1 и второго 2 дифференциальных интегрирующих усилителей,

Незатухающий колебательный процес и стабилизация амплитуды колебаний реализованы введением в звено нелинейной обратной связи с помощью реo

0

5

5

30

5 0

5 Q 5

лейного элемента 6, наличие которого обеспечивает перестройку частоты без переходного процесса установления амплитуды колебаний на выходах генератора ортогональных сигналов.

При.изменении частоты коэффициент передачи третьего дифференциального интегрирующего усилителя 7 управляемого фильтра 19 будет изменяться обратно пропорционально частоте, поэтому амплитуда колебаний на выходе третьего дифференциального интегрирующего усилителя 7 также будет изменяться. Чтобы коэффициент передачи управляемого фильтра 19 оставался постоянным (при изменении частоты), последовательно с третьим дифференциальным интегрирующим усилителем 7 включен третий аналоговый перемножитель 8, второй вход которого соединен с выходом второго дифференциального ин- тегриру1ядего усилителя 2. Суммарный коэффициент передачи третьего аналогового перемножителя 8 и третьего дифференциального интегрирующего усилителя 7 будет оставаться постоянным при изменении частоты при условии, что коэффициент передачи третьего аналогового перемножителя 8 будет изменяться по такому же закону, что и коэффициент передачи первого 4 и второго 5 аналоговых перемножителей.. Амплитуда колебании на выходе третьего аналогового перемножителя 8 также будет оставаться постоянной.

Для дальнейшего улучшения фильтрации сигнала нелинейной обратной связи в схему управляемого фильтра I9 дополнительно введен мостовой ограничитель 9, который выполняет следующие функции: исключает третью гармонику в сигнале нелинейной обратной связи, дополнительно стабилизирует сигнал обратной связи, устраняет не симметрию сигнала в цепи нелинейной обратной связи.

Для симметрирования ортогональных сигналов, т.е. устранения внутрифаз- ной асимметрии сигналов, дополнительно введены первый, второй и третий блоки 11 - 13 симметрирования.

При достаточно хорошей форме ортогональных сигналов разность амплитуд положительной U, и отрицательной U полуволн этих сигналов будет определять постоянную составлякщую U на выходе фильтра 17, а следовательно, и внутрифазовую асимметрию. С выхо10

15

20

51504782

дов пиковых детекторов 15 и 16 напряжения подаются на инвертирующий и не- инвертйрукщий соответственно входы дифференциального интегрирукщего уси- лителя 14. Фильтр 17 дополнительно отфильтровывает сигнал дифференциального интегрирующего усилителя 1А, полярность выходного сигнала фильтра 17 и его значение будут определяться разностью положительно и отрицательной полуволн входного напряжения. Постоянные времени дифференциального интегрирующего ус11лителя 14, фильтра 17 и суммарный коэффициент передачи первого, второго и третьего блоков 11-13 симметрирования выбираются из условия обеспечения устойчивой работы и поддержания необходимой статической и динамической ошибок регулирования.

Для увеличения быстродействия к выходу фильтра 7 подключен двусторонний ограничитель 18, который в исходном состоянии (при подаче напря- .жения питания и отсутствии управляющего сигнала) ограничивает напряжение на выходе фильтра 17 на уровне порогового напряжения диодов двустороннего ограничителя 18.

Введение управляемого фильтра позволило резко уменьшить нелинейные искажения цепи положительной обратной связи, увеличить глубину отрицательной обратной связи и тем самым повысить стабильность амплитуд ортогональных сигналов.

Введение первого, второго и третьего блоков 11 - 13 симметрирования позволило уменьшить нелинейные искажения выходных сигналов, симметрию ортогональных сигналов, повысить температурную стабильность и расширить рабочий диапазон частот в сторону бо25

30

тегрирунщего ycs-шителя,, первый анал говый перемножнтель, первый вход ко торого подключен к выходу аналогово го сумматора, а выход которого подключен к неинвертиругадему вход-у пер вого дифференциального интегрирукще го усилителя, второй аналоговьй пер множнтель, первый вход которого под ключен к выходу первого дифференциального интегрирукяцего усилителя, а выход которого подключен к инвертн-- рующему входу второго дифференциаль ного интегрирующего усилителя, рези тор, который включая между выходом второго аналогового пepe шoжитeля и дополнительным входом первого диффе ренциального интегрирующего усилите ля, при зтом выход второго днфферен

циальноц,о интегрирующего усилителя подключен к первому входу аналогово го сумматора, вторые входы первого второго аналоговых перемножителей объединены и являются входом управл НИН частотой генератора ортогонэх;ьк сигналов, о т л Р ti а ю ц и и с. я тем, что, с целью повышения стабиль ности амплитуды и у1меньшенкя келиней ных искажений выходных сигналов, в него введены последовательно соединенные третий днфференциальньй инте рирующий усилитель, третий аналоговый перемножитель и мостовой ограничитель, первьй и второй выходы которого подключены соответственно к вто рому и третьему входам аналогового сумматора, первый блок симметркропа- ния, который включен выходом третьего аналогового перемножителя 40 и неинвертирующим входом третьего

дифференциального интегрирующего усн Лителя, второй блок снмметр 1ронан;1Я, который включен между выходом анало™ гового сумматора и неннзертнрз/ ощим

35

лее низких частот, что-особенно важно 45 входом второго днффере цпального ин- при использовании генератора ортогональных сигналов в управляемых генераторах (генераторах ведущего сигнала) вентильных электроприводов.

тегрирующего усилителя, третий блок симметрирования, который включен ду выходом и инвертнруктдик входом первого дифференциального нптегрирую 5Q щего усилителя, при зтом инвертирующий вход -третьего дифференциального интегрирующего усилителя подключен к выходу релейного элемента, второй вход третьего аналогопого персмножиФормула изобретения

1. Генератор ортогональных сигналов, содержащий аналоговьй сумматор.

5

тегрирунщего ycs-шителя,, первый анало говый перемножнтель, первый вход которого подключен к выходу аналогового сумматора, а выход которого подключен к неинвертиругадему вход-у первого дифференциального интегрирукщего усилителя, второй аналоговьй перемножнтель, первый вход которого подключен к выходу первого дифференци . ального интегрирукяцего усилителя, а выход которого подключен к инвертн-- рующему входу второго дифференциального интегрирующего усилителя, резистор, который включая между выходом второго аналогового пepe шoжитeля и дополнительным входом первого дифференциального интегрирующего усилителя, при зтом выход второго днфферен™

циальноц,о интегрирующего усилителя подключен к первому входу аналогового сумматора, вторые входы первого к второго аналоговых перемножителей объединены и являются входом управле-- НИН частотой генератора ортогонэх;ькык сигналов, о т л Р ti а ю ц и и с. я тем, что, с целью повышения стабильности амплитуды и у1меньшенкя келиней-- ных искажений выходных сигналов, в него введены последовательно соединенные третий днфференциальньй интегрирующий усилитель, третий аналоговый перемножитель и мостовой ограничитель, первьй и второй выходы которого подключены соответственно к второму и третьему входам аналогового сумматора, первый блок симметркропа- ния, который включен выходом третьего аналогового перемножителя и неинвертирующим входом третьего

ифференциального интегрирующего усн ителя, второй блок снмметр 1ронан;1Я, оторый включен между выходом анало™ ового сумматора и неннзертнрз/ ощим

45 входом второго днффере цпального ин-

тегрирующего усилителя, третий блок симметрирования, который включен ду выходом и инвертнруктдик входом первого дифференциального нптегрирую- 5Q щего усилителя, при зтом инвертирующий вход -третьего дифференциального интегрирующего усилителя подключен к выходу релейного элемента, второй вход третьего аналогопого персмножи

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор ортогональных сигналов | 1988 |

|

SU1665490A1 |

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1775820A1 |

| Преобразователь однофазного напряжения в трехфазное | 1991 |

|

SU1786616A1 |

| Генератор ортогональных сигналов | 1990 |

|

SU1702514A1 |

| Устройство для преобразования однофазного напряжения в трехфазное | 1989 |

|

SU1653098A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР | 2012 |

|

RU2506692C1 |

| АДАПТИВНОЕ УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ДВОИЧНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 1998 |

|

RU2134026C1 |

| ФОРМИРОВАТЕЛЬ ГАРМОНИЧЕСКОГО СИГНАЛА | 2015 |

|

RU2565424C1 |

| Приемник фазоманипулированных сигналов | 1985 |

|

SU1261138A1 |

| Формирователь однополосного сигнала | 1990 |

|

SU1753578A1 |

Изобретение относится к электротехнике. Цель изобретения - повышение стабильности амплитуды и уменьшение нелинейных искажений выходных сигналов. Г-р содержит дифференциальные интегрирующие усилители /ДИУ/ 1 и 2, аналоговый сумматор 3, аналоговые перемножители 4 и 5, релейный эл-т 6, управляемый фильтр 19, состоящий из ДИУ 7, аналогового перемножителя 8 и мостового ограничителя 9, резистор 10, блоки симметрирования 11, 12 и 13, состоящие каждый из ДИУ 14, пиковых детекторов 15 и 16 отрицательных и положительных напряжений, фильтра 17 нижних частот и двухстороннего ограничителя 18. Введение управляемого фильтра 19 позволяет резко уменьшить нелинейные искажения цепи положительной обратной связи и тем самым повысить стабильность амплитуд ортогональных сигналов. Введение блоков симметрирования 11,12 и 13 позволяет уменьшить нелинейные искажения выходных сигналов, уменьшить асимметрию ортогональных сигналов, повысить температурную стабильность и расширить рабочий диапазон частот в сторону более низких частот. Г-р по п.2 ф-лы отличается выполнением блоков симметрирования 11, 12 и 13. 1 з.п.ф-лы, 1 ил.

первый дифференциальный интегрирующий 55 соединен с вторыми входами пер- усилитель, второй дифференциаль-ный интегриругаций усилитель, релейньй элемент, вход которого подключен к выходу второго дифференциального инв ого и второго аналоговых перемножителей.

по п. тем.

1 , о т л и - что каждый из

соединен с вторыми входами пер-

в ого и второго аналоговых перемножителей.

по п. тем.

1 , о т л и - что каждый из

715047828

блоков симметрирования содержит диф-ференциальнрго интегрирующего усилиференциальный интегриругадий усили-теля, фильтр нижних частот, вход котель, пиковый детектор отрицательныхторого подключен к вызсоду дифференцинапряжений, пиковый детектор положи- ального интегрирукщего усилителя,

тельных напряжений, входы которыхдвусторонний ограничитель напряжения,

объединены и являются входом блокакоторый, включен между выходом фильтра

симметрирования, а выходы которых .нижних частот и общей шиной, при этом

подключены соответственно к инверти-выход фильтра нижних частот является

рукщему и неинвертиругадему входам диф- двыходом блока симметрирования.

| Вавилов А.А | |||

| и др | |||

| Низкочастотные измерительные генераторы | |||

| Л.: Энергоатомиздат, 1985, с | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Справочник по нелинейным схемам | |||

| М.: Мир, 1977, с | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-08-30—Публикация

1986-12-02—Подача