Фиг.1

3150

Изобретение относится к импульсной технике и может быть использовано в вычислительной технике.

Цель изобретения - расширение функциональных возможностей устройства за счет формирования стационарного случайного процесса с заданной - автокорреляционной функцией.

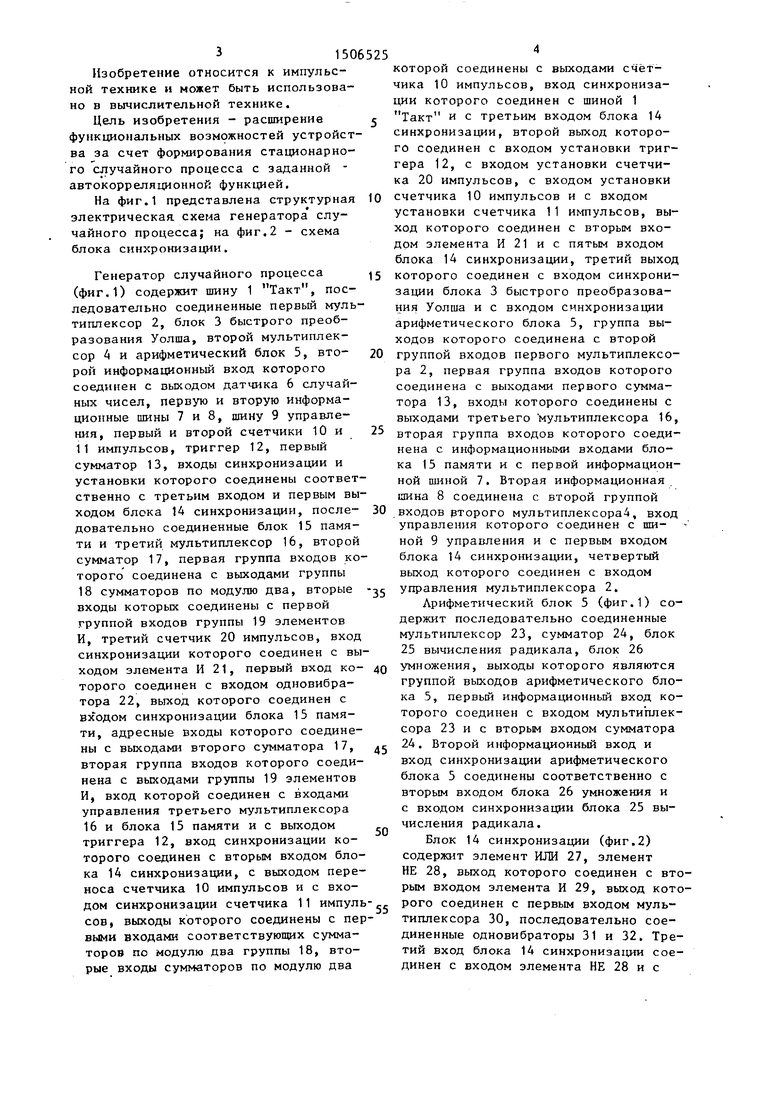

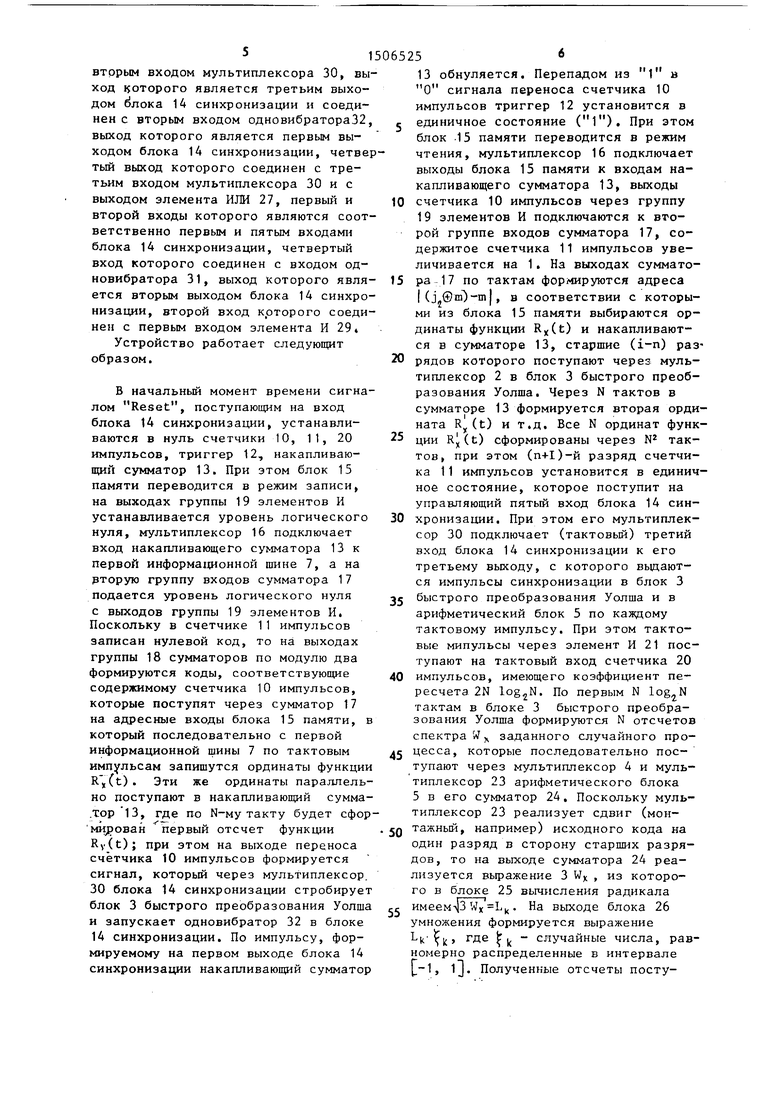

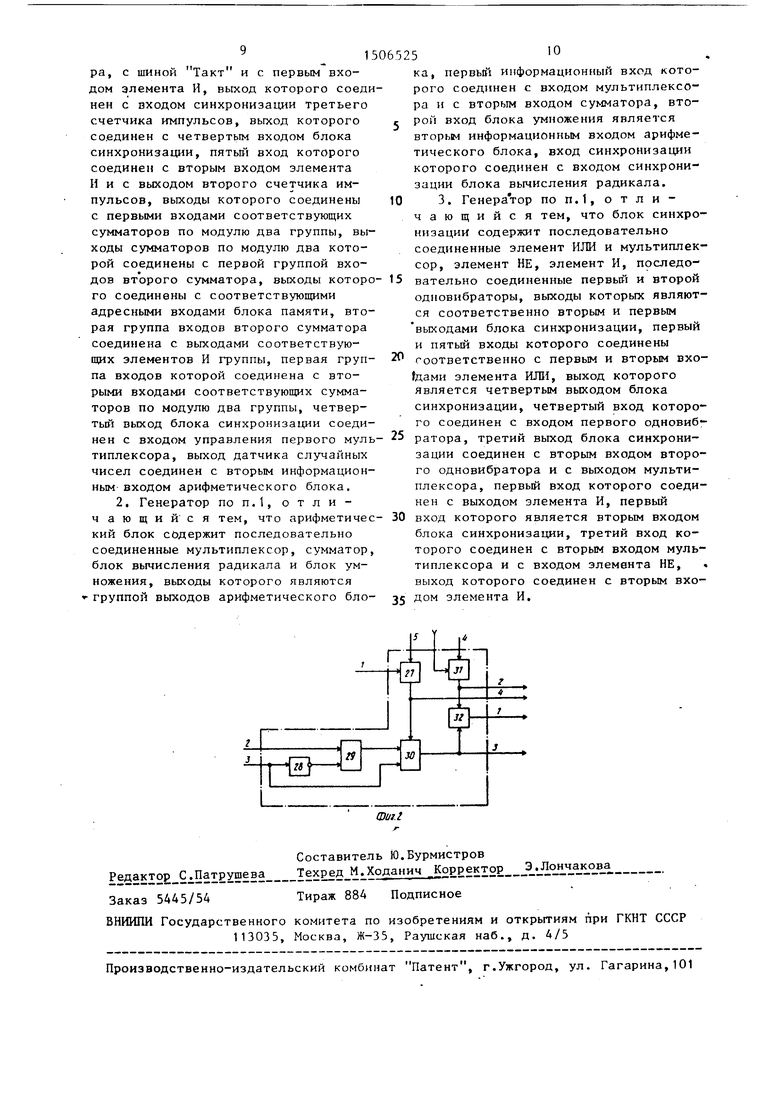

На фиг.1 представлена структурная электрическая схема генератора случайного процесса; на фиг.2 - схема блока синхронизации.

Генератор случайного процесса (фиг,1) содержит шину 1 Такт, последовательно соединенные первый мультиплексор 2, блок 3 быстрого преобразования Уолша, второй мультиплексор и арифметический блок 5, вто- рой информационный вход которого соединен с вькодом датчика 6 случайных чисел, первую и вторую информационные шины 7 и 8, шину 9 управления, первый и второй счетчики 10 и 11 импульсов, триггер 12, первый сумматор 13, входы синхронизации и установки которого соединены соответственно с третьим входом и первым выходом блока 14 синхронизации, после- довательно соединенные блок 15 памяти и третий мультиплексор 16, второй сумматор 17, первая группа входов которого соединена с выходами группы 18 сумматоров по модулю два, вторые входы которых соединены с первой группой входов группы 19 элементов И, третий счетчик 20 импульсов, вход синхронизации которого соединен с выходом элемента И 21, первый вход ко- торого соединен с входом одновибра- тора 22, выход которого соединен с входом синхронизации блока 15 памяти, адресные входы которого соединены с выходами второго сумматора 17, вторая группа входов которого соединена с выходами группы 19 элементов И, вход которой соединен с входами управления третьего мультиплексора 16 и блока 15 памяти и с выходом триггера 12, вход синхронизации которого соединен с вторым входом блока 14 синхронизации, с выходом переноса счетчика 10 импульсов и с входом синхронизации счетчика 11 импуль сов, выходы которого соединены с первыми входами соответствующих сумматоров по модулю два группы 18, вторые входы сумматоров по модулю два

0 5 0 5

0

которой соединены с вьгходами сч ёТ- чика 10 импульсов, вход синхронизации которого соединен с шиной 1 Такт и с третьим входом блока 14 синхронизации, второй выход которого соединен с входом установки триггера 12, с входом установки счетчика 20 импульсов, с входом установки счетчика 10 импульсов и с входом установки счетчика 11 иьтульсов, выход которого соединен с вторым входом элемента И 21 и с пятым входом блока 14 синхронизации, третий выход которого соединен с входом синхронизации блока 3 быстрого преобразования Уолша и с входом синхронизации арифметического блока 5, группа выходов которого соединена с второй группой входов первого мультиплексора 2, первая группа входов которого соединена с выходами первого сумматора 13, входы которого соединены с выходами третьего мультиплексора 16, вторая группа входов которого соединена с информационными входами блока 15 памяти и с первой информационной шиной 7. Вторая информационная шина 8 соединена с второй группой

входов второго мультиплексора4, вход управления которого соединен с шиной 9 управления и с первым входом блока 14 синхронизации, четвертый выход которого соединен с входом управления мультиплексора 2.

Арифметический блок 5 (фиг.1) содержит последовательно соединенные мультиплексор 23, сумматор 24, блок 25 вычисления радикала, блок 26 умножения, выходы которого являются группой выходов арифметического блока 5, первьш информационный вход которого соединен с входом мультиплексора 23 и с вторым входом сумматора 24. Второй информационный вход и вход синхронизации арифметического блока 5 соединены соответственно с вторым входом блока 26 умножения и с входом синхронизации блока 25 вычисления радикала.

Блок 14 синхронизации (фиг.2) содержит элемент ИЛИ 27, элемент НЕ 28, выход которого соединен с вторым входом элемента И 29, выход которого соединен с первым входом мультиплексора 30, последовательно соединенные одновибраторы 31 и 32. Третий вход блока 14 синхрониза1щи соединен с входом элемента НЕ 28 и с

51

втррьсм входом мультиплексора 30, выход ijoToporo является третьим выходом ёлока 14 синхронизации и соединен с вторым входом одновибратора32, выход которого является первым выходом блока 14 синхронизации, четвертый выход которого соединен с третьим входом мультиплексора 30 и с выходом элемента ИЛИ 27, первый и второй входы которого являются соответственно первым и пятьт входами блока 14 синхронизации, четвертый вход которого соединен с входом од- новибратора 31, выход которого является вторым выходом блока 14 синхронизации, второй вход которого соединен с первым входом элемента И 29t

Устройство работает следующит образом.

В начальный момент времени сигналом Reset, поступающим на вход блока 14 синхронизации, устанавливаются в нуль счетчики 10, 11, 20 импульсов, триггер 12, накапливающий сумматор 13. При этом блок 15 памяти переводится в режим записи, на выходах группы 19 элементов И устанавливается уровень логического нуля, мультиплексор 16 подключает вход накапливающего сумматора 13 к первой информационной шине 7, а на рторую группу входов сумматора 17 подается уровень логического нуля

с выходов группы 19 элементов И. Поскольку в счетчике 11 импульсов записан нулевой код, то на выходах группы 18 сумматоров по модулю два формируются коды, соответствуюЕЦие содержимому счетчика 10 импульсов, которые поступят через сумматор 17 на адресные входы блока 15 памяти, в который последовательно с первой информационной шины 7 по тактовым импульсам запишутся ординаты функции R(t). Эти же ординаты параллельно поступают в накапливающий сумма- .Тор 13, где по N-му такту будет сфор- минован первый отсчет функции Rv(t); при этом на выходе переноса счётчика 10 импульсов формируется сигнал, который через мультиплексор. 30 блока 14 синхронизации стробирует блок 3 быстрого преобразования Уолша и запускает одновибратор 32 в блоке 14 синхронизации. По импульсу, формируемому на первом выходе блока 14 синхронизахщи накапливающий сумматор

0

0

5

0

5

0

5

13 обнуляется. Перепадом из 1 в О сигнала переноса счетчика 10 импульсов триггер 12 установится в единичное состояние (1). При этом блок 15 памяти переводится в режим чтения, мультиплексор 16 подключает выходы блока 15 памяти к входам накапливающего сумматора 13, выходы счетчика 10 импульсов через группу 19 элементов И подключаются к второй группе входов сумматора 17, со- держитое счетчика 11 импульсов увеличивается на 1. На выходах суммато- 5 ра 17 по тактам формируются адреса l(j,®™)4 | S соответствии с которыми из блока 15 памяти выбираются ординаты функции ) и накапливаются в сумматоре 13, старшие (i-n) разрядов которого поступают через мультиплексор 2 в блок 3 быстрого преобразования Уолша. Через N тактов в сумматоре 13 формируется вторая ордината RJ, (t) и т.д. Все N ординат функции Rj((t) сформированы через N тактов, при этом (п+1)-й разряд счетчика 11 импульсов установится в единичное состояние, которое поступит на управляющий пятый вход блока 14 синхронизации. При этом его мультиплексор 30 подключает (тактовый) третий вход блока 14 синхронизации к его третьему выходу, с которого вьдают- ся импульсы синхронизации в блок 3 быстрого преобразования Уолша и в арифметический блок 5 по каждому тактовому импульсу. При этом тактовые мипульсы через элемент И 21 поступают на тактовый вход счетчика 20 импульсов, имеющего коэффициент пересчета 2N logjN. По первым N

тактам в блоке 3 бьютрого преобразования Уолша формируются N отсчетов

спектра W , заданного случайного процесса, которые последовательно поступают через мультиплексор 4 и мультиплексор 23 арифметического блока 5 в его сумматор 24. Поскольку мультиплексор 23 реализует сдвиг (мон

тажный, например) исходного кода на один разряд в сторону старших разрядов, то на выходе сумматора 24 реализуется выражение 3 , из которого в блоке 25 вычисления радикала имеем- З W L . На выходе блока 26 умножения формируется выражение где |( - случайные числа, равномерно распределенные в интервале -1, ij. Полученные отсчеты поступают вноаь в блок 3 быстрого преобразования Уолша через мультиплексор 2, поскольку высоким потенциалом с четвертого выхода блока 14 синхро- низации выход его блока 26 умножения подключается к входу блока 3 быстрого преобразования Уолша, где в последующие N тактов формируются N отсчетов искомого случайно- го процесса, поступающего на выход устройства. После формирования последнего отсчета процесса x(t) на выходе счетчика 20 импульсов формируется сигнал, запускающий одновибратор 31, на выходе которого формируется импульс, устанавливающий в исходное нулевое состояние счетчики 10, 11, 20 импульсов, триггер 12 и накапливающий сумматор 13, Тем самым устрой- ство вновь готово к работе.

Режим формирования двоично-нестационарного случайного процесса с заданными спектральными характеристиками задается единичным сигналом на шине 9 управления. На второй вход мультиплексора 4 синхронно с тактами подаются отсчеты задаваемого спектра W, поступающие в арифметический блок 5, где происходит вычисление соотношения , над которым далее производится быстрое преобразование Уолша. Тем самым на выходе блока 3 быстрого преобразования Уолша формируется двоично-нестацио- нарный случайный процесс с заданными спектральными характеристиками.

Таким образом, предлагаемое устройство позволяет формировать двоично-нестационарный случайный про цесс с заданными спектральными характеристиками, а также процесс, наилучшим образом аппроксимирующий стацио- норньп случайный процесс с заданной автокорреляционной функцией.

Формула изобретения

1.Генератор случайного процесса, содержащий последовательно соединенны первый мультиплексор и блок быстрого преобразования Уолша, датчик случайных чисел, первый счетчик импульсов, выходы которого соединены с группой входов группы элементов И, блок па- мяти, первый сумматор, вход установки которого соединен с первым выходом блока синхронизации, второй выход которого соединен с входом уста-

0

5

0 5

5

0

0

новки первого счетчика импульсов, отличающийся тем, что, с целью расширения функциональных возможностей за счет формирования стационарного случайного процесса с заданной автокорреляционной функцией, в него введены второй и третий мультиплексоры, арифметический блок, второй и третий счетчики импульсов, триггер, второй сумматор, элемент И, группа сумматоров по модулю два, первая и вторая информационные шины, шина Такт, шина управления и одновибратор, выход которого соединен с входом синхронизации блока памяти, выходы которого соединены с первой группой входов третьего мультиплексора, выходы которого соединены с соответствующими входами первого сумматора, выходы которого соединены с первой группой входов первого мультиплексора, вторая группа входов которого соединена с группой выходов арифметического блока, первый информационный вход которого соединен с выходом второго мультиплексора, первая группа входов которого соединена с соответствующими выходами блока быстрого преобразования Уолша, вход синхронизации которого соединен с входом синхронизации арифметического блока и с третьим выходом блока синхронизации, первый вход которого соединен с шиной управления и с входом управления второго мультиплексора, вторая группа входов которого соединена с второй информационной шиной, первая информационная шина соединена с соответствующими информационными входами блока памяти и с второй группой входов третьего мультиплексора, вход управления которого соединен с входом управления блока памяти, с входом группы элементов И и с выходом триггера, вход установки которого соединен с Входом установки третьего счетчика импульсов, с вторым выходом блока синхронизации и с входом установки второго счетчика импульсов, вход синхронизации которого соединен с входом синхронизации триггера, с вторым входом блока синхронизации и с выходом переполнения первого счетчика импульсов, вход синхронизации которого соединен с третьим входом блока синхронизации, с входом синхронизации первого сумматора, с входом одновибратошиной Такт и

ра, с шиной Такт и с первым входом элемента И, выход которого соединен с входом синхронизации третьего счетчика импульсов, выход которого соединен с четвертым входом блока синхронизации, пятый вход которого соединен с вторым входом элемента И и с выходом второго счетчика импульсов, выходы которого соединены с первь ми входами соответствующих сумматоров по модулю два группы, выходы сумматоров по модулю два которой соединены с первой группой вхо

ка, первый информационный вход которого соединен с входом мультиплексора и с вторым входом сумматора, второй вход блока умножения является вторым информационным входом арифметического блока, вход синхронизации которого соединен с входом синхронизации блока вычисления радикала.

3. Генера тор по п.1, отличающийся тем, что блок синхронизации содержит последовательно соединенные элемент ИЛИ и мультиплексор, элемент НЕ, элемент И, последо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования в базисе кусочно-квадратичных функций Уолша | 1987 |

|

SU1520539A1 |

| Устройство для вычисления коэффициентов Уолша | 1987 |

|

SU1444817A1 |

| Генератор функций Уолша | 1984 |

|

SU1166134A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Анализатор спектра Уолша | 1985 |

|

SU1264199A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2446461C2 |

| Генератор испытательных сигналов | 1986 |

|

SU1406742A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Изобретение относится к импульсной технике. Цель изобретения - расширение функциональных возможностей за счет формирования стационарного случайного процесса с заданной автокорреляционной функцией-достигается путем введения в устройство мультиплексоров 16 и 4, арифметического блока 5, счетчиков 11 и 20 импульсов, триггера 12, сумматора 17, элемента И 21, группы 18 сумматоров по модулю два, шин 1, 7, 8 и 9, одновибратора 22 и образования новых функциональных связей. Устройство содержит также блок 3 быстрого преобразования Уолша, датчик 6 случайных чисел, счетчик 10 импульсов, сумматор 13, блок 14 синхронизации, блок 15 памяти, мультиплексор 2, группу 19 элементов И. 2 з.п. ф-лы, 2 ил.

дов второго сумматора, выходы которо- 15 вательно соединенные первый и второй

го соединены с соответствующими адресными входами блока памяти, вторая группа входов второго сумматора соединена с выходами соответствующих элементов И группы, первая груп- па входов которой соединена с вторыми входами соответствующих сумматоров по модулю два группы, четвер- TbDi выход блока синхронизации соединен с входом управления первого мультиплексора, выход датчика случайных чисел соединен с вторым информационным входом арифметического блока. 2. Генератор по п.1, о т л и - ч ающийся тем, что арифметичес кий блок содержит последовательно соединенные мультиплексор, сумматор, блок вычисления радикала и блок умножения, выходы которого являются

группой выходов арифметического бло- 35 Дом элемента И.

L..

одновибраторы, выходы которых являются соответственно вторым и первым выходами блока синхронизации, первый и пятый входы которого соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является четвертым выходом блока синхронизации, четвертый вход которого соединен с входом первого одновиб- ратора, третий выход блока синхронизации соединен с вторым входом второго одновибратора и с выходом мультиплексора, первый вход которого соединен с выходом элемента И, первый вход которого является вторым входом блока синхронизации, третий вход которого соединен с вторым входом мультиплексора и с входом элемента НЕ, . выход которого соединен с вторым вхо

| Генератор случайных процессов | 1984 |

|

SU1196861A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор случайных процессов | 1980 |

|

SU968811A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-07—Публикация

1988-01-11—Подача