Изобретение относится к технике средств связи, может быть использовано при построении цифровых телевизионных систем, использующих канал связи с ограниченной пропускной способностью и осуществляющих, наряду с цифровым телевизионным сигналом, передачу допольнительной информации, и является усовершенствованием изобретения по авт. св. № 1394465.

Целью изобретения является увеличение передаваемой информации.

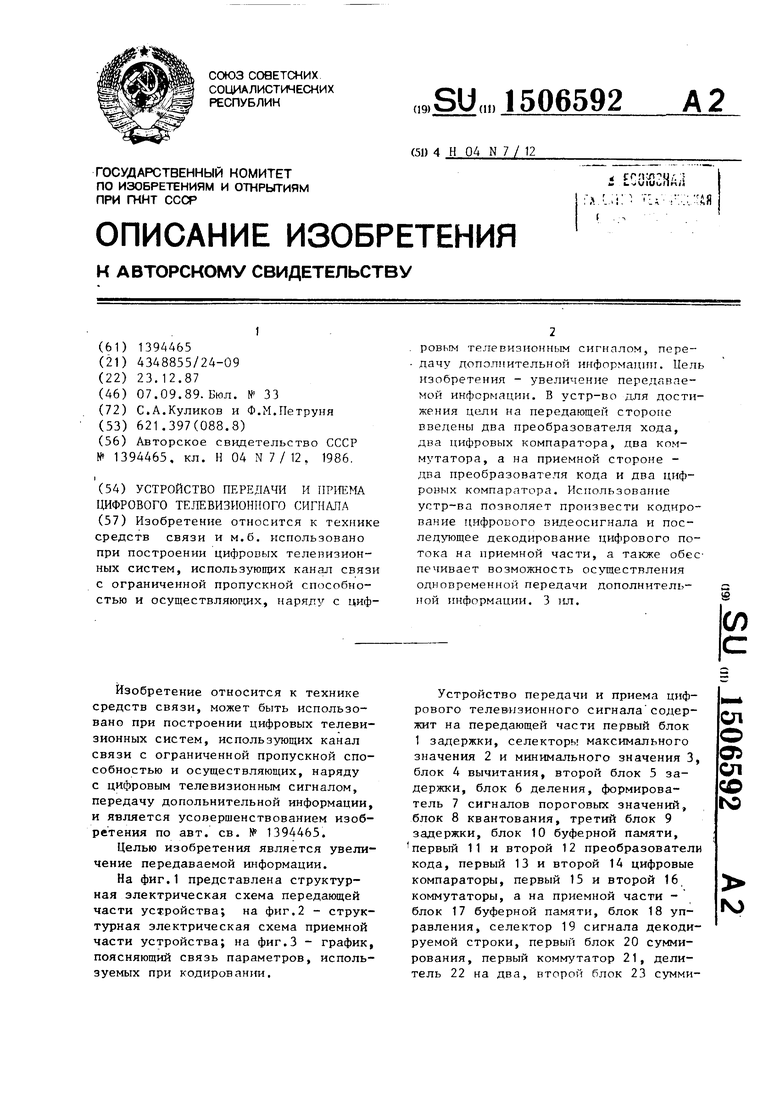

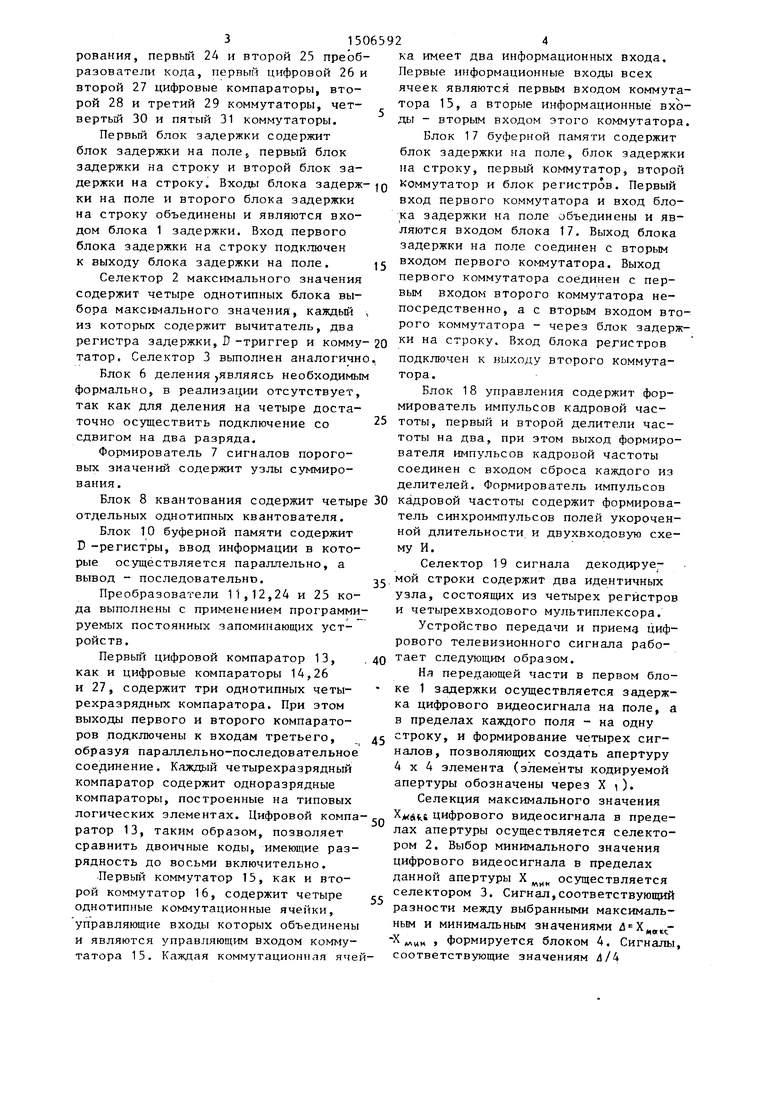

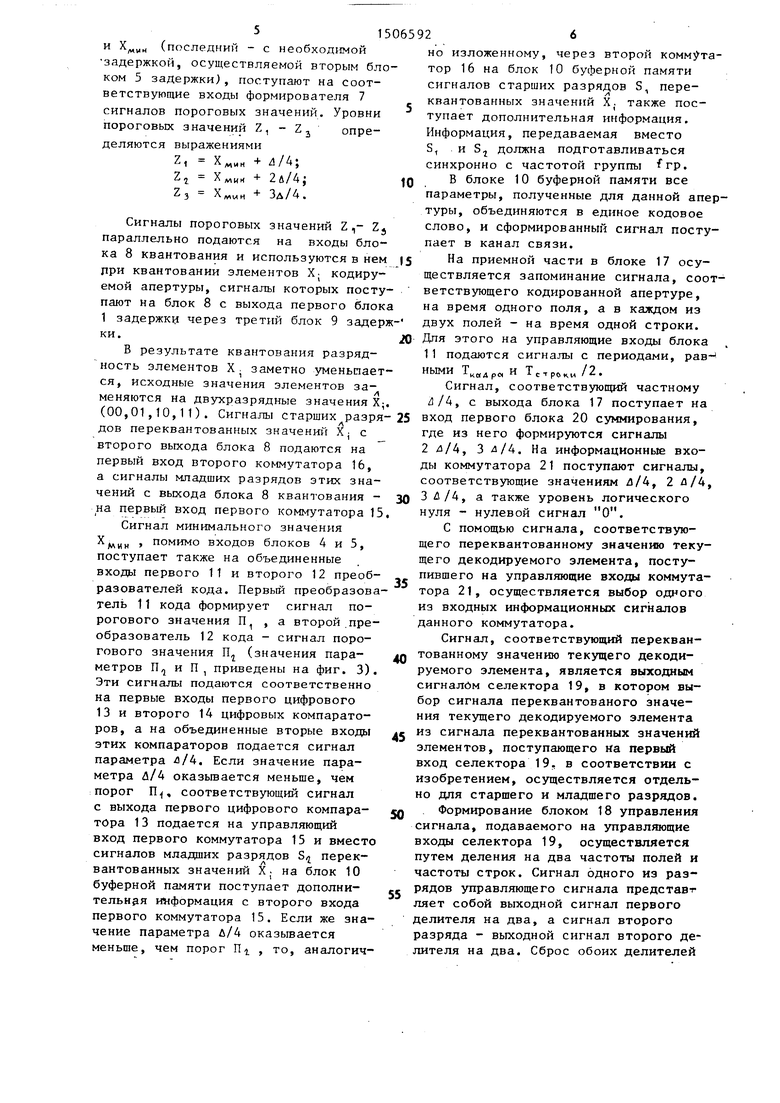

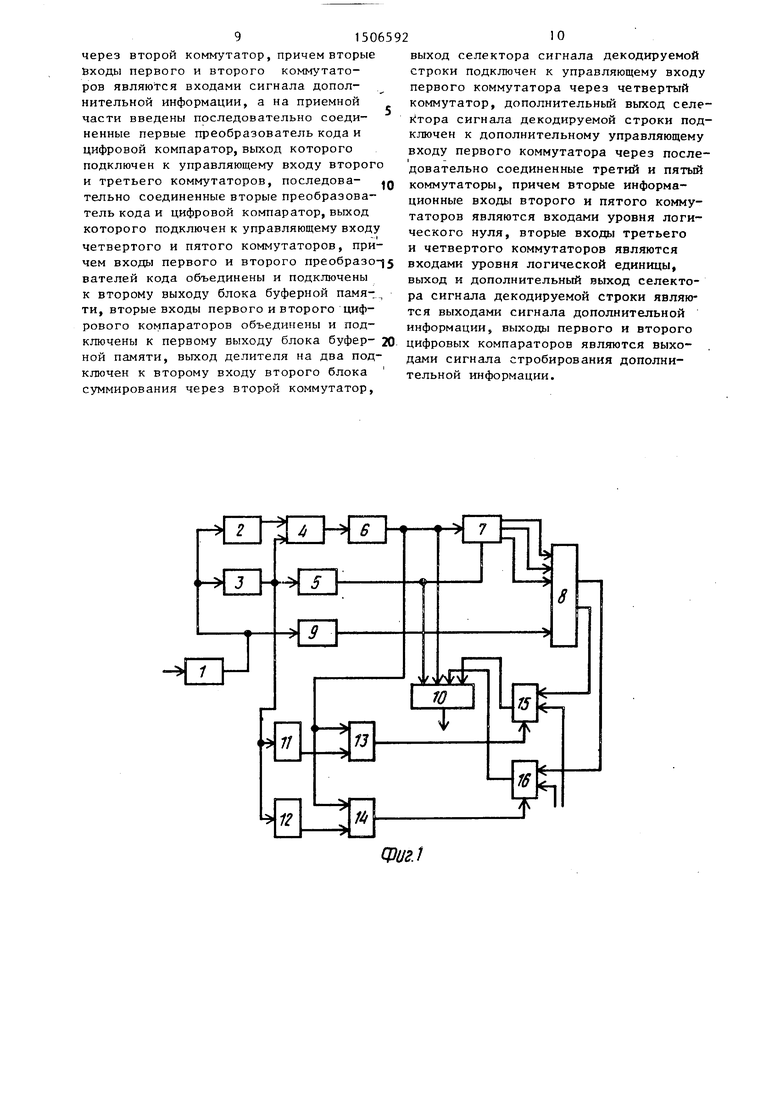

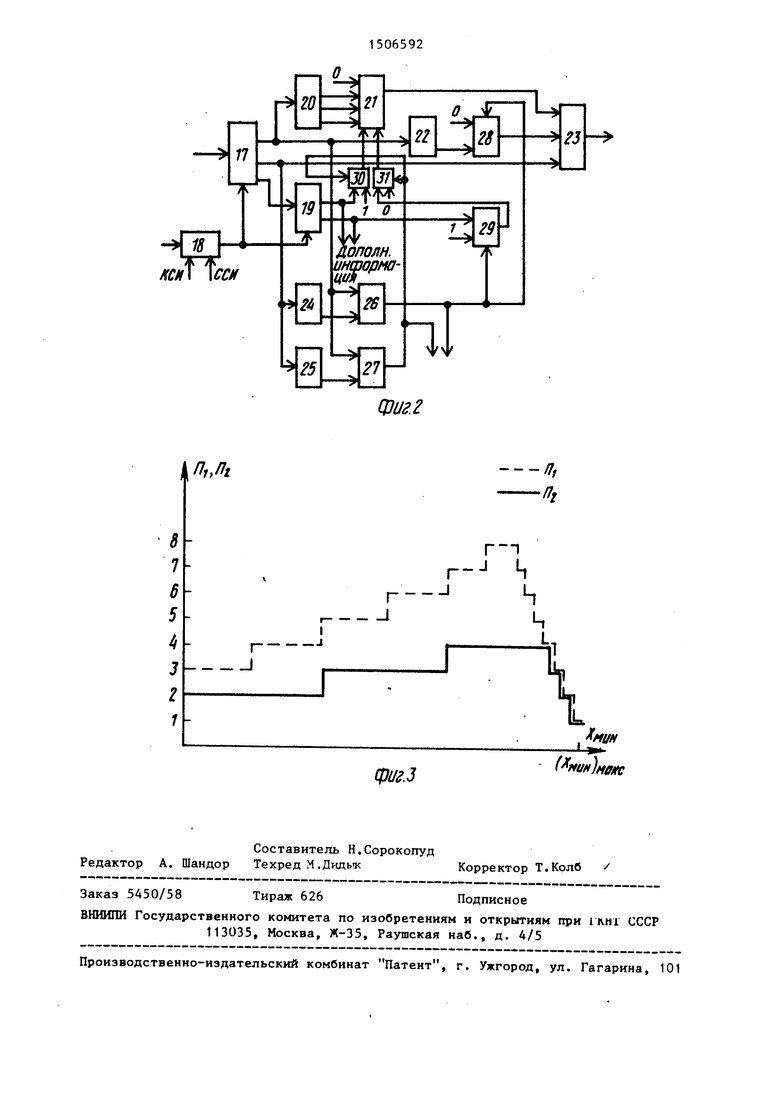

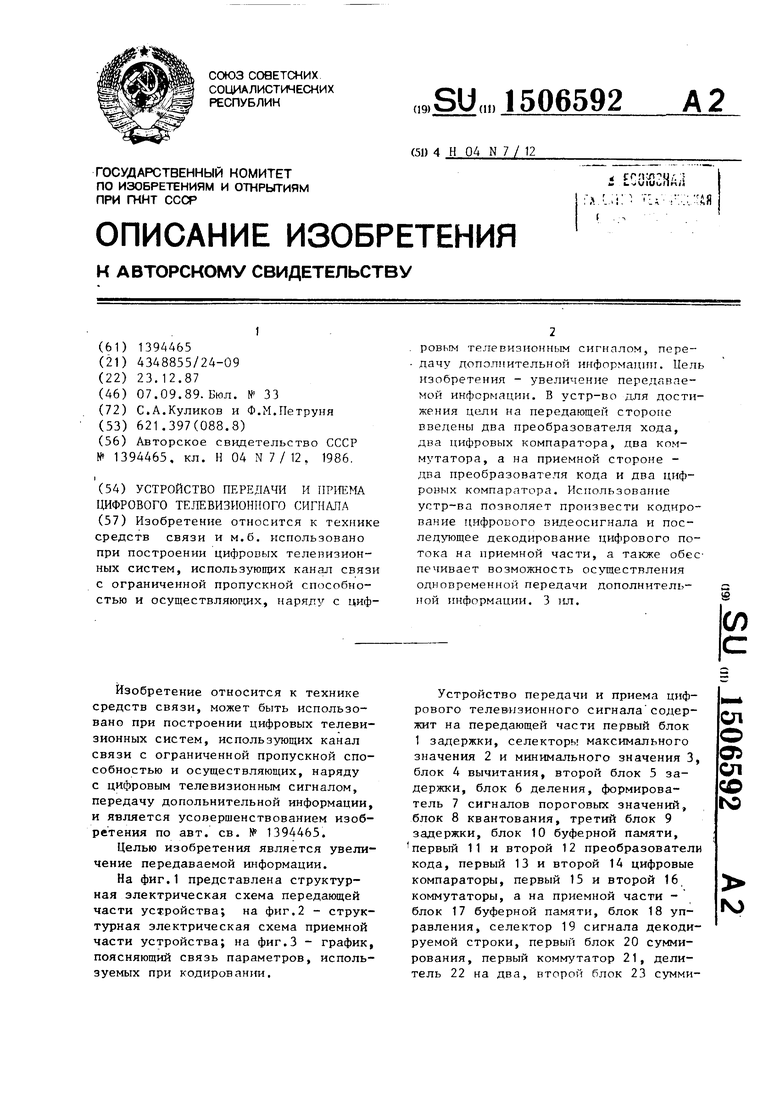

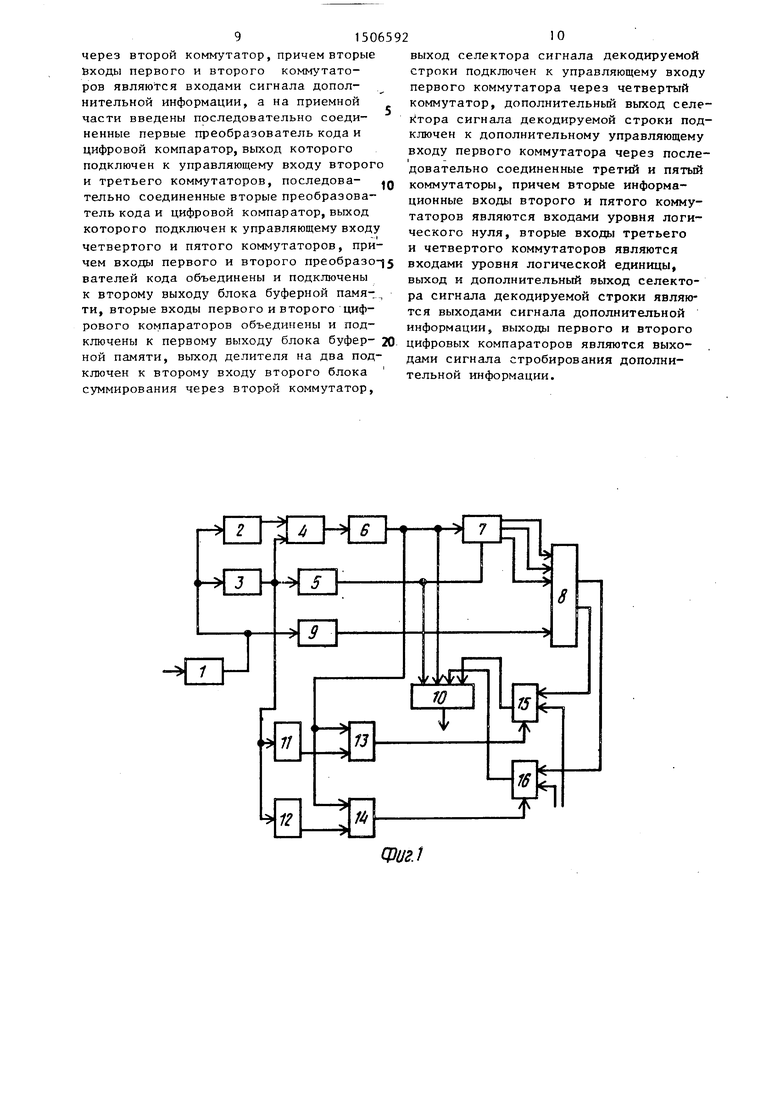

На фиг.1 представлена структурная электрическая схема передающей части устройства; на фиг.2 - структурная электрическая схема приемной части устройства; на фиг.З - график, поясняющий связь параметров, используемых при кодировании.

Устройство передачи и приема цифрового телевизионного сигнала содержит на передающей части первый блок 1 задержки, селекторь; максимального значения 2 и минимального значения 3, блок 4 вычитания, второй блок 5 задержки, блок 6 деления, формирователь 7 сигналов пороговых значений, блок 8 квантования, третий блок 9 задержки, блок 10 буферной памяти, первый 11 и второй 12 преобразователи кода, первый 13 и второй 14 цифровые компараторы, первый 15 и второй 16 коммутаторы, а на приемной части - блок 17 буферной памяти, блок 18 управления, селектор 19 сигнала декодируемой строки, первый блок 20 суммирования, первый коммутатор 21, делитель 22 на два, второй блок 23 суммисл о а ел

1ЧЭ

N)

рования, nepBbtfi 2k и второй 25 преобразователи кода, первьгй цифровой 26 и второй 27 цифровые компараторы, второй 28 и третий 29 коммутаторы, четвертый 30 и пятый 31 коммутаторы. Первый блок задержки содержит блок задержки на поле первый блок задержки на строку и второй блок зака имеет два информационных входа. Первые информационные входы всех ячеек являются первым входом коммутатора 15, а вторые информационные входы - вторым входом этого коммутатора.

Блок 17 буферной памяти содержит блок задержки на поле, блок задержки на строку, первый коммутатор, второй

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройтво передачи и приема цифрового телевизионного сигнала | 1986 |

|

SU1394465A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Устройство для обработки изображений | 1986 |

|

SU1388915A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Устройство цифрового кодирования сигналов цветности системы СЕКАМ | 1982 |

|

SU1059704A1 |

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Устройство для воспроизведения видеосигнала | 1981 |

|

SU1070706A2 |

Изобретение относится к технике средств связи и может быть использовано при построении цифровых телевизионных систем, использующих канал связи с ограниченной пропускной способностью и осуществляющих, наряду с цифровым телевизионным сигналом, передачу дополнительной информации. Цель изобретения - увеличение передаваемой информации. В устройство для достижения цели на передающей стороне введены два преобразователя хода, два цифровых компаратора, два коммутатора, а на приемной стороне - два преобразователя кода и два цифровых компаратора. Использование устройства позволяет произвести кодирование цифрового видеосигнала и последующее декодирование цифрового потока на приемной части, а также обеспечивает возможность осуществления одновременной передачи дополнительной информации. 3 ил.

держки на строку. Входы блока задерж- ю оммутатор и блок регистров. Первый

вход первого коммутатора и вход блока задержки на поле объединены и являются входом блока 17. Выход блока задержки на поле соединен с вторым входом первого коммутатора. Выход первого коммутатора соединен с первым входом второго коммутатора непосредственно, а с вторым входом вто рого коммутатора - через блок задерж

ки на поле и второго блока задержки на строку объединены и являются входом блока 1 задержки. Вход первого блока задержки на строку подключен к выходу блока задержки на поле.

Селектор 2 максимального значения содержит четыре однотипных блока выбора максимального значения, каждый из которых содержит вычитатель, два

15

вход первого коммутатора и вход бло ка задержки на поле объединены и яв ляются входом блока 17. Выход блока задержки на поле соединен с вторым входом первого коммутатора. Выход первого коммутатора соединен с первым входом второго коммутатора непосредственно, а с вторым входом вт рого коммутатора - через блок задер

регистра задержки, D-триггер и комму-20 строку. Вход блока регистров

татор. Селектор 3 выполнен аналогично,

Блок 6 деления )Являясь необходимым формально, в реализации отсутствует, так как для деления на четыре достаточно осуществить подключение со сдвигом на два разряда.

Формирователь 7 сигналов пороговых значений содержит узлы суммирования.

Блок 8 квантования содержит четыре 30 кадровой частоты содержит формироваотдельных однотипных квантователя.

Блок 10 буферной памяти содержит D -регистры, ввод информации в которые осуществляется параллельно, а вывод - последовательно.

Преобразователи 11,12,24 и 25 кода выполнены с применением программируемых постоянных запоминающих устройств.

Первый цифровой компаратор 13, как и цифровые компараторы 14,26 и 27, содержит три однотипных четы- рехразрядньрс компаратора. При этом выходы первого и второго компараторов подключены к входам третьего, образуя параллельно-последовательное соединение. Каждый четырехразрядный компаратор содержит одноразрядные компараторы, построенные на типовых логических элементах. Цифровой компаратор 13, таким образом, позволяет сравнить двоичные коды, имеющие разрядность до восьми включительно.

Первый коммутатор 15, как и второй коммутатор 16, содержит четыре однотипные коммутационные ячейки, управляющие входы которых объединены и являются управляющим входом комму40

тель синхроимпульсов полей уко ной длительности и двухвходову му И.

Селектор 19 сигнала декоди .JJ мой строки содержит два иденти узла, состоящих из четырех рег и четырехвходового мультиплекс

Устройство передачи и прием рового телевизионного сигнала тает следующим образом.

На передающей части в перво ке 1 задержки осуществляется з ка цифрового видеосигнала на п в пределах каждого поля - на о строку, и формирование четырех налов, позволяющих создать апе 4x4 элемента (элементы кодир апертуры обозначены через X i)

Селекция максимального знач .1 цифрового видеосигнала в лах апертуры осуществляется се ром 2. Выбор минимального знач цифрового видеосигнала в преде данной апертуры X осуществл селектором 3. Сигнал,соответст разности между выбранными макс ным и минимальным значениями Л лии формируется блоком 4. С

45

50

55

татора 15. Каждая коммутационная ячей- соответствующие значениям 4/4

оммутатор и блок регистров. Первый

вход первого коммутатора и вход блока задержки на поле объединены и являются входом блока 17. Выход блока задержки на поле соединен с вторым входом первого коммутатора. Выход первого коммутатора соединен с первым входом второго коммутатора непосредственно, а с вторым входом второго коммутатора - через блок задерж5

подключен к выходу второго коммутатора.

Блок 18 управления содержит формирователь импульсов кадровой частоты, первый и второй делители частоты на два, при этом выход формирователя импульсов кадровой частоты соединен с входом сброса каждого из делителей. Формирователь импульсов

0

тель синхроимпульсов полей укороченной длительности и двухвходовую схему И.

Селектор 19 сигнала декодируе- J мой строки содержит два идентичных узла, состоящих из четырех регистров и четырехвходового мультиплексора.

Устройство передачи и приема цифрового телевизионного сигнала работает следующим образом.

На передающей части в первом блоке 1 задержки осуществляется задержка цифрового видеосигнала на поле, а в пределах каждого поля - на одну строку, и формирование четырех сигналов, позволяющих создать апертуру 4x4 элемента (элементы кодируемой апертуры обозначены через X i).

Селекция максимального значения .1 цифрового видеосигнала в пределах апертуры осуществляется селектором 2. Выбор минимального значения цифрового видеосигнала в пределах данной апертуры X осуществляется селектором 3. Сигнал,соответствующий разности между выбранными максимальным и минимальным значениями Л Х,,,- лии формируется блоком 4. Сигналы,

5

0

5

и /иим (последний - с необходимой задержкой, осуществляемой вторым блком 5 задержки), поступают на соответствующие входы формирователя 7 сигналов пороговых значений. Уровни пороговых значений Z, - Z определяются выражениями

Zi Х„„„ + Л/4; + 2й/4; Зд/А.

Z J X мик

3

2 ч X длин

В блоке 10 буферной памяти все параметры, полученные для данной апе туры, объединяются в единое кодовое слово, и сформированный сигнал посту пает в канал связи.

На приемной части в блоке 17 осуществляется запоминание сигнала, соо

ными Т

когд р

с, и TC т ромл

Сигналы пороговых значений Z,- Zj параллельно подаются на входы блока 8 квантования и используются в нем |5 при квантовании элементов Х- кодируемой апертуры, сигналы которых посту- ветствующего кодированной апертуре, пают на блок 8 с выхода первого блока на время одного поля, а в каждом из 1 задержку через третий блок 9 задерж- двух полей - на время одной строки. ки.. Для этого на управляющие входы блока

В результате квантования разряд- 11 подаются сигналы с периодами, рав ность элементов X, заметно уменьиает- ся, исходные значения элементов заменяются на двухразрядные значения X;.

(00,01,10,11). Сигналы старших разря- 25 вход первого блока 20 суммирования, ДОН переквантованных значений Xj с где из него формируются сигналы второго выхода блока 8 подаются на 2 л/4, . На информационные вхо- первый вход второго коммутатора 16, ды коммутатора 21 поступают сигналы, а сигналы младших разрядов этих значений с выхода блока 8 квантования - на первый вход первого коммутатора 15,

Сигнал минимального значения мин помимо входов блоков 4 и 5, поступает также на объединенные входы первого 11 и второго 12 преобразователей кода. Первый преобразователь 11 кода формирует сигнал поСигнал, соответствующий частному /3/4, с выхода блока 17 поступает на

соответствующие значениям Л/4, 2 л/4 30 3 Л/4, а также уровень логического

35

нуля - нулевой сигнал О.

С помощью сигнала, соответствующего переквантованному значению текущего декодируемого элемента, поступившего на управляющие входы коммутатора 21, осуществляется выбор одного из входных информационных сигналов данного коммутатора.

рогового значения П, , а второй .преобразователь 12 кода - сигнал порогового значения П (значения параметров П и П , приведены на фиг. 3). Эти сигналы подаются соответственно на первые входы первого цифрового 13 и второго 14 цифровых компараторов, а на объединенные вторые входы « з сигнала переквантованных значений

этих компараторов подается сигнал параметра л/4. Если значение параметра Л/4 оказьгоается меньше, чем порог П, соответствующий сигнал с выхода первого цифрового компаратора 13 подается на управляющий вход первого коммутатора 15 и вместо сигналов младших разрядов 5 переквантованных значений X; на блок 10 буферной памяти поступает дополнительная и {формация с второго входа первого коммутатора 15. Если же значение параметра Д/4 оказывается меньше, чем порог П , то, аналогич50

55

элементов, поступающего на первый вход селектора 19. в соответствии с изобретением, осуществляется отдельно для старшего и младшего разрядов. Формирование блоком 18 управления сигнала, подаваемого на управляющие входы селектора 19, осуществляется путем деления на два частоты полей и частоты строк. Сигнал одного из разрядов управляющего сигнала представт ляет собой выходной сигнал первого делителя на два, а сигнал второго разряда - выходной сигнал второго делителя на два. Сброс обоих делителей

но изложенному, через второй тор 16 на блок 10 буферной памяти сигналов старших разрядов S, переквантованных значений X; также поступает дополнительная информация. Информация, передаваемая вместо S, и S долзкна подготавливаться синхронно с частотой группы гр.

В блоке 10 буферной памяти все параметры, полученные для данной апертуры, объединяются в единое кодовое слово, и сформированный сигнал поступает в канал связи.

На приемной части в блоке 17 осуществляется запоминание сигнала, соответствующего кодированной апертуре, на время одного поля, а в каждом из двух полей - на время одной строки. Для этого на управляющие входы блока

ными Т

когд р

с, и TC т ромл

11 подаются сигналы с периодами, рав

вход первого блока 20 суммирования, где из него формируются сигналы 2 л/4, . На информационные вхо- ды коммутатора 21 поступают сигналы,

Сигнал, соответствующий частному /3/4, с выхода блока 17 поступает на

25 вход первого блока 20 суммирования, где из него формируются сигналы 2 л/4, . На информационные вхо- ды коммутатора 21 поступают сигналы,

соответствующие значениям Л/4, 2 л/4, 0 3 Л/4, а также уровень логического

5

0

нуля - нулевой сигнал О.

С помощью сигнала, соответствующего переквантованному значению текущего декодируемого элемента, поступившего на управляющие входы коммутатора 21, осуществляется выбор одного из входных информационных сигналов данного коммутатора.

Сигнал, соответствующий переквантованному значению текущего декодируемого элемента, является выходным сигналим селектора 19, в котором выбор сигнала переквантованого значения текущего декодируемого элемента

0

5

элементов, поступающего на первый вход селектора 19. в соответствии с изобретением, осуществляется отдельно для старшего и младшего разрядов. Формирование блоком 18 управления сигнала, подаваемого на управляющие входы селектора 19, осуществляется путем деления на два частоты полей и частоты строк. Сигнал одного из разрядов управляющего сигнала представт ляет собой выходной сигнал первого делителя на два, а сигнал второго разряда - выходной сигнал второго делителя на два. Сброс обоих делителей

осуществляется импульсами кадровой частоты, ф(1рмируемыми из си гхро11мпул сов полей и строк.

Сигнал старшего разряда переквап- тованного значения поступает на управляющий вход коммутатора 21 через коммутатор 30, а сигнал мадшего разряда - на другой управляющий вход коммутатора 21 через коммутаторы 29 и 31. Когда значение параметра

4/4 оказывается меньше, чем порог П (это соответствует случаю поступления на приемную часть только старшего разряда S переквантованого значения X . ) , то соответствующий сигнал с выхода первого цифрового компаратора 26 поступает на управляющие входы коммутаторов 28 и 29. При этом сигнал логической 1 с второго входа коммутатора 29 через коммутатор 31 подается на управляющий вход коммутатора 21 и с выхода коммутатора 21 на второй блок 23 суммирования поступают только сигналы значений

З/А и 3 Л/4. Что касается коммутатора 28, то через него на блок 23 подается нулевой сигнал. Таким образом восстановление элементов группы производится двумя уровнями:

УН м и н + ii / 4 ,

у 6 XMUH+ 34/4,

в этом сигнал дополнительной информации снимается с второго выхода селектора 19, а cVirHajioM строби рования этой информации служит выходной сигнал первого цифрового компаратора 26.

В случае, если значение параметра 4/4 оказывается меньше, чем порог П (это соответствует случаю, когда вместо разрядов Si и S, переквантол i

ванного значения X. на приемную част поступает дополнительная информация) то соответствующий сигнал с выхода второго цифрового компаратора 27 поступает на управляющие входы кoм fyтa- торов 30 и 31. При этом с выходов коммутаторов 30 и 31 на ВХОДЕИ коммутатора 21 подается двоичньш код 10, а с выхода коммутатора 21 на второй блок 23 суммирования поступает только сигнал , соответствующий значению 2 Л/4. Через второй коммутатор 28 при этом на второй блок 23 суммирования подается сигнал .1/8, Следовательно, восстановление всех элементов группы пронзпо.щггся одним уровнем, опрелеляеммм выражением

0

5

0

5

0

У Х„,„+2 W4 + Л/8. R этом случае сигнал дополнительной информации снимается с первого и второго выходов селектора 19, а сигналом стробирования этой информации служит сигнал цифрового компаратора 27.

Использование предлагае ого устройства позволяет произвести кодирование цифрового В1адеосигнала и последующее декодирование цифрового потока на приемной части, а также обеспечивает возможность осуществления одновременной передачи дополнительной информации. Например, при реализации варианта устройства, соответствующего случаю кодирования апертуры 4 4 злеу f;eHTa, суммарное значение цифрового потока на выходе передающей части устройства примерно 38 Мбит/с (при час тоте дискретизации яркостного видеосигнала 13, 5 МГц). При этом часть цифрового потока, занимаемая для передачи Кодированного видеосигнала, раина примерно 35 Мбит Ус, а передаваемая дополнительная информация (цвет или телетекст) занимает остальную часть цифрового потока. На приемной части при этом обеспечивается практически такое же качество изображения, как и при использовании известного устройства.

Формула изобретения

Устройство передачи и приема цифрового телевизионного сигнала по авт. ; св. № 1394465, отличающее- с я тем, что, с целью увеличения передаваемой информации, на передающей части введены последовательно соединенные первые преобразователь кода, цифровой компаратор и коммутатор,последовательно соединенные вторые преобразователь кода,цифровой компаратор и коммутатор, причем входы первого и вто- , рого преобразователей кода объединены и подключены к выходу селектора минимального значения, вторые входы первого и второго цифровых компараторов объединены и подключены к выходу блока деления, выход блока квантования подключен к третьему входу блока буферной памяти через первый коммутатор, дополнительный выход блока квантования подключен к четвертому входу блока буферной памяти

через второй коммутатор, причем вторые Входы первого и второго коммутаторов являются входами сигнала дополнительной информации, а на приемной части введены последовательно соединенные первые преобразователь кода и цифровой компаратор, выход которого подключен к управляющему входу второго и третьего коммутаторов, последова- д тельно соединенные вторые преобразователь кода и цифровой компаратор, выход

которого подключен к управляющему входу

- (

четвертого и пятого коммутаторов, причем входы первого и второго преобразо-|5 вателей кода объединены и подключены к второму выходу блока буферной памя- ти, вторые входы первого и второго цифрового компараторов объединены и подключены к первому выходу блока буфер- 20 ной памяти, выход делителя на два подключен к второму входу второго блока суммирования через второй коммутатор.

azH

выход селектора сигнала декодируемой строки подключен к управляющему входу первого коммутатора через четвертый коммутатор, дополнительный выход селе- kTopa сигнала декодируемой строки подключен к дополнительному управляющему входу первого коммутатора через последовательно соединенные третий и пятый коммутаторы, причем вторые информационные входы второго и пятого коммутаторов являются входами уровня логического нуля, вторые входы третьего и четвертого коммутаторов являются входами уровня логической единицы, выход и дополнительный выход селектора сигнала декодируемой строки являются выходами сигнала дополнительной информации, выходы первого и второго цифровых компараторов являются выходами сигнала стробирования дополнительной информации.

сриг.1

дололн.

информа

циТ

10

ЬЕЬ

ПъПг

I

I .J

I

Ц)иг.г

/7,

I1

г- Ц

-JЦ

L,

. Ifff

| Устройтво передачи и приема цифрового телевизионного сигнала | 1986 |

|

SU1394465A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1987-12-23—Подача