Изобретение относится к телевидению и может быть использовано при построении цифровых телевизионных (ТВ) систем, использующих канал связи с ограниченной пропускной способностью

Цель изобретения - повышение точности передачи мелких деталей изображений.

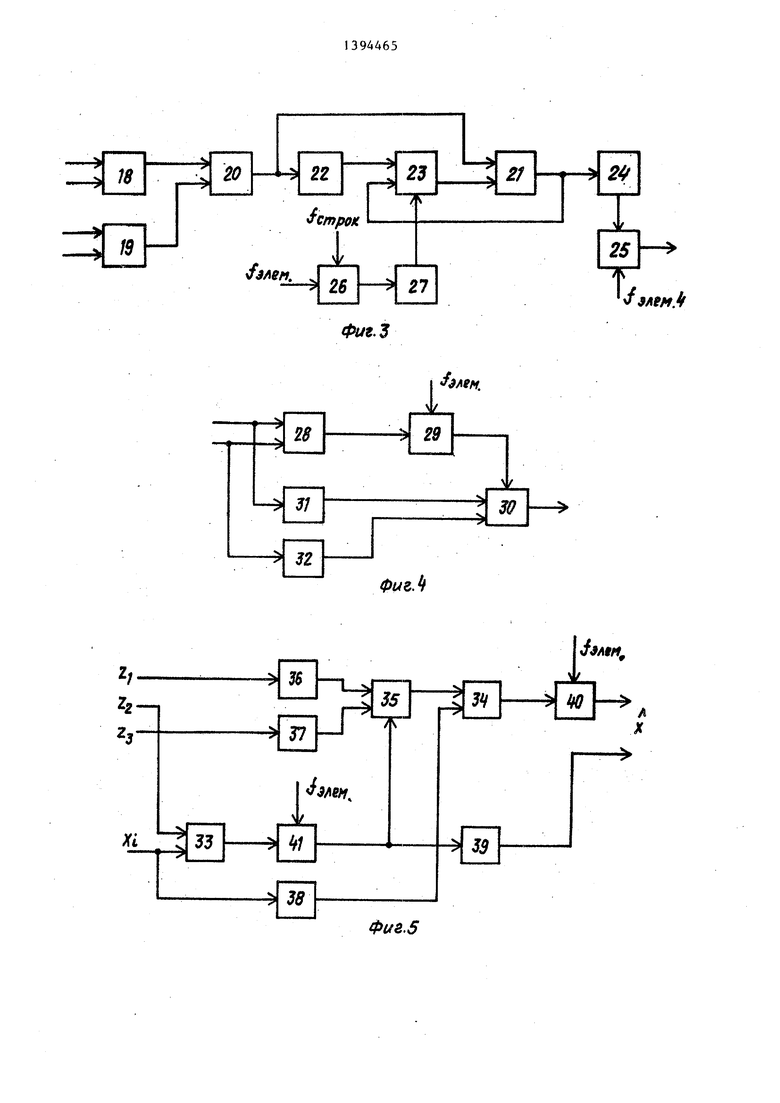

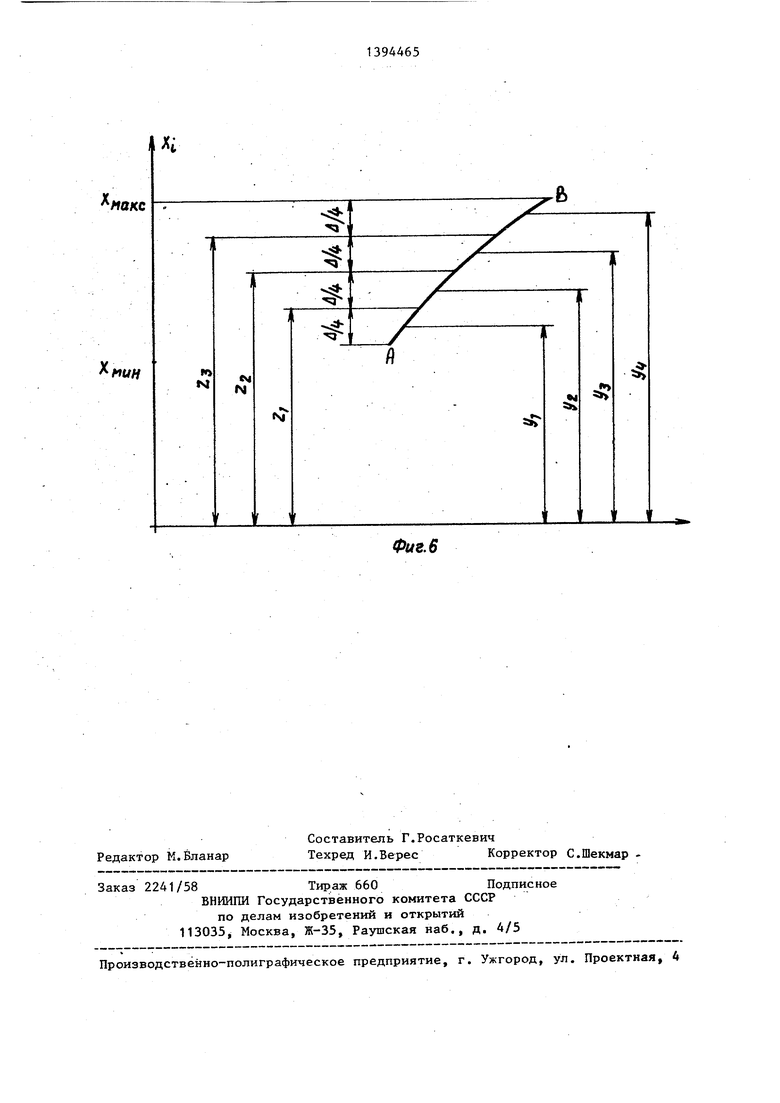

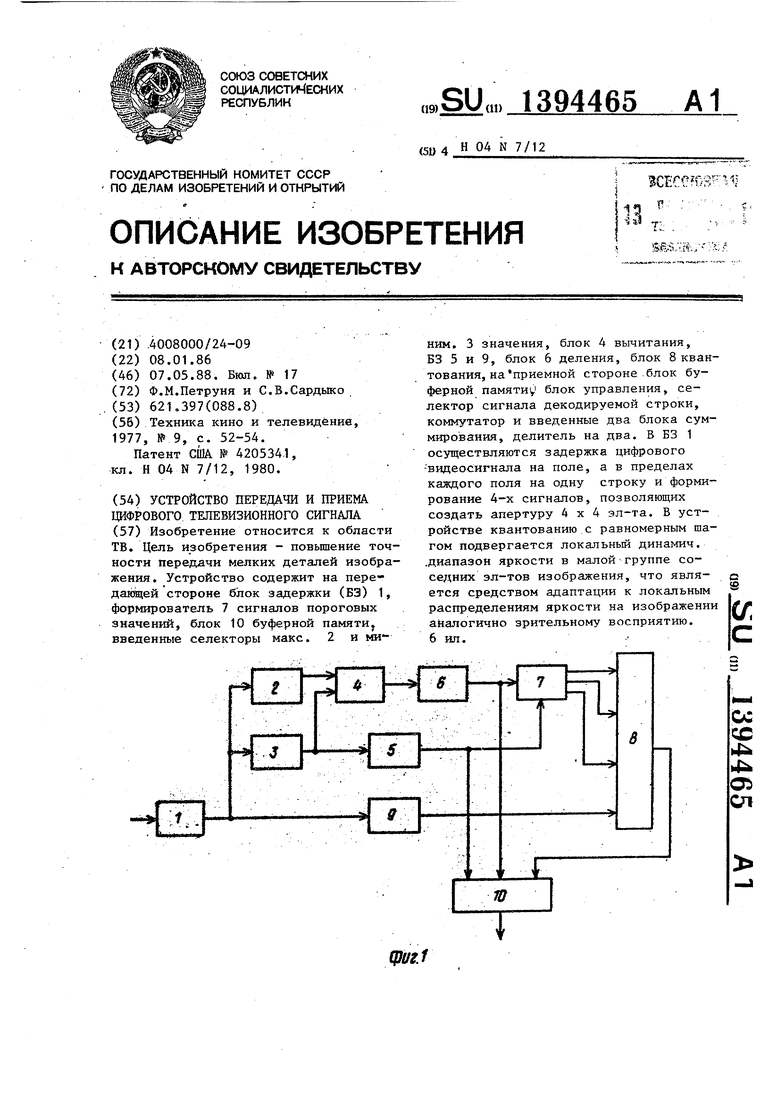

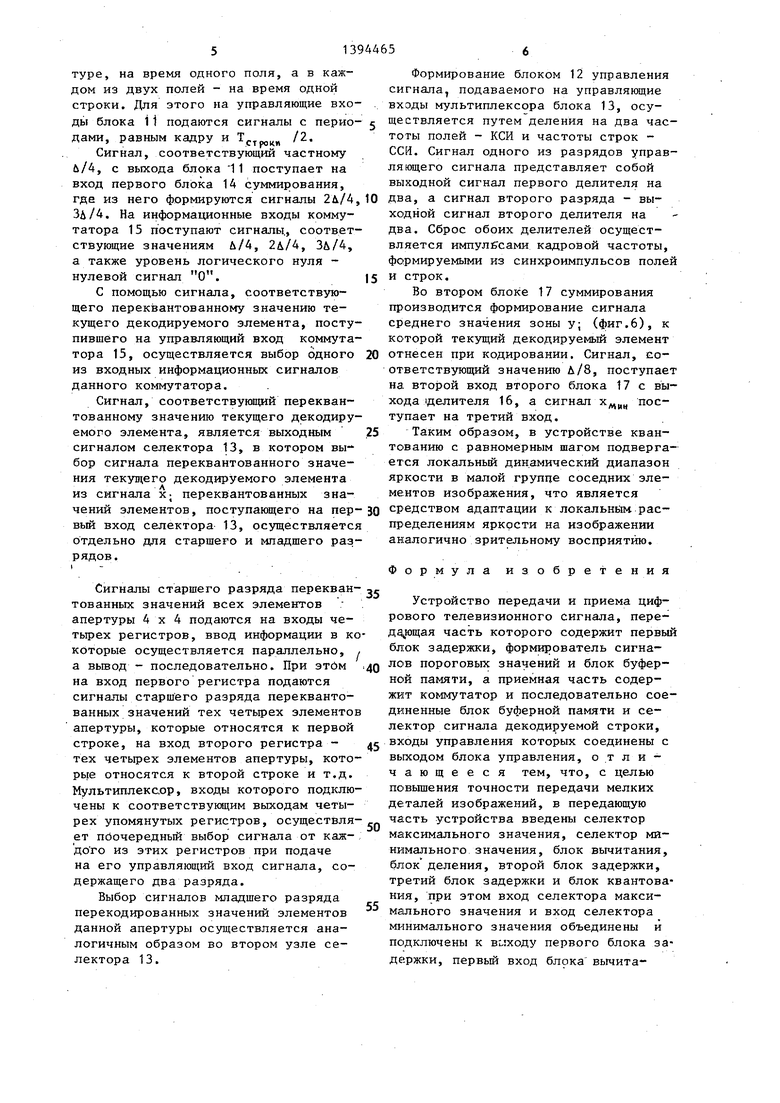

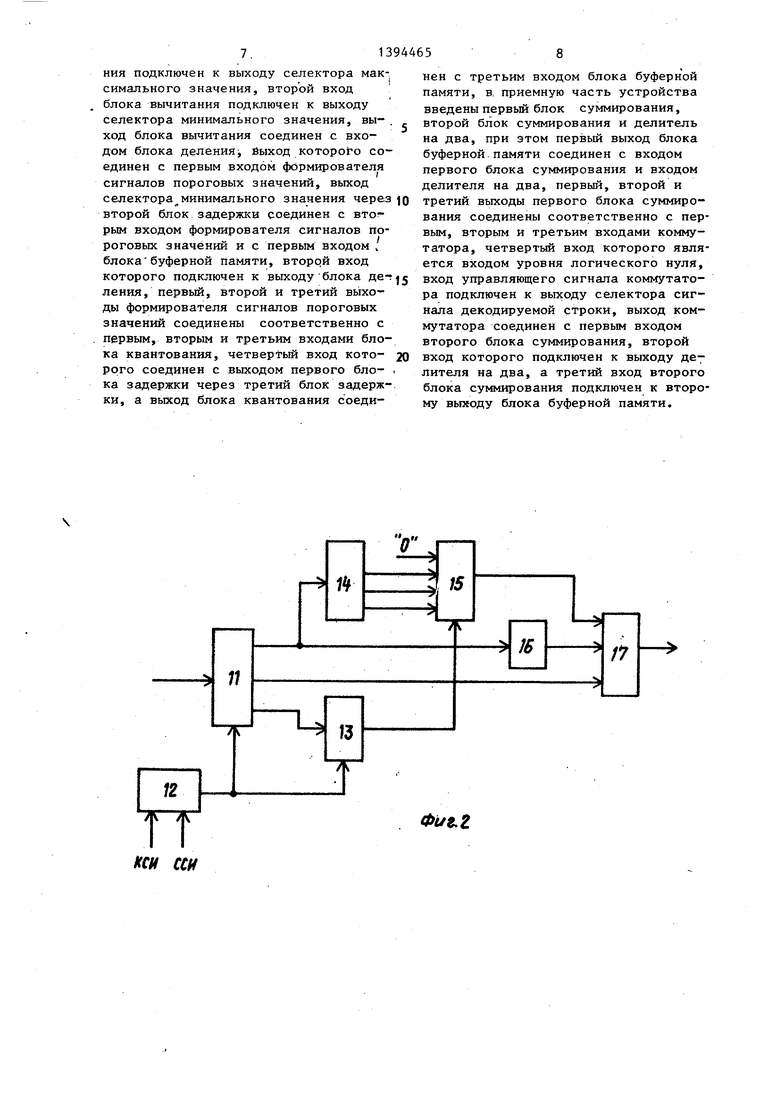

На фиг.1 представлена структурная электрическая схема передающей части устройства передачи и прием цифрового ТВ сигнала; на фиг.2 - структурна электрическая схема приемной части устройства передачи и приема цифрово го ТВ сигнала; на фиг.З - структурна электрическая схема селектора максимального, значения-, на фиг.4 - структурная электрическая схема блока выбора максимальных значений, входящег в состав селектора максимального значения; на фиг.З - структурная электрическая Схема квантователя, входящего в состав блока квантованияj на (Ьиг.6 - диаграмма видеосигнала.

Устройство передачи и приема цифрового ТВ сигнала содержит на передающей стороне (фиг.1) первый блок 1 задержки, селектор 2 максимального значения, селектор 3 минимального значения, блок 4 вычитания, второй блок 5 задержки, блок 6 деления, формирователь 7 сигналов пороговых значений, блок 8 квантования, третий блок 9 задержки, блок 10 буферной па- мяти, а на приемной стороне (фиг.2) - блок 11 буферной памяти, блок 12 управления, селектор 13 сигнала декодируемой строки, первый блок 14 суммирования, коммутатор 15, делитель 16 на два и второй блок 17 суммирования.

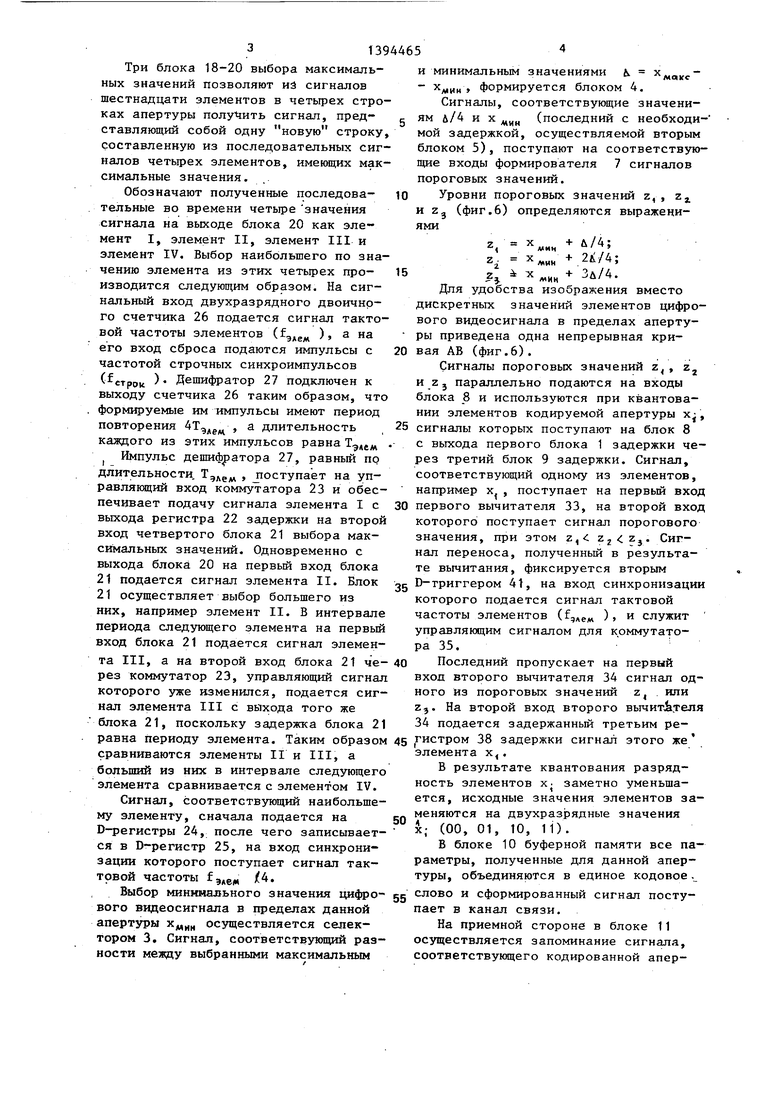

Селектор 2 максимального значения (фиг.З) содержит четыре однотипных блока 18-21 выбора максимальных значений, регистр 22 задержки, коммута- тор 23, D-регистры 24 и 25, счетчик 26, дешифратор 27. .

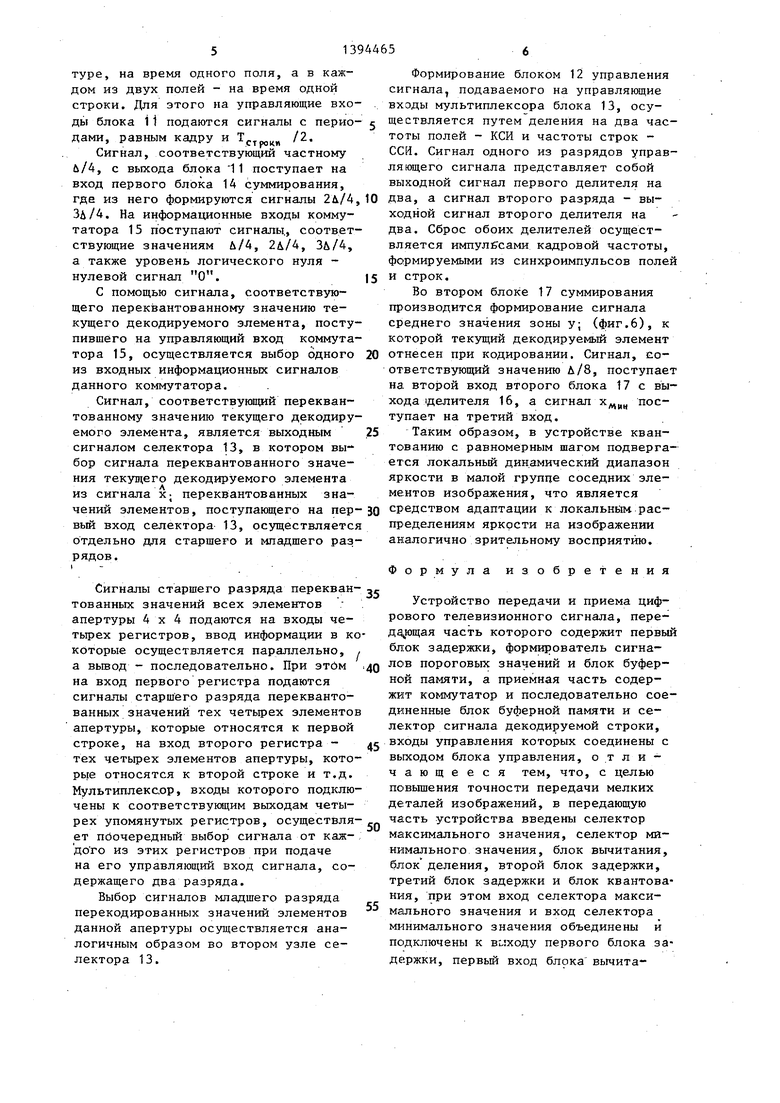

Блок 18 выбора максимальных значений (фиг.4) содержит вычитатель 28, D-триггер 29, коммутатор 30, первьш 31 и йторой 32 регистры задержки.

Селектор 3 минимального значения по составу аналогичен селектору 2 максимального значения. Отличие состоит в том, что управляющий вход коммутатора 30 в соответствующих блоках подключен не к прямому, а к инверсно7 му выходу D-триггера 29. Второй блок 5 задержки построен на D-регистрах.

с

Q 5 0 5

О Q

с

5

Блок 8 квантования содержит четы- ре отдельных однотипных квантователя. Каукдътй квантователь (фиг.5) содержит цервый 33 и второй 34 вычитатели, коммутатор 35, первый 36, второй 37, третий 38 и четвертьй 39 регистры задержки, первый 40 и второй 41 D- триггеры.

Блок 10 буферной памяти содержит D-регистры, ввод информации в которые осуществляется параллельно, а вывод - последовательно.

Блок 12 управления содержит формирователь импульсов кадровой частоты, первый делитель частоты на два и второй делитель частоты на два, при этом выход формирователя соединен с входом сброса каждого из делителей. Формирователь импульсов кадровой частоты содержит формирователь синхроимпульсов полей укороченной длительности и двухвходовую схему И.

В первом блоке 1 задержки осуществляется задержка цифрового видеосигнала на поле, а в -пределах каждого поля - на одну строку и формирование четырех сигналов, позволяющих создать апертуру 4x4 элемента ( элементы кодируемой апертуры обозначают через X;). ,

Селекция максимального значения цифрового видеосигнала в пределах апертуры х„д, осуществляется селек- : тором 2. При этом на первьй вход пер-j вого блока .18 выбора максимальных , значе ний поступает видеосигнал первой строки, а на второй вход - видеосигнал второй строки..

При вычитании первого элемента строки из первого элемента первой строки на выходе вычитателя 28 (фиг.4) формируется сигнал переноса. Этот сигнал фиксируется D-триггером 29, на вход синхронизации которого подается сигнал тактовой частоты элементов ( ) Р подаче сигнала переноса на управляющий вхйд коммутатора 30 на выход последнего через соответствующие регистры 31 и 32 задержки подается сигнал того элемента из двух, значение которого больше. Следова- тел:ьно, из сигналов восьми элементов, принадлежащих двум строкам, на выходе ком -1утатора 30 формируется сигнал,, соответствующий четьфем элементам, каждый из которых оказывается большим в своей паре.

313944654

Три блока 18-20 выбора максималь- и минимальным значениями ных значений позволяют из сигналов - , формируется блоком 4. шестнадцати элементов в четырех стро- Сигналы, соответствующие значени- ках апертуры полу 1ить сигнал, пред- g ям л/4 и х ,„ (последний с необходи- ставляющий собой одну новую строку, мой задержкой, осуществляемой вторым составленную из последовательных сиг- блоком 5), поступают на соответствую- напов четырех элементов, имеющих мак- щие входы формирователя 7 сигналов симапьные значения.пороговых значений.

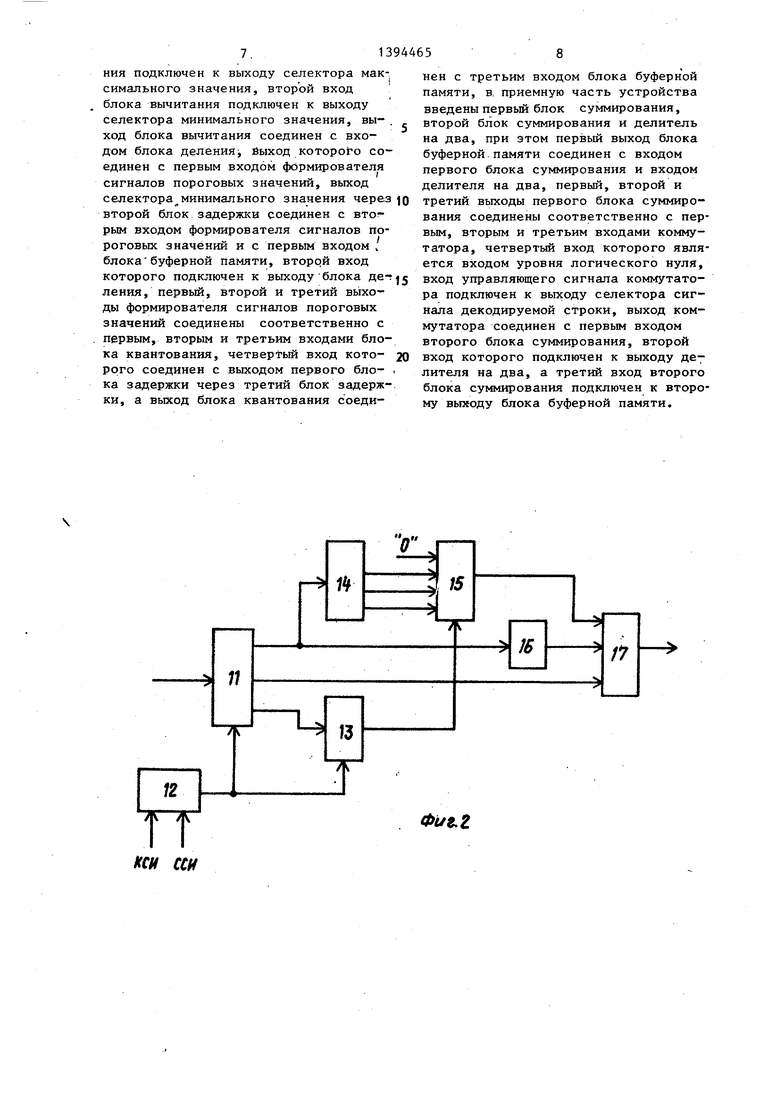

Обозначают полученные последова- ю Уровни пороговых значений z,, z тельные во времени четыре значения и Zj (фиг.6) определяются выражени- сигнала на выходе блока 20 как эле- ями

мент I, элемент II, элемент III иz «мн /

элемент IV, Выбор наибольшего по зна-z х „„ +

чению элемента из этих четырех про- 15 z „ + Зд/4.

.-Я. Лп ИН

изводится следующим образом. На сиг- Для удобства изображения вместо напьный вход двухразрядного двоично- дискретных значений элементов цифро- го счетчика 26 подается сигнал такто- вого видеосигнала в пределах аперту- вой частоты элементов ( ), а на ры приведена одна непрерывная кри- его вход сброса подаются импульсы с 20 вая АВ (фиг.6).

частотой строчных синхроимпульсов Сигналы пороговьк значений z, Zj (fстрои ). Дешифратор 27 подключен к и Zj параллельно подаются на входы выходу счетчика 26 таким образом, что блока 8 и используются при квантова- формируемые им импульсы имеют период нии элементов кодируемой апертуры х, повторения , а длительность 25 сигналы которых поступают на блок 8 каждого из этих импульсов равна Тд,е . с выхода первого блока 1 задержки чеИмпульс дешифратора 27, равный по рез третий блок 9 задержки. Сигнал, длительности. T,дg , jiocTynaeT на уп- соответствующий одному из элементов, равлякщий вход коммутатора 23 и обес- например х , поступает на первый вход печивает подачу сигнала элемента I с 30 первого вычитателя 33, на второй вход выхода регистра 22 задержки на второй которого поступает сигнал порогового вход четвертого блока 21 выбора мак- значения, при этом z, . Сиг- симальных значений. Одновременно с нал переноса, полученный в результа- выхода блока 20 на первый вход блока те вычитания, фиксируется вторым 21 подается сигнал элемента II. Блок -g D-триггером 41, на вход синхронизации 21 осуществляет выбор большего из которого подается сигнал тактовой них, например элемент II. В интервале частоты элементов (f,AeM ) служит периода следующего элемента на первый управляющим сигналом для крммутато- вход блока 21 подается сигнал элемен- ра 35.

та III, а на второй вход блока 21 ч е- 40 Последний пропускает на первый рез коммутатор 23, управляющий сигнал вход второго вычитателя 34 сигнал од- которого уже изменился, подается сиг- ного Из пороговых значений z, шти нал элемента III с выхода того же z,. На второй вход второго вычитЬтеля блока 21, поскольку задержка блока 21 34 подается задержанный третьим ре- равна периоду элемента. Таким образом 45 гистром 38 задержки сигнал этого же сравниваются элементы II и III, а элемента х,.

больший из них в интервале следующего результате квантования разряд- элемента сравнивается с элементом IV. элементов х. заметно уменьшаСигнал, соответствующий наибольше- - исходные значения элементов заму элементу, сначала подается на 50 « двухразрядные значения D-регистры 24, после чего записывает- . wO, 01, 10, 11).

ся в D-регистр 25, на вход синхрони- блоке 10 буферной памяти все па- зации которого поступает сигнал так- раметры, полученные для данной апер- товой частоты туры, объединяются в единое кодовое,.

Выбор минимального значения цифро- eg и сформированный сигнал посту- вого видеосигнала в пределах данной пает в канал связи, апертуры осуществляется селек- На приемной стороне в блоке 11 тором 3. Сигнал, соответствующий раз- осуществляется запоминание сигнала, ности между выбранными максимальным соответствующего кодированной апертуре, на время одного поля, а в каждом из двух полей - на время одной строки. Для этого на управляющие входы блока 11 подаются сигналы с перио- дами, равным кадру и Тстрокл

Сигнал, соответствующий частному &/4, с выхода блока 1 1 поступает на вход первого блока 14 суммирования, где из него формируются сигналы 2А/4, ЗА/4. На информационные входы коммутатора 15 поступают сигналы., соответствующие значениям Л/4, 2i/4, ЗЛ/4, а также уровень логического нуля нулевой сигнал О.

С помощью сигнала, соответствую- щего переквантованному значению текущего декодируемого элемента, поступившего на управляющий вход коммутатора 15, осуществляется выбор одного из входных информационных сигналов данного коммутатора.

Сигнал, соответствующий переквантованному значению текущего декодируемого элемента, является выходным сигналом селектора 13, в котором вы бор сигнала переквантованного значения текущего декодируемого элемента из сигнала Х; переквантованных значений элементов, поступающего на пер- вый вход селектора 13, осуществляется отдельно для старшего и мпадшего разрядов.

Сигналы старшего разряда перекван- тованных значений всех элементов апертуры 4x4 подаются на входы четырех регистров, ввод информации в ко которые осуществляется параллельно, а вьшод - последовательно. При этим на вход первого регистра подаются сигналы старшего разряда переквантованных значений тех четырех элементов апертуры, которые относятся к первой строке, на вход второго регистра - тех четырех элементов апертуры, которые относятся к второй строке и т.д. Мультиплексор, входы которого подключены к соответствующим выходам четырех упомянутых регистров, осуществля- ет пбочередньм выбор сигнала от каж- до го из этих регистров при подаче на его управляющий вход сигнала, содержащего два разряда.

Выбор сигналов младшего разряда перекодированных значений элементов данной апертуры осуществляется аналогичным образом во втором узле селектора 13.

j

0

5

0

5 30

0 5 „

Формирование блоком 12 управления сигнала, подаваемого на управляющие входы мультиплексора блока 13, осуществляется путем деления на два частоты полей - КСИ и частоты строк - ССИ. Сигнал одного из разрядов управляющего сигнала представляет собой выходной сигнал первого делителя на два, а сигнал второго разряда - выходной сигнал второго делителя на два. Сброс обоих делителей осуществляется импульсами кадровой частоты, формируемыми из синхроимпульсов полей и строк.

Во втором блоке 17 суммирования производится формирование сигнала среднего значения зоны у; (фиг.6), к которой текущий декодируемый элемент отнесен при кодировании. Сигнал, соответствующий значению Л/8, поступает на второй вход второго блока 17 с выхода делителя 16, а сигнал х поступает на третий вход.

Таким образом, в устройстве квантованию с равномерным шагом подвергается локальный динамический диапазон яркости в малой группе соседних элементов изображения, что является средством адаптации к локальным рас- щз еделениям яркости на изображении аналогично зрительному восприятию.

Формула изобретения

Устройство передачи и приема цифрового телевизионного сигнала, пере- часть которого содержит первый блок задержки, формирователь сигналов пороговых значений и блок буферной памяти, а приемная часть содержит коммутатор и последовательно соединенные блок буферной памяти и селектор сигнала декодируемой строки, входы управления которых соединены с выходом блока управления, о .т л и - чающееся тем, что, с целью повьппения точности передачи мелких деталей изображений, в передающую часть устройства введены селектор максимального значения, селектор минимального значения, блок вычитания, блок деления, второй блок задержки, третий блок задержки и блок квантования, при этом вход селектора макси- Мсшьного значения и вход селектора минимального значения объединены и подключены к в иходу первого блока задержки, первьй вход блока вычитания подключен к выходу селектора максимального значения, второй вход блока вычитания подключен к выходу селектора минимального значения, выход блока вычитания соединен с входом блока деления Выход которого соединен с первым входом формирователя сигналов пороговых значений, выход селектора минимального значения через второй блок задержки соединен с втог- рым входом формирователя сигналов пороговых значений и с первым входом блока буферной памяти, второй вход которого подключен к выходу блока деления, первый, второй и третий выходы формирователя сигналов пороговых значений соединены соответственно с первым, вторым и третьим входами блока квантования, четвертый вход кото- ррго соединен с выходом первого бло- ка задержки через третий блок задержки, а выход блока квантования соединен с третьим входом блока буферной памяти, в, приемную часть устройства введены первый блок суммирования, второй блок суммирования и делитель на два, при этом первый выход блока буферной памяти соединен с входом первого блока суммирования и входом делителя на два, первый, второй и третий выходы первого блока суммирования соединены соответственно с первым, вторым и третьим входами коммутатора, четвертый вход которого является входом уровня логического нуля, вход управляющего сигнала коммутатора подключен к выходу селектора сигнала декодируемой строки, выход коммутатора соединен с первым входом второго блока суммирования, второй вход которого подключен к выходу делителя на два, а третий вход второго блока суммирования подключен к второму выходу блока буферной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи и приема цифрового телевизионного сигнала | 1987 |

|

SU1506592A2 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Устройство компенсации сигнала царапин кинопленки | 1986 |

|

SU1392635A1 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Устройство компенсации сигнала дефектов киноленты | 1987 |

|

SU1494247A1 |

| Телевизионное устройство для счета объектов | 1980 |

|

SU935989A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

| Устройство кодирования телевизионного сигнала | 1986 |

|

SU1381730A1 |

| Устройство для выделения изображений подвижных объектов | 1987 |

|

SU1462373A1 |

Изобретение относится к области ТВ. Цель изобретения - повьшение точности передачи мелких деталей изображения. Устройство содержит на пере- данщей стороне блок задержки (БЭ) 1, формирователь 7 сигналов пороговых значений, блок 10 буферной памяти, введенные селекторы макс. 2 и минин. 3 значения, блок 4 вычитания, БЗ 5 и 9, блок 6 деления, блок 8 квантования, на приемной стороне блок буферной памяти блок управления, селектор сигнала декодируемой строки, коммутатор и введенные два блока суммирования, делитель на два. В БЗ 1 осуществляются задержка цифрового -видеосигнала на поле, а в пределах каждого поля на одну строку и формирование 4-х сигналов, позволяющих создать апертуру 4x4 эл-та. В устройстве квантованию с равномерным шагом подвергается локальный динамич. .диапазон яркости в малой-группе соседних эл-тов изображения, что является средством адаптации к локальным распределениям яркости на изображении аналогично зрительному восприятию. 6 ил. с S сг с

Фиг.5

Фцг.6

| Техника кино и телевидение, 1977, № 9, с | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Патент CIIIA | |||

| ЗАХВАТНОЕ УСТРОЙСТВО | 1972 |

|

SU420534A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-07—Публикация

1986-01-08—Подача