Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах цифрового телевидения с эффективным кодированием видеосигнала.

Цель изобретения - повышение информативности устройства за счет сокращения избыточности кодированного сигнала.

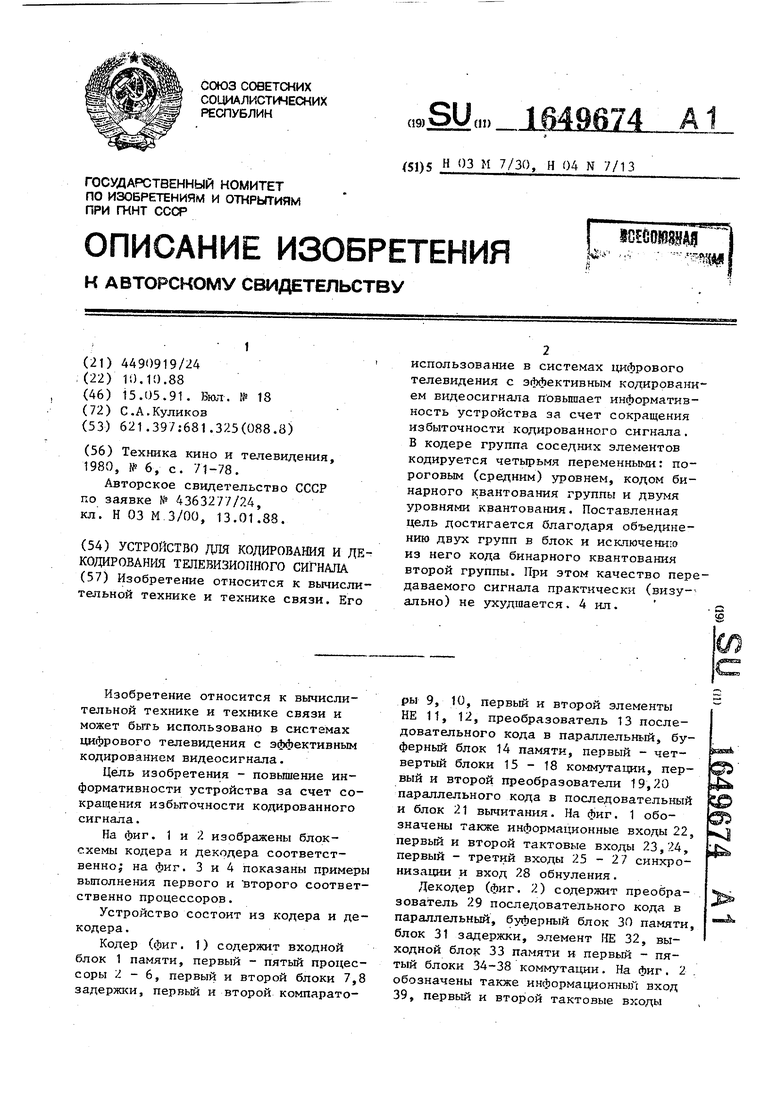

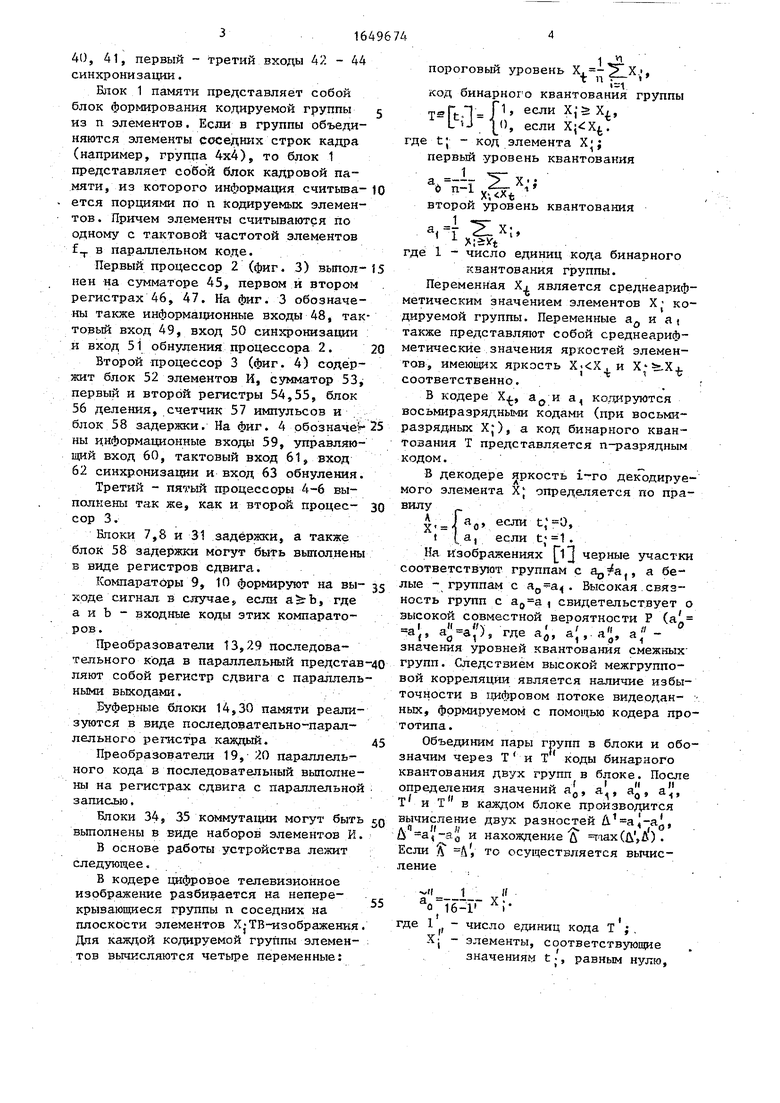

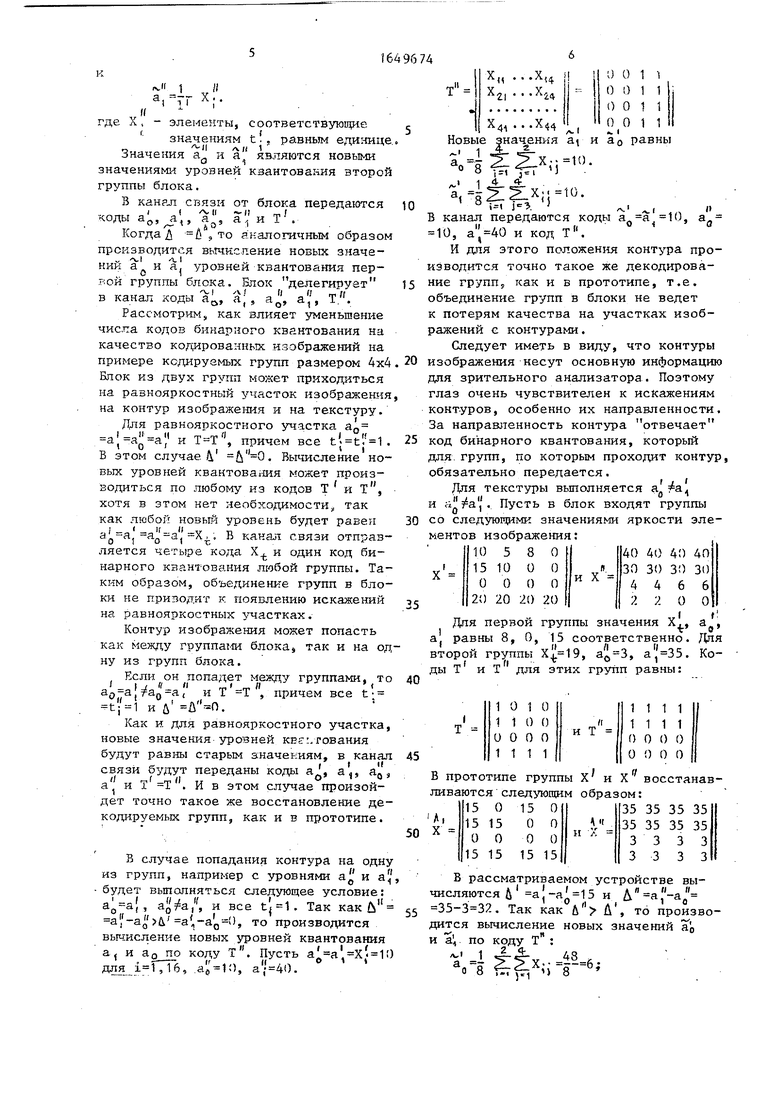

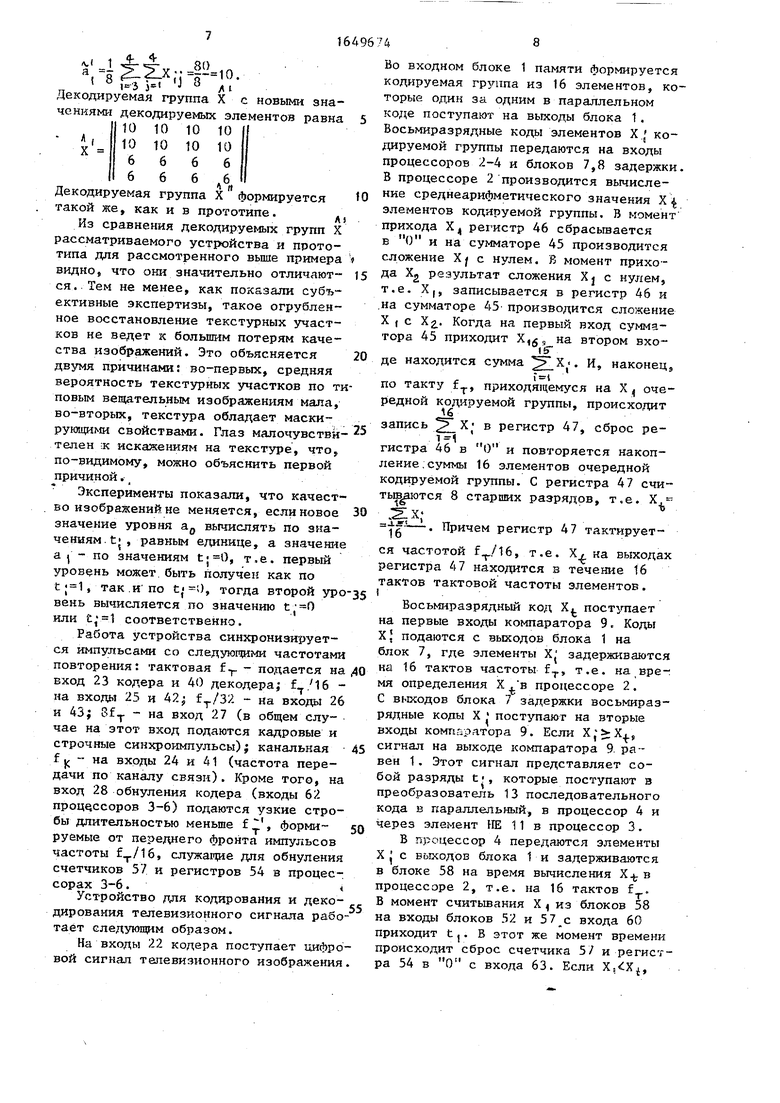

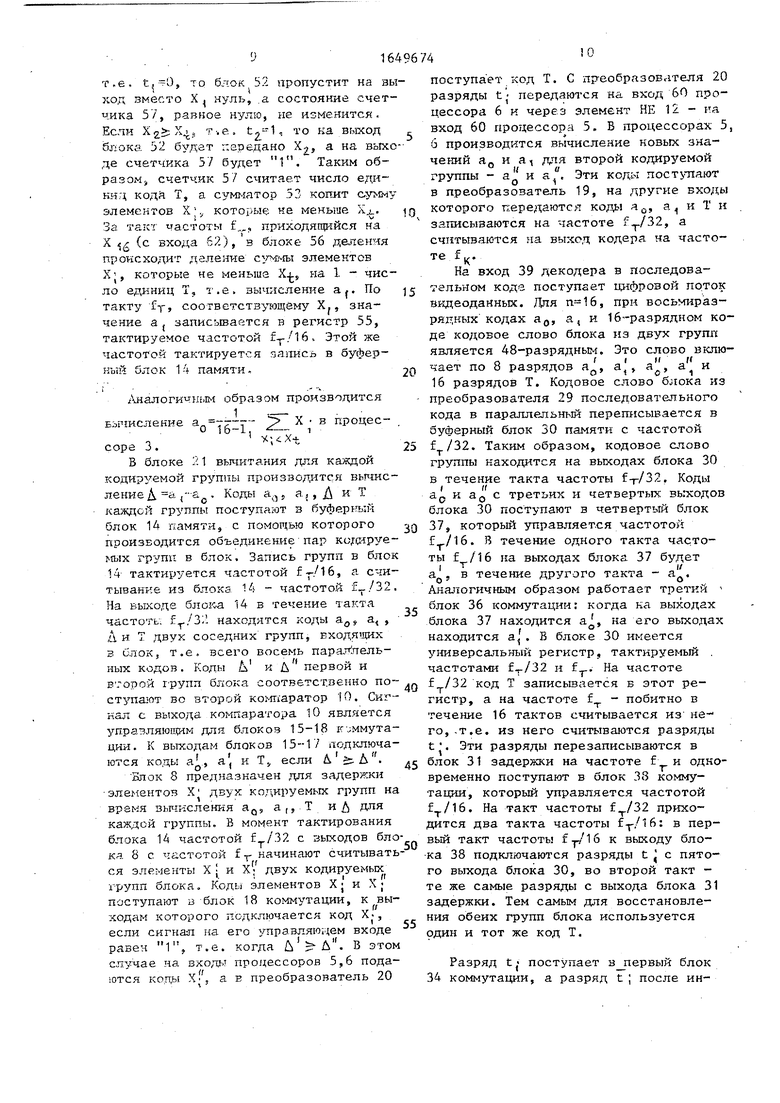

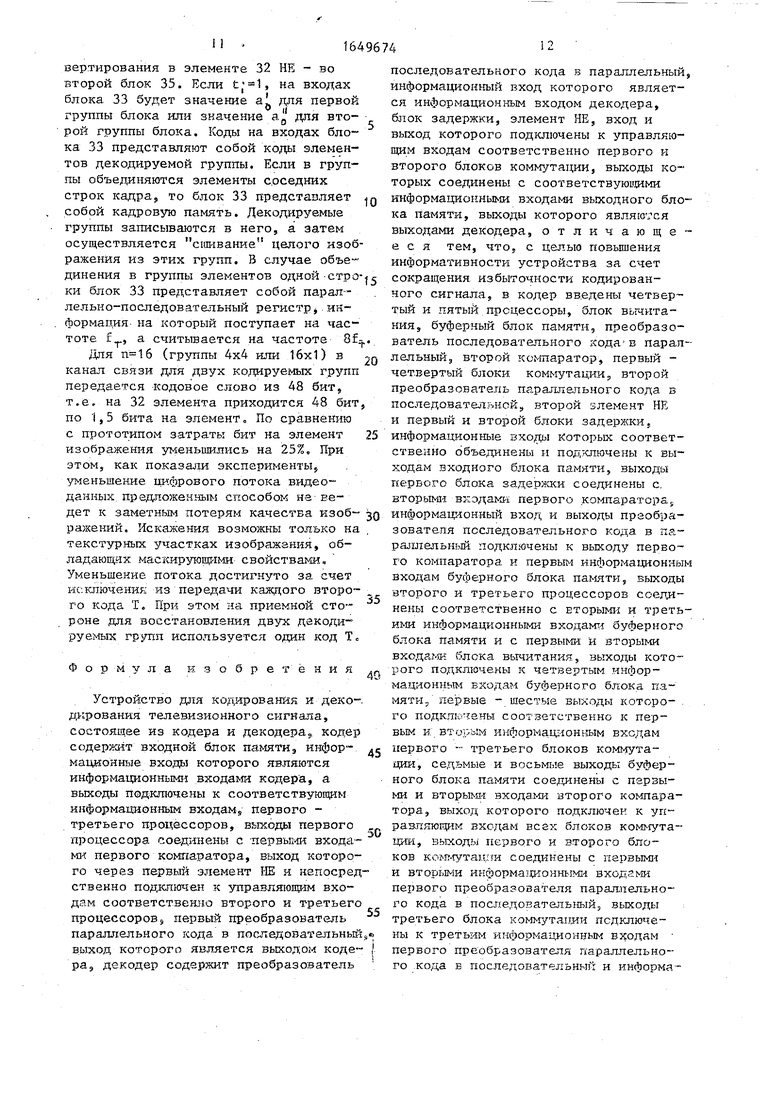

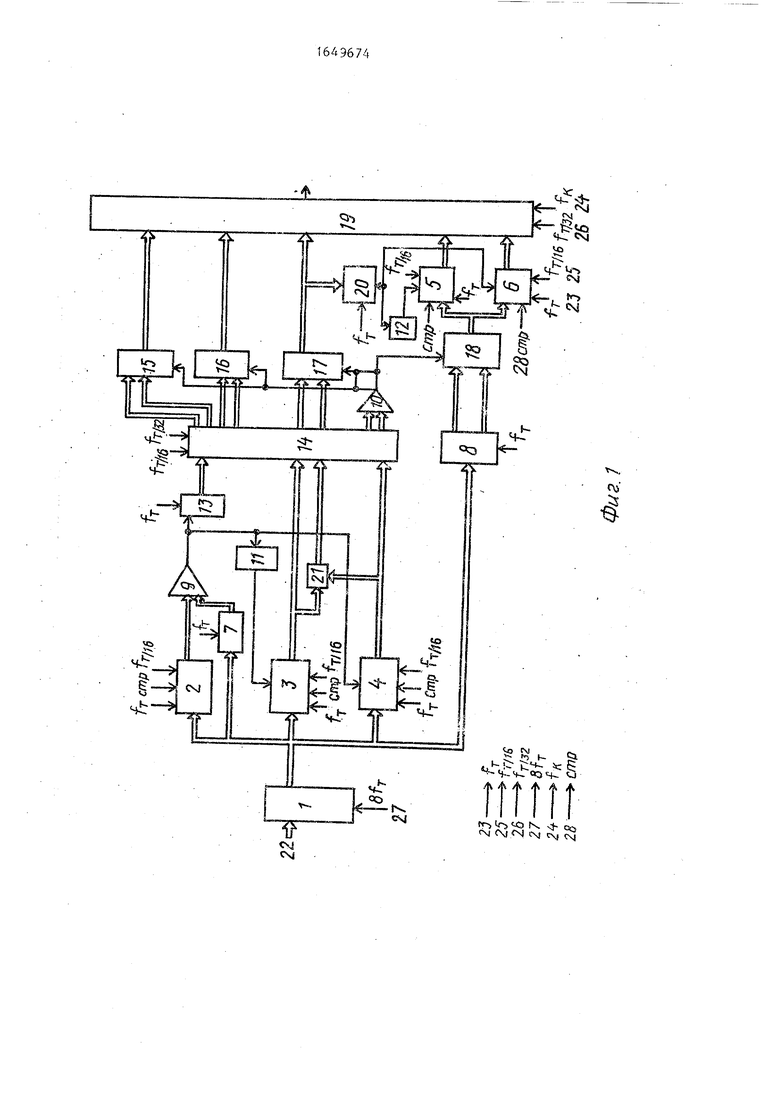

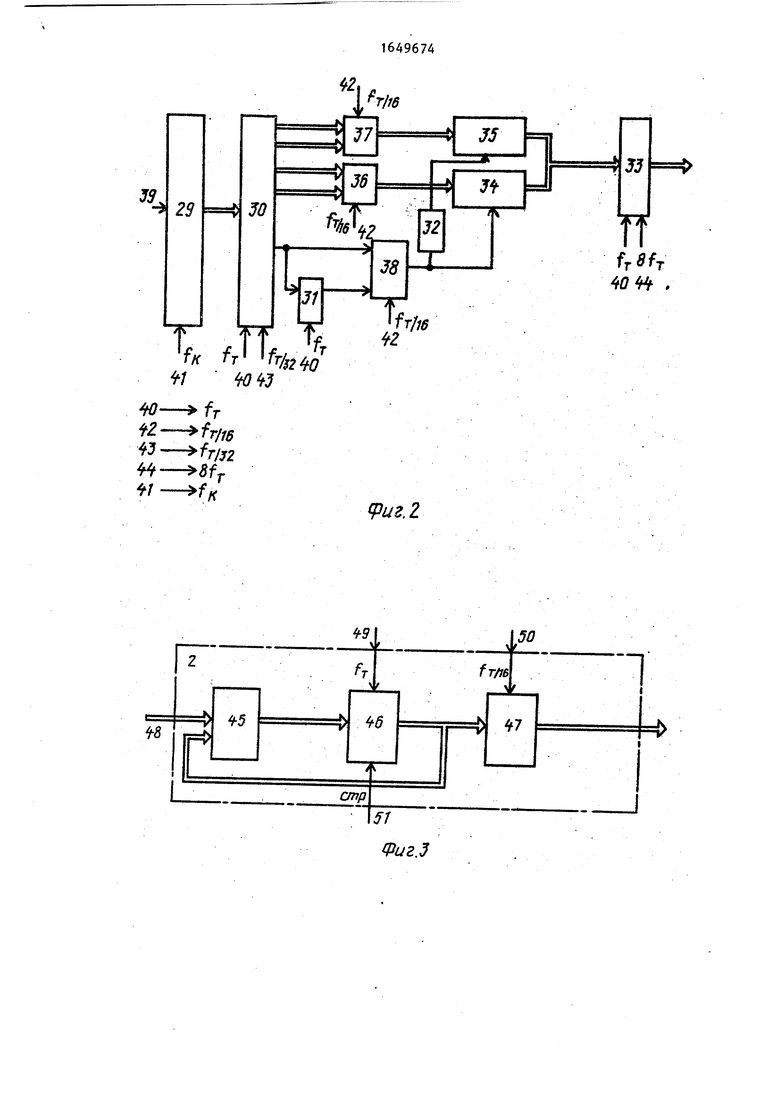

На фиг. 1 и 2 изображены блок- схемы кодера и декодера соответственно; на фиг. 3 и 4 показаны примеры выполнения первого и второго соответственно процессоров.

Устройство состоит из кодера и декодера .

Кодер (фиг. 1) содержит входной блок 1 памяти, первый - пятый процессоры 2-6, первый и второй блоки 7,8 задержки, первый и второй компараторы 9, 10, первый и второй элементы НЕ 11, 12, преобразователь 13 последовательного кода в параллельный, буферный блок 14 памяти, первый - четвертый блоки 15-18 коммутации, первый и второй преобразователи 19,20 параллельного кода в последовательный и блок 21 вычитания. На фиг. 1 обозначены также информационные входы 22, первый и второй тактовые входы 23,24, первый - третий входы 25-27 синхронизации и вход 28 обнуления.

Декодер (фиг. 2) содержит преобразователь 29 последовательного кода в параллельный, буферный блок 30 памяти, блок 31 задержки, элемент НЕ 32, выходной блок 33 памяти и первый - пятый блоки 34-38 коммутации. На фиг. 2 . обозначены также информационный вход 39, первый и второй тактовые входы

40, 41, первый - третий входы 42 - 44 синхронизации.

Блок 1 памяти представляет собой блок формирования кодируемой группы $ из п элементов. Если в группы объединяются элементы соседних строк кадра (например, группа 4x4), то блок 1 представляет собой блок кадровой памяти, из которого информация считыва- 10 ется порциями по п кодируемых элементов . Причем элементы считываются по одному с тактовой частотой элементов Јт в параллельном коде.

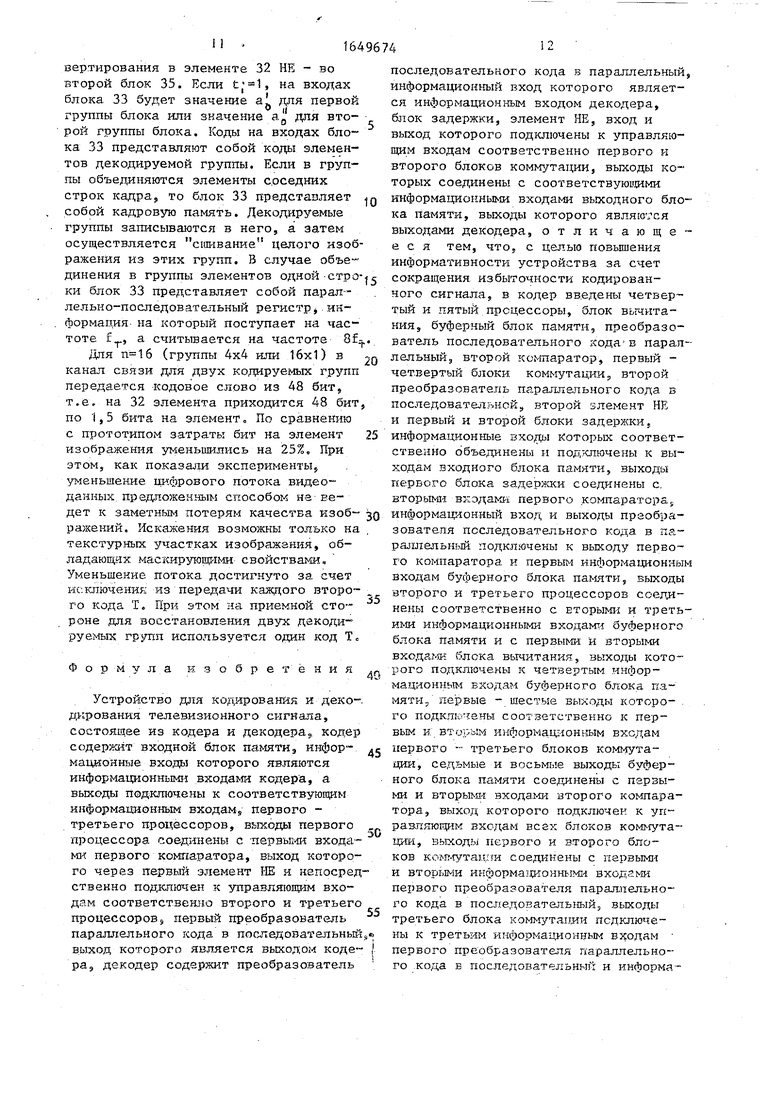

Первый процессор 2 (фиг. 3) выпол- 15 нен на сумматоре 45, первом и втором регистрах 46, 47. На фиг. 3 обозначены также информационные входы 48, тактовый вход 49, вход 50 синхронизации и вход 51 обнуления процессора 2. 20

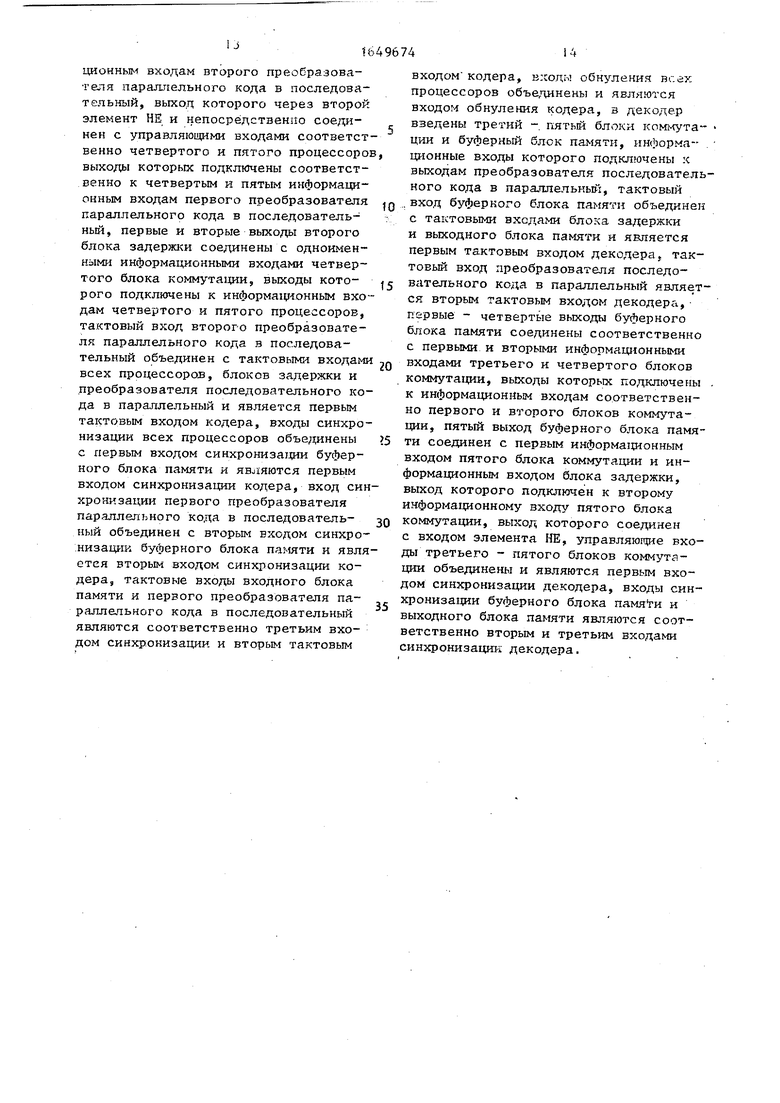

Второй процессор 3 (фиг. 4) содержит блок 52 элементов И, сумматор 53, первый и второй регистры 54,55, блок 56 деления, счетчик 57 импульсов и

Х

пороговый уровень X, код бинарного квантования группы jel

,П.Л П, если X, SXt, L -J |0, если . где t; - код элемента

первый уровень квантования

а --Ч Х;

второй уровень квантования

а i Z Xj

L ;i)Ct где 1 - число единиц кода бинарного

квантования группы.

Переменная X. является среднеарифметическим значением элементов Х кодируемой группы. Переменные ао и a t также представляют собой среднеарифметические значения яркостей элементов, имеющих яркость , и . соответственно.

В кодере Х, ао и а, кодируются восьмиразрядными кодами (при восьмиблок 58 задержки. На фиг. 4 обозначен-25 разрядных X;), а код бинарного кванны информационные входы 59, управляющий вход 60, тактовый вход 61, вход 62 синхронизации и вход 63 обнуления.

Третий - пятый процессоры 4-6 выполнены так же, как и второй процес- 30 сор 3.

Блоки 7,8 и 31 задержки, а также блок 58 задержки могут быть выполнены в виде регистров сдвига.

Компаряторы 9, Ю формируют на вы- 35 лые , группам с ходе сигнал в случае, если , где а и Ъ - входные коды этих компараторов.

Преобразователи 13,29 последовательного кода в параллельный представ-40 ляют собой регистр сдвига с параллельными выходами.

Буферные блоки 14,30 памяти реализуются в виде последовательно-параллельного регистра каждый.45

Преобразователи 19, 20 параллельного кода в последовательный выполнены на регистрах сдвига с параллельной . записью,

тозания Т представляется п-разрядны кодом.

В декодере яркость 1-го декодиру

мого элемента Х| определяется по пр вилу

А

X

, Га0, если , 1 (а, если . На изображениях черные участ соответствуют группам с ., а бе . Высокая связ

ность групп с свидетельствует высокой совместной вероятности Р (а

-Я1 я , -) ргтр , Я1 я II я II а( О I s ГЛ-е аО 1 ао 31

значения уровней квантования смежны групп. Следствием высокой межгруппо вой корреляции является наличие изб точности в цифровом потоке видеодан ных, формируемом с помощью кодера п тотипа.

Объединим пары групп в блоки и о значим через Т и Т коды бинарного квантования двух групп в блоке. Пос определения значений а, - Т и Т

о no в каждом блоке производится

Блоки 34, 35 коммутации могут быть сп вычисление двух разностей U aJ-a ,

АИ ff , I I

выполнены в виде наборов элементов И.

В основе работы устройства лежит следующее.

В кодере цифровое телевизионное изображение разбивается на неперекрывающиеся группы п соседних на плоскости элементов Х}-ТВ-изображенкя, Для каждой кодируемой группы элементов вычисляются четыре переменные:

и нахождение пахОУ,Д) .

/ i

Если Д -ft, то осуществляется вычисление

55

и

V

16-1

X

и

где 1 - число единиц кода Т ;,

Xj - элементы, соответствующие значениям t, равным нулю,

Х

пороговый уровень X, код бинарного квантования группы jel

,П.Л П, если X, SXt, L -J |0, если . где t; - код элемента

первый уровень квантования

а --Ч Х;

второй уровень квантования

а i Z Xj

L ;i)Ct где 1 - число единиц кода бинарного

квантования группы.

Переменная X. является среднеарифметическим значением элементов Х кодируемой группы. Переменные ао и a t также представляют собой среднеарифметические значения яркостей элементов, имеющих яркость , и . соответственно.

В кодере Х, ао и а, кодируются восьмиразрядными кодами (при восьмитозания Т представляется п-разрядным кодом.

В декодере яркость 1-го декодируелые , группам с

мого элемента Х| определяется по правилу

А

X

, Га0, если , 1 (а, если . На изображениях черные участки соответствуют группам с ., а бе- . Высокая связлые , группам с

ность групп с свидетельствует о высокой совместной вероятности Р (а

-Я1 я , -) ргтр , Я1 я II я II ° а( О I s ГЛ-е аО 1 ао 31

значения уровней квантования смежных групп. Следствием высокой межгрупповой корреляции является наличие избыточности в цифровом потоке видеодан- ных, формируемом с помощью кодера прототипа.

Объединим пары групп в блоки и обозначим через Т и Т коды бинарного квантования двух групп в блоке. После определения значений а, - Т и Т

о no в каждом блоке производится

вычисление двух разностей U aJ-a ,

вычисление двух разностей U aJ-a ,

АИ ff , I I

и нахождение пахОУ,Д) .

/ i

Если Д -ft, то осуществляется вычисление

и

V

16-1

X

и

где 1 - число единиц кода Т ;,

Xj - элементы, соответствующие значениям t, равным нулю,

x

где X, - элементы, соответствующие

значениям t, равным елияице

а являются новыми значениями уровней квантования второй группы блока.

В канал связи от блока передаются

Значения а

.

/о ИТ/ КогдаД fi , то нелогичным образом

9

вычкс

р.ение новых значепрсизводитсяний а и я. уровней квантования пергой группы блока. Елок делегирует

канал коды а

с.

V I

;

и

I

10 а1

. It

Рассмотрим, как влияет уменьшение числа кодов бинарного квантования на качество кодированных изображений на примере кодируемых групп размером 4x4 Блок из двух групп может приходиться на равнояркостный участок изображения на контур изображения и на текстуру.

Для равнояркостного участка а о

я«--а1|

-а. а„-а

и , причем все

tUt / i

-а -а -а, и , причем все 1. В этом случае 4 . Вычисление новых уровней квактова шя может производиться по любому из кодов Т и Т, хотя в этом нет необходимости„ так как любой новый уровень будет равен а а| Х,. В канал связи отправляется четыре кода Xt и один код бинарного квантования любой группы. Таким образом, объединение групп в блоки не призо тит к появлению искажений на равнояркостных участках.

Контур изображения может попасть как между группами блока, так и на одну из групп блока.

Если он попадет между группами, то

и Т Т . причем все t-

;.. . i

и Д -и -(К

Как и для равнояркостного участка, новые значения уровней квг:,гования будут равны старым значениям, в канал связи будут переданы коды a , at, a0}

- 4- - 1 -tj -I

а и Т Т . И в этом случае произойдет точно такое же восстановление декодируемых групп, как и в прототипе.

О О О О О О

1 1

W41

л-i

Новые значения а и

- )-ю.

0011

.. I

ао равны

ао 8

л-1 1

i-1 J

4 А

5

i i-to- ,..,,„ .

В канал передаются коды (), ад 10, и код Т.

И для этого положения контура производится точно такое же декодирование групп5 как и в прототипе, т.е. объединение групп в блоки не ведет к потерям качества на участках изображений с контурами.

Следует иметь в виду, что контуры 0 изображения несут основную информацию для зрительного анализатора. Поэтому глаз очень чувствителен к искажениям контуров, особенно их направленности.

5

0

За направленность контура отвечает код бинарного квантования, который для групп, по которым проходит контур, обязательно передается.

Для текстуры выполняется afl a и . Пусть в блок входят группы со следуют имк значениями яркости элементов изображения:

30

35

40

ды Т1 и T для этих групп равны:

Т

В прототипе группы X и Xf восстанавливаются следующим образом:

50

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер сигнала изображения | 1989 |

|

SU1730727A1 |

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Кодер телевизионного сигнала | 1988 |

|

SU1569990A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1986 |

|

SU1424125A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах цифрового телевидения с эффективным кодированием видеосигнала повышает информативность устройства за счет сокращения избыточности кодированного сигнала. В кодере группа соседних элементов кодируется четырьмя переменными: пороговым (средним) уровнем, кодом бинарного квантования группы и двумя уровнями квантования. Поставленная цель достигается благодаря объединению двух групп в блок и исключению из него кода бинарного квантования второй группы. При этом качество передаваемого сигнала практически (визу- ально) не ухудшается. 4 ил. в

В случае попадания контура на одну из групп, например с уровнями аЈ и а,

будет выполняться следующее условие:

, -„I ч

а

а

и

В рассматриваемом устройстве вы(. . .числяются u и Д. а,-а0

все . Так какй 55 . Так как & Д1, то произвоdQ j , dp ( , n DI-C - i . idJ4 J4.iift. j

a -a u a 1-a 0:(), то производится вычисление новых уровней квантования а, и agjrro коду Т. Пусть ) ,16, , .

дится вычисление новых значений а 0 и а, по коду Тв :

- 1 s ,

дится вычисление новых значений а 0 и а, по коду Тв :

- 1 s ,

Ј l4-4-x..

( ,, o1U.

b Јз IJ 8 /I

Декодируемая группа X

i X

Л)

с новыми значениями декодируемых элементов равна

10 10 10 10

10 10 10 10 6666 6 6 6 46й Декодируемая группа X формируется такой же, как и в прототипе.

Из сравнения декодируемых групп X рассматриваемого устройства я прототипа для рассмотренного выше примера видно, что они значительно отличают- ся. Тем не менее, как показали субъективные экспертизы, такое огрубленное восстановление текстурных участков не ведет к большим потерям качества изображений. Это объясняется двумя причинами: во-первых, средняя вероятность текстурных участков по типовым вещательным изображениям мала, во-вторых, текстура обладает маскирующими свойствами. Глаз малочувстви телен к искажениям на текстуре, что, по-видимому, можно объяснить первой причиной.t

Эксперименты показали, что качество изображений не меняется, если новое значение уровня а0 вычислять по значениям t«, равным единице, а значени а | - по значениям , т,е. первый уровень может быть получен как по

55

45

tj 1, так и по , тогда второй УРо-35 вень вычисляется по значению t( или t, соответственно.

Работа устройства синхронизируется импульсами со следующими частотами повторения: тактовая fr - подается на (40 вход 23 кодера и 40 декодера; f7 16 - на входы 25 и 42} fT/32 - на входы 26 и 43; 8fT - на вход 27 (в общем случае на этот вход подаются кадровые и строчные синхроимпульсы); канальная f ц - на входы 24 и 41 (частота передачи по каналу связи). Кроме того, на вход 28 обнуления кодера (входы 62 процессоров 3-6) подаются узкие стробы длительностью меньше f , формируемые от переднего фронта импульсов частоты fT/16, служащие для обнуления счетчиков 57 и регистров 54 в процессорах 3-6.

Устройство для кодирования и декодирования телевизионного сигнала работает следующим образом.

На входы 22 кодера поступает цифровой сигнал телевизионного изображения.

50

Во входном блоке 1 памяти формируется кодируемая группа из 16 элементов, которые один за одним в параллельном коде постз пают на выходы блока 1 . Восьмиразрядные коды элементов X кодируемой группы передаются на входы процессоров 2-4 и блоков 7,8 задержки В процессоре 2 производится вычисление среднеарифметического значения X элементов кодируемой группы. В момент прихода Xj регистр 46 сбрасывается в О и на сумматоре 45 производится сложение Xf с нулем. В момент прихода Х результат сложения Xj с нулем, т.е. X,, записывается в регистр 46 и на сумматоре 45 производится сложение X ( с Xg.. Когда на первый вход сумматора 45 приходит Х,Ј,на втором вхо1Ь

Хде находится сумма по такту f

приходящемуся на

И, наконец

X , очеJ-, uymiuf L.n no. /v л

редкой кодируемой группы, происходит

1 О

запись B Регистр 47, сброс регистра 46 в О и повторяется накопление суммы 16 элементов очередной кодируемой группы. С регистра 47 считываются 8 старших разрядов, т.е. X

IQ

S1 х;

tjr- Причем регистр 47 тактирует- I Ь

ся частотой , т.е. X, на выходах регистра 47 находится в течение 16 тактов тактовой частоты элементов.

5

5

Восьмиразрядный код Х. поступает на первые входы компаратора 9, Коды X | подаются с выходов блока 1 на блок 7, где элементы X задерживаются

LT

т .е.

на вре- 2.

0

на 16 тактов частоты мя определения X . в процессоре С выходов блока 7 задержки восьмиразрядные коды X поступают на вторые входы комп.-.р-чтора 9. Если , сигнал на выходе компаратора 9 равен 1. Этот сигнал представляет собой разряды t, которые поступают в преобразователь 13 последовательного кода в параллельный, в процессор 4 и через элемент НЕ 11 в процессор 3.

В процессор 4 передаются элементы X { с выходов блока 1 и задерживаются в блоке 58 на время вычисления Х. в процессоре 2, т.е. на 16 тактов fT. В момент считывания X из блоков 58 на входы блоков 52 и входа 60 приходит t j. В этот же момент времени происходит сброс счетчика 5/ и регистра 54 в 0м с входа 63. Если Х,ОГ4,

т.е. t(0, то блок S2 пропустит на выход змее, т о X нуль, а состояние ечет- иика 5/, равное нулю, не изменится, Еста т.е. , то ка выход 6j OKi 32 будет ::аоецано X, а на выходе счетчика 5/ будет 1. Таким образом, счетчик 5/ считает число ели- нч j кода Т, а сумматор 5 копит с,умму элементов X;, которые ке меньше Xj. За так частоты i ., приходящийся ча X (с входа 6Л,), в блоке 56 деле.нмя происходит деление суммы элементов X |, которые че меньше Х.$ на 1 - число единиц Т, i.e. вычисление ар По такту f-r соответствующему X., значение а( записывается и регистр 55, тактируемое частотой fT 16, Этой же частотой тактируется талисл в буферный блок 1 памяти.

Аналоги ьглм образом производится

j

вычисление а / Х в пР°Цес

° , -

-1

,

соре 3.

В блоке - 1 вычитания для каждой кодируемой группы производится вычис- ление Д с, - а . Коды а0 , а , , j и Т каждой группы поступают в буферный блок 14 памяти, с ПОМОРЬЮ которого производится объединение пар кодируемых групп в блок. Запись групп в блок 14 тактируется частотой , а считывание из блока 1 - частотой Гт/32. На ъыходе блока 14 в течение тат та частоть ГТ/ЗЛ находятся коды а0, а , А и Т двух соседних групп, гходящих в сток, т.е. всего восемь паряУлель- ных кодов. Коды & и А первой и в ГОРОЙ групп блока соответственно поступает во второй компаратор 10. Сигнал с выхода компаратора 10 является управляющем для блоков 15-18 к ммута- ции. К выходам блоков 15--1/ лод ключа- и Т

ют с я коцы а, а ( и Т, если ьА. Блок 8 предназначен для задержки элементов Xе кодируемых групп на время вычисления aQS а,, Т иД для каждой группы. В момент тактирования блока 14 частотой с выходов блокя Ь с частотой f-r- начинают считывать1 г

ся элементы X ; и Х- двух кодируемых

t ff iрулп блока Коды элементов Xj и j

поступают j блок 18 коммутации, к выходам которого подключается код Х-, если сигнал на его управляющем входе равен 1, т.е. когда . В этом случае ча входы процессоров 5,6 подаются копы X , а в преобразователь 20

,- 50

5

о

5

0

5

поступает код Т. С преобразователя 20 разряды t - передаются вход 60 процессора 6 и через элемент НЕ 12 - на вход 60 процессор 5. В процессорах 5, 6 производится вычисление новых значений а0 и а ч для второй кодируемой группы - а и а. Эти коды поступают в преобразователь 19, на другие входы Q которого передаются коды ай, э1 и Т и записываются на частоте fT/32, a считываются на выход кодера на частоте fK.

На вход 39 декодера в последовательном коде поступает цифровой поток видеоданных. Для п-16, при восьмиразрядных кодах а0, а, и 16-разрядном коде кодовое слово блока из двух групп является 48-разрядным. Это слово включает по 8 разрядов а, a (t а, а и 16 разрядов Т. Кодовое слово блока из преобразователя 29 последовательного кода в параллельный переписывается в буферный блок 30 памяти с частотой fT/32. Таким образом, кодовое слово группы находится на выходах блока 30 в течение такта частоты f-r/32. Коды а0 к ао с третьих и четвертых выходов блока 30 поступают в четвертый блок 37, который управляется частотой fr/16. В течение одного такта частоты f /16 на выходах блока 37 будет а. в течение другого такта - а . Аналогичным образом работает третий блок 36 коммутации: когда ьа выходах блока 37 находится а, на его выходах находится а|. В блоке 30 имеется универсальный регистр, тактируемый частотами и fr. На частоте fT/32 код Т записывается в этот регистр, а на частоте f - побитно в течение 16 тактов считывается из него, т.е. из него считываются разряды t . Эти разряды перезаписываются в блок 31 задержки на частоте f и одновременно поступают в блок 38 коммутации, который управляется частотой fT/16. На такт частоты fT/32 приходится два такта частоты fr/16: в первый такт частоты к выходу блока 38 подключаются разряды t | с пятого выхода блока 30, во второй такт - те же самые разряды с выхода блока 31 задержки. Тем самым для восстановления обеих групп блока используется один и тот же код Т.

Разряд t(- поступает в первый блок 34 коммутации, а разряд t ; после инвертирования в элементе 32 НЕ - во второй блок 35. Если t( 1, на входах блока 33 будет значение а для первой группы блока или значение а Ј для второй гоуппы блока. Коды на входах блока 33 представляют собой коды элементов декодируемой группы. Если в группы объединяются элементы соседних строк кадра, то блок 33 представляет собой кадровую память. Декодируемые группы записываются в него, а затем осуществляется сшивание целого изображения из этих групп. В случае объединения в группы элементов одной стро-|5 сокращения избыточности кодировании блок 33 представляет собой параллельно-последовательный регистр, ик- формапия на который поступает на часчого сигнала, в кодер введены четве тый и пятый процессоры, блок вычита ния, буферный блок памяти, преобраз ватель последовательного кода в пар лельный., второй компаратор, первый четвертый блоки коммутации,, второй преобразователь параллельного кода последовательной., второй элемент НЕ и первый и второй блоки задержки, информационные входы Которых соотве ственно объединены и подключены к в ходам входного блока памяти, выходы первого блока задержки соединены с вторыми в:: одами первого компаратора информационный вход и выходы преобр зователя последовательного года в п раллельный подключены к выходу перв го компаратора и первым информацион входам буферного блока памяти, выхо второго и третьего процессоров соед нены соответственно с вторыми и тре ими информационными входами буферно блока памяти и с первыми и вторыми входами блока вычитания, выходы кот рого подключены к четвертым информационным входам буферного блока па мяти, первые - шестые выходы которо го подключены соответственно к первым и информационным входам первого третьего блоков коммутации, седьмые и восьмые выходы буфер ного блока памяти соединены с первы ми и вторыми входами второго компар тора, выход которого подключен к уп равляющим входам всех блоков коммут ции, пыходы первого и второго блоков коммутации соединены с первыми и вторыми информационными входами первого преобразователя параллельно го кода в последовательный, выходы третьего блока коммутации подключены к третьим информационным входам первого преобразователя параллельно го кода в последовательный и информ

тоте гт, а считывается на частоте

8ft

Для (группы 4x4 или 16x1) в канал связи для двух кодируемых групп передается кодовое слово из 48 бит, т.е. на 32 элемента приходится 48 бит по 1,5 бита на элемент„ По сравнению с прототипом затраты бит на элемент изображения уменьшились на 25%. При этом, как показали эксперименты, уменьшение цифрового потока видеоданных предложенным способом не ведет к заметным потерям качества изображений. Искажения возможны только на текстурных участках изображения, обладающих маскирующими свойствами. Уменьшение потока достигнуто за счет ис ключения из передачи каждого второго кода Т. При этом на приемной стороне для восстановления двух декодируемых групп используется один код Тс

40

45

Формула изобретения

Устройство для кодирования и декодирования телевизионного сигнала, состоящее из кодера и декодера,, кодер содержит входной блок памяти3 информационные входы которого являются информационными входами кодера, а выходы подключены к соответствующим информационным входам„ первого - третьего процессоров, выходы первого процессора соединены с первыми входа- мк первого компаратора, выход которого через первый элемент НЕ и непосредственно подключен к управляющим вхо- дпм соответственно второго и третьего процессоров, первый преобразователь параллельного кода в последовательный выход которого является выходом коде- / раэ декодер содержит преобразователь

50

55

последовательного кода в параллельный, информационный вход которого является информационным входом декодера, блок задержки, элемент НЕ, вход и выход которого подключены к управляющим входам соответственно первого и второго блоков коммутации, выходы которых соединены с соответствующими информационными входами выходного блока памяти, выходы которого являются выходами декодера, отличающееся тем, что, с целью повышения информативности устройства за счет

сокращения избыточности кодирован

5

д

0

5

0

5

/

0

5

чого сигнала, в кодер введены четвертый и пятый процессоры, блок вычитания, буферный блок памяти, преобразователь последовательного кода в параллельный., второй компаратор, первый - четвертый блоки коммутации,, второй преобразователь параллельного кода в последовательной., второй элемент НЕ и первый и второй блоки задержки, информационные входы Которых соответственно объединены и подключены к выходам входного блока памяти, выходы первого блока задержки соединены с вторыми в:: одами первого компаратора;, информационный вход и выходы преобразователя последовательного года в параллельный подключены к выходу первого компаратора и первым информационным входам буферного блока памяти, выходы второго и третьего процессоров соединены соответственно с вторыми и третьими информационными входами буферного блока памяти и с первыми и вторыми входами блока вычитания, выходы которого подключены к четвертым информационным входам буферного блока памяти, первые - шестые выходы которого подключены соответственно к первым и информационным входам первого третьего блоков коммутации, седьмые и восьмые выходы буферного блока памяти соединены с первыми и вторыми входами второго компаратора, выход которого подключен к управляющим входам всех блоков коммутации, пыходы первого и второго блоков коммутации соединены с первыми и вторыми информационными входами первого преобразователя параллельного кода в последовательный, выходы третьего блока коммутации подключены к третьим информационным входам первого преобразователя параллельного кода в последовательный и информационным входам второго преобразователя параллельного кода в последовательный, выход которого через второй элемент НЕ и непосредственно соединен с управляющими входами соответственно четвертого и пятого процессоров выходы которых подключены соответственно к четвертым и пятым информационным входам первого преобразователя параллельного кода в последовательный, первые и вторые выходы второго блока задержки соединены с одноименными информационными входами четвертого блока коммутации, выходы кото- рого подключены к информационным входам четвертого и пятого процессоров, тактовый вход второго преобразователя параллельного кода в последовательный объединен с тактовыми входами всех процессоров, блоков задержки и преобразователя последовательного кода в параллельный и является первым тактовым входом кодера, входы синхронизации всех процессоров объединены с первым входом синхронизации буферного блока памяти и являются первым входом синхронизации кодера, вход синхронизации первого преобразователя параллельного кода в последователь- ный объединен с вторым входом синхронизации буферного блока памяти и является вторым входом синхронизации кодера, тактовые входы входного блока памяти и первого преобразователя параллельного кода в последовательный являются соответственно третьим входом синхронизации и вторым тактовым

Q « 5 0

5

входом кодера, входы обнуления всех процессоров объединены и являются входом обнуления кодера, з декодер введены третий - пятый блоки коммутации и буферный блок памяти, информационные входы которого подключены к выходам преобразователя последовательного кода в параллельный, тактовый .вход буферного блока памяти объединен с тактовыми входами блока задержки и выходного блока памяти и является первым тактовым входом декодера f тактовый вход преобразователя последовательного кода в параллельный является вторым тактовым входом декодера, первые - четвертые выходы буферного блока памяти соединены соответственно с первыми и вторыми информационными входами третьего и четвертого блоков коммутации, выходы которых подключены к информационным входам соответственно первого и второго блоков коммутации, пятый выход буферного блока памяти соединен с первым информационным входом пятого блока коммутации и информационным входом блока задержки, выход которого подключен к второму информационному входу пятого блока коммутации, выход которого соединен с входом элемента НЕ, управляющие входы третьего - пятого блоков коммутации объединены и являются первым входом синхронизации декодера, входы синхронизации буферного блока памяти и выходного блока памяти являются соответственно вторым и третьим входами синхронизации декодера.

Фиг А

| Техника кино и телевидения, 1980, № 6, с | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Авторское свидетельство СССР по заявке № 4363277/24, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1988-10-10—Подача