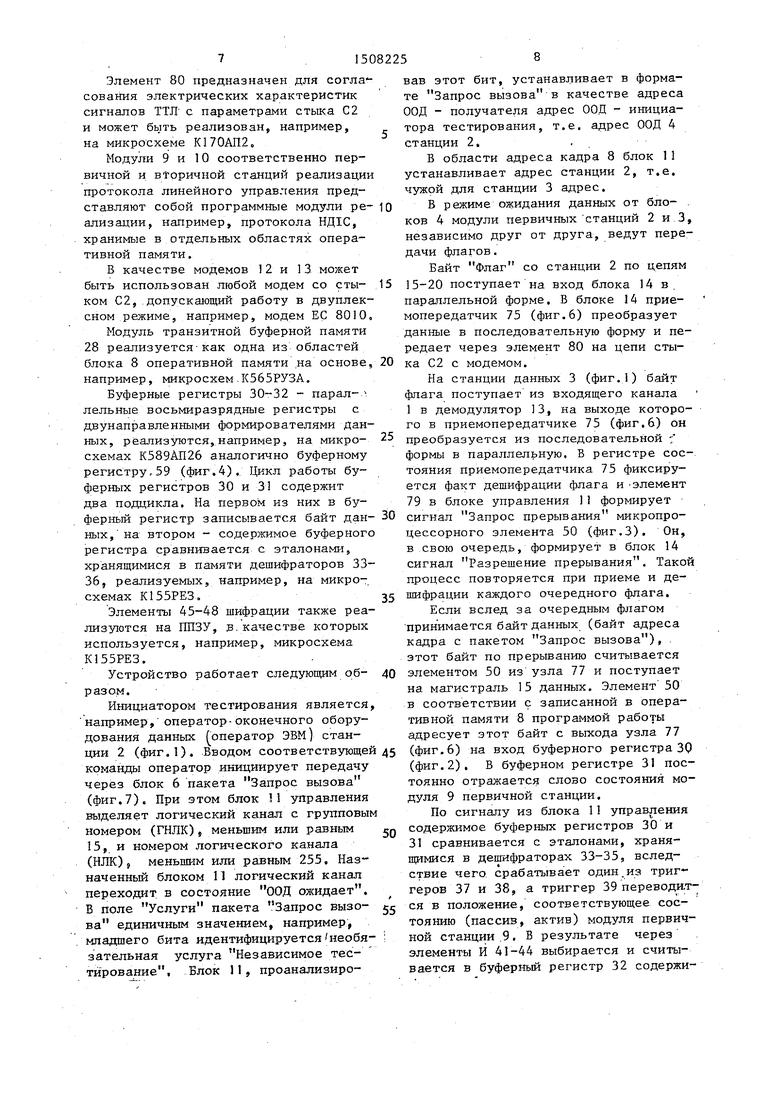

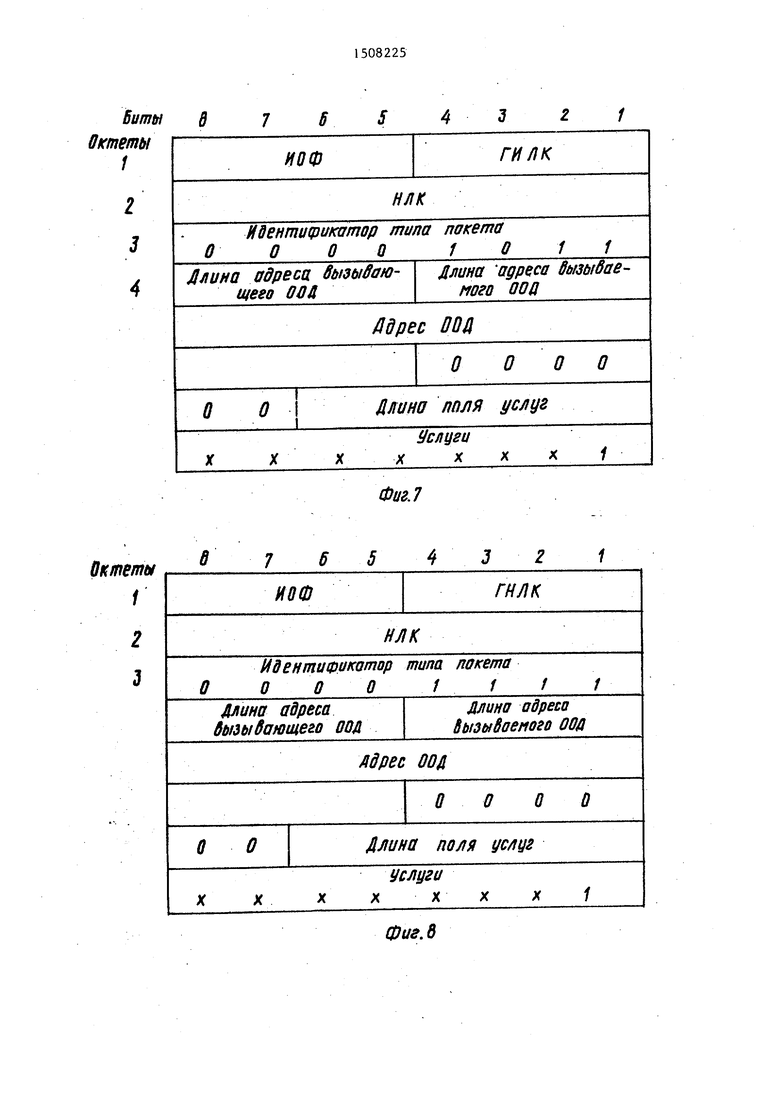

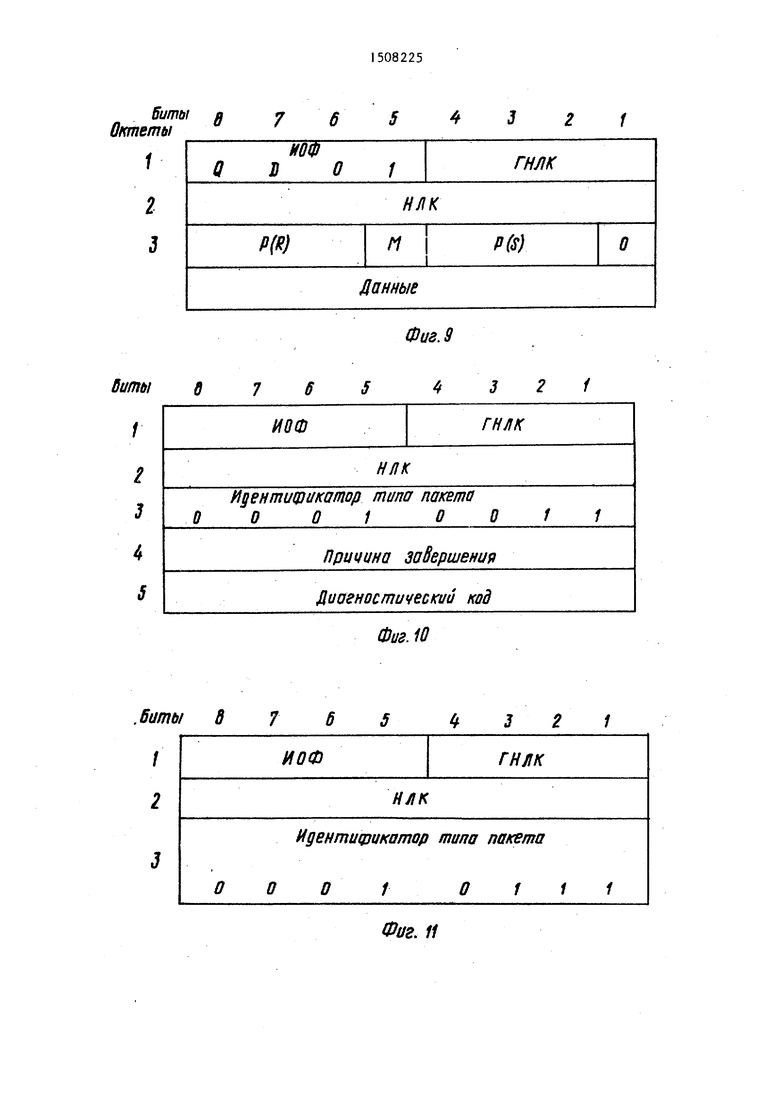

нения передачи пакетов независимого тестирования; на фиг.8 - формат пакетов Вызов принят, Соединение установлено для установления соединения передачи пакетов независимого тестирования; на фиг.9 - формат пакетов Данные ООД, Данные на фиг.. 10- формат пакетов Запрос завершения соединения ; на фиг. 11 - формат пакета Подтверждение завершения.

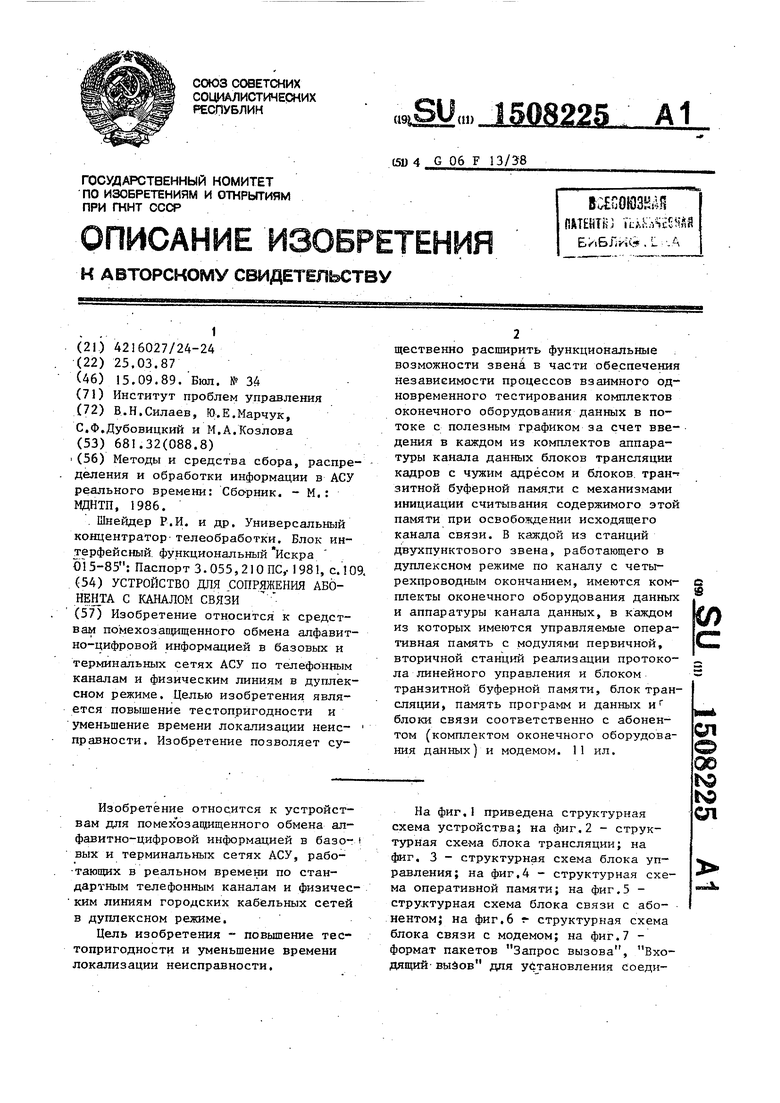

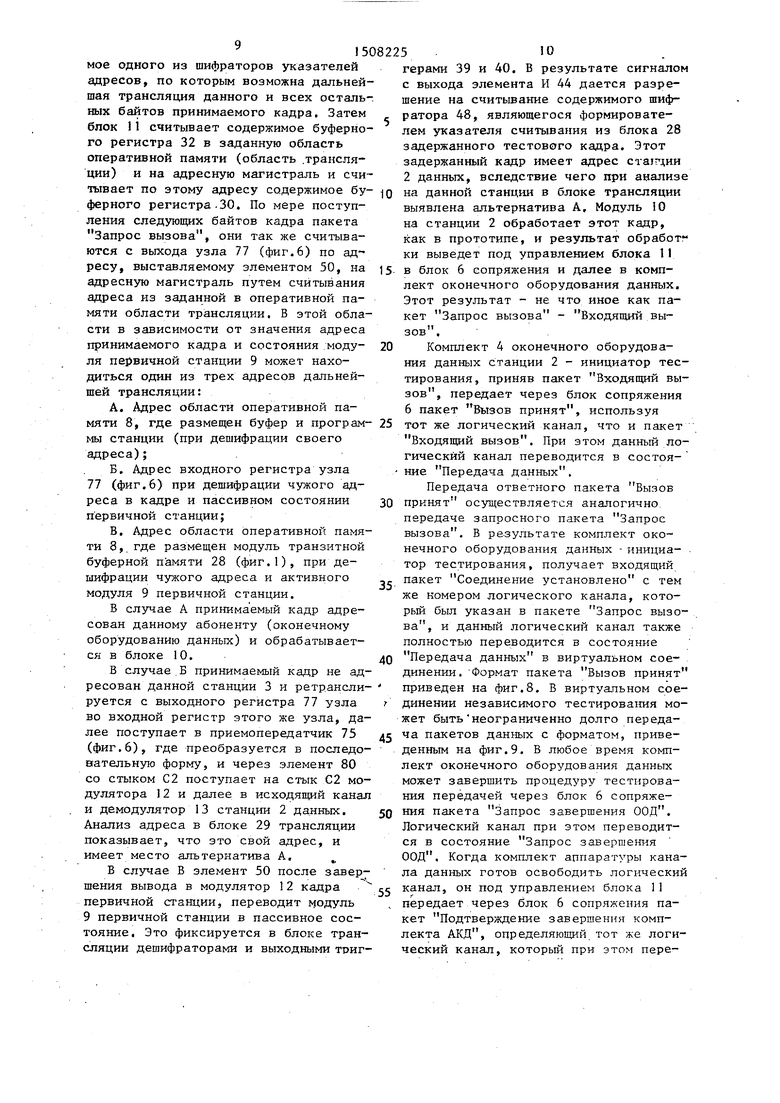

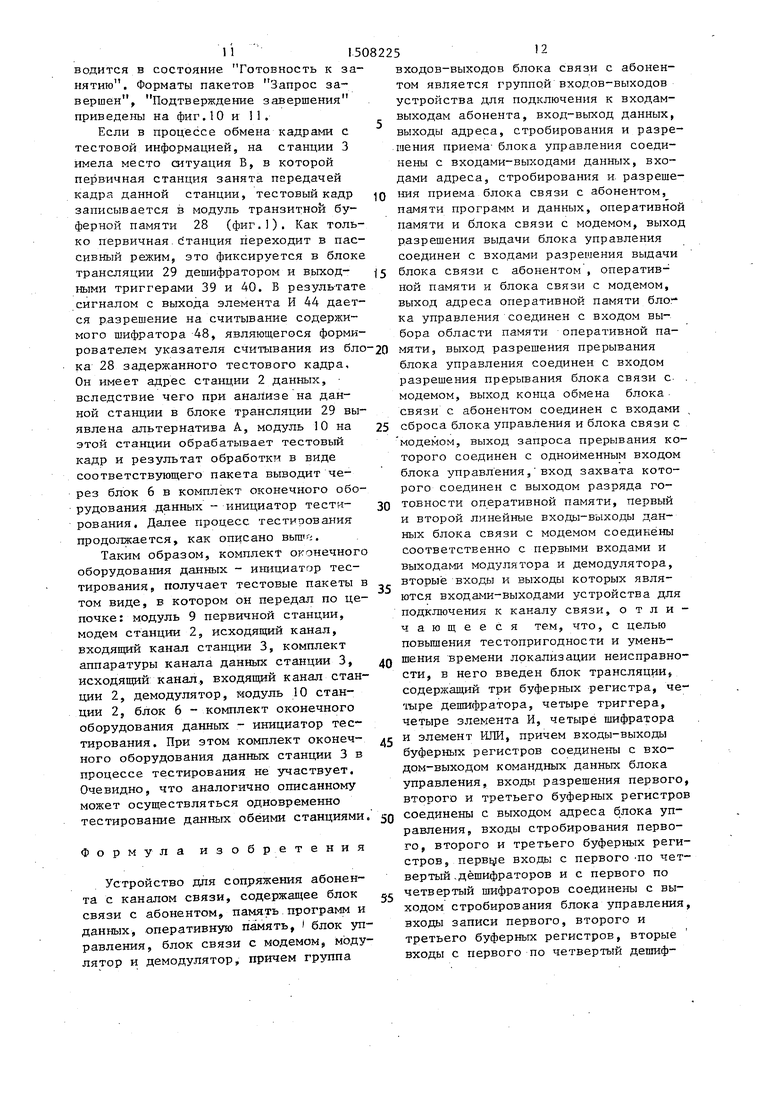

Устройство содержит канал 1 связи с четырехпройодным окончанием, две одинаковые станции данных 2 и 3 абонента, в каждой из которых содержится комплект 4 оконечного оборудования данных и комплект 5 аппаратуры канала данных. В комплекте аппаратуры данных

15 В блоке П управления м сорный элемент 50 реализов мер, на интегральной схем По входным связям 22-25 в равления поступают сигналы

ным связям 16-21 в блок I сигналы адреса, стробиров решения приема и вьщачи,. ративной памяти,, разрешени

25 ния, Кроме того, блок 11 у соединен с магистралью 15 указанные связи могут быть ны в. соответствии с интерф

30

35

имеются блок 6 связи с абонентом, память 7 программ и данных, оперативная 20 прерывания, сброс, захват память 8 с программными модулями 9 и 10 соответственно первичной и вторич- .ной станций реализации протокола линейного управления, блок 11 управления, модулятор 12, демодулятор 13 и блок 14 связи с модемом.

. Оперативная память 8, блоки 6 и 14 и блок 11 управления соединены между собой связями 15-25. Блоки 6 и 14 соединены с абонентом и модемом связями 26 и 27. В оперативную память 8 введен модуль транзитной буферной памяти 28, входы и выходы которого объединены с соответствующими входа - ми и выходами оперативной памяти. В комплект аппаратуры канала данных введен блок 29 трансляции.

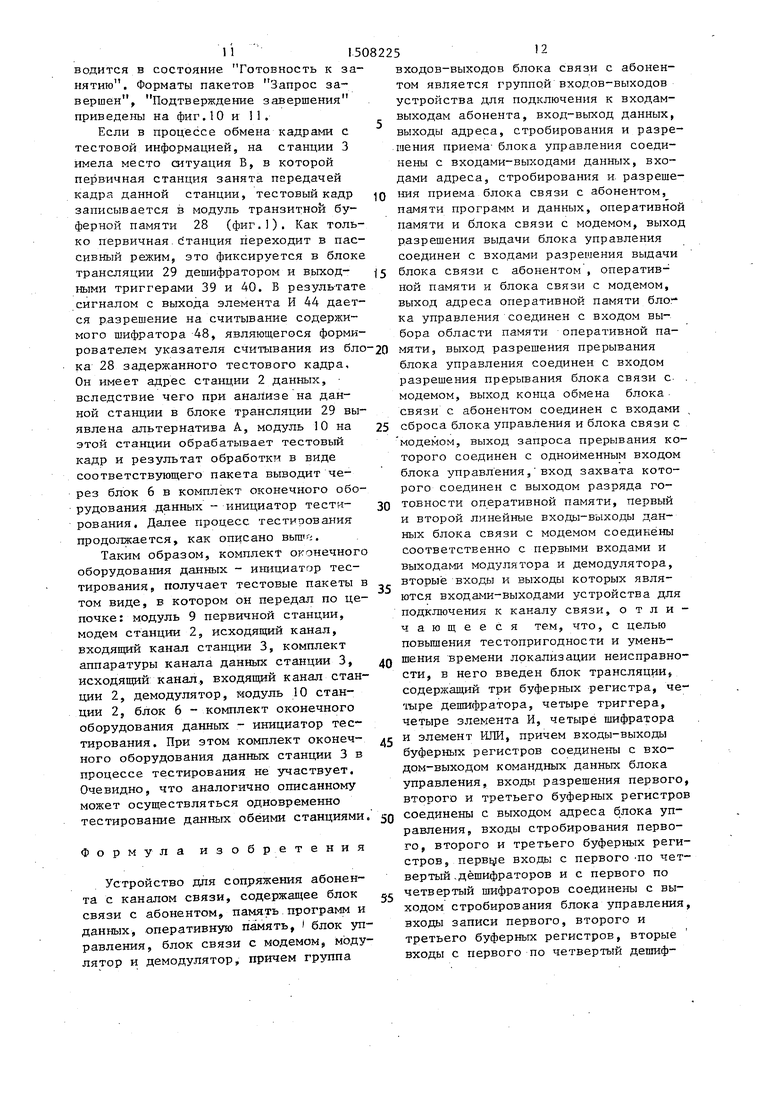

Блок 29 трансляции содержит три буферных регистра 30-32, четыре дешифратора 33-36, четыре триггера 37- 40, четыре элемента И 41-44, четыре шифратора 45-48 и элемент ИЛИ 49.

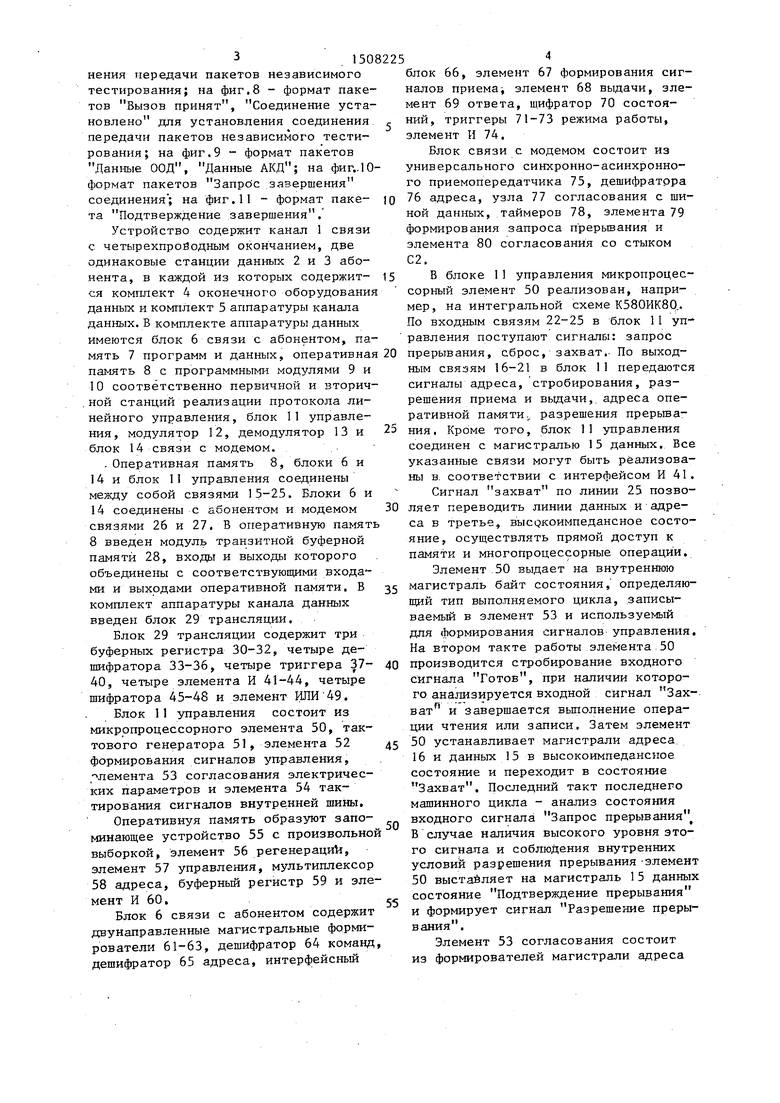

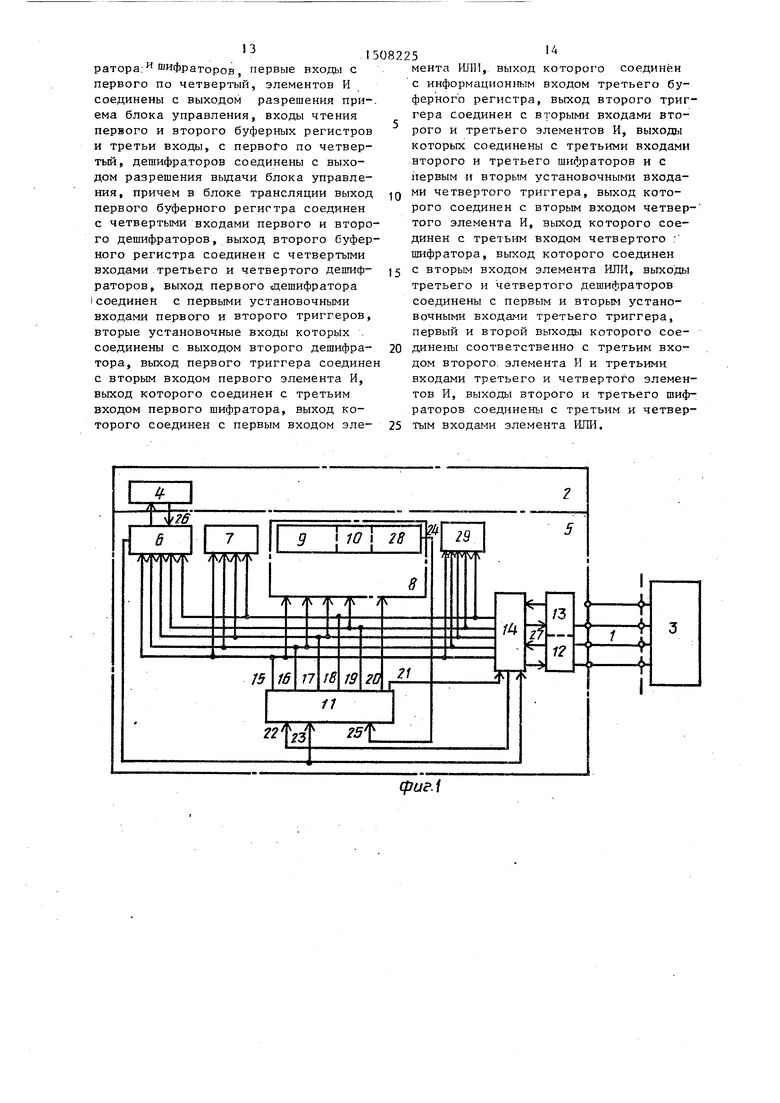

Блок 11 управления состоит из микропроцессорного элемента 50, тактового генератора 51, элемента 52 формирования сигнапов управления, .лемента 53 согласования электрических параметров и элемента 54 тактирования сигналов внутренней шины,

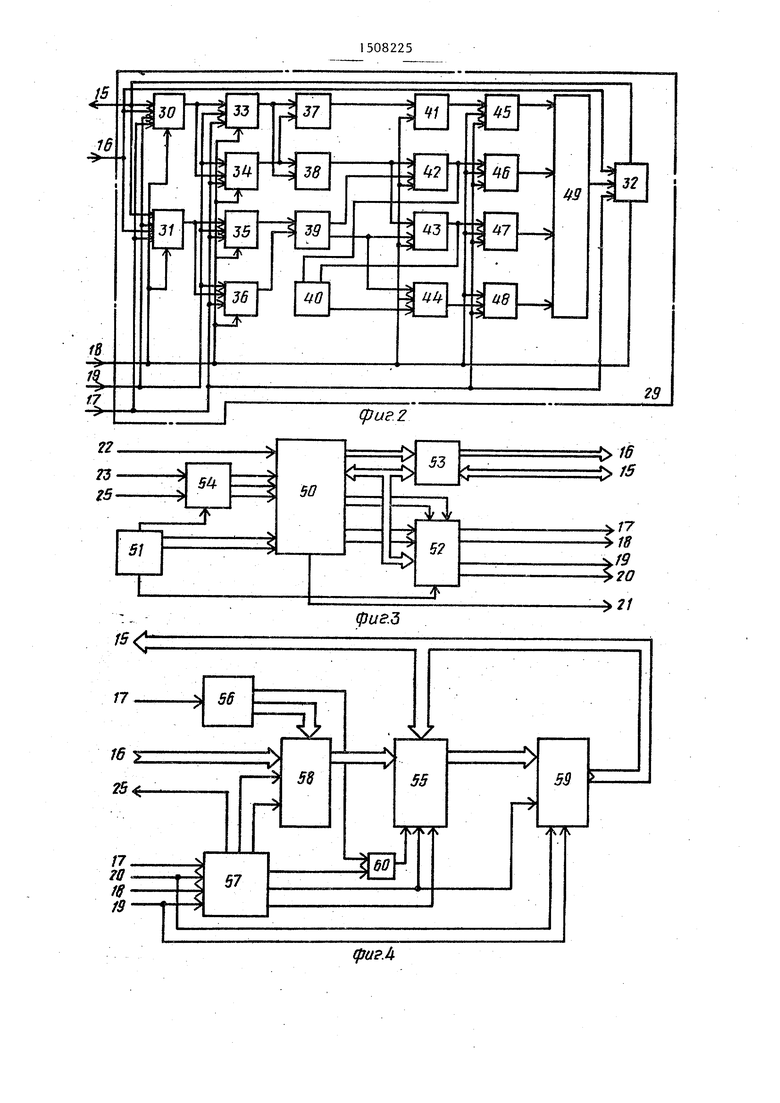

Оперативнуя память образуют запоминающее устройство 55 с произвольной выборкой, элемент 56 регенераций, элемент 57 управления, мультиплексор 58 адреса, буферньш регистр 59 и элемент И 60.

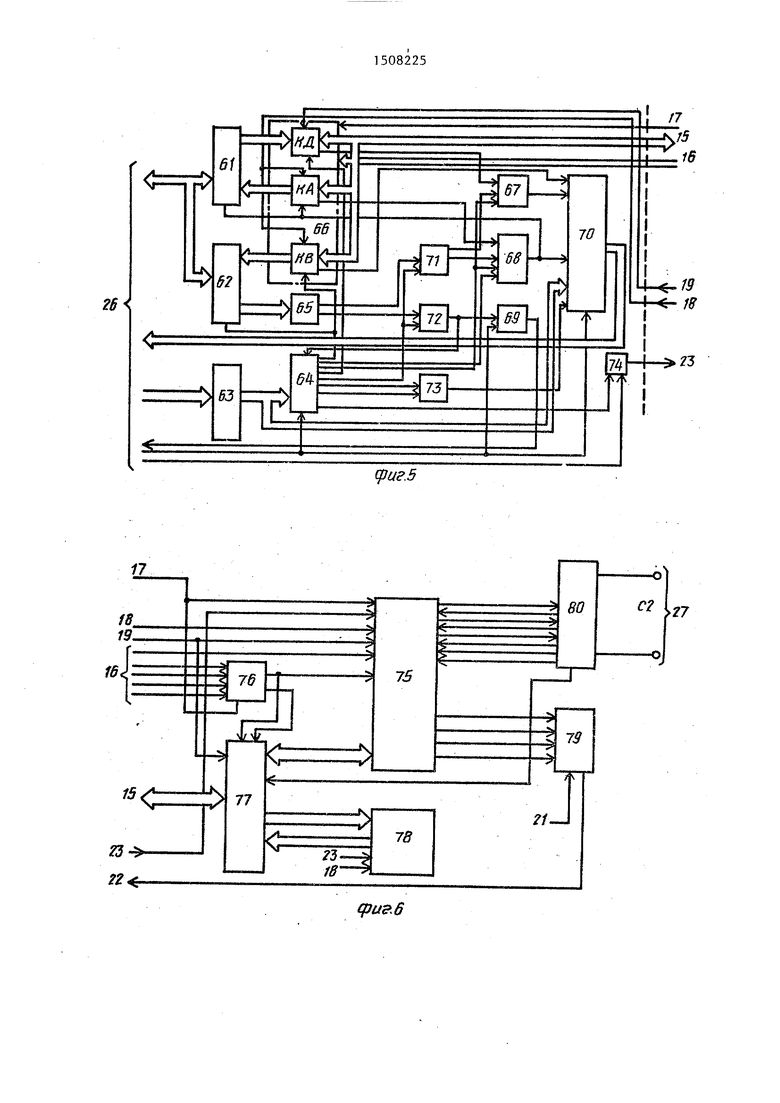

Блок 6 связи с абонентом содержит двунаправленные магистральные формирователи 61-63, дешифратор 64 команд, дешифратор 65 адреса, интерфейсный

40

45

50

55

Сигнал захват по лини ляет переводить линии данн са в третье высдкоимпедан яние, осуществлять прямой памяти и многопроцессорные

Элемент 50 выдает на вн магистраль байт состояния щий тип выполняемого цикл ваемый в элемент 53 и испо для формирования сигналов На втором такте работы эл производится стробировани сигнала Готов, при налич го анализируется входной с ват и завершается вьшолн ции чтения или записи. Зат 50 устанавливает магистрал 16 и данных 15 в высокоимп состояние и переходит в со Захват, Последний такт п машинного цикла - анализ с входного сигнала Запрос п В случае наличия высокого го сигнала и соблюдения вн условии разрешения прерыва 50 выстайляет на магистрал состояние Подтверждение п и формирует сигнал Разреш вания.

Элемент 53 согласования из формирователей магистра

8225

блок 66, элемент 67 формирования сигналов приемаi элемент 68 выдачи, элемент 69 ответа, шифратор 70 состояний, триггеры 71-73 режима работы, элемент И 74.

Блок связи с модемом состоит из универсального синхронно-асинхронного приемопередатчика 75, дешифратора

10 76 адреса, узла 77 согласования с шиной данных, таймеров 78, элемента 79 формирования запроса п рерьшания и элемента 80 согласования со стыком С2.

15 В блоке П управления микропроцессорный элемент 50 реализован, например, на интегральной схеме К580ИК80.. По входным связям 22-25 в блок 11 управления поступают сигналы: запрос

По выходным связям 16-21 в блок II передаются сигналы адреса, стробирования, разрешения приема и вьщачи,. адреса оперативной памяти,, разрешения прерьша25 ния, Кроме того, блок 11 управления соединен с магистралью 15 данных. Все указанные связи могут быть реализованы в. соответствии с интерфейсом И 41.

20 прерывания, сброс, захват

Сигнал захват по линии 25 позволяет переводить линии данных и адреса в третье высдкоимпедансное состояние, осуществлять прямой доступ к памяти и многопроцессорные операции.

Элемент 50 выдает на внутреннюю магистраль байт состояния, определяющий тип выполняемого цикла, записываемый в элемент 53 и используемый для формирования сигналов управления. На втором такте работы элемента 50 производится стробирование входного сигнала Готов, при наличии которого анализируется входной сигнал Захват и завершается вьшолнение операции чтения или записи. Затем элемент 50 устанавливает магистрали адреса 16 и данных 15 в высокоимпедансное состояние и переходит в состояние Захват, Последний такт последнего машинного цикла - анализ состояния входного сигнала Запрос прерывания В случае наличия высокого уровня этого сигнала и соблюдения внутренних условии разрешения прерывания элемент 50 выстайляет на магистраль 15 данных состояние Подтверждение прерывания и формирует сигнал Разрешение прерывания.

Элемент 53 согласования состоит из формирователей магистрали адреса

и двунаправленных формирователей магистрали данных. Формирователь адреса - это восьмиразрядный регистр, имеющий выходные схемы с тремя состояниями. Третье высокоимпедансное состояние имеет место при высоком уровне выходного сигнала Подтверждение захвата. При низком уровне этого сигнала формирователи.магистрали адреса повторяют уровни сигналов адресных линий элемента 50. Двунаправленные формирователи данных поддерживают выходы в третьем высоконмпеданс- ном состоянии при наличии высокого уровня выходного сигнала элемента 50 Подтверждение захвата и наличии - сигнала Прием или Выдача.

Элемент формирования сигналов упсопряженне магистрали 26 ввода- вывода комплекта 4 оконечного оборудования данных и внутренней шины блока 11. Магистральные формирователи

61-63 реализованы, например, на схемах К589АП26.

Дешифратор 64 команд может быть реализован на схеме KI55PE3.

Дешифратор 65 адреса выполнен аналогично дешифратору команд. Он обеспечивает сравнение передаваемого физического адреса с его значением в блоке 11 управления. При совпадении

срабатывает соответствующий триггер режима и обеспечивает функциональное подключение блока 11 управления к магистрали 26 ввода-вывода.

Интерфейсный блок 66 осуществляет

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИФИЦИРОВАННЫЙ МОДУЛЬ АВТОМАТИЧЕСКОЙ ТЕЛЕФОННОЙ СТАНЦИИ С ПРОЦЕССОРНЫМ УПРАВЛЕНИЕМ | 1992 |

|

RU2039411C1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| УСТРОЙСТВО ОПЕРАТИВНОЙ ТЕЛЕФОННОЙ СВЯЗИ | 2000 |

|

RU2197071C2 |

Изобретение относится к средствам помехозащищенного обмена алфавитно - цифровой информацией в базовых и терминальных сетях АСУ по телефонным каналам и физическим линиям в дуплексном режиме. Целью изобретения является повышение тестопригодности и уменьшение времени локализации неисправности. Изобретение позволяет существенно расширить функциональные возможности устройства в части обеспечения независимости процессов взаимного одновременного тестирования комплектов оконечного оборудования данных в потоке с полезным графиком за счет введения в каждом из комплектов аппаратуры канала данных блоков трансляции кадров с чужим адресом и блоков транзитной буферной памяти с механизмами инициации считывания содержимого этой памяти при освобождении исходящего канала связи. В каждой из станций устройства, работающего в дуплексном режиме по каналу с четырехпроводным окончанием, имеются комплекты оконечного оборудования данных и аппаратуры канала данных, в каждом из которых имеются управляемые оперативная память с модулями первичной, вторичной станций реализации протокола линейного управления и блоком транзитной буферной памяти, блок трансляции, память программ и данных и блоки связи соответственно с абонентом (комплектом оконечного оборудования данных) и модемом. 11 ил.

равления 52 формирует сигналы Прием,20 буферизацию байтов передаваемой и

Выдача, Подтверждение захвата, Стробирование и сигнал выбора области оперативной памяти Адрес оперативной памяти.

Элемент 54 тактирования входных сигналов обеспечивает их преобразование из асинхронных в синхронные.

Память 7 используется для хранения программ монитора. Это, например, запрограммированная микросхема К565РТ5.

Оперативная память 8 используется для хранения рабочей программы и мас сивов данных. В этом блоке (фиг,4) используются, например, запоминающие элементы на интегральных схемах К565РУЗА. .

Буферный регистр 59 обеспечивает энергетическое сопряжение выходных ших запоминающего устройства 55 с магистралью 15 данных.

Элемент 56 регенерации предназначен для регенерации запоминающего -устройства 55, формирует адреса строк, смена которых происходит циклически, по окончании цикла регенерации очередной строки, реализован, например, на схемах К155ТМ2, К155ИЕ2, К155ИЕ5.

Элемент 57 управления может быть реализован на схемах К155ТМ2, К155ЛИ1, К531ЛИ5, К155ЛАЗ.

Мультиплексор 58 адреса выставляет адрес строки и адрес столбца ячейки запоминающего устройства 55, к которой происходит обращение, или адрес ; регенерируемой строки устройства 55, , Блок сопряжения с абонентом обеспечивает энергетическое и логическое

принимаемой информации и хранение байтов уточненного состояния блока II управления, реализован, например, на схеме К580ИК55. Блок 66 программируется путем записи в него из элемента 50 (фиг.З) управляющего слова. Регистр управляющего слова блока 66 определяет функцию и направление работы каждого из каналов ввода-вывода

Элементы 67-69 реализованы соответственно на схемах ИЛИ-НЕ и триггере; ИЛИ-НЕ и двух триггерах; И-НЕ; И-НЕ и инверторе.

Шифратор состояния 70 выполнен на ППЗУ, в качестве которого может быть использована, например, схема К556РТ4. Шифратор 70 используется для энергетического сопряжения блока 11 с магистралью состояний комплекта 4 оконечного оборудования данных.

Приемопередатчик 75 может быть реализован на микросхеме К580ИК51.

Дешифратор 76 вырабатывает сигналы обращения к регистрам узла 77 в соответствии с адресом, выставленным на адресной магистрали. Может быть реализован, например, на двухвходо- вых элементах И и интегральных схе- мах К155ЛАЗ, К155ВД4.

Узел 77 предназначен для энергетического сопряжения с внутренней шиной и может быть реализован, нап- ример, на микросхеме К589АП16 и эле- ментах ИЛИ, И.

Таймер 78 представляет собой совокупность четырех одновибраторов, вы- рабатывакяцих импульсы различного периода для обеспечения тайм-аута.

7150

Элемент 80 предназначен для согла сования электрических характеристик сигналов ТТЛ с параметрами стыка С2 и может быть реализован, например, на микросхеме К170АП2.

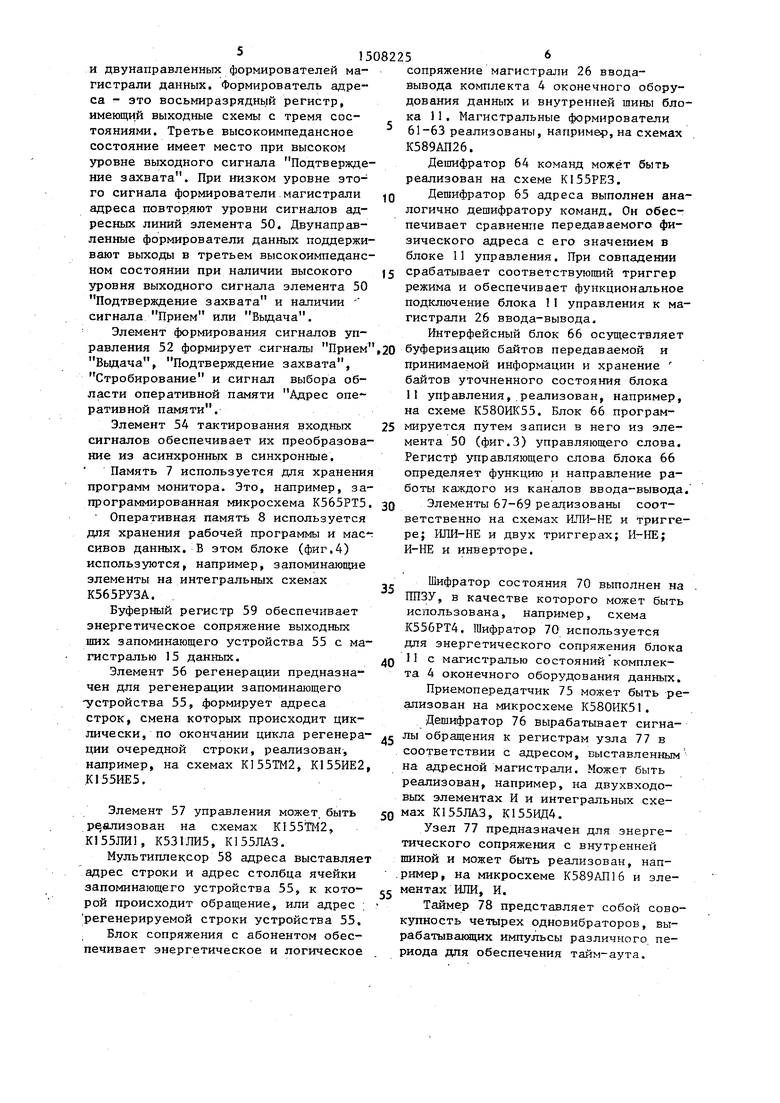

Модули 9 и 10 соответственно первичной и вторичной станций реализации протокола линейного управления представляют собой программные модули ре- ализации, например, протокола НД1С, хранимые в отдельных областях оперативной памяти,

В качестве модемов 12 и 13 может быть использован любой модем со сты- ком С2, допускающий работу в двуплек- сном режиме, например, модем ЕС 8010,

Модуль транзитной буферной памяти 28 реализуется-как одна из областей блока 8 оперативной памяти ,на основе, например, микросхем.К565РУЗА.

Буферные регистры 30-32 - парал- лельные восьмиразрядные регистры с двунаправленными формирователями данНа станции данных 3 (фиг.1) байт флага поступает из входящего канала 1 в демодулятор 13, на выходе которого в приемопередатчике 75 (фиг.6) Он преобразуется из последовательной ; формы в параллельную, Б регистре состояния приемопередатчика 75 фиксируется факт дешифрации флага и -элемент 79 в блоке управления 11 формирует

схемах K589AI126 аналогично буферному регистру,59 (фиг.4). Цикл работы буферных регистров 30 и 31 содержит два подцикла. На первом из них в буферный регистр записывается байт дан- 30 сигнал Запрос прерывания микропроцессорного элемента 50 (фиг.З). Он, в свою очередь, формирует в блок 14 сигнал Разрешение прерывания. Такой пр-оцесс повторяется при приеме и де35

ных, на втором - содержимое буферного регистра сравнивается с эталонами, хранящимися в памяти дешифраторов 33- 36, реализуемых, например, на микро- схемах К155РЕЗ.

Элементы 45-48 шифрации также реализуются на ППЗУ, в.качестве которых используется, например, микросхема К155РЕЗ.

Устройство работает следующим об- 40 разом.

Инициатором тестирования является, например, оператор-оконечного оборудования данных Гоператор ЭВМ) станции 2 (фиг.1). Вводом соответствующей 45 команды оператор инициирует передачу через блок 6 пакета Запрос вызова (фиг.7). При этом блок П управления выделяет логический канал с групповым

шифрации каждого очередного флага.

Если вслед за очередным флагом принимается байт данных (байт адреса кадра с пакетом Запрос вызова), . этот байт по прерыванию считывается элементом 50 из узла 77 и поступает на магистраль 15 данных. Элемент 50 в соответствии с записанной в оперативной памяти 8 программой работы адресует этот байт с выхода узла 77 (фиг.6) на вход буферного регистра 30 (фиг.2). В буферном регистре 31 постоянно отражается слово состояния модуля 9 первичной станции.

По сигналу из блока 11 управления содержимое буферных регистров 30 и 31 сравнивается с эталонами, храня- ш 1мися в дешифраторах 33-35, вследствие чего срабатывает один.из триг- геров 37 и 38, а триггер 39 переводится в положение, соответствующее состоянию (пассив, актив) модуля первичной станции.9. В результате через элементы И 41-44 выбирается и считывается в буферный регистр 32 содержиномером (ГНЛК), меньшим или равным 15, и номером логического канала (НЛК), меныиим или равным 255, Наз- наченньш блоком 11 логический канал переходит, в состояние ООД ожидает.

В поле Услуги

ва единичным значением, например, младшего бита идентифицируется необязательная услуга тйрование,

пакета Запрос вызо-

Независимое тес- Блок 11, проанализиро

5

0

5

вав этот бит, устанавливает в формате Запрос вызова в качестве адреса ООД - получателя адрес ООД - инициатора тестирования, т.е. адрес ООД 4 станции 2..

В области адреса кадра 8 блок 11 устанавливает адрес станции 2, т.е. чужой для станции 3 адрес.

В режиме ожидания данных от бло- . ков 4 модули первичных станций 2 и 3, независимо друг от друга, ведут передачи флагов.

Байт Флаг со станции 2 по цепям 15-20 поступает на вход блока 14 в. параллельной форме. В блоке 14 приемопередатчик 75 (фиг.6) преобразует данные в последовательную форму и передает через элемент 80 на цепи стыка С2 с модемом.

На станции данных 3 (фиг.1) байт флага поступает из входящего канала 1 в демодулятор 13, на выходе которого в приемопередатчике 75 (фиг.6) Он преобразуется из последовательной ; формы в параллельную, Б регистре состояния приемопередатчика 75 фиксируется факт дешифрации флага и -элемент 79 в блоке управления 11 формирует

0 сигнал Запрос прерывания микропроцессорного элемента 50 (фиг.З). Он, в свою очередь, формирует в блок 14 сигнал Разрешение прерывания. Такой пр-оцесс повторяется при приеме и де5

0

5

0

5

шифрации каждого очередного флага.

Если вслед за очередным флагом принимается байт данных (байт адреса кадра с пакетом Запрос вызова), . этот байт по прерыванию считывается элементом 50 из узла 77 и поступает на магистраль 15 данных. Элемент 50 в соответствии с записанной в оперативной памяти 8 программой работы адресует этот байт с выхода узла 77 (фиг.6) на вход буферного регистра 30 (фиг.2). В буферном регистре 31 постоянно отражается слово состояния модуля 9 первичной станции.

По сигналу из блока 11 управления содержимое буферных регистров 30 и 31 сравнивается с эталонами, храня- ш 1мися в дешифраторах 33-35, вследствие чего срабатывает один.из триг- геров 37 и 38, а триггер 39 переводится в положение, соответствующее состоянию (пассив, актив) модуля первичной станции.9. В результате через элементы И 41-44 выбирается и считывается в буферный регистр 32 содержимое одного из шифраторов указателей адресов, по которым возможна дальнейшая трансляция данного и всех остальных байтов принимаемого кадра. Затем блок 11 считывает содержимое буферного регистра 32 в заданную область оперативной памяти (область .трансляции) и на адресную магистраль и считывает по этому адресу содержимое бу- д на данной станции в блоке трансляции ферного регистра.30. По мере поступления следующих байтов кадра пакета Запрос вызова, они так же считываются с выхода узла 77 (фиг.6) по адресу, выставляемому элементом 50, на адресную магистраль путем считывания адреса из заданной в оперативной памяти области трансляции. В этой области в зависимости от значения адреса принимаемого кадра и состояния модуля первичной станции 9 может находиться один из трех адресов дальнейшей трансляции:

А. Адрес области оперативной павыявлена альтернатива А, Модуль 10 на станции 2 обработает этот кадр, как в прототипе, и результат обработг ки выведет под управлением блока 11

15 в блок 6 сопряжения и далее в комплект оконечного оборудования данных. Этот результат - не что иное как пакет Запрос вызова - Входящий вызов.

20 Комплект 4 оконечного оборудования данных станции 2 - инициатор тестирования, приняв пакет Входящий вызов, передает через блок сопряжения 6 пакет Вызов принят, используя

30

35

40

мяти 8, где размещен буфер и програм- 25 тот же логический канал, что и пакет мы станции (при дешифрации своего адреса);

Б, Адрес входного регистра узла 77 (фиг.6) при дешифрации чужого адреса в кадре и пассивном состоянии первичной станции;

В. Адрес области оперативной памяти 8, где размещен модуль транзитной буферной памяти 28 (фиг.1), при дешифрации чужого адреса и активного модуля 9 первичной станции.

В случае А принимаемый кадр адресован данному абоненту (оконечному оборудованию данных) и обрабатывается в блоке 10.

В случае.Б принимаемый кадр не адресован данной станции 3 и ретранслируется с выходного регистра 77 узла во входной регистр этого же узла, далее поступает в приемопередатчик 75 (фиг.6), где преобразуется в последовательную форму, и через элемент 80 со стыком С2 поступает на стык С2 модулятора 12 и далее в исходящий канал и демодулятор 13 станции 2 данных. Анализ адреса в блоке 29 трансляции показывает, что это свой адрес, и имеет место альтернатива А.

В случае В элемент 50 после завершения вывода в модулятор 12 кадра первичной станции, переводит модуль 9 первичной станции в пассивное состояние. Это фиксируется в блоке трансляции дешифраторами и выходными триг Входяш 1й вызов. При этом данньш логический канал переводится в состоя- ние Передача данных,

Передача ответного пакета Вызов принят осуществляется аналогично, передаче запросного пакета Запрос вызова. В результате комплект оконечного оборудования данных - ннициа- тор тестирования, получает входящий пакет Соединение установлено с тем же номером логического канала, который был указан в пакете Запрос вызо ва, и данный логический канал также полностью переводится в состояние Передача данных в виртуальном соединении. Формат пакета Вызов принят

приведен на фиг.8. В виртуальном сое- динении независимого тестирования может быть неограниченно долго передад5 ча пакетов данных с форматом, приведенным на фиг.9. В любое время комплект оконечного оборудования данных может завершить процедуру тестирования передачей через блок 6 сопряжения пакета Запрос завершения ООД. Логический канал при этом переводится в состояние Запрос завершения ООД. Когда комплект аппаратуры канала данных готов освободить логический канал, он под управлением блока 11 передает через блок 6 сопряжения пакет Подтверждение завершения комплекта АКД, определяющий тот же логический канал, который при этом пере50

55

герами 39 и 40. В результате сигналом с выхода элемента И 44 дается разрешение на считывание содержимого шифратора 48, являющегося формирователем указателя считывания из блока 28 задержанного тестового кадра. Этот задержанный кадр имеет адрес стаггдии 2 данных, вследствие чего при анализе

на данной станции в блоке трансляции

выявлена альтернатива А, Модуль 10 на станции 2 обработает этот кадр, как в прототипе, и результат обработг ки выведет под управлением блока 11

в блок 6 сопряжения и далее в комплект оконечного оборудования данных. Этот результат - не что иное как пакет Запрос вызова - Входящий вызов.

Комплект 4 оконечного оборудования данных станции 2 - инициатор тестирования, приняв пакет Входящий вызов, передает через блок сопряжения 6 пакет Вызов принят, используя

тот же логический канал, что и пакет

Входяш 1й вызов. При этом данньш логический канал переводится в состоя- ние Передача данных,

Передача ответного пакета Вызов принят осуществляется аналогично, передаче запросного пакета Запрос вызова. В результате комплект оконечного оборудования данных - ннициа- - тор тестирования, получает входящий пакет Соединение установлено с тем же номером логического канала, который был указан в пакете Запрос вызо ва, и данный логический канал также полностью переводится в состояние Передача данных в виртуальном соединении. Формат пакета Вызов принят

приведен на фиг.8. В виртуальном сое- динении независимого тестирования может быть неограниченно долго передача пакетов данных с форматом, приведенным на фиг.9. В любое время комплект оконечного оборудования данных может завершить процедуру тестирования передачей через блок 6 сопряжения пакета Запрос завершения ООД. Логический канал при этом переводится в состояние Запрос завершения ООД. Когда комплект аппаратуры канала данных готов освободить логический канал, он под управлением блока 11 передает через блок 6 сопряжения пакет Подтверждение завершения комплекта АКД, определяющий тот же логический канал, который при этом пере

водится в состояние Готовность к занятию. Форматы пакетов Запрос завершен, Подтверждение завершения приведены на фиг.10 и 11.

Если в процессе обмена кадрами с тестовой информацией, на станции 3 имела место ситуация В, в которой первичная станция занята передачей кадра данной станции, тестовый кадр записывается в модуль транзитной буферной памяти 28 (фиг.1). Как только первичная.Станция переходит в пассивный режим, это фиксируется в блоке трансляции 29 дешифратором и выход- ными триггерами 39 и 40, В результате сигналом с выхода элемента И 44 дается разрешение на считывание содержимого шифратора 48, являющегося формирователем указателя считывания из бло ка 28 задержанного тестового кадра, Он имеет адрес станции 2 данных, вследствие чего при анализе на данной станции в блоке трансляции 29 выявлена альтернатива А, модуль 10 на этой станции обрабатывает тестовый кадр и результат обработки в виде соответствующего пакета выводит через блок 6 в комплект оконечного оборудования .данных - инициатор тести- рования. Далее процесс тестирования продолжается, как описано вьш ;.

Таким образом, комплект оконечного оборудования данных - инициатор тестирования, получает тестовые пакеты в том виде, в котором он передал по цепочке: модуль 9 первичной станции, модем станции 2, исходящий канал, входящий канал станции 3, комплект аппаратуры канала данных станции 3, исходящий канал, входящий канал станции 2, демодулятор, модуль 10 станции 2, блок 6 - комплект оконечного оборудования данных - инициатор тестирования. При этом комплект оконеч- ного оборудования данных станции 3 в процессе тестирования не участвует. Очевидно, что аналогично описанному может осуществляться одновременно тестирование данных обеими станциями

Формула изобретения

Устройство для сопряжения абонента с каналом связи, содержащее блок связи с абонентом, память программ и данных, оперативную память, блок управления, блок связи с модемом, модулятор и демодулятор, причем группа

входов-выходов блока связи с абонентом является группой входов-выходов устройства для подключения к входам- выходам абонента, вход-выход данных, выходы адреса, стробирования и разрешения приема- блока управления соединены с входами-выходами данных, входами адреса, стробирования и. разрешения приема блока связи с абонентом, памяти программ и данных, оперативной памяти и блока связи с модемом, выход разрешения выдачи блока управления соединен с входами разрешения выдачи блока связи с абонентом , оперативной памяти и блока связи с модемом, выход адреса оперативной памяти блока управления соединен с входом выбора области памяти оперативной памяти, выход разрешения прерывания блока управления соединен с входом разрешения прерывания блока связи с. модемом, выход конца обмена блока - связи с абонентом соединен с входами сброса блока управления и блока связи с модемом, выход запроса прерывания которого соединен с одноименным входом блока управления, вход захвата которого соединен с выходом разряда готовности оперативной памяти, первый и второй линейные входы-выходы данных блока связи с модемом соединены соответственно с первыми входами и выходами модулятора и демодулятора, вторые входы и выходы которых являются входами-выходами устройства для подключения к каналу связи, отличающееся тем, что, с целью повышения тестопригодности и уменьшения времени локализации неисправности, в него введен блок трансляции} содержащий три буферных регистра, че- ibipe дешифратора, четыре триггера, четыре элемента И, четыре шифратора и элемент ИЛИ, причем входы-выходы буферных регистров соединены с входом-выходом командных данных блока управления, входы разрешения первого, второго и третьего буферных регистров соединены с выходом адреса блока управления, входы стробирования первого, второго и третьего буферных регистров , первое входы с первого ПО четвертый .дешифраторов и с первого по четвертый шифраторов соединены с выходом стробирования блока управления, входы записи первого, второго и третьего буферных регистров, вторые входы с первого по четвертый дешиф13

ратора: шифраторов , первые входы с первого по четвертый, элементов И соединены с выходом разрешения при-. ема блока управления, входы чтения первого и второго буферных регистров и третьи входы, с первого по четвертый, дешифраторов соединены с выходом разрешения выдачи блока управления, причем в блоке трансляции выход первого буферного регистра соединен с четвертыми входами первого и второго дешифраторов, выход второго буферного регистра соединен с четвертыми входами третьего и четвертого дешифраторов, выход первого «дешифратора I соединен с первыми установочными входами первого и второго триггеров, вторые установочные входы которых . соединены с выходом второго дешифратора, выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с третьим входом первого шифратора, выход которого соединен с первым входом элеГ П

V W W Г j

В 1о I --- --j - -- I

/V /rvv 7 7

16

Л

J8 11

19

22

Щ

. н08225

14

10

15

20

25

мента Ш1И, выход которого соединён с информационным входом третьего буферного регистра, выход второго триггера соединен с вторыми входами второго и третьего элементов И, выходы которых соединены с третьими входами второго и третьего шифраторов и с первым и вторым установочными входами четвертого триггера, выход которого соединен с вторым входом четвер- того элемента И, выход которого соединен с третьим входом четвертого : шифратора, вьгход которого соединен с вторым входом элемента ИЛИ, выхода третьего и четвертого дешифраторов соединены с первым и вторым установочными входами третьего триггера, первый и второй выходы которого соединены соответственно с третьим входом второго, элемента И и третьими, входами третьего и четвертого элементов И, выходы второго и третьего шифраторов соединены с третьим и четвертым входами элемента ИЛИ.

29

Ш

/3

20

21

12

CfJUf.l

фие.

(ригЛ

сриг,6

биты д

Октеты

1

Фае. 7

фиг. в

биты а Октеты

ffi/m д

биты 8

Фиг. 9

Фиг. 10

Авторы

Даты

1989-09-15—Публикация

1987-03-25—Подача