1

Изобретение относится к вьгчислительной технике и может быть применено для обмена информацией между процессором и каналами пёрбдачи дйс- кретной информации в узлах коммутации сообщений, или центрах обработки данных автоматизированных систем управления.

Известны устройства 1 сопряже- tn НИН процессоров с каналами связи, содержащие блок чтения-записи, блок микропрограммного управления, регистры, счетчики, дешифраторы, блок контроля и блок управления, осуществляющие сопряжение между процессором и группой каналов передачи дискретной информации.

Недостаток этих устройств заключается в их низкой пропускной спо- 20 собности.

Наиболее близким к предложенному техническим решением является устройство t23 сопряжения процессора обмена с каналами связи, содержа- 25 щёе блок управления, блоки связи с каналом, блок обмена служебными сигналами, шифратор адреса абонента, блок формирования адреса ОЗУ , счетчик данных, дешифратор, блок управле-зо

ния счетным входом, блок управления поразрядным обменом, счетчик адреса,, регистр данных, коммутатор, регистр служебных признаков, блок обмена байтами, причем блок управления соединен с входом первого блока связи с каналом, со всеми блоками связи с каналами через магистраль, с выходом п-го блока связи с каналом и с коммутатором, шифратор адреса абонента соединен с блокг1ми связи с каналами и блоком формирования адреса ОЗУ; колилутатор подключен к регистру дайных, регистру служебных признаков и счетчику адреса, который соединен с блоком формирования адреса ОЗУ и . блоком управления; информационные выходы блоков связи с каналами соединены с информационной магистралью, дешифратор нуля - с блоком управления.

Недостатком известного устройства является низкая пропускная способность, так как оно не обеспечивает синхронизацию по кодовым последовательностям путем поиска комбинаций фазирования в принимаемой информации, что значительно усложняет програкадную обработку информацирнных массивовj не обеспечивает контроль за выполнением операций, что может привести к посылке информации не по нужному каналу или к искажению информации, хранящейся в оперативном запоминающем устройстве и прошедшей проверку программными методами контроля.

Цель изобретения - повышение пропускной способности устройства.

.Поставленная цель достигается Тем, что в устройство, содержащее М блоков связи с каналом, группы входов-выходов которых являются соответствующими группами входов-выходов синхронизации устройства, шифратор кода канала, соединенный выходом с первым входом блока формирования адреса памяти, входом-выходом с адресным входом-выходом устройства, а вторым входом - с первым выходом счетчика адреса, соединенного двусторонней связью с коммутатором магистрали, дешифратор нуля, выходом подключенный к первому входу блока управления, первый выход и второй вход кЪторого соединны соответственно со входом счетчика адреса и первым выходом регистра служебных признаков, соединенного двусторонней связью с коммутатором магистрали, вход-выход которого является информационным входом-выходом устройства, а первый и второй входы соединены соответственно с певым Еыходом регистра данных и вторы выходом блока управления, вход-выход которого является управляющим входом-выходом устройства, причем первый выход i-го блока связи с каналом подключен к первому входу ( i+ 1)-го блока связи с каналом ( 1 1, М-Т), выход М-го и вход первого блоков связи с каналом соединены соответственно с третьими входом и выходом блока управления, четвертые вход и выход которого соответственно подключены ко вторым выходам и входам блоков связи с каналом, третьи выходы которых соединены с соответствующими входами шифратора кода канала, согласно изобретению, введены шифратор контрольного кода, дешифратор переполнения счетчиков, дешифратор состояния регистра данных, две схемы сравнения, буферный Р5 гистр, дешифратор типа байта и коммутатор требований. При этом четвертые выходы блоков связи с канало 1|одключены к соответствующим входам шифратора контрольного кода, третьи входы - ко второму выходу регистра служебных признаков, в четвертые входы - ко второму выходу регистра данных. Третий выход регистра данньрс через дешифратор состояния регистра данных подключен к пятому входу блока управления, первый вход к пятому выходу блока управления.

четвертый выход - к третьему входу блока формирования адреса памяти, а пятый выход и второй вход - соответ-. ственно к первому входу первой схемы сравнения и выходу коммутатора магистралиi Второй вход первой схемы сравнения подключен к первому выходу коммутатора магистрали, первый выход и третий вход - соответственно к шестому и четвертому входам блока управления, а четвертый вход к первому входу буферного регистра и выходу дешифратора типа байта, входом соединенного с третьим выходом регистра служебных признаков. Вход и четвертый выход регистра служебных признаков соединены соответственно со вторым выходом первой схемы сравнения и первьом входом второй схемы сравнения, второй вход и выход которой соединены соответственно с выходом шифратора контрольного кода и седьмым входом блока управления, шее-, той и седьмой выходы которого соеди- нены соответственно со вторым входом буферного регистра и первым входом коммутатора -требований, выходы которых подключены к первому входу коммутатора магистрали. Второй вход коммутатора требований соединен с выходом шифратора кода канала, вход и первый выход счетчика длины массива, соединенного двусторонней связью с коммутатором/магистрали, подключены соответртвенно к первому и второму входам дешифратора переполнения счетчиков, третьим входом соединенного со вторым выходом счетчика адреса, а первым входом и выходом - соответст.венно с первым выходом и восьмым входом блока управления. Восьмой выход блока управления подключен к четвертому входу блока формирования адреса памяти, пятым входом соединенного с пятым выходом.регистра служебных признаков, второй выход счетчика длины массива подключен ко входу дешифратора нуля.

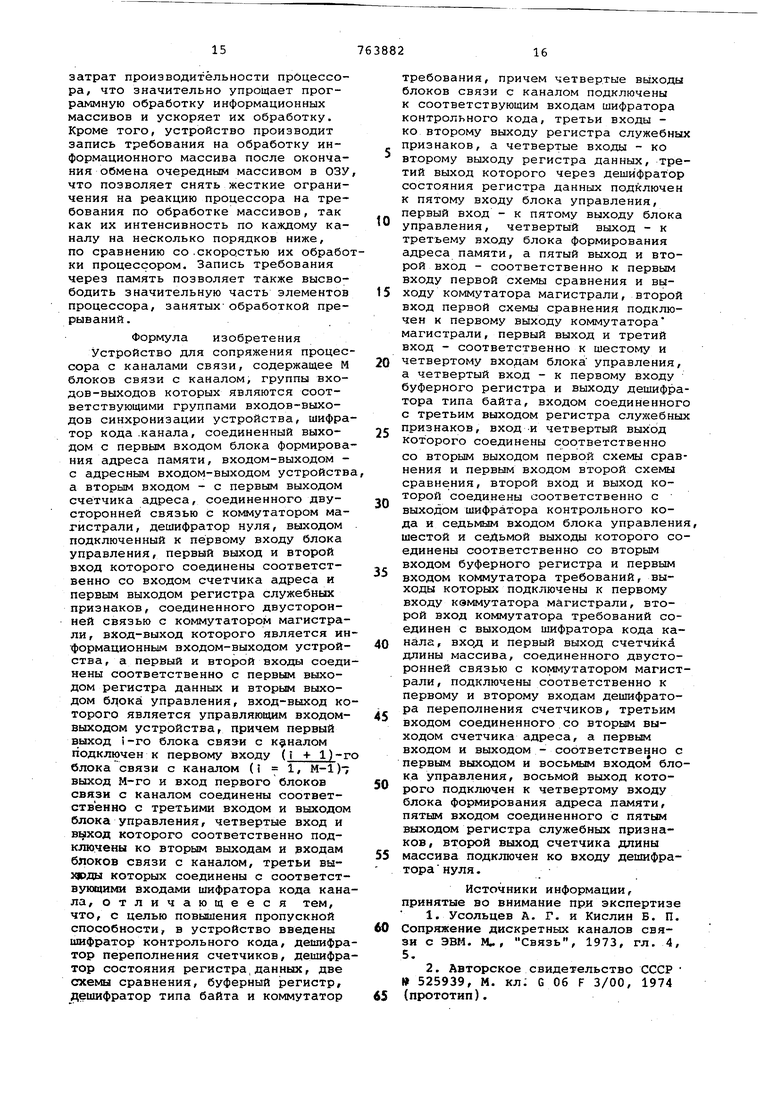

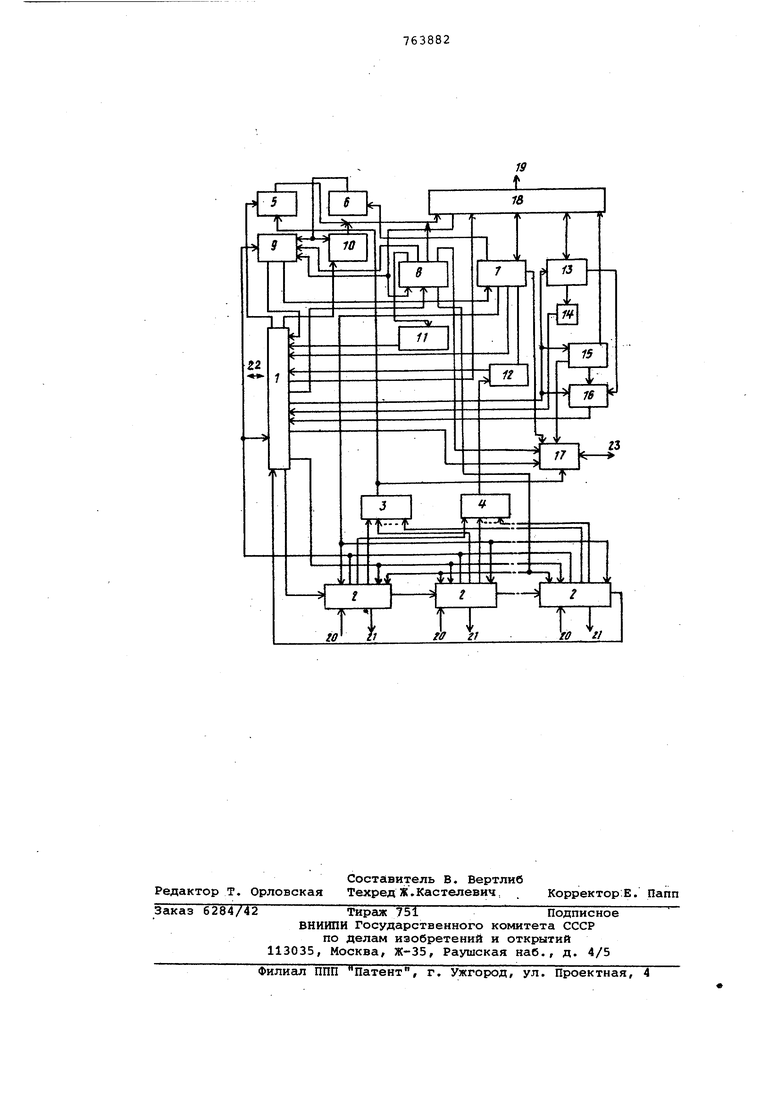

На чертеже представлена ст|эуктурная схема устройства, содержащего блок 1 управления, блоки 2 связи с каналами, шифратор 3 кода канала, шифратор 4 контрольного кода, коммутатор 5 требований, дешифратор б типа байта, регистр 7 служебных признаков, регистр 8 данных, первую схему сравнения 9, буферный регистр 10, дешифратор 11 состояния регистра данных,, вторую схему сравнения 12, счетчик 13 длины массива, дешифратор 14 нуля, счетчик 15 адреса памяти, дешифратор 16 переполнения счетчиков, блок 17 формирования адреса, коммутатор 18 магистрали, информационный вход-выход 19 устройства, входы 20 и выходы 21 синхронизации устройства, управляющий вход-выход 22 устройства и адресный вход-выход 23 устройства.

Блоки 2 связи с каналами осуществляют выборку заявок, каналов по приоритету, закре11ленному за блоком в зависимости от его порядкового номера, и обеспечивают обмен информацией и служебными признаками с аппаратурой преобразования сигналов дискретного канала связи; шифратор 3 кода канала формирует двоичный код выбранного канала, шифратор 4 контрольного кода формирует контрольный код адреса выбранного канала; коммутатор 5 требований предназначен для занесения в ОЗУ кода канала, по которому закончен обмен информационным массивом; шифратор

6типа байта предназначен для расшифровки содержимого одного из полей регистра 7 служебных признаков, определяющего формат информации, которой производится обмен; регистр

7служебных признаков содержит управляющую информацию, необходимую для управления обменом по каналу связи; направление обмена, формат информации, ключ зоны памяти, этап обработки , приоритет обработки информацией ного массива процессором; регистр 8 данных предназначен для поразрядного накопления (выдачи) байта информации из (в) канала связи и для организаци очереди требований .на обработку информационных массивов процессором. Число битов, накапливаемых в регистре 8, определяется типом байта (элементной структурой байта), который принят в обмене. В соответствии со стандартом элементная структура байт может быть 8-5 разрядов. Заполнение регистра 8 информацией принимаемой

из канала, производится начиная с одного из четырех младших разрядов регистра в зависимости от элементной структуры следующим образом: с 0-го для 8-элементного байта, с 1-го для 7-элементного байта/ со 2-го для 6-элементного байта и с 3-го для 5-элементного байта. Буферный регист

10 предназначен для добавления в содержимое регистра 8 информации, принимаемой из канала связи, или добавления константы, управляющей формированием байта, из принимаемой информационной последовательности или управляющей побитной выдачей байта в канал связи из устройства; дешифратор 11 состояния регистра данных предназначен для определения момента накопления (выдачи) байта в (из) регистре 8. Схема сравнения 12 осуществляет сравнение ключа зоны, хранящегося в поле регистра служебных признаков управляющего слова канала связи, с контрольным кодом сформированным шифратором 4; дешифратором 14 нуля предназначен для определения момента окончания обменом информационным массивом.

Устройство работает следующим образом.

Обмен информацией с каналами связи производится побитно. Устройство обслуживает каналы связи в мультиплексном режиме. Обмен информацией по каждому каналу разбивается на промежуточные циклы, связанные с приемом или вьадачей одного бита информации. Каждый промежуточный цикл начинается с чтения управляющего слова

0 канала, хранящегося в фиксированных ячейках зоны канала в памяти (ОЗУ), и записи его через вход-выход 19 коммутатора 18 на регистры 8, 7 и счетчики 13, 15. Заканчивается про5межуточный цикл занесением управляющего слова канала в скорректированном виде из регистров 7, 8 и счетчиков 13, 15 в те же ячейки памяти. В конце промежуточного цикла производит0ся также сброс выбранного запроса канала и бита информации,, принятого с этим запросом, хранящихся в блоке 2.

На различных этапах обработки информации промежуточные циклы отли5чаются друг от друга длительностью и операциями по обмену информацией с ОЗУ.

На входы 20 блоков 2 поступают последовательности тактовых импуль0сов дискретных каналов связи по приему и передаче, которые синхронизируют обмен информационными последовательностями и служебными сигналами с дискретными каналами связи через

5 выходы 21 этих блоков. Каждый тактовый импульс запоминается в соответствующем каждому каналу блоке 2 как запрос канала на прием бита информации из канала или на выдачу бита

0 в канал. Принимаемый из канала бит информации хранится в блоке 2 до выдачи в буферный регистр 10 для приформирования к разрядам, принятым в предыдущих промежуточных циклах из данного канала. Передаваемые из ре5гистра 8 бит информации и служебные признаки о состоянии обмена из регистра 7 хранятся до момента выдачи в канал в соответствующем блоке 2.

Если устройство не занято обслу0жива:нием ранее выбранной заявки, то по сигналу с четвертого выхода блока 1 производится опрос блоков 2 на наличие запросов каналов. После опрЬса производится приоритетная вы5борка запроса канала по сигналу с третьего выхода блока 1, поступающего на первый вход первого блока 2. Сигнал выборка последовательно проходит через все.блоки 2 до ближайшего блока, имеющего запрос кана0ла на обмен, который блокирует дальнейшее прохождение сигнала выборка, с первого выхода последнего блока 2 на третий вход блока 1 поступает сигнал готовности к обмену.

5

Сигналы о выборе запроса канала с третьих выходов блоков 2 поступают на соответствующий вход шифратора 3, который формирует двоичный код выбранного канала, С выхода шифратора 3 кода канала код поступает на первый вход блока 17, где используется как базовый адрес ячеек памяти при организации обмена. Сигналы с четвертых выходов блоков 2 поступают на входы шифратора 4, который формирует контрольный код выбранного канала. Через вход-выход 22 из блока 1 в процессор выдается запрос на чтение из ячеек зоны выбранного канала памяти управляющего слова канала. После поступления из процессора в блок 1 разрешения на работу с памятью производится чтение управляющего слова канала. После чтения управляющего слова канала из памяти и записи его на регистры 7, 8 и счетчики 13, 15 производится проверка управляющего слова. Проверка осуществляется сравнением контрольного кода, хранящегося в регистре 7, с контрольным кодом, сформированным шифратором 4. Сравнение производится схемой сравнения 12. Результат сравнения поступает в блок управления 1, Если коды не сравнивались, то производится повторное выполнение данного промежуточного цикла. Если при последующих попытках начать обмен обнаружится несравнение кодов, то блок 1 фиксирует это как отказ устройства. Если коды сравнивались, то блок 1 анализирует признак направления обмена, поступающий от регистра 7.

Прием информации из канала разбивается на два этапа: поиск комбинации фазирования и собственно прием.

Обмен информацией по каналу начинается с синхронизации приемника устройства с передатчиком абонента. Синхронизация заключается в том, что из канала в информационной последовательности поступает комбинация заранее известного вида, которую необходимо обнаружить и после этого перейти к приему информации.

оиск комбинации фазирования складывается из двух этапов: первый - поиск первого байта комбинации фазирования осуществляется путем сравнения информационной последовательности, принимаемой из каналов и накапливаемой в регистре 8, с константой фазир вания, хранящейся в ОЗУ в каждом промежуточном цикле второй - поиск следующих байтов комбинации фазирования - осуществляется путем сравнения накопленной информации в регистре данных 8 с константой фазирования причем сравнение происходит не в каждом промежуточном цикле, а только после накопления байта в регистре 8.

в соответствии с первый эта фазирования реализуется следующим образом.

После чтения управляющей информации из ОЗУ на регистры 7, 8 и счетчики 13, 15 и соответствующего контроля кодов содержимое регистра 8 со сдвигом на один разряд в сторону старших поступает (без старшего разряда) на первый вход схемы сравнения 9. (в регистре 8 хранятся биты, принятые в предыдущих промежуточных циклах из канала). На схему сравнения 9 поступает бит информации, принятый из канала связи в данном промежуточном цикле. Принятый бит добавляется к одному из младших разрядов регистра данных, определяемых типом байта и освобожденных в результате сдвига содержимого регистра данных при поступлении его на схему сравнения 9. Далее бло 1 формирует сигналы для чтения из ОЗУ константы комбинаций фазировани Адрес константы формируется блоком 17 на основании кода канала (базового адреса) и содержимого счетчика 15 (индексного адреса).

Константа фазирования из ОЗУ чер коммутатор 18 поступает на второй вход схемы сравнения 9, где происходит сравнение информационной последовательности, принятой из канал с константой комбинации фазирования прочитанной из ОЗУ.

Число разрядов регистра 8, участвующих в сравнении (8, 7, б или 5) определяется дешифратором 6, которы расшифровывает соответствующие разряды (поле формата информации) регистра 7.

Если сравнения не произошло то содержимое регистра 7 и счетчиков 13 и 15 записываются в ОЗУ через коммутатор 18 без изменения. Содержимое же регистра 8 записывается в ОЗУ со сдвигом на один разряд в сторону старших разрядов. При записи содержимого регистра 8 в ОЗУ в один из младших его разрядов производится приформирование бита информации, принятого в данном промежуточном цикле из канала. Младший разряд, к которому приформировывается бит, определяется буферным регистром 10 на основании сигнала, поступающего от дешифратора б и по сигналу от блока 1.

На этом выполнение промежуточного цикла заканчивается.

Если сравнение произошло, то сигналом с первого выхода схемы сравнения 9 корректируются разряды кода операции, хранящиеся в регистре 7. . После корректировки содержимое райрядов кода операции соответствует второму этапу фазирования. Сигнал о сравнении со второго, выхода схемы сравнения 9 поступает в блок 1, коггорый формирует сигнал Пересчет. этот, сигнал вьщается. из блока 1 на вход счетчика 13, из которого про.изводится вычитание 1, на вход счетчика 15, к которому производится добавление 1, и на вход блока 16, который осуществляет контроль переполнения счетчика 15 и выход за границу счета счетчика 13. Результат контроля поступает на восьмой вход блока 1, который анализирует сигнал о нарушении работы счетчиков..

Если нарушения в работе счетчиков не произошло, то содержимое .регистра 7 и счетчиков 13 и 15 в скорректированном виде записываются в ОЗУ.

Занесение содержимого регистра 8 в ОЗУ блокируется сигналом с пятого выхода блока 1. Вместо содержимого регистра 8 в ОЗУ записывается константа, содержащая в одном из четырех младших разрядов 1, которая необходима для нарезки из информационной последовательности, поступающей из канала связи в регистр 8, байтов огтределенного формата (5, б, 7, 8разрядов). Данная 1 оказывается, таким образом, записанной перед информационной последовательное™ тью, накапливаемой в регистре 8, и сдвигается в каждом промежуточном цикле вместе с ней. Когда 1 достигает старшего (8-го) разряда регистра, это означает, что байт накоплен. Данная константа формируется в буферном регистре 10 сигналами из дешифратора б, определяющего положение 1 в константе.

На этом выполнение данного промежуточного цикла заканчивается, а вместе с ним и выполнение первого этапа фазирования.

Если произошло нарушение в работе одного из счетчиков, то по сигналу дешифратора 16 в блок 1 прекращается выполнение данного промежуточного цикла и производится попытка повторной, обработки запроса канала, как было описано.

В следующем промежуточном цикле после чтения управляющего слова ка,нала блок 1 анализирует состояние разрядов кода операции регистра 7, которые указывают на второй этап фазирования.

Второй этап фазирования заключается в том, что сравнение информационных битов, принятых из канала, . с константой фазирования производит ся не в каждом промежуточном , как на первом этапе, а только после накопления байта заданного формата в регистре 8.

Далее дешифратор 14 анализирует состояние счетчика 13. Если содержимое этого счетчика равно О, то дешифратор 14 вырабатывает сигнал, который поступает на вход блока 1, который фиксирует окончание (отсутст.Бие) второго этапа фазирования и ор.ганизует чтение управляющего слоза канала по приему из фиксированных ячеек памяти оперативного запоминающего .устройства.

Если содержимое счетчика 13 не равно О, то начинается выполнение второго этапа фазирования. Блок 1 формирует сигнал, по которому прочитанное управляющее слово записыOвается обратно в ОЗУ. Содержимое регистра 7 и счетчиков 13 и 15 записываются без изменения, а содержимое регистра 8 - со сдвигом на один разряд в сторону старших разрядов. При

5 записи содержимого регистра 8 в память, в один из четырех его младших разрядов, определяемых дешифратором 6, из буферного регистра 10 добавляется бит информации, принятый из канала в текущем промежуточ0ном цикле. На этом .выполнение промежуточного цикла заканчивается.

Выполнение промежуточных циклов, связанных с накоплением байта, продолжается до тех пор, пока дешифра5тор 11 не обнаружит 1 в старшем разряде регистра 8.. которая означает, что байт накоплен и его содер-. жимое со сдвигом на один разряд в сторону старших разрядов поступает

0 на схему сравнения 9. На третий вход этой схемы из блока 2 поступает бит информации, принятый в данном промежуточном цикле. Бит информации добавляется к одному из младших разрядов

5 содержимого регистра 8, поступившего в тот же блок как было описано.

Блок 1 формирует сигналы для чтения следующей константы фазирования по адресу, формируемому блоком 17

0 на основании кода, поступающего от шифратора 3 (базового адреса), и содержимого счетчика 15 (индексного адреса). Константа фазирования из памяти через коммутатор 18 поступает на второй вход схемы сравнения 9

5 для сравнения с накопленным байтом.

Если сравнения .не произошло, то возобновляется первый этап фазирования, для чего по сигналу от блока 1 блок 17 формирует адрес ячеек па0мяти, где хранится управляющее слово фазирования. Адрес ячеек памяти формируется на основании кода выбранного канала, выдаваемого шифраторЬм 3. Управляющее слово фазирова5ния записывается в регистр 7, на счетчики 13 и 15 и затем по сигналу от блока 1 переписывается из регистров 7, 8 и счетчиков 13, 15 в ОЗУ в ячейки, где хранилось текущее управляющее слово. Со следующего про0межуточного цикла возобновляется первый этап фазирования, описанный ранее.

Если сравнение произошло, то схема сравнения 9 сообщает блоку 1, ко5

торый- сигналом с первого выхода корректирует счетчики 13 и 15.

Скорректированное управляющее слово из регистра 7 и счетчиков 13 и 15 записывается в ОЗУ. При этом запись содержимого регистра 8 в ОЗУ блокируется сигналом с пятого выхода блока 1. Вместо содержимого регистра 8 в ОЗУ записывается константа, содержащая 1 в одном из младших разрядов и формируемая в буферном регистре 10 как было описано. На этом данный промежуточный цикл заканчивается.

В следующем промежуточном цикле анализируется содержимое счетчика 13 дешифратором 14. Если содержимое счетчика 13 не равно нулю, то продолжается второй .этап фазирования. Если содержимое счетчика 13 равно нулю, то второй этап фазирования закончен и происходит чтение управляющего слова канала по приему. Базовый адрес ячеек памяти, где хранится управляющее слово, поступает в блок 17 из шифратора 3. Индексный адрес ячеек памяти, где хранится новое управляющее слово, формируется блоком 17 по сигналу от блока Полностью сформированный адрес (базовый и индексный) выдается в ОЗУ для чтения новой управляющей информации .

Управляющее слово канала по приёму записывается на регистр 7, счетчик 13 и счетчик 15 и начинается прием первого бита информации. При приеме информации происходит нарезка информационной последовательности, поступающей из канала на байты принятого формата, и размещение принятых байтов внутри зоны канала по адресу, который выдает счетчик 15, а также формирование массивов заданной длины. Длина массива (число байтов в массиве) определяется счетчиком 13.

Прием информации из канала происходит следующим образом.

Каждый промежуточный цикл по приему после чтения управляющего слова канала на регистры и счетчики начинается с анализа содержимого счетчика 13 дешифратором 14 и регистра 8 дешифратором 11.

Если в регистре 8 байт не накоплен, то по сигналу блока 1 содержиMCfe регистра 7, счетчиков 13 и 15 без изменения записывается в ОЗУ. Сй)держимое регистра 8 в составе управляющего слова записывается в ОЗУ со сдвигом на один разряд в сторону старшего. К освободившемуся младшему разряду в буферном регистре 10 добавляется бит информации, принятой из канала связи блоком 2.

Данные промежуточные циклы выполняются до тех пор, пока в .регистре 8 не будет накоплен байт. Накопление байта определяется дешифратором 11 по появлению 1 в старшем разряде регистра 8. По сигналу дешифратора 11 блок 1 организует запись сформированного байта в ОЗУ.

Блок 17 по сигналу блока 1 формирует адрес ячейки, где должен быть размещен накопленный байт. Адрес ячейки формируется блоком 17 по коду канала (базовому адресу), поступающему от шифратора 3, и содержимому счетчика 15 (индексному адресу). После записи в ОЗУ накопленного байта блок 1 корректирует счетчик 13 (вычитает 1) и счетчик 15 (прибавляет 1). Затем содержимое регистра 7 и счетчиков 13 и 1 в скорректированном виде записывается в ОЗУ. Запись содержимого регистра 8 в ОЗУ блокируется сигналом от блока 1. Вместо содержимого регистра 8 в ОЗУ из буферного регистра 10 записывается константа, содержащая 1 в одном из младших разрядов. Положение 1 в константе . определяется дешифратором 6. На это выполнение указанного промежуточного цикла заканчивается.

Чередование выполнения описанных промежуточных циклов, связанных с накоплением очередного байта и размещением накопленного байта в ОЗУ, продолжается до тех пор, пока содержимое счетчика.13 не станет равным нулю. Это означает, что массив инфомации по данному управляющему слову принят и необходимо выставить требование в процессор на обработку накопленного массива и прочесть новое управляющее слово для продолжения приема.

По сигналу от дешифратора 14 бло 1 организует чтени нового управляющего слова.

Прочитанное из ОЗУ новое управляющее слово, как было описано, заносится на регистр 7 и счетчики 13 и 15. в конце промежуточного цикла управляющее слово с приформированны битом информации, принятым из канала связи в данном промежуточном цикле, записывается в ОЗУ, в ячейки где хранилось текущее управляющее слово, но на этом выполнение данно.го промежуточного цикла не. заканчивается.

Блок 1 организует выставление требования на обработку массива в процессоре. Очередь организуется в специально отведенной зоне ОЗУ по приоритетам, которые хранятся в регистре 7. Внутри приоритета очередь организуется по принципу последний пришел - последний в очереди. Каждому приоритету выделено две ячейки памяти: в первой хранится первая заявка в очереди, во второй - последняя. Для всех текущих заявок в

ОЗУ организована специальная таблица.

После записи управляющего слова канала в память по сигналу блока 1 блок 17 формирует адрес ячейки, где хранится последняя заявка в очереди данного приоритета. Адрес формируется на основании номера приоритета хранящегося в регистре 7. Содержимое прочитанной ячейки памяти записывается на регистр 8, содержимое которого поступает на дешифратор 11.

Если содержимое регистра 8 равно нулю, то требований данного приоритета нет и по сигналу дешифратора 1 блок 1 организует запись требований обслуживаемого канала первым и последним в очередь, так как оно является единственным требованием данного приоритета.

Требование канала на обработку массива представляет собой код канала, по которому данный массив сформирован. Код канала поступает на второй вход коммутатора 5 от шифратора 3.

Сигналом блока 1 на коммутатор 5 разрешается занесение требованийв ОЗУ. Если содержимое регистра 8 после записи на него последнего требования из очереди не равно нулю, то в очереди данного приоритета есть заявки.

По сигналу блока 1 блок 17 формирует адрес ячейки таблицы, где будет храниться очередное требование данного приоритета. Адрес ячейки в блоке 17 формируется по содержимому регистра 8. Сформированные требования через коммутатор 5 и коммутатор 18 записываются в таблицу, отведенную для очередного требования, в ОЗУ После записи заявки в таблицу происходит также запись данной заявки последней в очереди, как было описано.

После этого промежуточный цикл, связанный с выставлением заявки в процессор, заканчивается и возобновляется новый цикл выполнения описанных промежуточных циклов, связанных с приемом информации.

Выдача информации из устройства, происходит следующим образом. Промежуточные циклы, связанные с выдачей информации, аналогичны промежуточным циклам при приеме информации.

После чтения управляющей информации из памяти на регистры 7, 8 и счетчики 13, 15 анализируется содержимое регистра 8 и счетчика 13. Если содержимое регистра 8 не равно нулю, то старший разряд регистра 8 записывается на элемент памяти выбранного блока 2 для выдачи в канал связи. Служебные признаки, хранящиеся на регистре 7 и характеризующие состояние обмена по каналу, через

второй выход также записываются на элементы памяти выбранного блока СВЯЗИ с блоком 2, После этого управляющее слово записывается в ОЗУ: Содержимое регистра 7 и счетчиков 13 и 15 без изменения, а содержимое регистра 8 - со сдвигом на один разряд в сторону старших разрядов. На этом промежуточный цикл, связанный с выдачей битав канал связи/ закончен .

0

Если содержимое регистра 8 равно нулю (кроме старшего разряда), это означает, что байт выдан в канал полностью, и по сигналу дешифратора 11 блок 1 формирует сигналы

5 для чтения очередного байта из ОЗУ для выдачи в канал. По сигналу блока 1 блок 17 на основании кода канала, поступающего от шифратора 3 (базового адреса) и содержимого счетчика 15 (индексного адреса) формиру0ет адрес чтения байта. Прочитанный из памяти байт записывается на регистр 8.

После этого содержимое старшего разряда регистра 8 и служебные сим5воль из регистра 7 записываются на элементы памяти блоков 2, Блок 1 корректирует счетчики 13 и 15. После этого управляющее слово записывается в ОЗУ: содержимое регистра

D служебных признаков 7 без изменения, а содержимое счетчиков 13, 15 - в скорректированном виде. Содержимоерегистра 8 записывается в ОЗУ со сдв-игон на один разряд в сторону

5 старших разрядов. При этом К; содержимог 1у регистра к содержимому ре гистра 8 в один из четырех младших разрядов из буферного регистра 10 записывается 1, необходимая для

0 определения момента полной выдачи байта в канал,. Разряд, куда необходимо приформировать 1, определяется дешифратором б.

После этого промежуточный цикл, связанный с чтением очередного бай5та из ОЗУ для выдачи в канал, заканчивается.

Чередование выполнения описанных промежуточных циклов, связанных с выдачей бита информации в канал свя0зи и с чтением очередного байта для последовательной выдачи в канал связи, происходит до тех пор, пока содержимое счетчика 13 не станет равнУм нулю (массив информации, опреде5ленный данным управляющим словом, полностью выдан). После этого происходит чтение нового управляющего слова для продолжения обмена и выставится требование в процессор на подготовку очередного массива для

0 передачи.

Таким образом, устройство снимает с процессора функции, связанные с синхронизацией по кодовым последовательностям и требующие значительных

5

затрат производительности прбцессора, что значительно упрощает прогрг1ммную обработку информационных массивов и ускоряет их обработку. Кроме того, устройство производит запись требования на обработку информационного массива после окончания обмена очередным массивом в ОЗУ что позволяет снять жесткие ограничения на реакцию процессора на требования по обработке массивов, так как их интенсивность по каждому каналу на несколько порядков ниже, по сравнению со .скоростью их обрабоки процессором. Запись требования через память позволяет также высвободить значительную часть элементов процессора, занятыхобработкой прерываний.

Формула изобретения Устройство для сопряжения процессора с каналами связи, содержащее М блоков связи с каналом, группы входов-выходов которых являются соответствующими группами входов-выходов синхронизации устройства, шифратор кода .канала, соединенный выходом с первым входом блока формирования адреса памяти, входом-выходом с адресным входом-выходом устройств а вторым входом - с первым выходом счетчика адреса, соединенного двусторонней связью с коммутатором магистрали, дешифратор нуля, выходом подключенный к первому входу блока управления, первый выход и второй вход которого соединены соответственно со входом счетчика адреса и первым выходом регистра служебных признаков, соединенного двусторонней связью с коммутатором магистрали, вход-выход которого является информационным входом-выходом устройства, а первый и второй входы соединены соответственно с первым выходом регистра данных и вторым выходом бцока управления, вход-выход которого является управляющим входомвыходом устройства, причем первый выход i-го блока связи с каналом подключен к первому входу (i + 1)-г блока связи с каналом (i 1, М-1)7 выход М-го и вход первого блоков связи с каналом соединены соответственно с третьими входом и выходом блока управления, четвертые вход и выход которого соответственно подключены ко вторым выходам и эходам блоков связи с каналом, третьи выхрды которых соединены с соответствующими входами шифратора кода канала, отличающееся тем, что, с целью повышения пропускной способности, в устройство введены шифратор контрольного кода, дешифратор переполнения счетчиков, дешифратор состояния регистра,данных, две схемы сравнения, буферный регистр, дешифратор типа байта и коммутатор

требования, причем четвертые выходы блоков связи с каналом подключены к соответствующим входам шифратора контрольного кода, третьи входы ко второму выходу регистра служебны признаков, а четвертые входы - ко второму выходу регистра данных, третий выход которого через дешифратор состояния регистра данных подключен к пятому входу блока управления, первый вход - к пятому выходу блока управления, четвертый выход - к третьему входу блока формирования адреса памяти, а пятый выход и второй вход - соответственно к первым входу первой схемы сравнения и выходу коммутатора магистрали, второй вход первой схемы сравнения подключен к первому выходу коммутатора магистрали, первый выход и третий вход - соответственно к шестому и четвертому входам блока управления, а четвертый вход - к первому входу буферного регистра и выходу дешифратора типа байта, входом соединенног с третьим выходом регистра служебны признаков, вход -и четвертый выход которого соединены соответственно со вторым выходом первой схемы сравнения и первым входом второй схемы сравнения, второй вход и выход которой соединены соответственно с выходом шифратора контрольного кода и седьмым входом блока управлени шестой и седьмой выходы которого соединены соответственно со вторым входом буферного регистра и первым входом коммутатора требований, выходы которых подключены к первому входу кэммутатора магистрали, второй вход коммутатора требований соединен с выходом шифратора кода канала, вход и первый выход счетчики длины массива, соединенного двусторонней связью с коммутатором магистрали, подключены соответственно к первому и второму входам дешифратора переполнения счетчиков, третьим входом соединенного со вторым выходом счетчика адреса, а первым входом и выходом - соответственно с первым выходом и восьмью входом блока управления, восьмой выход которого подключен к четвертому входу блока формирования адреса памяти, пятым входом соединенного с пятым выходом регистра служебных признаков , второй выход счетчика длины массива подключен ко входу дешифратора нуля.

Источники информации, принятые во внимание при экспертизе

1,Усольцев А. Г. и Кислин Б. П. Сопряжение дискретных каналов связи с ЭВМ. IC, Связь, 1973, гл. 4, 5.

2,Авторское свидетельство СССР 525939, М. кл; G Об F 3/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора обмена с каналами связи | 1974 |

|

SU525939A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Селекторный канал | 1982 |

|

SU1053096A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1307462A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

Авторы

Даты

1980-09-15—Публикация

1978-06-28—Подача