00

.

с

151

Изобретение относится к электротехнике и может быть использовано в системах автоматического управления и роботизированных комплексах для уп- равления шаговыми электродвигателями (шэд) с самокоммутацией и электрическим дроблением шага с помощью синус- но-косинусного датчика положения, где

24

БОСД 3 содержит селектор 18 квадранта, аналоговые входы которого соединены с выходами СКВТ 2, коммутационный вход которого соединен с шиной 14 кода 1 квадранта, а выходы - с аналоговыми входами третьего 19 и четвертого 20 ПЦАП, цифровые входы которых соединены с выходами соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым электродвигателем | 1987 |

|

SU1520647A1 |

| Устройство для управления шаговым электродвигателем с дроблением шага | 1987 |

|

SU1417162A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Следящий преобразователь угла поворота вала в код | 1984 |

|

SU1243092A1 |

| Преобразователь координат | 1983 |

|

SU1120387A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1365353A2 |

| Преобразователь угла поворота вала с контролем выходного кода | 1986 |

|

SU1334373A2 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312737A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1644380A1 |

Изобретение относится к электротехнике, в частности к дискретному электроприводу. Цель изобретения состоит в повышении производительности путем увеличения быстродействия и расширении эксплуатационных возможностей. Электропривод содержит синусно-косинусный вращающийся трансформатор 2, блок 3 обработки сигналов датчика, вырабатывающий код положения, аналоговые сигналы, скорости и ускорения, регулятор 8, вырабатывающий закон регулирования скорости, блок сопряжения 6, выдающий аналоговый сигнал ошибки, умножаемый в цифроаналоговых преобразователях 9 и 10 на синусоидальный и косинусоидальный сигналы, частота которых определяется сигналом положения ротора двигателя 1. Такой же модуляции в блоке 3 подвергается сигнал с выхода вращающегося трансформатора 2 после приведения его к первому квадранту в селекторе квадрантов 18. 1 з.п.ф-лы, 3 ил.

нолучение высокой точности нозициони- 10 ветственно ПЗУ 15 и 17, а выходы - с

рования и надежности функционирования связано с использованием малоредук- торного и безредукторного шагового электропривода (ШЭП)..

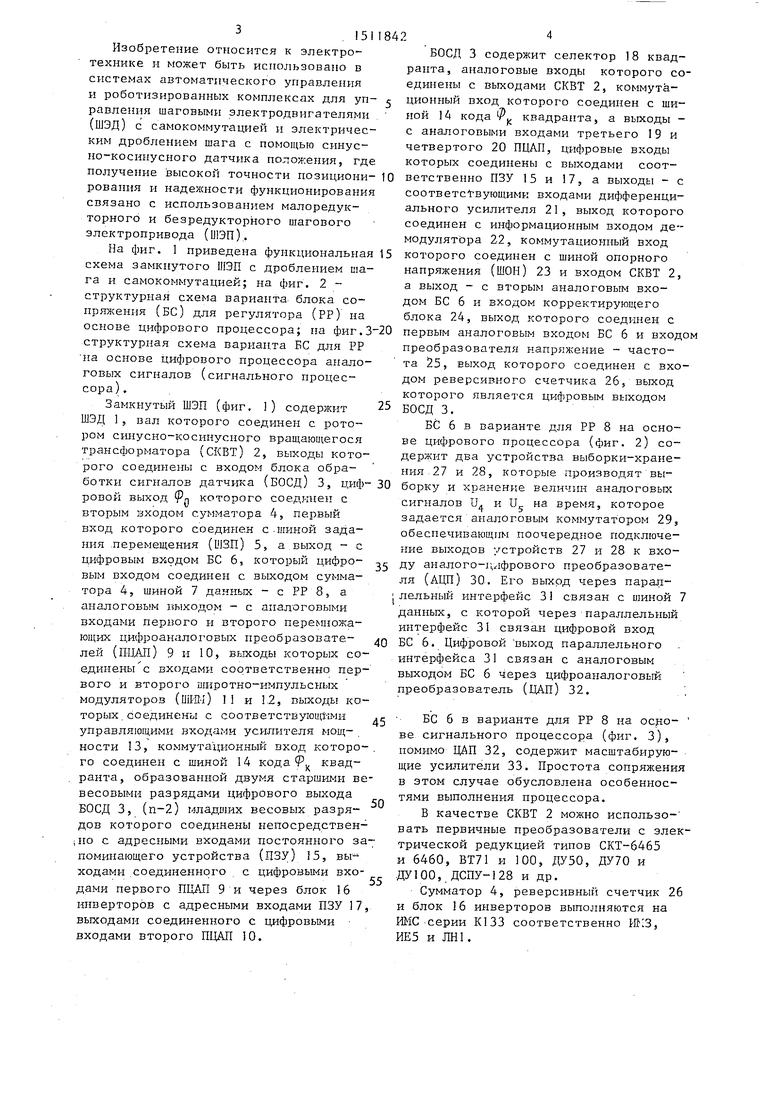

На фиг. 1 приведена функциональная 15 которого соединен с шиной опорного схема замкнутого ШЭП с дроблением шага и самокоммутацией; на фиг. 2 - структурная схема варианта блока сопряжения (БС) для регулятора (РР) на основе цифрового процессора; на фиг.3-20 первым аналоговым входом ЕС б и входом структурная схема варианта БС для РР преобразователя напряхсение - частота Й5, выход которого соединен с входом реверсивного счетчика 26, выход которого является цифровым вь1ходом БОСД 3.

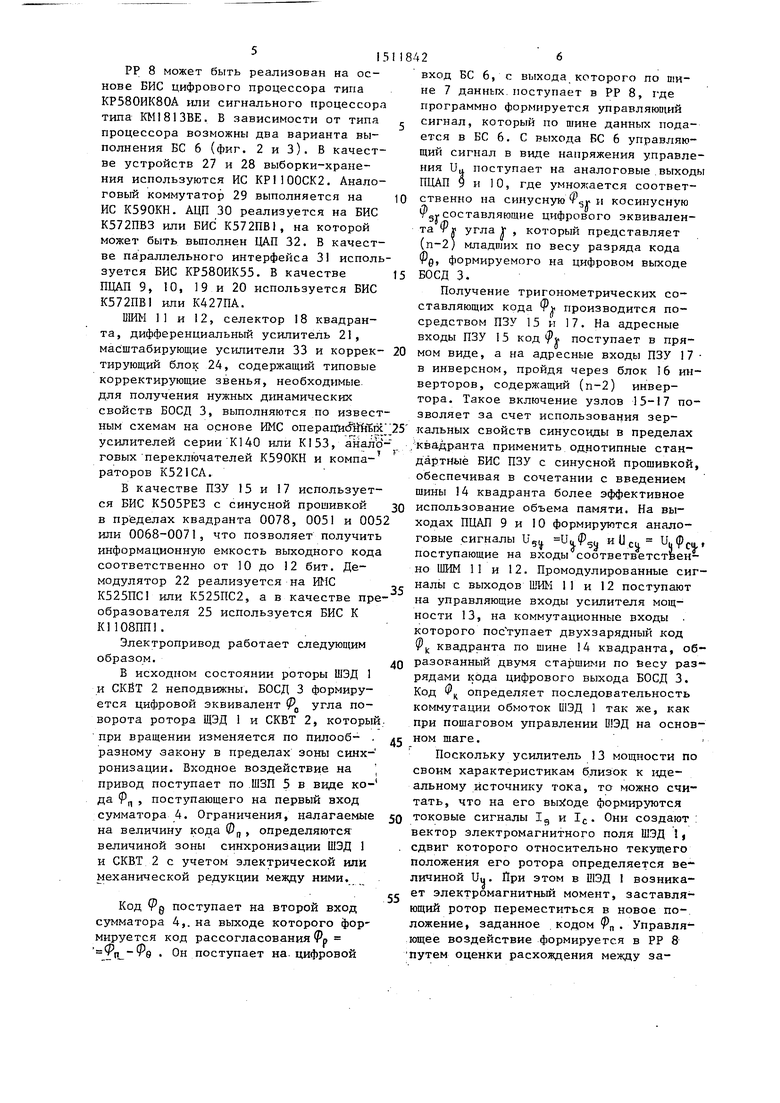

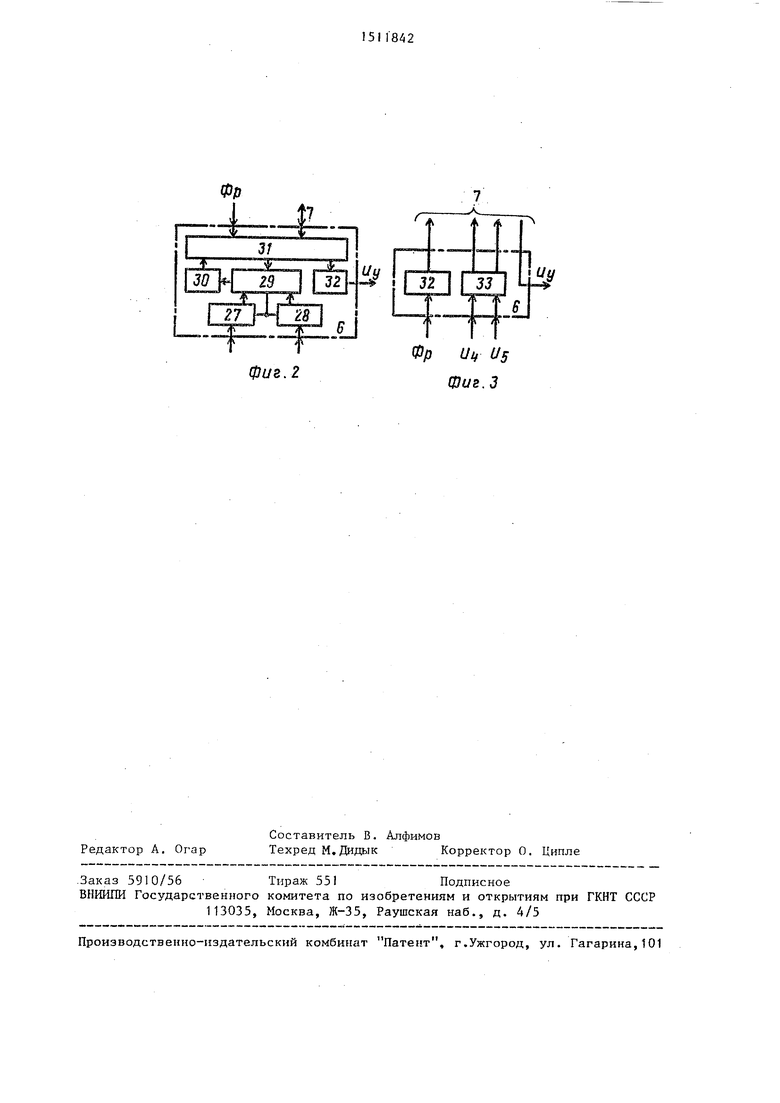

БС 6 в варианте для РР 8 на основе цифрового процессора (фиг. 2) сосоответс -вующими входами дифференциального усилителя 21, выход которого соединен с информационным входом демодулятора 22, коммутационный вход

напряжения (ШОИ) 23 и входом СКВТ 2, а выход - с вторым аналоговым входом БС 6 и входом корректирующего блока 24, выход которого соединен с

на основе цифрового процессора аналоговых сигналов (сигнального процессора).

Замкнутый ШЭП (фиг. 1) содержит ШЭД 1, вал которого соединен с ротором сш1усно-косинусного вращающегося трансформатора (СКВТ) 2, выходы которого соединены с входом блока обра25

держит два устройства выборки-храгш- ния 27 и 28, которые производят выботки сигналов датчика (БОСД) 3, циф- 30 борку и хранение величин аналоговых

40

ровой выход фп которого соединен с вторым входом сумматора 4, первый вход которого соединен с.шиной задания .перемещения (ШЗП) 5, а выход - с цифровым входом БС 6, который цифровым входом соединен с выходом сумматора 4, шиной 7 данных - с РР 8, а аналоговым выходом - с аналоговыми входами первого и второго перемножающих цифроаналоговых преобразователей (П-ЦАП) 9 и 10, выходы которых со- единены с входами соответственно первого и второго широтно-импульсных модуляторов (ШШ-l) 11 и 1.2, выходы которых, соединены с соответствующими д управлягапдими входами усилителя мощ ности 13, коммутационный вход которо-. го соединен с шиной 14 кода Р квадранта, образованной двумя старшими ве- весовыми разрядами цифрового выхода БОСД 3, (п-2) младишх весовых разрядов которого соединены непосредствен- iiio с адресными входами постоянного запоминающего устройства (ПЗУ) 15, вы-- ходами .соединенного с цифровыми вхо дами первого ПЦАП 9 и через блок 16 инверторов с адресными входами ПЗУ 17, выходами соединенного с цифровыми входами второго ПЦАП 10.

сигналов и и U на время, которое задается аналоговым коммутатором 29, обеспечивающим поочередное подключение выходов устройств 27 и 28 к вхо- 35 ДУ аналого-г ифрового преобразователя (АЦП) 30. Его вькрд через napari- лельный интерфейс 31 связан с шиной 7 данных, с которой через параллельный интерфейс 31 связал цифровой вход

50

55

БС 6. Цифровой выход параллельного интерфейса 31 связан с аналоговым вьрсодом БС 6 через цифроаналоговый преобразователь (ЦАП) 32.

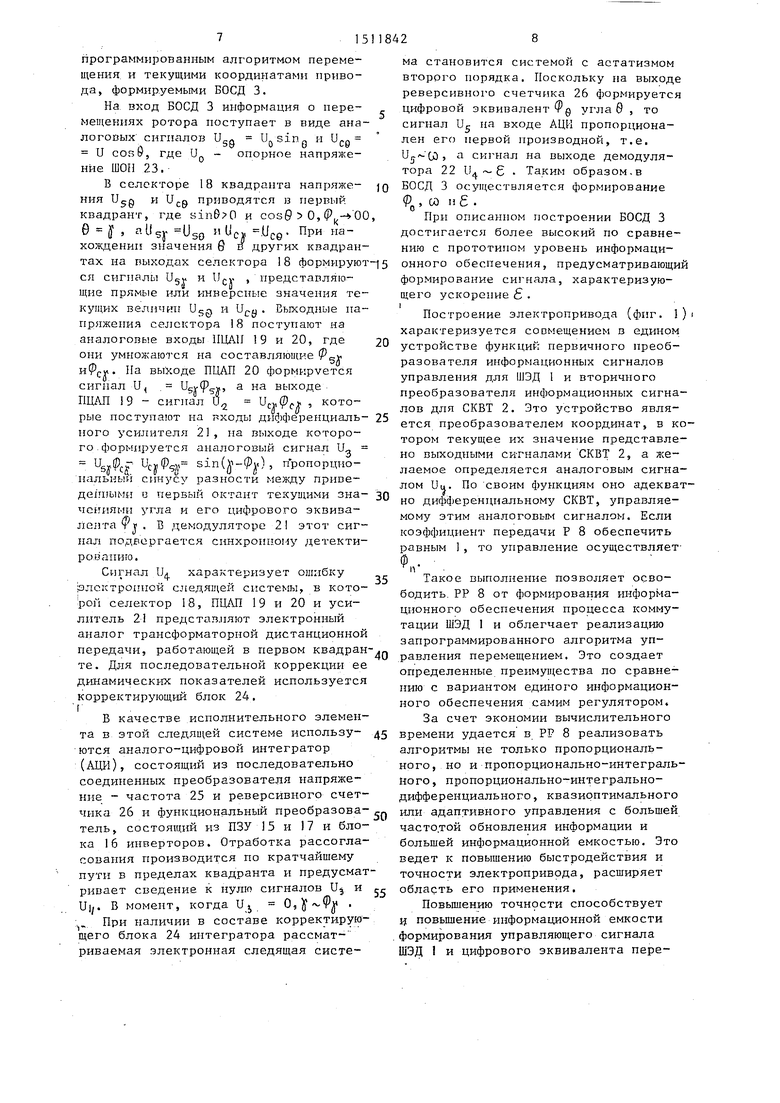

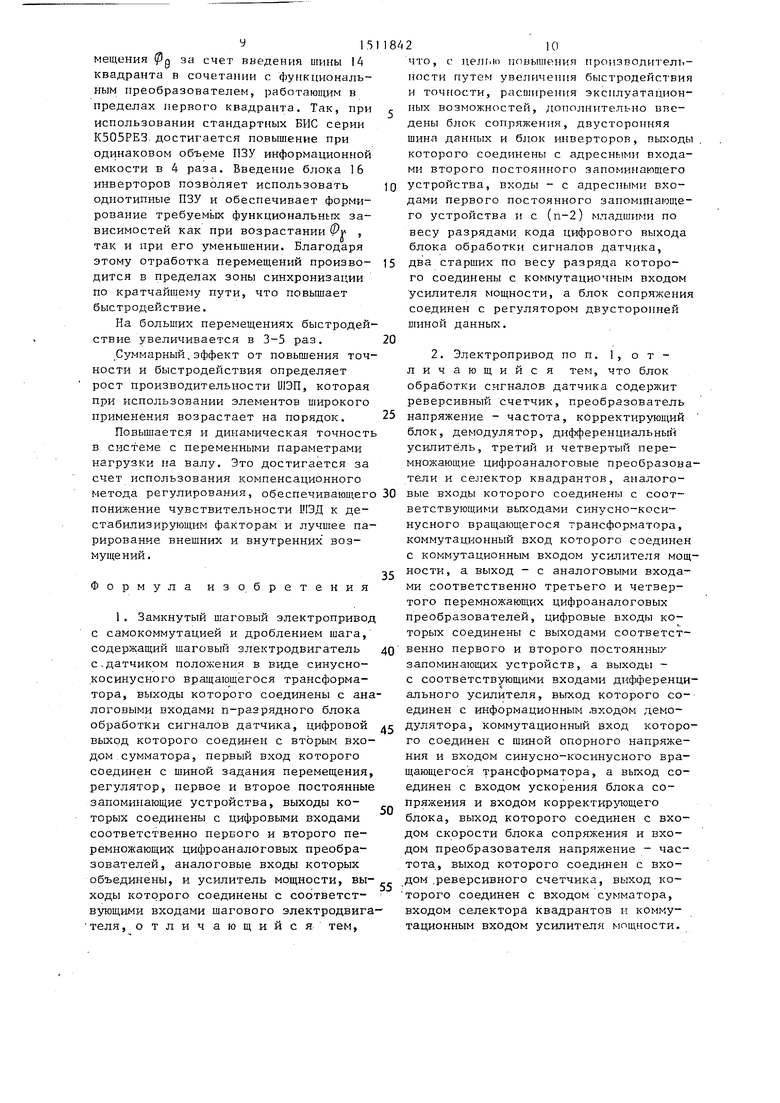

БС 6 в варианте для РР 8 на серо- ве сигнального процессора (фиг. 3), помимо ЦАП 32, содержит масштабирующие усилители 33. Простота сопряжения в этом случае обусловлена особенностями выполнения процессора.

В качестве СКВТ 2 можно использо- вать первичные преобразователи с электрической редукцией типов СКТ-6465 и 6460, ВТ71 и 100, ДУ50, ДУ70 и .ДУЮО, ДСПУ-128 и др.

Сумматор 4, реверсивны счетчик 26 и блок 16 инверторов выполн яются на ИМС .серии К133 соответственно Ш;3, ИЕ5 и ЛН1.

соответс -вующими входами дифференциального усилителя 21, выход которого соединен с информационным входом демодулятора 22, коммутационный вход

которого соединен с шиной опорного первым аналоговым входом ЕС б и входо преобразователя напряхсение - частота Й5, выход которого соединен с входом реверсивного счетчика 26, выход которого является цифровым вь1ходом БОСД 3.

напряжения (ШОИ) 23 и входом СКВТ 2, а выход - с вторым аналоговым входом БС 6 и входом корректирующего блока 24, выход которого соединен с

держит два устройства выборки-храгш- ния 27 и 28, которые производят выборку и хранение величин аналоговых

сигналов и и U на время, которое задается аналоговым коммутатором 29, обеспечивающим поочередное подключение выходов устройств 27 и 28 к вхо- ДУ аналого-г ифрового преобразователя (АЦП) 30. Его вькрд через napari- лельный интерфейс 31 связан с шиной 7 данных, с которой через параллельный интерфейс 31 связал цифровой вход

40

.

0

5

БС 6. Цифровой выход параллельного интерфейса 31 связан с аналоговым вьрсодом БС 6 через цифроаналоговый преобразователь (ЦАП) 32.

БС 6 в варианте для РР 8 на серо- ве сигнального процессора (фиг. 3), помимо ЦАП 32, содержит масштабирующие усилители 33. Простота сопряжения в этом случае обусловлена особенностями выполнения процессора.

В качестве СКВТ 2 можно использо- вать первичные преобразователи с электрической редукцией типов СКТ-6465 и 6460, ВТ71 и 100, ДУ50, ДУ70 и .ДУЮО, ДСПУ-128 и др.

Сумматор 4, реверсивны счетчик 26 и блок 16 инверторов выполн яются на ИМС .серии К133 соответственно Ш;3, ИЕ5 и ЛН1.

РР 8 может быть реализован на основе БИС цифрового процессора типа КР580ИК80А или сигнального процессора типа КМ1813ВЕ, В зависимости от типа процессора возможны два варианта выполнения БС 6 (фиг. 2 и З). В качестве устройств 27 и 28 выборки-храпения используются ИС KPI100CK2. Аналоговый коммутатор 29 выполняется на ИС К590КН. АЦП 30 реализуется на БИС К572ПВЗ или БИС К572ПВ1, на которой может быть выполнен ЦАП 32. В качестве параллельного интерфейса 3 используется БИС КР580ИК55. В качестве ПЦАП 9, 10, 19 и 20 используется БИС К572ПВ1 или К427ПА.

ШИМ 11 и 12, селектор 18 квадранта, дифференциальный усилитель 21, масштабирующие усилители 33 и корректирующий блок 24, содержащий типовые корректирующие звенья, необходимые для получения нужных динамических свойств БОСД 3, выполняются по известным схемам на основе И1ЯС операЦййШйтх усилителей серии К140 или KI53, анало говых переключателей К590КН и компа- раторов К521СА.

В качестве ПЗУ 15 и 17 используется БИС К505РЕЗ с синусной прошивкой в пределах квадранта 0078, 0051 и 005 или 0068-0071, что позволяет получить информационную емкость выходного кода соответственно от 10 до 12 бит. Демодулятор 22 реализуется на ИНС К525ПС или К525ПС2, а в качестве преобразователя 25 используется БИС К К 108ПП.

Электропривод работает следующим образом.

В исходном состоянии роторы ШЭД 1 и СКВТ 2 неподвижны. БОСД 3 формируется цифровой эквивалент угла поворота ротора ЩЭД 1 и СКВТ 2, который при вращении изменяется по пилооб- . разному закону в пределах зоны синхронизации. Входное воздействие на привод поступает по ШЗП 5 в виде ко- да Р , поступающего на первый вход сумматора 4. Ограничения, налагаемые на величину кода Ф„, определяются величиной зоны синхронизации ШЭД 1 и СКВТ 2 с учетом электрической или механической редукции между ними.

Код Ф0 поступает на второй вход сумматора 4,. на выходе которого фор мируется код рассогласования Фр Он поступает на. цифровой

-

2,

10

15

20

35

40

50

55

426

вход БС 6, с выхода которого по шине 7 данных, поступает в РР 8, где программно формируется управляюп1ий сигнал, который по шине данных подается в БС 6. С выхода БС б управляющий сигнал в виде напряжения управления UM поступает на аналоговые выходы ПЦАП 9 и 10, где умножается соответственно на синусную Pgip и косинусную

Г-).составляющие цифрового эквивален/лта ГУ угла t , который представляет

(п-2) младших по весу разряда кода VQ, формируемого на цифровом выходе БОСД 3.

Получение тригонометрических составляющих кода TV производится посредством ПЗУ 15 и 17. На адресные входы ПЗУ 15 код у поступает в прямом виде, а на адресные входы ПЗУ 17 в инверсном, пройдя через блок 16 инверторов, содержащий (п-2) инвертора. Такое включение узлов 15-17 позволяет за счет использования зеркальных свойств синусоиды в пределах квадранта применить однотипные стандартные БИС ПЗУ с синусной прошивкой, обеспечивая в сочетании с введением шины 14 квадранта более эффективное использование объема памяти. На выходах ПЦАП 9 и IО формируются аналоговые сигналы Uga и,1Р поступающие на входы но ШИМ 11 и 12. Промодулированные сигналы с выходов ШИМ 11 и 12 поступают на управляющие входы усилителя мощности 13, на коммутационные входы которого пос тупает двухзарядный код |(. квадранта по шине 14 квадранта, образованный двумя старшими по весу раз- рядами кода цифрового выхода БОСД 3. Код Ф определяет последовательность коммутации обмоток ШЭД 1 так же, как при пошаговом управлении ШЭД на основном шаге.

Поскольку усилитель 13 мощности по своим характеристикам близок к 1зде- альному источнику тока, то можно считать, что на его выходе формируются токовые сигналы 1 и 1с. Они создают ; вектор электромагнитного поля ШЭД | сдвиг которого относительно текущего положения его ротора определяется величиной и. При этом в ШЭД 1 возникает электромагнитный момент, заставляющий ротор переместиться в новое положение, заданное . кодом „ . Управляющее воздействие формируется в РР 8 Путем оценки расхождения между заи.} Uu Pgy HUcjj ц Рсч. входы соответветственпрограммированным алгоритмом перемещения и текущими координатами привода, формируемыми БОСД 3.

На. вход БОСД 3 информация о перемещениях ротора поступает в виде аналоговых сигналов и, и cos б, где нйе ШОН 23.

В селекторе 18 квадраьгга напряже о

и Ucg

опорное напряжения Ugg и Uj.g приводятся в первый

К на 00

квадрант, где и ,(Р

, (Uj- Uso .Uc0- При хождении значения б в других квадраней сигналы Ugw и Ugj.. , представляющие прямые или инверсные значения текущих величин Ugg и Uj,y . Выходные напряжения селектора 18 поступают на аналоговые входы ПЦАИ 19 и 20, где они умножаются на составляющие v иФс«. Па выходе ПЦАП 20 формируется

20

а на выходе

тах на выходах селектора 18 формируют- 5 онного обеспечения, предусматривающий

формирование сигнала, характеризующего ускорение .

Построение электропривода (фиг. l)i характеризуется совмещением в едином устройстве функций первичного преобразователя информационных сигналов управления для ШЭД 1 и вторичного преобразователя информационных сигналов для СКВТ 2. Это устройство является преобразователем координат, в котором текущее их значение представлено выходными сигналами СКВТ 2, а желаемое определяется аналоговым сигналом Uu. По своим функциям оно адекватно дифференциальному СКВТ, управляемому этим аналоговы т сигналом. Если коэффициент передачи Р 8 обеспечить равным 1, то управление осуществляетсигнал и

ППАП 19 .. сигнал и

- 2 7 рые поступают на входы дифференциаль- 25

ного усилителя 21, на выходе которого .формируется аналоговый сигнал и„

sin

(

пропорцио-

30

35

Usjfi cj; cyp.j.

нальныи синусу разности между приведенными о первый октант текущими значениями угла и его цифрового эквива- jieiira у J , В демодуляторе 21 этот сигнал подвергается синхронному детекти- ро.вапию.

Сигнал и характеризует ошибку рлсктропной следящей системы, в кото- рой селектор 18, ППДП 19 и 20 и усилитель 21 предетггв.няют электронный аналог трансформаторной дистанционной передачи, работающей в нервом квадран-. те. Для последовательной коррекцни ее динамических показателей используется

корректирующий блок 24. г

В качестве исполнительного элемента в этой следящей системе использу- дЗ ются аналого-цифровой интегратор (АЦИ), состоящий из последовательно соединенных преобразователя напряжеТакое выполнение позволяет освободить. РР 8 от формирования информационного обеспечения процесса коммутации ШЭД 1 и облегчает реализацию запрограммированного алгоритма управления перемещением. Это создает определенные преимущества по сравнению с вариантом единого информационного обеспечения самнм регулятором.

За счет экорюмии вычислительного времени удается в РР 8 реализовать алгоритмы не только пропорционального, но и пропорционально-интегрального , пропорционально-интегрально- дифференциального , квазиоптимального

За счет экорюмии вычислительного времени удается в РР 8 реализовать алгоритмы не только пропорционального, но и пропорционально-интеграль ного , пропорционально-интегрально- дифференциального , квазиоптимального

ние - частота 25 и реверсивного счетчика 26 и функциональный преобразова- или адаптивного управления с большей

часто.той обновления информации и большей информационной емкостью. Это ведет к повышению быстродействия и

тель, состоящий из ПЗУ 15 и 17 и блока 16 инверторов. Отработка рассогласования производится по кратчайшему пути в пределах квадранта и предусматривает сведение к нулю сигналов Uj

и

Ui;. В момент, когда Uj О, ;. При наличии в составе корректирующего блока 24 интегратора рассмат- риваемая электронная следящая систе55

точности электропривода, расширяет область его применения.

Повьшению ТОЧН9СТИ способствует 1J повьш1ение информационной емкости формирования управляющего сигнала ШЭД 1 и цифрового эквивалента пере

10

,

ма становится системой с астатизмом второго норядка. Поскольку на выходе реверсивного счетчика 26 формируется цифровой эквивалент Фд угла 0 , то сигнал Uj на входе АЦН пропорционален его первой производной, т.е. , а сигнал на выходе демодулятора 22 и . Таким образом,в БОСД 3 осу1цествляется формирование

р,, 00 и е.

При описанном построении БОСД 3 достигается более высокий по сравнению с прототипом уровень информаци

Такое выполнение позволяет освободить. РР 8 от формирования информационного обеспечения процесса коммутации ШЭД 1 и облегчает реализацию запрограммированного алгоритма управления перемещением. Это создает определенные преимущества по сравнению с вариантом единого информационного обеспечения самнм регулятором.

За счет экорюмии вычислительного времени удается в РР 8 реализовать алгоритмы не только пропорционального, но и пропорционально-интегрального , пропорционально-интегрально- дифференциального , квазиоптимального

или адаптивного управления с большей

55

точности электропривода, расширяет область его применения.

Повьшению ТОЧН9СТИ способствует 1J повьш1ение информационной емкости формирования управляющего сигнала ШЭД 1 и цифрового эквивалента переу1.5

мещения ф за счет введения шины 14 квадранта в сочетании с функциональным преобразователем, работающим в пределах первого квадранта. Так, при использовании стандартных БИС серии К505РЕЗ достигается повышение при одинаковом объеме ПЗУ информационной емкости в 4 раза. Введение блока 16 инверторов позволяет использовать однотипные ПЗУ и обеспечивает формирование требуемьк функциональных зависимостей как при возрастании фу- , так и при его уменьшении. Благодаря этому отработка перемещений производится в пределах зоны синхронизации по кратчайшему пути, что повьппает быстродействие.

На больших перемещениях быстродействие увеличивается в 3-5 раз.

Суммарный.эффект от повышения точности и быстродействия определяет рост производительности ШЭП, которая при использовании элементов широкого применения возрастает на порядок.

Повышается и динамическая точность в системе с переменными параметрами нагрузки на валу. Это достигается за счет использования компенсационного метода регулирования, обеспечивающего понижение чувствительности к дестабилизирующим факторам и лучшее парирование внешних и внутренних возмущений.

Формула изобретения

84210

что, с гювышения пpoизвoд тeл - ности путем увеличения быстродействия и точности, расширения эксплуатацион- ных возможностей, дополнительно введены блок сопряжения, двусторонняя шина данных и блок инверторов, выходы которого соединены с адресными входами второго постоянного запоминаюп1его

Q устройства, входы - с адресными входами первого постоянного запом1шаю це- го устройства и с (п-2) младшими по весу разрядами кода цифрового выхода блока обработки сигналов датчика,

5 два старших по весу разряда которого соединены с коммутационным входом усилителя мощности, а блок сопряжения соединен с регулятором двусторонней шиной данных.

0

5 напряжение - частота, корректирующий блок, демодулятор, дифференциальный усилитель, третий и четвертый перемножающие цифроаналоговые преобразователи и селектор квадрантов, аналого0 вые входы которого соединены с соответствующими выходами синусно-коси- нусного вращающегося трансформатора, коммутационный вход которого соединен с коммутационным входом усилителя мощг ности, а выход - с аналоговыми входами соответственно третьего и четвертого перемножающих цифроаналоговых преобразователей, цифровые входы которых соединены с выходами соответст0 венно первого и второго постоянных запоминающих устройств, а выходы с соответствующими входами дифференциального усилителя, выход которого соединен с информационным .входом демог дулятора, коммутационный вход которого соединен с шиной опорного напряжения и входом синусно-косинусного вращающегося трансформатора, а выход соединен с входом ускорения блока сопряжения и входом корректир тощего блока, выход которого соединен с входом скорости блока сопряжения и входом преобразователя напряжение - частота, выход которого соединен с входом .реверсивного счетчика, выход ко- торого соединен с входом сумматора, входом селектора квадрантов и коммутационным входом усилителя oщнocти.

0

Фр

фиг. 2

4f/

-ц I

Фр Uif Us фиг. 3

| Устройство для управления шаговым двигателем | 1981 |

|

SU1015335A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Замкнутый шаговый электропривод | 1984 |

|

SU1259465A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-09-30—Публикация

1988-01-13—Подача