ел ел

со

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| Компаратор | 1986 |

|

SU1322227A1 |

| Устройство считывания информации для доменной памяти | 1990 |

|

SU1751813A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| Устройство формирования сигнала изображения | 1985 |

|

SU1297259A1 |

| Преобразователь напряжения с защитой от асимметрии | 1990 |

|

SU1772877A1 |

| Формирователь центра тяжести импульсов | 1983 |

|

SU1129581A1 |

| Выпрямитель для дуговой сварки с комбинированными внешними характеристиками | 1988 |

|

SU1637969A1 |

| Источник питания электрофильтра | 1983 |

|

SU1201807A1 |

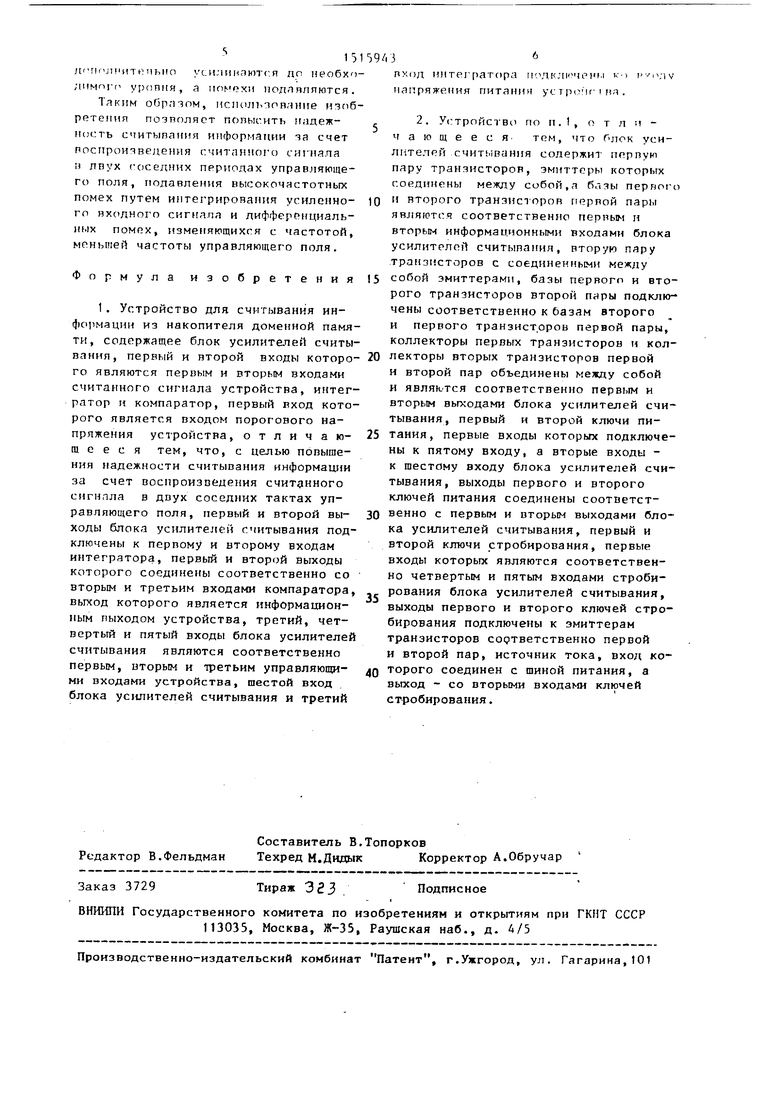

Изобретение относится к вычисли- телы1П11 технике и может бьт, использовано при иострпснии таноминлюших УСТрОЙСТП на ИИ-ЧЧПЛРИЧСГКИХ МШ ЧИТИЫХ домсплк, наксититпли которых содс ржат в Tpaine cMiiTi.inainiH рабочей и комнен- сацио11Н.П1 длтчяки. Цель и юбрг тенпя - noniiiiiicHUi: н,1.чеж||пс |-и с П тынлиия nHtJop- млции ил счет иоспрпиз чедония считан ного сигнала в /твух соседних тактах управляющего поля. Устройство для считмпанил информации из накоттителя доменной памяти содержит блок 1 усилителей считывания, интегратор 2 и компаратор 3. Блок 1 усилителей счи- тыранил включает в себя первую пару 4, 5 и вторую пару 6, 7 транзисторов, первый 8 и нторой 9 ключи питания, перпый 10 и второй 11 ключи стро- биронянип и источник 12 тока. Интегратор обрааопан накопительными конденсаторами 13, 14 и истокоными Повторителями на полепых транзисторах 15, 16 и резисторах 17, 18. Надежность с читыванип повышается за счет удпоении усиленного считанного сигнала, пг даиления высокочастотных помех путем интегрирова П1я усиленного входного сигнала и подавления диффе- ренниальн1.1х помех, частота изменения котормх Meftbme частоты управляющего поля. 1 з.л.ф-лы, 1 ил. С 9 (Л

77

«Я.А

Ичйбпетрние отмп. мтсп к тилчисли- телыюй Ti XHure и Obirii ,-- :1ов;п1о IVHM эапоминлюцщк ycTpov u-.Tn и.ч: uKjinnnpu iecioix м;1гиит- иых домет1зх, li.ittnriiii с чи кот рьгх cf- р траг .-гс считыялиия рлбо тии и кo иeн :. дятчики.

Цель и-лоРрр-п.иия - noBMii; iin , надежности считывания информагщ гча счет вогпроизпедепил считанного смг- алд р дпух соседких трактах упрап- ляющего поля.

Яа чг1 теже показана схема устрой-- :тва дл считывания информации ия гакоПи f jin доменной памяти.

Устройство для считывания (мгформа- ,ции г.од,ержит бдок 1 усилителей считывания, и 1тегратор 2 и компаратор 3.

.ж )-(:илителей считывания вклю- чает в cet;,4 первую пару траиэисторов и 5, пару транэисторои 6 и /, перпый 8 и второй 9 ключи пита ним, первый 10 и второй 11 кдмочи стробиропалия и источник 12 тока.

Интегратор содержит перяый 13 и пторой Ь 4 1;акопитедьпые ко1гденсаторы перБ,111 15 и второй 16 полеоые тран- чисгоры, перпыи 17 и второй 18 нагрузочные резисторы.

Ил чертеже показаны первый и второй икоды 19, 20 считашюго гигнала устройгтнп, первый 21, второй 22 и третий 2Э управдяю1Щ1е пходы устройства, вход 24 напряжения + Е питани устройства, вход 25 порогового напряжения устройства, информационный выход 26 устройства, накопитель 27 доменной памяти с рабочим 28 и компенс 1У1011НЫМ 29 датчиками считывания, ис- точники тока 30, 31 для рабочего и компенсацпо1П ого датчиков считывания, ишна 32 нулевого потенциала и шина 33 питания -Е.

Устройство работает следую цим об- разом.

Датчики 28, 29 и источники 30 и 31 тока об15лзуют мостовую схему детектирования доменов, с диагонали которой снимаются электрические си1- налы считывания, пропорююнальные изменению сопротивлений датчиков при прохождении вблизи них доменов. В момент времени, предшествуюп1ий счи- танному сигналу, на первые входы ключей 8, 9 питания по входу 21 поступает упр,чрлян;1ЯУ1й импутьс и ключи питания чаь ыкпытся на премя 2,, .

При 1 1 г М Н,(Л ЬНЫС- К( |Н;1РИГ.аТО

рм 13 и 1 ч.-;;;тжл1отся дс Напряжения

V

и ипсме гл 1М.1. ключей 8, 9

ПС г 1 л-1:я чаря - пныни некотчфое npf- мя. После рачмыканип ключ сй 8 и 9 с И1.п. датчиков 28 и 29 на бате rp.-nni;(-Topon /I и 5 поступает c ;итaн- нми сигнал. 1а пррп1,й вход первого к.пча 10 строПиропания подаетс.я импульс пррпси с) i .TpoRa. Киюч 10 замы- к.чгтся мл время б. . При зтом оказы- п-тртгя г кл10 1ЕЧ1Пой дифференциальная пара Т1 ап-зисторотз А, 5с источником 12 тока п цепи тмиттеров. Током включенных транзисторов /i и 5 копдепсаторы 13 и 14 13 время

разряжаются на

5

0 ,

0

5 0

5

0 55

величины напряжения, пропорциональные токам транзисторов. По истечении време1П1 .лействия сигнала первого строба первая ди1Ьференциапьная пара отключается. При этом, если на базе транзистора 4 напряжение больше, чем на баяе транзистора 5, то конденсатор 13 разрядится больше,чем конденсатор 14. Разность напряжений между выводами конденсаторов 13 и 14 пропорциональна леличине сигнала с выхода датчика 28. В следующем периоде управляющего поля, когда несущий информацию домен переместится из датчика 28 в датчик 29, возникает повторный считавсный сигнал противоположной полярности. Это сигнал поступает с базы транзисторов первой и второй пар, но во втором периоде импудьсом второго строба по входу 23 замыкается на.время Oj. ключ 11, включающий дифференциальную пару на транзисторах 6, 7 с источником 12 тока. При этом конденсатор 13 и в этом периоде разряжается больше, чем конденсатор 14. В результате напряжение между выводами конденсаторов, отображающее входной сигнал, практически удваивается.

Напряжение с выходов накопительных конденсаторов 13 и 14 поступает на входы истоковых повторителей, выполненных на полевых транзисторах 15, 16 и резисторах 17, 18. Благодаря большому входному сопротивлению истоковых повторителей исключается влияние последующих электрических цепей на работу накопительных конденсаторов, С В1)1ходоп истоковых повторителей сигналы подаются на входы компаратора 3, в1- полняю цего функцию различения полезных сигналов и помех по их амплитуде. При этом полезные сигналы

П Ч1г Л11цт м1Ы1о усилиилютс.п до необходимого уропня, а помехи поллялпются.

Тяким оОрпзом, HciuiJib ioB,4iiite изпб- ретепип поэполяст повысить надежность считывания информации -эа счет роснроияведення считаннщ о сигнала п лпух госединх периодах управляющего поля, подавления высокочастотных помех путем интегрирования усиленного нхс)дного сигнала и дифферрнциаль- ных помех, изменяющихся с частотой, меньшей частоты управляющего поля.

Формула изобретения

Составитель В.Топорков Редактор В.Фельдман Техред М.Дидык Корректор А.Обручар

Заказ 3729

Тираж 323 .

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКМТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/5

вход интегратора подклюмсч м ) i -- i -iv напряжения питании устрочг i rsn .

собой эмиттерами, базы первого и второго транзисторов второй пары подключены соответственно к базам второго и первого транзисторов первой пары, коллекторы первых транзисторов и коллекторы вторых транзисторов первой и второй пар объединены между собой и являются соответственно первым и вторым выходами блока усилителей считывания, первый и второй ключи питания, первые входы которых подключены к пятому входу, а вторые входы - к шестому входу блока усилителей считывания, выходы первого и второго ключей питания соединены соответственно с первым и вторым выходами блока усилителей считывания, первый и второй ключи стробирования, первые входы которых являются соответственно четвертым и пятым входами стробирования блока усилителей считывания, выходы первого и второго ключей стробирования подключены к эмиттерам транзисторов содтветственно первой и второй пар, источник тока, вход которого соединен с шиной питания, а выход - со вторыми входами ключей стробирования.

Подписное

| Electronic De., v.24, Nov.22, 1979, p | |||

| Пружинная погонялка к ткацким станкам | 1923 |

|

SU186A1 |

| Circuits M-inuf act-tir inp, v.19, 19/0, № 9, p | |||

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1991-09-23—Публикация

1986-12-22—Подача