Изобретение относится к технике телевидения и может быть использовано в системах СБИС видеокодека цифровой обработки для повышения разрешающей способности квантования.

Цель изобретения - повышение разрешающей способности, быстродействия и упрощение устройства,

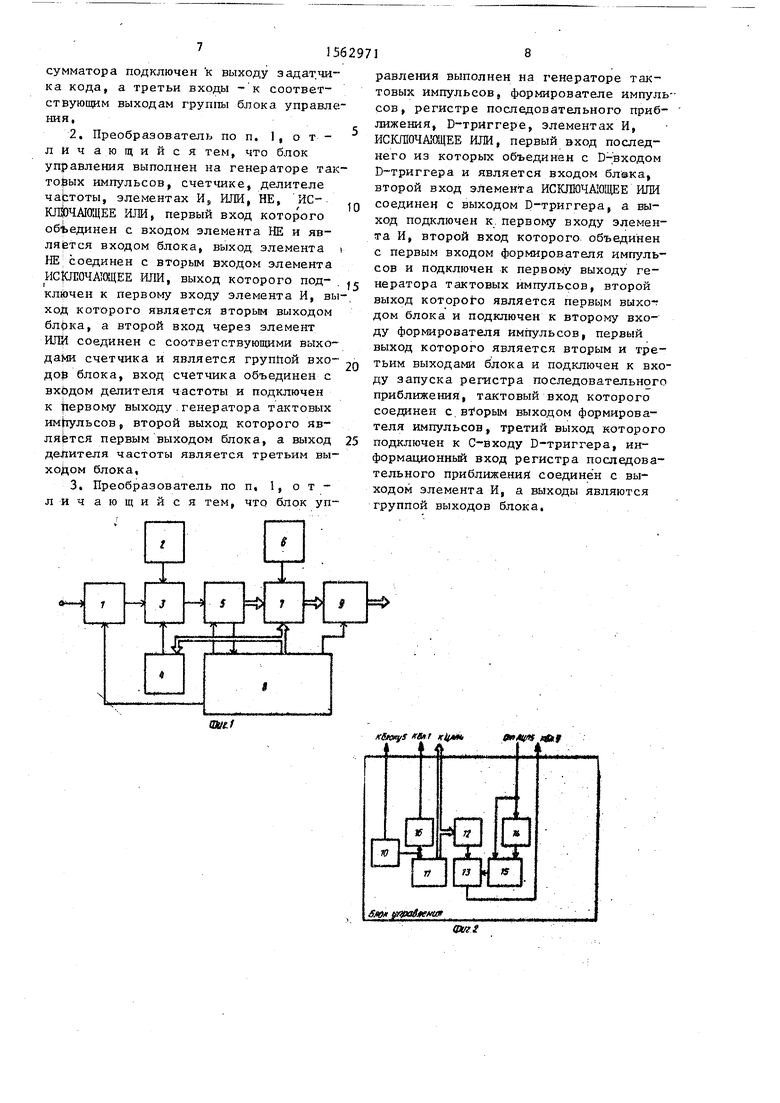

На фиг, I представлена структурная схема аналого-цифрового преобразователя; на фиг. 2 и 3 - структурные схемы вариантов выполнения блока управления; на фиг, 4 и 5 - временные диаграммы, иллюстрирующие работу устройства по первому и второму вариантам соответственно (А - сигнал на выходе аналогового сумматора, Б - сигнал на выходе схемы выборки и хранения).

Аналого-цифровой преобразователь (фиг, 1) содержит блок 1 выборки и хранения, источник 2 напряжения смещения, аналоговый сумматор 3, цифроаналоговый преобразователь (ЦА11) 4, параллельный аналого-цифровой преобразователь (АЦП) 5, вадатчик 6 кода, цифровой сумматор 7, блок 8 управления, регистр 9.

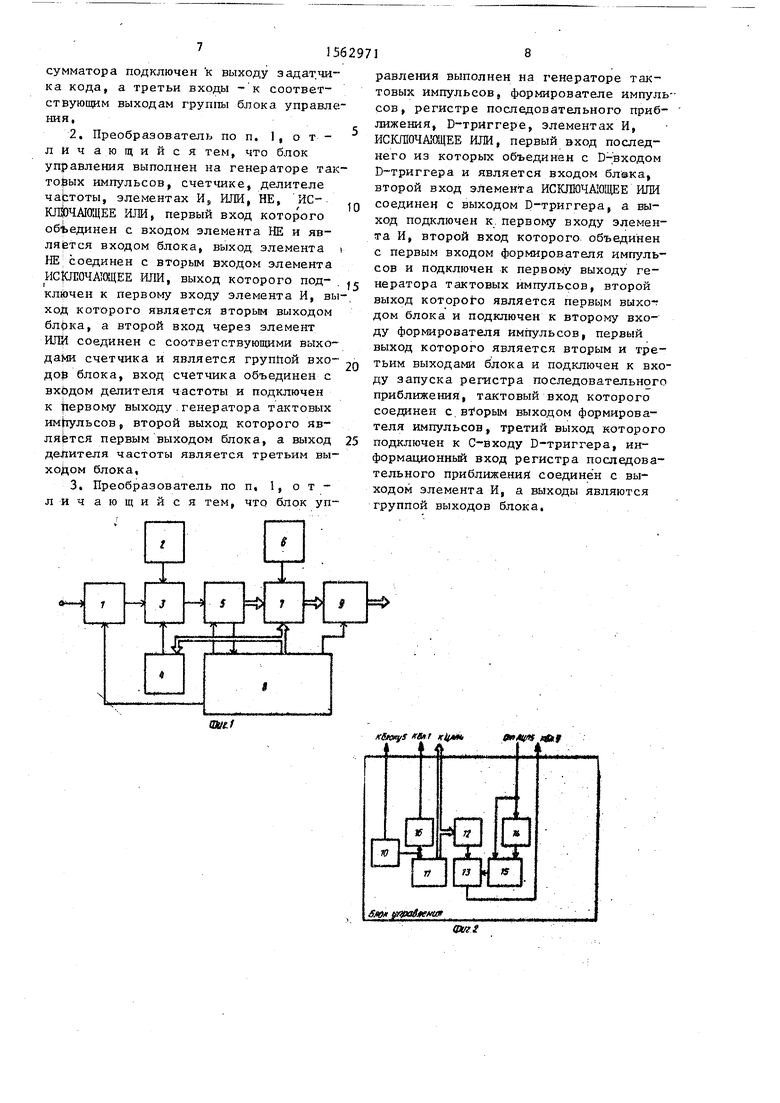

Бл Ж 8 управления (фиг, 2) содержит ieneparop 10 тактовых импульсов, счетчик 11, элемент ИЛИ 12, элемент И 13, элемент НЕ 14, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, делитель 16 частоты.

Блок 8 управления (фиг. 3) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17, генератор 18 тактовых импульсов, формирователь 19 импульсов, регистр 20 последовательного приближения, элемент И 21 , Р-триггер 22.

Устройство (фш. 1, 2 и 4) работает следующим ofip.rsoM (работа для наглядности ишиоетрируеггя для случая увеличения pa ipoiiunoiueii способности на два ра рид,1) ,

Тегнчш ш.чпг.ип i и гнал дискретнзи- рурт (. я в (шок г i ныПоркп и хранения

(Л

ел

о

ГС

;о

Ki

момент времени, соответствующие .импульсам (фиг, 46) с выхода делителя/ 16 частоты, до вида (фиг. 4а, сигнал В) и пбступает на вход аналогового сумматора 3, в котором к ним добавляются сигнал постоянного напряжения с выхода источника 2 напряжения смещения величиной .,, где U., - величина кванта, параллельного АЦП 5, . ft сигнал с выхода ЦАП 4, представляющий ступенчато-нарастающее напряжение равное О, U2, 2U2 3U2 в тактах О, 1, 2, 3 соответственно. Сигнал на выходе аналогового сумматора 3 прини- мазт вид (фиг1, 4а, сигнал А), Интер- ва-i времени от такта 0 дй такта 3 является циклам квантования телевизионного сигнала, В тактах О, 1, 2, 3 по сигналу с выхода генератора 10 такто- J вых импульсов ЧФиг, 4г) производится стробирование параллельного АЦП 5, m-разрядмый выходной код которого сов- местно с N-разрядным выходным кодом счетчика 11 поступают на цифровой cyM-j матор 7 который выполняет операцию вычитания из первого кода второго и кода задатчика 6, соответствующего напряжению Uj., Операция вычитания кода задатчика 6 осуществляется по цепи у заем младшего разряда цифрового сумматора 7, При этом эадатчик 6 кода является источником логической едини- цы.

В результате вычитания на выходе cv siaTOpa 7 происходит повышение разрядности результата,

Например, , , Код с выхода АЦП 5 011111 в такте 0 и 100000 в тактах 1, 2, 3 (фиг, 4и) код со счетчи- 4 ка 00, 01, 10, 11 в тактах О, 1, 2, 3 (фиг. 4а) на выходе цифрового сумматора 7 получают в такте ОJ011111

„01.

01111011

в такте 1100000

10

такте 2

такте 3

01111101 100000 11

оТТТТТоо

100000 00

оТТТТооо

Истинное значение результата квантования получается в такте 1 (фиг, 4и) в момент изменения состояния младше-Q j .

Q45

50

5э

го разряда АЦП 5 при нарастающем характере изменения выходного сигнала ЦАП 4..

Суть повышения разрядности в TOW, что последовательно увеличивая значение выборки ступенями на величину И j в каждом такте добиваются изменения I кода младшего разряда АЦП 5, т.е. взвешивают известным числом ступеней Иг недостающее до целого числа |квантов значение выборки телевизионного сигнала.

Элементы НЕ 14, ИСКЛЮЧАЮЩЕЕ ИШ 15,. ИЛИ 12 и И 13 формируют строб, соответствующий истинному значению результата квантования и записываемому это значение в регистр 9, при этом элемент НЕ 14 инвертирует и задерживает в результате ограниченного быстродействия сигнал с выхода младшего разряда АЦП 5 (фиг, 4д), На входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 таким образом существуют два противофазных задержанных один относительно другого сигнала. Что на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 будут формироваться короткие импульсы (фиг, 4е) при изменении сиг- нала на выходе младшего разряда АЦП 5, В элементе ИЛИ 12 формируется сигнал логической единицы в каждом так- те, кроме нулевого (фиг. 4ж), Совпаг- Дение выходных сигналов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и элемента ИЛИ 12 формирует на выходе элемента И 13 строб записи (фиг, 4э) в регистр 9.

Восстановление частоты изменения выходного кода АЦП (выравнивание по времени) может производиться за счет вторичной перезаписи кода с выхода регистра 9 в дополнительный регистр, который для этого должен быть включен на выходе регистра в момент времени дискретизации (фиг. 46) телевизионного сигнала,

Для более четкой работы генератор 10 тактовых импульсов вырабатывает две последовательности тактовых импульсов, (фиг, 4в, г). Делитель 16 частоты пропускает каждый 1/2 N входной импульс, формируя цикл квантования.

Аналого-цифровой преобразователь (фиг. 1, 3 и 5) работает следующим образом.

Телевизионный сигнал дискретизиру- ется в блоке 1 выборки и хранения в моменты времени, соответствующие импульсам (фиг. 56) с второго выхода

51562

формирователя 19 импульсов. Аналоговый сумматор 3 добавляет к значениям выборок телевизионного сигнала постоянное напряжение величиной U, и напряжение с выхода ДАЛ 4, представляющее собой ступенчато-изме шющийся сигнал, равный

О в такте 0;

2Uj в такте j

3U 2 в такте 2, если не произошло изменение состояния младшего разряда параллельного АЦП 5, или И , если было такое изменение.

Управляющий код для ЦАП 4 вырабаты вает регистр последовательного приближения 20 совместно с блоками 17, 18,

19,21 и 22 в соотзетствии с алгоритмом поразрядного уравновешивания,

В результате, выходной сигнал аналогового сумматора 3 принимает вид (фиг, 5а, сигнал А). Интервал времени включающий такты 0, 1,2 является и циклом квантования телевизионного сигнала,

В тактах О, 1, 2 по сигналу - (фиг. 5г) с выхода генератора 18 тактовых импульсов производится стро- бировазше параллельного АЦП 5, ш-раз- рядный выходной код которого совместно с N-разрядным выходным кодом РШ1 20 подаются на цифровой сумматор 7,

Истинное значение результата квантования получается всегда в одном и том же такте 2 и записывается в регистр 9 по сигналу (фиг, 56) с второго выхода формирователя 19 импульсов,

В конце цикла квантования по сигналу (фиг, 56) с выхода формирователя 19 импульсов происходит обнуление РГШ

20,В такте 0 по сигналу (фиг, 5е) с выхода формирователя 19 импульсов происходит запись состояния младшего разряда параллельно АЦП 5 в D-триггер 22

0

0

5

5

5

0

ход элемента И 21 проходит импульс (фиг. 5к), в результате чего в РГШ 20 происходит обнуление триггера старшего разряда. При противоположном состоянии выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17 этого обнуления не происходит.

Кроме того, по сигналу (фиг, 5д) с выхода формирователя 19 импульсов происходит установка в 1 триггера младшего разряда РПП 20. Сформированный таким образом код разрядностью N с Р1Ш 20 поступает на цифровой сумматор 7,

Формирователь 19 импульсов полностью описывается диаграммой состояний входов и выходов (фиг, 5в, ч, б, г, д). Формирователь 19 импульсов наряду с формированием сигналов, необходимых для работы РПП 20, формирует сигнал (фиг, 5е) записи в D-триг- гер 22,

Формула изобретения

1, Аналого-цифровой преобразователь, содержащий аналоговый сумматор, первый вход которого соединен с выходом цифроаналогового преобразовате- 0 ля, а выход подключен к информационному входу параллельного аналого-цифрового преобразователя, управляющий - вход которого подключен к первому выходу блока управления, а цифровые выходы - к первым входам цифрового сумматора, выход которого соединен с информационным входом регистра, управляющий вход которого подключен к второму выходу блока управления, выход является выходной шиной, а группа выходов блока управления подключена к соответствующим входам цифроаналого- вого преобразователя, отлич а ю щ и и с я тем, что, с целью повыше

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1658380A2 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Многоканальный аналого-цифровой преобразователь | 2023 |

|

RU2815253C1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1320901A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

Изобретение относится к технике телевидения. В аналого-цифровой преобразователь, содержащий параллельный АЦП, цифровой сумматор, регистр, генератор тактовых импульсов, счетчик, ЦАП, аналоговый сумматор, блок выборки и хранения, введены делитель частоты, задатчик кода, источник напряжения смещения, регистр последовательного приближения. Это позволяет сократить аппаратурную избыточность сверхбыстродействующих АЦП при повышении разрядности квантования ТВ сигнала, упростить требования к плотности упаковки и потребляемой мощности при создании СБИС кодека цифровой обработки ТВ сигнала. 2 з.п. ф-лы, 5 ил.

и по сигналу (фиг, 5д) с выхода форми 45 ння разрешающей способности, быстро- рователя 19 импульсов происходит уста- действия и упрощения преобразователя, новка в состояние i триггера старшего разряда РПП 20,

В такте 1 выходной сигнал D-тригге- ра 22 (фиг, 5и) и выходной сигнал мпад50 вторым входом аналогового сумматора,

в него введен блок выборки и хранения, задатчик кода, источник напряжения смещения, выход которого соединен с

шего раз ряда, параллельно го АЦП 5, анализируются элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 17, выходной сигнал (фиг, 5к) которого равен логической единице, если произошло изменение младшего разряда параллельно АЦП 5 относительно его состояния в такте 0, Далее, если сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17 равен логической единице, то на выння разрешающей способности, быстро- действия и упрощения преобразователя,

вторым входом аналогового сумматора,

в него введен блок выборки и хранения, задатчик кода, источник напряжения смещения, выход которого соединен с

третии вход которого соединен с выходом блока выборки и хранения, информационный вход которого является входной шиной, а управляющий вход подключен к третьему выходу блока управления, вход которого соединен с выходом младшего разряда параллельного аналого-цифрового преобразователя, при этом второй вход цифрового

115

сумматора подключен к выходу задатчи- ка кода, а третьи входы - к соответствующим выходам группы блока управления,

НЕ соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому входу элемента И, выход которого является вторым выходом блока, а второй вход через элемент ИЛИ соединен с соответствующими выходами счетчика и является группой входов блока, вход счетчика объединен с входом делителя частоты и подключен к первому выходу генератора тактовых HMtryvnbcoB, второй выход которого является первым выходом блока, а выход делителя частоты является третьим выходом блока,

3,Преобразователь по п, 1, о т - лич ающийся тем, что блок уп

ОЭД/

8

равления выполнен на генераторе тактовых импульсов, формирователе импульсов, регистре последовательного приближения, D-трИггере, элементах И, ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход последнего из которых объединен с D-входом D-триггера и является входом блэка, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом D-триггера, а выход подключен к первому входу элемента И, второй вход которого объединен с первым входом формирователя импульсов и подключен к первому выходу генератора тактовых импульсов, второй выход которого является первым выходом блока и подключен к второму входу формирователя импульсов, первый выход которого является вторым и третьим выходами блока и подключен к входу запуска регистра последовательного приближения, тактовый вход которого соединен с вторым выходом формирователя импульсов, третий выход которого подключен к С-входу D-триггера, информационный вход регистра последовательного приближений соединён с выходом элемента И, а выходы являются группой выходов блока.

XSHHtj/S Xty

Фиг. з

1562971

JL

| Журнал Электроника, 1980, № 20, с | |||

| Экономайзер | 0 |

|

SU94A1 |

| Авторское свидетельство СССР № 1188990, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-07—Публикация

1986-05-28—Подача