1

(21)4416525/24-24

(22)26.04.88

(46) 07.11.89.БЮЛ. № 41

(71)Рижский политехнический институт им.А.Я.Пельше

(72)Г.Н.Котович, И.О.Флейшман и И.М.Малашонок

(53)621.395.34 (088.8)

(56)Авторское свидетельство СССР № 1021017, кл. Н 04 М 3/56, 1981.

Авторское свидетельство СССР № 1297229, кл. Н 03 М 3/02, 1985.

(54)КОММУТАТОР

(57)Изобретение относится к вычислительной технике и технике связи. Его использование в системах приоритетной

конфереицсвязи с дельта-модуляцией позволяет повысить помехоустойчивость коммутатора, который содержит распределитель 1 импульсов, группу элементов И 2, регистр 4 сдвига, двоичные счетчики 8,9, триггер 10, элементы И 11-13, элемент-ИЛИ 17 и дешифраторы 21,22. Благодаря введению реверсивного счетчика 3, элемента ИСКЛЮЧАЮЩЕЕ ИЖ 5, элементов НЕ 6, 7, элементов И 14-16, элементов ИЛИ 18-20, дешифратора 23, цифровых компараторов 24,25 и источников 26, 27 постоянного кода в коммутаторе обеспечивается безошибочное и устойчивое занятие канала активным абонентом . 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство конференц-связи с дельта-модуляцией | 1989 |

|

SU1660202A1 |

| Коммутатор | 1985 |

|

SU1297229A1 |

| Устройство измерения длительности импульсных сигналов | 1986 |

|

SU1476405A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Система передачи цифровой информации | 1987 |

|

SU1518911A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах приоритетной конференцсвязи с дельта-модуляцией позволяет повысить помехоустойчивость коммутатора, который содержит распределитель 1 импульсов, группу элементов И 2, регистр 4 сдвига, двоичные счетчики 8,9, триггер 10, элементы И 11-13, элемент ИЛИ 17 и дешифраторы 21, 22. Благодаря введению реверсивного счетчика 3, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элементов НЕ 6,7, элементов И 14-16, элементов ИЛИ 18-20, дешифратора 23, цифровых компараторов 24,25 и источников 26,27 постоянного кода в коммутаторе обеспечивается безошибочное и устойчивое занятие канала активным абонентом. 3 ил.

л

5Д

05

фдг

Изобретение относится к вычислительной технике и технике связи и может использоваться в системах приоритетной конференцсвязи с дельта- модуляцией (ДМ) .

Цель изобретения - повышение помехоустойчивости коммутатора.

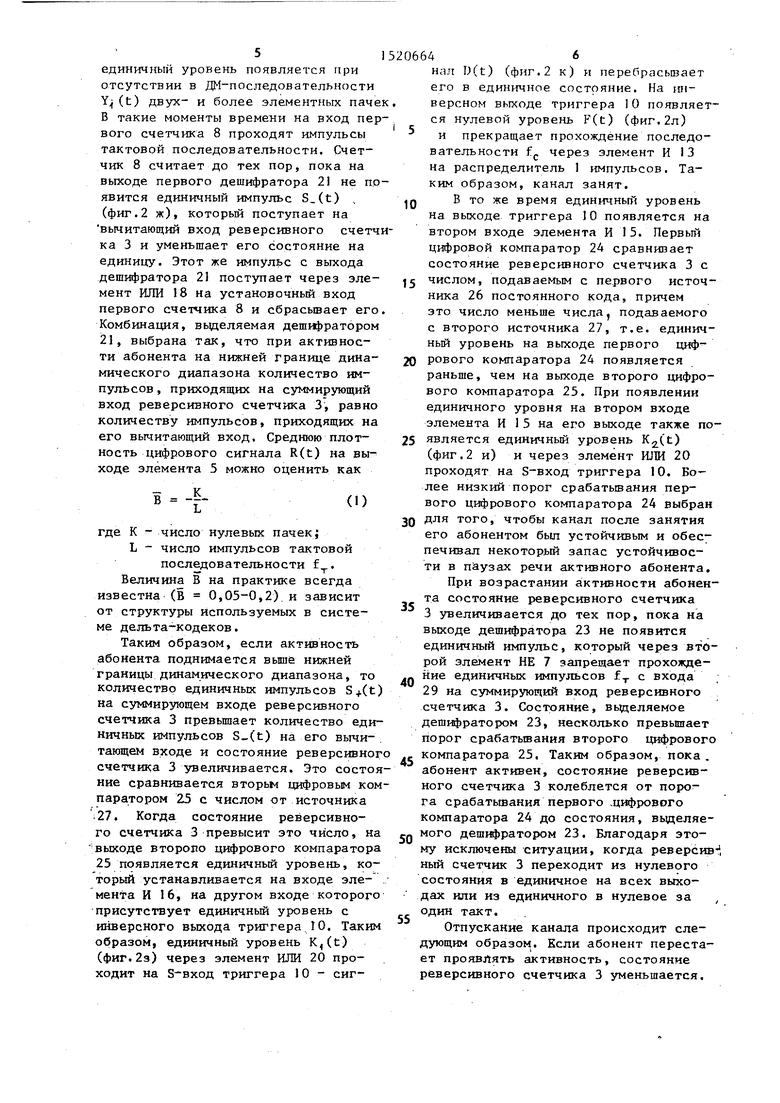

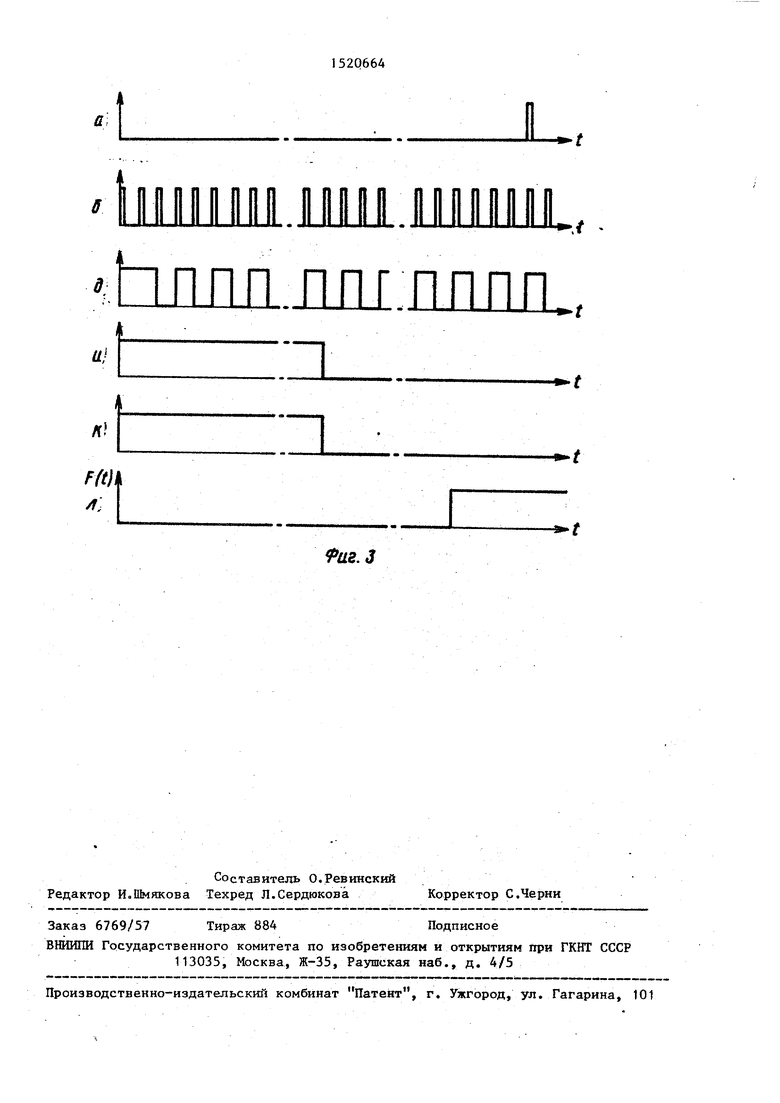

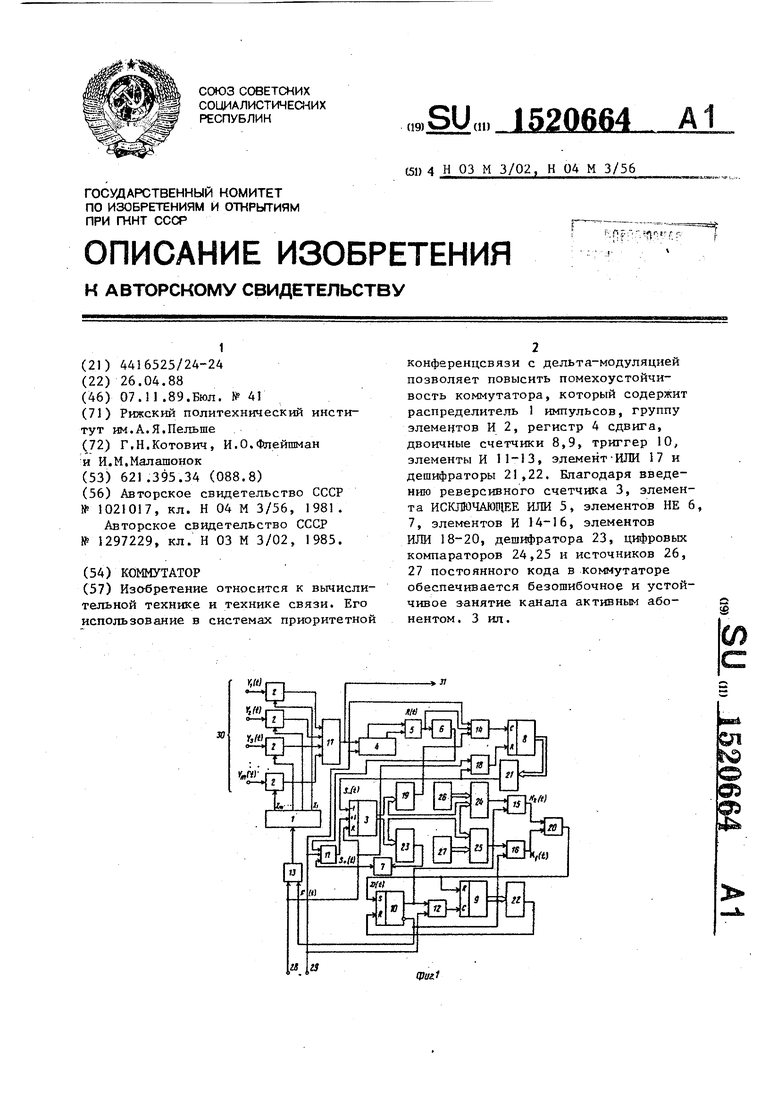

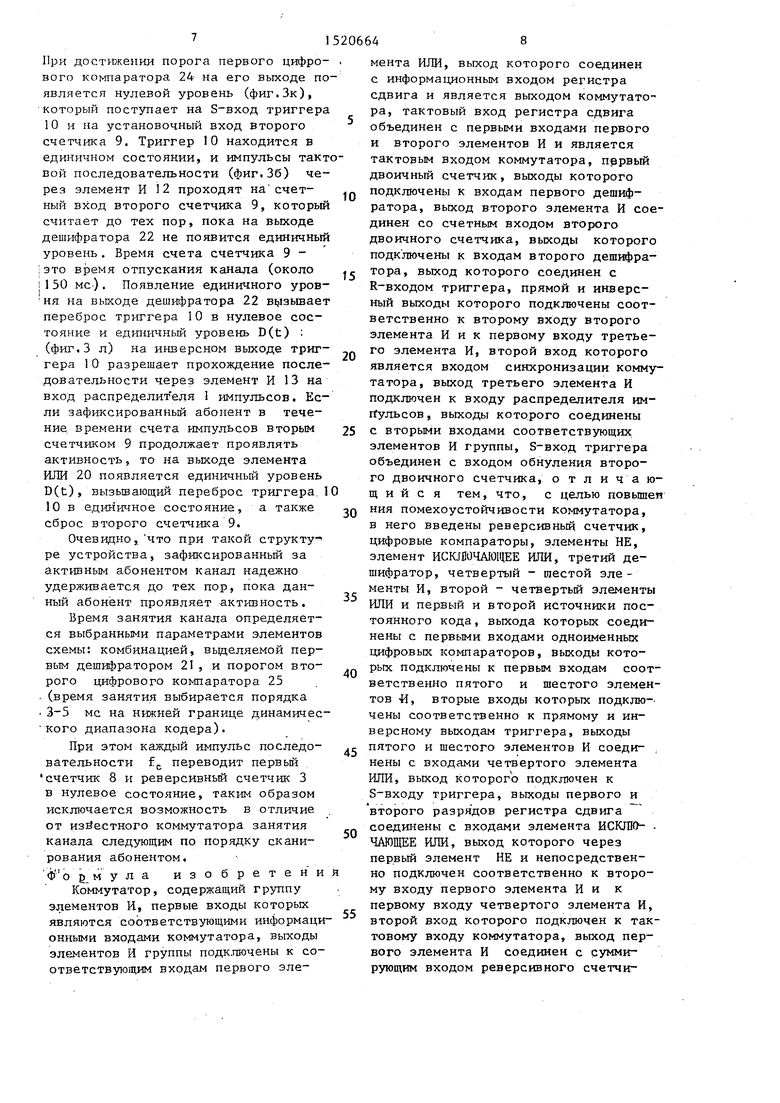

На фш.1 приведена функциональная схема коммутатора; на фиг.2 и 3 - временные диаграммы работы коммутатора.

Коммутатор содержит распредели-- тель 1 импульсов, группу элементов И 2, реверсивный счётчик 3, регистр 4 сдвига, элемент ИСКЛОЧА10ЩЕЕ ИЛИ 5, первый 6 и второй 7 элементы НЕ, первый 8 и второй 9 двоичные счетчики, триггер 10, первый - шестой элементы И 11-16, первый - четвертый элементы ИЛИ 17-20, первый - третий дешифраторы 21 - 23, первьй 24 и второй 25 цифровые компараторы и первый 26 и второй 27 источники постоянного кода, которые могут быть реализованы, например, на ПЗУ. На фиг.1 обозначены вход 28 синхрониза ции, тактовый вход 29, информационные входы 30 и вькод 31.

На фиг.2 и 3 обозначены: а - последовательность импульсов с частотой f иа входе распределителя 1; б - последовательность тактовых импульсов с частотой f иа входе 29} в,г - сигналы Xi , К2. на выходах распределителя 1; д - ДМ-поиледователь- ность Y;(t) на выходе 31; е - сигнал S(t) на выходе первого элемента И П (на суммирующем входе; счетчика 3)j ,ж - сигнал S (t) на выходе первого дешифратора 21 (на вы-х читающем входе счетчика 3); з,и - сигналы K,(t) и K(t) на выходах соответственно шестого 16 и пятого 15 элементов И; к - сигнал D(t). на вьгходе четвертого элемента ИЛИ 20 , (на S-входе триггера 10); л - сиг нал на инверсном выходе триггера 10

Коммутатор работает следзтащим образо м.

ДМ-сигналы Y,(t)-Y(t) с выходов кодеров абонентов поступают на входы 30 и через элементы И 2 по очереди поступают на выход первого элемента ИЛИ 17, а с него - на инфор мационный вход регистра 4, В случае когда все абоненты пассивны, сигналы У (t)-Y (t) представляют собой последовательность импульсов вида

...101010..., которые, записавшись в регистр 4, не вызывают изменения сигнала на выходе элемента ИСКЛ10ЧАЮЩЕЕ ИЛИ 5. Реверсивный счетчик 3 находится в нулевом состоянии, на выходе элемента ИЛИ 19 нулевой потеН1да- ал, который запрещает работу первого счетчика 8.

В этом режиме триггер 10 находится в нулевом состоянии и единичный логический потенциал F(t) (фиг.2 л) на его инверсном выходе не препятствует прохождению импульсов с тактового

входа 29 через элемент И.13 на вход распределителя 1 импульсов. Импульсы последовательности с(фиг.2), поступая на вход распределителя 1, вызывают поочередное появление единичных

(разрешающих) сигналов Х, на его выходах в любом установленном порядке по циклу.

При проявлении каким-либо абонен - том активности в ДМ-последовательнести Y;(t) (фиг.2 д) появляются двух- и более элементные пачки, что вызьшает появление единичных импульсов на выходе первого элемента НЕ 6.

Эти импульсы поступают на вход i элемента И 11, на другой вход которого постзтает тактовая последовательность (фиг.26). На третий вход элемента И 11 через второй элемент

НЕ 7 подключен выход дешифратора 23, который вьщеляет определенную комбинацию на вьгяоде реверсивного счетчика 3. Пока такая комбинация не появилась,,на выходе дешифратора

23 - логический О, а на третьем

входе элемента И П - логическая J. Таким образом, в моменты появления двух- и более элементных пачек в да-последовательности Y/(t) единичные импульсы S (t) (фиг.2 е) поступают на суммирующий вход реверсивного сШетчика 3 и увеличивают еро состояние oj-olioe становится отличным от нулевого. Это приводит .к

тому, что на выходе элемента ШШ 19 появляется единичный уровень, который сохраняется, пока состояние реверсивного счетчика 3 отлично от нулевого. Единичный уровень на выходе элемента ИЛИ 19 определяет, единичный уровень на одном из входов элемента И 14, на другой вход которого заведен сигнал R(t) с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, где

едиргичный уровень появляется при отсутствии в ДМ-последовательности Y(t) двух- и более элементных пачек В такие моменты времени на вход первого счетчика 8 проходят импульсы тактовой последовательности. Счетчик 8 считает до тех пор, пока на выходе первого дешифратора 21 не появится единичный импульс S(t) , (фиг.2 ж), который поступает на вычитающий вход реверсивного счетчика 3 и уменьшает его состояние на единицу. Этот же импульс с выхода дешифратора 21 поступает через эле- мент ИЛИ 18 на установочный вход первого счетчика 8 и сбрасьтает его. Комбинация, вьщеляемая дешифратором 21, выбрана так, что при активности абонента на нижней границе дина- мического диапазона количество импульсов , приходящих на суммирующий вход реверсивного счетчика 3, равно количеству импульсов, приходящих на его вычитающий вход. Среднюю плот- ность цифрового сигнала R(t) на выходе элемента 5 можно оценить как

- -5- L

(1)

где К - число нулевых пачек;

L - число импульсов тактовой последовательности f.

Величина В на практике всегда известна (В 0,05-0,2) и зависит от структуры используемых в системе дельта-кодеков,

Таким образом, если активность абонента поднимается выше нижней границы динамического диапазона, то количество единичных импульсов S.(t) на суммирующем входе реверсивного счетчика 3 превьш1ает количество еди- ничньгх: импульсов S(t) на его вычи- . тающем входе и состояние реверсивног счетчика 3 увеличивается. Это состояние сравнивается вторьм цифровым компаратором 25 с числом от источника .27. Когда состояние реверсивного счетчика 3 превысит это число, на выходе второро цифрового компаратора 25 появляется единичный уровень, который устанавливается на входе эле- мента И 16, на другом входе которого присутствует единичный уровень с инверсного выхода триггера 10, Таким образом, единичный уровень K,(t) (фиг,2з) через элемент ИЛИ 20 проходит на S-вход триггера 10 - сиг

Q r 0 5

0

5

п

5

нал D(t) (фиг.2 к) и перебрасывает его в единичное состояние. На ini- нерсном выходе триггера 10 появляется нулевой уровень P4t) (фиг. 2л)

и прекращает прохождение последовательности fp через элемент И 13 на распределитель 1 импульсов. Таким образом, канал занят,

В то же время единичньй уровень на выходе триггера 10 появляется на втором входе элемента И 15, Первьй цифровой компаратор 24 сравнивает состояние реверсивного счетчика 3 с числом, подаваемым с первого источника 26 постоянного кода, причем это число меньше числа, подаваемого с второго источника 27, т.е. единич- ньй уровень на выходе первого цифрового компаратора 24 появляется раньше, чем на выходе второго цифрового компаратора 25, При появлении единичного уровня на втором входе элемента И 15 на его вькоде также появляется единичньй уровень K2(t) (фиг. 2 и) и через элемент ШЖ 20 проходят на S-вход триггера 10, Более низкий порог срабатьшания первого цифрового компаратора 24 выбран для того, чтобы канал после занятия его абонентом был устойчивым и обеспечивал некоторый запас устойчивости в паузах речи активного абонента.

При возрастании активности абонента состояние реверсивного счетчика 3 увеличивается до тех пор, пока на выходе дешифратора 23 не появится единичный импульс, который через второй элемент НЕ 7 запрещает прохождение единичных импульсов f,- с входа 29 на суммирующий вход реверсивного счетчика 3, Состояние, вь еляемое дешифратором 23, несколько превышает порог срабатьшания второго цифрового компаратора 25. Таким образом, пока, абонент активен, состояние реверсивного счетчика 3 колеблется от порога срабатьшания первого .цифрового компаратора 24 до состояния, вьщеляе- мого дешифратором 23, Благодаря этому исключены ситуации, когда реверсив , ный счетчик 3 переходит из нулевого состояния в единичное на всех выходах или из единичного в нулевое за , один такт,

Отпускание канала происходит следующим образом. Если абонент перестает проявлять активность, состояние реверсивного счетчика 3 уменьшается.

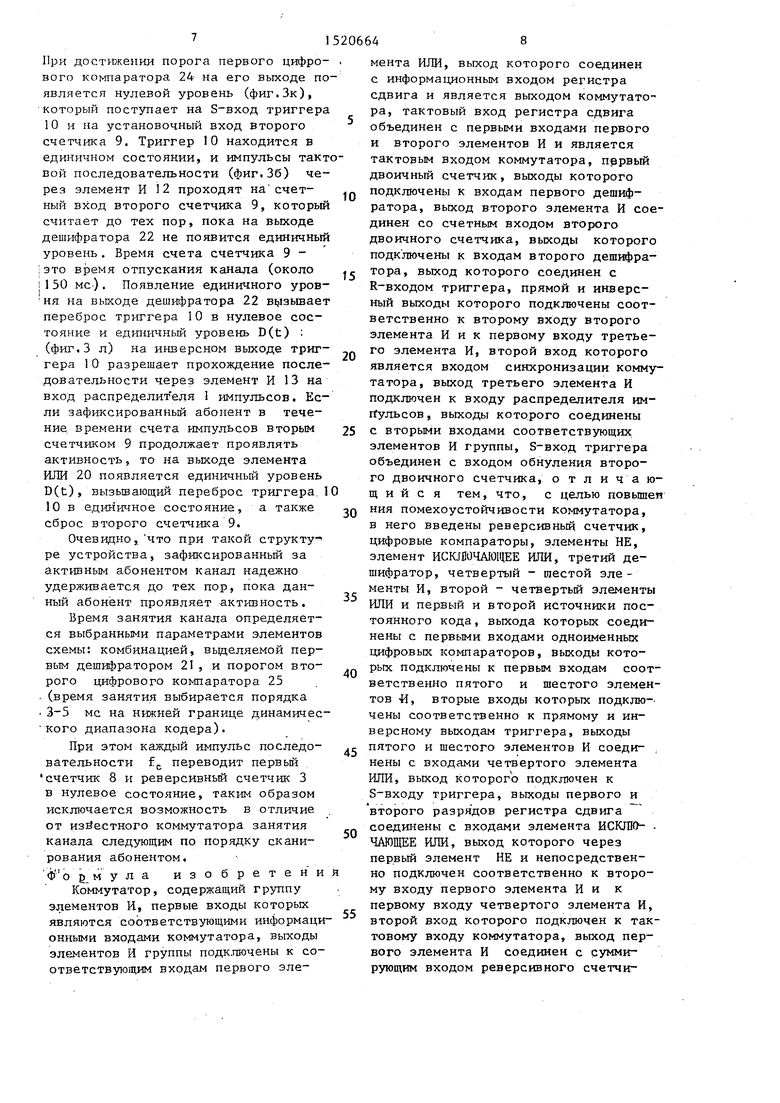

При достюкении порога первого цифро- вого компаратора 24 на его выходе появляется нулевой уровень (фиг.Зк), который поступает на S-вход триггера 10 и на установочный вход второго счетч1-п :а 9, Триггер 10 находится в единичном состоянии, и импульсы тактвой последовательности (фиг.36) через элемент И 12 проходят на счетный вход второго счетчика 9, который считает до тех пор, пока на выходе дешифратора 22 не появится единичный уровень , Время счета счетчика 9 - i это BJaeMK отпускания канала (около j 1 50 МС-). Появление единичного уров- ня на выходе дешифратора 22 вузьтает переброс триггера 10 в нулевое состояние и единичньш уровень D(t) : (фиг.З л) на инверсном выходе триггера IО разрешает прохождение последовательности через элемент И 13 на вход распределителя 1 импульсов. Если зафиксированный абонент в течение времени счета импульсов вторым счетчиком 9 продолжает проявлять активность, то на выходе элемента ИЛИ 20 появляется единичный уровень D(t), вызьшающий переброс триггера. 10 в единичное состояние, а также сброс второго счетчика 9.

0ч ев ид но з( что при такой структур ре устройства, зафиксированный за активным абонентом канал надежно удерживается до тех пор, пока данный абонент проявляет активность.

Время занятия канала определяется выбранными параметрами элементов схемы: комбинадней, вьщеляемой первым дешифратором 21, и порогом второго цифрового компаратора 25 .(время занятия выбирается порядка . 3-5 мс на нижней границе динамичес кого диапазона кодера).

При этом каждый импульс последовательности f(, переводит первый счетчик 8 и реверсивный счетчик 3 в нулевое состояние, таким образом исключается возможность в отличие от известного коммутатора занятия канала следующим по порядку сканирования абонентом, рмула изобретени

Коммутатор, содержащий группу элементов И, первые входы которых являются соответствующими информационными входами коммутатора, выходы элементов И группы подк.шочены к соответствующим входам первого эле

мента ИЛИ, выход которого соединен с информационным входом регистра сдвига и является выходом коммутато- ра, тактовый вход регистра сдвига объединен с первыми входами первого и второго элементов И и является тактовым входом коммутатора, пррвый двоичный счетчик, выходы которого подключены к входам первого дешифратора, выход второго элемента И соединен со счетным входом второго двоичного счетчика, выходы которого подк лючены к входам второго дешифратора, выход которого соединен с R-входом триггера, прямой и инверсный выходы которого подключены соответственно к второму входу второго элемента И и к первому входу третьего элемента И, второй вход которого является входом синхронизации коммутатора, выход третьего элемента И подключен к входу распределителя им- Лульсов, выходы которого соединены с вторыми входами соответствующих элементов И группы, S-вход триггера объединен с входом обнуления второго двоичного счетчика, о т л и ч а ю щ и и с я тем, что, с целью повьппе ния помехоустойчивости коммутатора, в него введены реверсивньй счетчик, цифровые компараторы, элементы НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий дешифратор, четвертый - шестой элементы И, второй - четвертьй элементы ИЛИ и первый и второй источники постоянного кода, выхода которьк соединены с первыми входами одноименных цифровых компараторов, выходы которых подключены к первым входам соответственно пятого и шестого элементов -И, вторые входы которых подключены соответственно к прямому и инверсному выходам триггера, выходы пятого и шестого элементов И соединены с входами четвертого элемента ИЛИ, выход которого подключен к S-ВХОДУ триггера, вькоды первого и второго разрядов регистра сдвига соединены с входами элемента ИСКГОО- ЧАЮЩЕЕ ИЛИ, выход которого через первый элемент НЕ и непосредственно подключен соответственно к второму входу первого элемента И и к первому входу четвертого элемента И, второй вход которого подключен к тактовому входу коммутатора, выход первого элемента И соединен с суммирующим входом реверсивного счетчика, вход обнуления которого объедине с первым входом второго элемента ИЛИ и подключен к входу синхронизации коммутатора, выходы реверс1-шного счетчика соединены с вторыми входами цифровых компараторов и с входами третьих дешифратора и элемента ИЛИ, выходы которых соответственно чере второй элемент НЕ и непосредственно подключены к третьим

входам соответственно третьего и четвертого элементов И, выход первого дешифратора соединен с вычитаю-( щим входом реверсивного счетчика и вторым входом второго элемента ИЛИ, выход которого и выход четвертого элемента И подключены соответственно к входу обнуления и счетному входу первого двоичного счетчика.

Фиг.2

ППП ППГ ПППП,,

Ht /I

аг.З

Авторы

Даты

1989-11-07—Публикация

1988-04-26—Подача