с ех тветствующего блока формирования «аетот дискретизации,установочные .ssoflbi распределителя импульсов, «счетчика адреса, четвертого триггера йврвого и второго реверсивных счетчиков соединены с выходом элемента Ш1И, выход элемента ИЛИ-НЕ подключен к единичному входу первого триггера к единичному входу четвертого триггера, к единичному и нулевому входам пятого триггера, тактовый вход которого и первый вход третьего элемента И соединены с выходом генератора так товых импульсов, выход второго триггера подключен к первому входу четвертого элемента И, выход которого соединен со счетным входом первого реверсивного счетчика, выходы разрядов регистра номера канала соединены с адресным входом мультиплексора, информационные входы которого соединены соответственно с выходами усилителей, выход мультиплексора подключен к входу формирователя одиночных импульсов, выход которого соединен с нулевым входом второго триггера, единичный вход которого соединен с выходом предварительного запуска дешифратора команд, выходы внешнего запуска, пуска, останова и сброса которого соединены соответственно с единичным входом третьего триггера, с первьш входом элемента ИЛИ-НЕ, с нулевым, входом первого триггера и с первым уходом элемента ИЛИ, второй вход которого соединен с выходом формирователя импульса сброса, второй вход второго элемента И соединен с входом внешнего запуска системы, третий вход подключен к выходу третьего триггера, выход второго элемента И соединен с вторым входом элемента ИЛИ-НЕ, выход первого триггера соединен с входом генератора тактовых импульсов, выход одновибратора блока формирования частот дискретизации соединен с соответствующим входом коммутатора выход первого элемента НЕ подключен к соответствующему входу первого элемента И, второй вход третьего эле мента И соединен с выходом пятого триггера, третий вход третьего элемента И и вход первого элемента НЕ подключен к выходу первого элемента И-НЕ, выход второго элемента И-НЕ соединен с первым входам третьего элемента И-НЕ, второй вход которого 42 соединен с выходом четвертого триггера, выход третьего элемента И-НЕ соединен с первым входом первого элемента И-НЕ, второй вход которого, вход первого элемента .задержки и счетный вход счетчика адреса соединены с выходом переноса первого реверсивного счетчика, выход пятого элемента И соединен с тактовым входом второго реверсивного счетчика, выход шестого элемента И соединен с тактовым входом первого реверсивного счетчика, информационный вход которого и информационный вход дешифратора конца программы соединены с выходом первого запоминающего узда, выход дешифратора конца программы подключен к первому входу второго элемента И-НЕ и к входу второго элемента НЕ, выход которого соединен с вторым входом четвертого элемента И и с первым входом шестого элемента И, второй вход которого соединен с выходом первого элемента задержки, третий вход шестого элемента И, счетный вход второго реверсивного счетчика и первый вход пятого элемента И подключены к выходу третьего элемента И, второй вход пятого элемента И соединен с выходом второго элемента задержки, вход которого, третий вход четвертого элемента И, входы одновибратора и третьего элемента НЕ соединены с выходом переноса второго реверсивного счетчика, выход третьего элемента НЕ соединен с вторым входом второго элемента И-НЕ, выходы разрядов счетчика адреса тюдкпючены к адресным входам первого и второго запоминающих узлов, тактовый вход счетчика адреса, первого и второго запоминающих узлов соединены соответственно с первым, вторьм и третьим выходами распределителя импульсов, выход второго запонинакицего узла подключен к информационному входу второго реверсивного счетчика. 2, Система по п. 1, о т л и ч а ющ а я с я тем, что блок ввода про-ъ грамм содержит элементы И, ИЛИ, задержки, схемы сравнения, триггеры, регистр команд, регистр адреса и согласующие элементы, причем информационные входы с первого по шестнадцатый согласующих элементов являются входами данных, блока, выходы согласующих элементов с первого по четвертый подктаочены соответственно к ин.формационным входам регистра команд информационные входы согласующих элементов с семнадцатого по двадцать первый являются синхронизирующими входами блока, выход двадцать второго согласующего элемента является синхронизирующим выходом блока, выход двадцать третьего согласукяцего элемента соединен с информационным входом шестнадцатого согласующего элемента, вход блокировки блока соединен с разрешакндими входами согласующих элементов с пятого по шестнад цатый и двадцать первого, с первыми входами первого и второго элементов И, с входом .:блокировки регистра команд, выходы разрядов которого и выход второго элемента И являются вторым информационным выходом блока, выходы согласующих элементов с пятог по шестнадцатый являются первым информационным выходом блока, выход каждого согласующего элемента с пятого по двенадцатый соединен с первым входом соответствующей схемы сравнения,второй вход которой подключе к выходу соответствующего разряда регистра адреса, первый вход третьего элемента И соединен с выходом двадцать первого согласующего элемента, входы, начиная с второго, третьего элемента И, соединены соответственно с выходами схем сравнения вьпсод третьего элемента И соединен с 1 2 единичным входом первого триггера, выход которого подключен к второму входу второго элемента И, к разрешающему входу двадцать второго согласующего элемента и к первьм входам четвертого и пятого элементов И, второй вход первого элемента И является разрешающим входом блока, выход подключен к единичному входу второго триггера, информационный и разрешающий входы двадцать третьего согласующего элемента соединены соответственно с выходами четвертого элемента И и второго триггера, тактовый вход которого подключен к выходу четвертого элемента И, установочные входы первого и второго триггеров и регистра команд подключены к выходу восемнадцатого согласующего элемента, выход двадцатого согласующего элемента соединен с вторым четвертого элемента И и с первьм входом элемента ИЛИ, второй вход которого и третий вход второго элемента И подключены к выходу девятнадцатого согласующего элемента, выход элемента ИЛИ соединен с вторым входом пятого элемента И, выход которого через элемент задержки соединен с информационным входом двадцать второго согласующего элемента, тактовые входы первого триггера и регистра команд соединены с выходом семнадцатого согласующего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1990 |

|

SU1781625A1 |

| Многоканальное устройство для регистрации и индикации мгновенных значений сигналов | 1985 |

|

SU1312391A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1560980A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

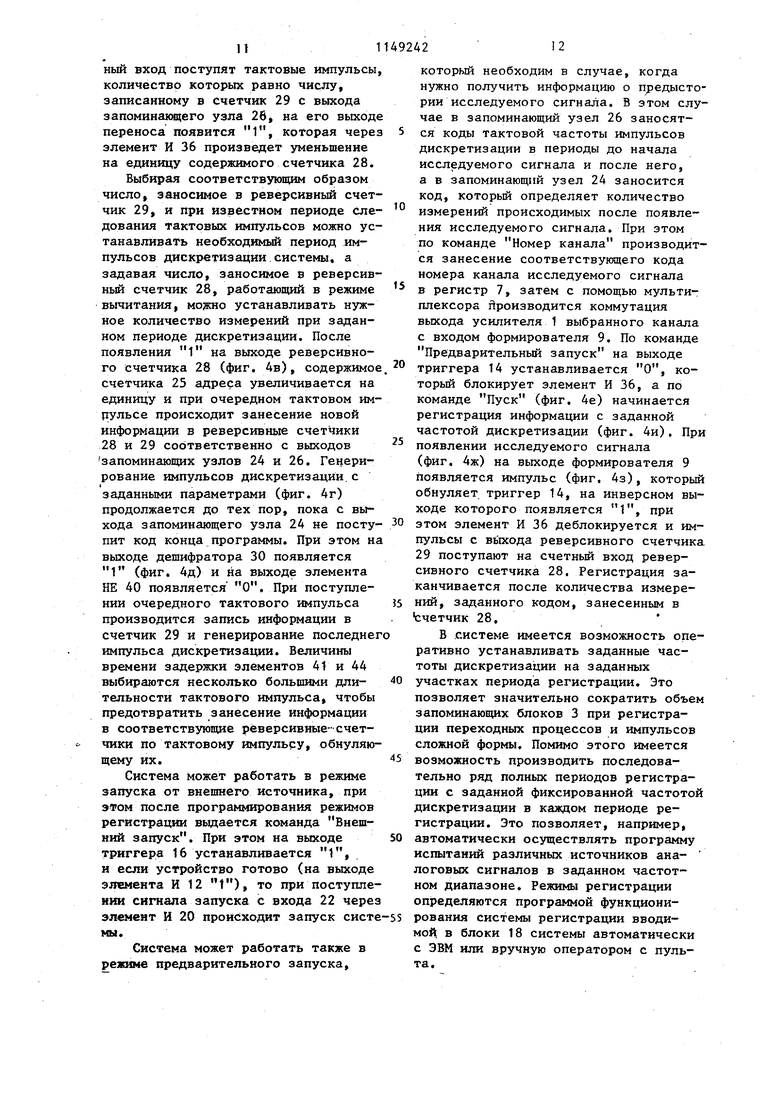

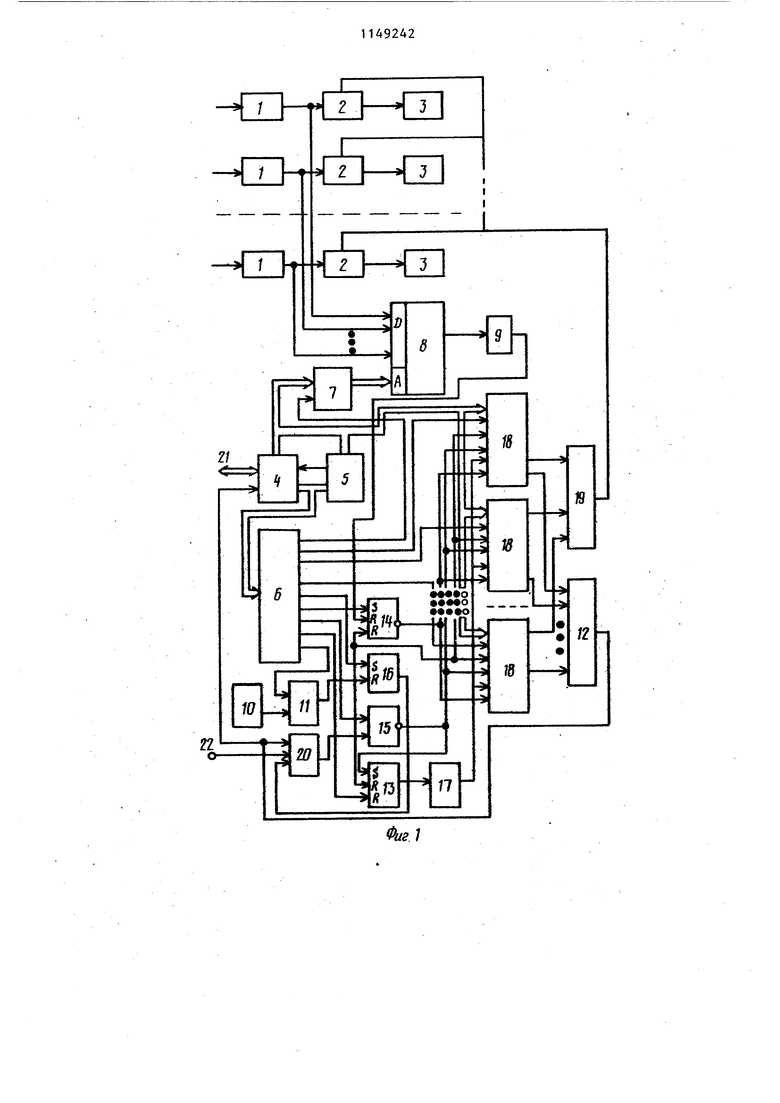

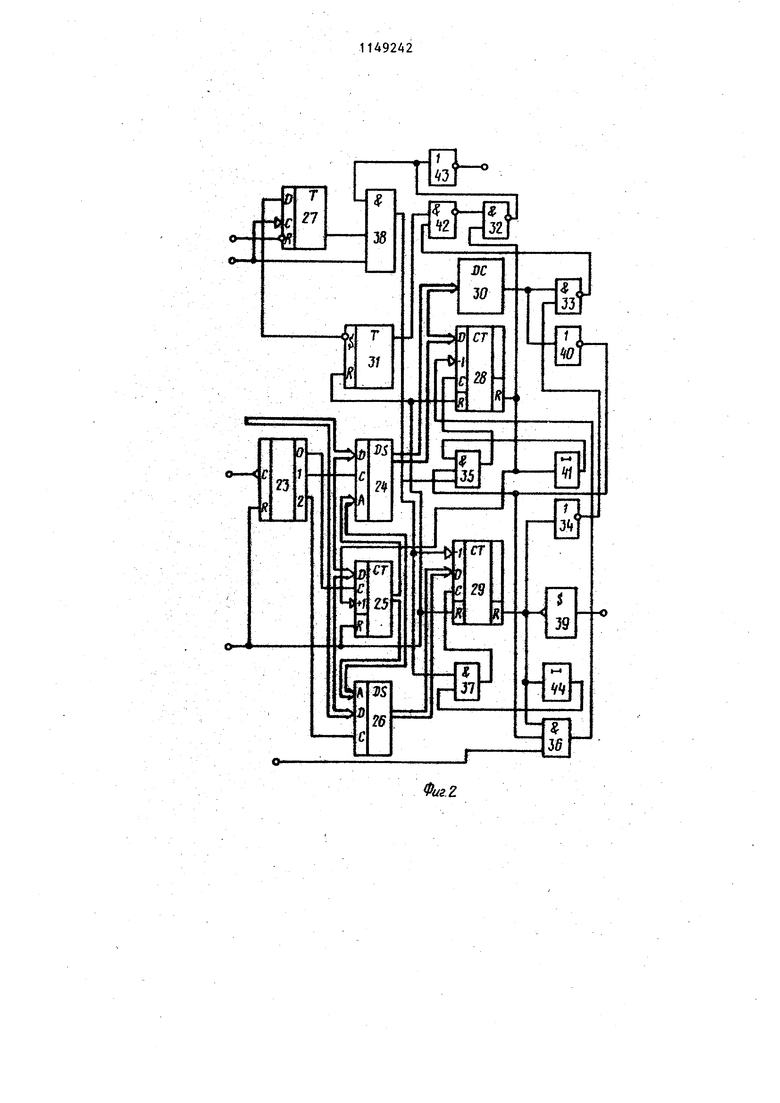

1. МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ АНАЛИЗА ФОРМЫ И РЕГИСТРАЦИИ АНАЛОГОВЫХ ПРОЦЕССОВ, содержащая в каждом канале усилитель, выход которого подключен к информационному входу аналого-цифрового преобразователя, выход которого соединен с входом запоминающего блока, входы усилителей являются информационньв4и входами системы, вход запуска каждого аналогоцифрового преобразователя соединен с выходом коммутатора, отличающаяся тем, что, с целью расширения ее функциональных возможностей путем оперативного установления частот дискретизации на заданных участках периода регистрации и повышения производительности, в нее введены блок ввода программ, блок задания режимов, дешифратор команд, формирователь импульса сброса, мультиплексор, регистр номера канала, формирователь одиночных импульсов, элемент ИЛИ, первый, второй и третий триггеры, первьй и второй элементы И, элемент ИЛИ-НЕ, генератор тактовых импульсов и блоки формирования частот дискретизации, каждый из которых имеет первый и второй запоминающие узлы, счетчик адреса, распределитель импульсов, дешифратор конца программы, первый и второй реверсивные счетчики, одновибратор, четвертый и пятый триггеры, третий, четвертый, пятый и шестой элементы И, первый, второй и третий элементы И-НЕ, первый, второй и третий элементы НЕ, первый и второй элементы задержки, причем установочные входы первого, второго и третьего триггеров соединены с выходом элемента ИЛИ, выход перврго элемента И соединен с первым входом второго элемента И и с разрешающим входом блока ввода программ, входы данных которого являются входами данных системы, синхронизирующие входы и выход являются синхронизирующими входами и выходом системы, вход блокировки подключен к управляющему блокировкой выходу блока задания режимов, первые инфор- О мационные выходы блока ввода программ Ю и блока задания режимов соединены с информационными входами регистра номера канала, первого и второго .запоминающих узлов и счетчика адреса, вторые информационные выходы блока ввода программ и блока задания режимов соединены с информационными входами дешифратора команд, выход номера канала которого подключен к управляющему входу записи регистра номера канала, каждый выход разрешения записи которого подключен к тактовому входу распределителя импульсов

1

Изобретение относится к вычислительной технике и может быть использовано для цифрового анализа формы нескольких одновременно протекающих аналоговых процессов.

Известна многоканальная система регистрации аналоговых процессов, содержащая аналого-цифровые преобразователи и блоки памяти. . Принцип действия этой системы заключается в дискретизации исследуемых процессов, выборке дискретных значений сигналов, преобразовании их в цифровой код и запоминании кодов в блоках памяти, для восстановления впоследствии формы исследуемых сигналов l J.

Недостатком известкой системы являются ее ограниченные функциональные возможности.

Известна также многоканальная сисТема регистрации аналоговых процессов, содержащая в каждом канале последовательно соединенные усшштель входного сигнала, аналого-ци овой преобразователь и запоминающий блок, а также общий для всех каналов блок управления, соединенный с соответствующими входами аналого-цифровых преобразователей, источник частот дискретизации, подключеннь } своими выходами

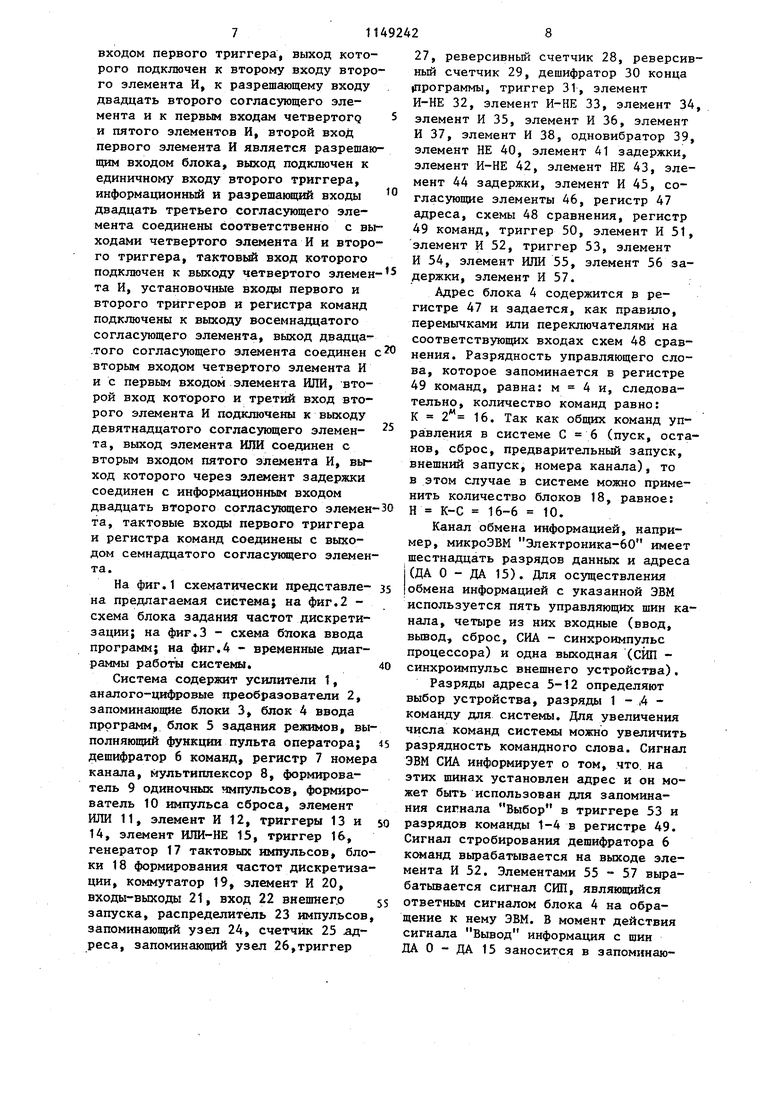

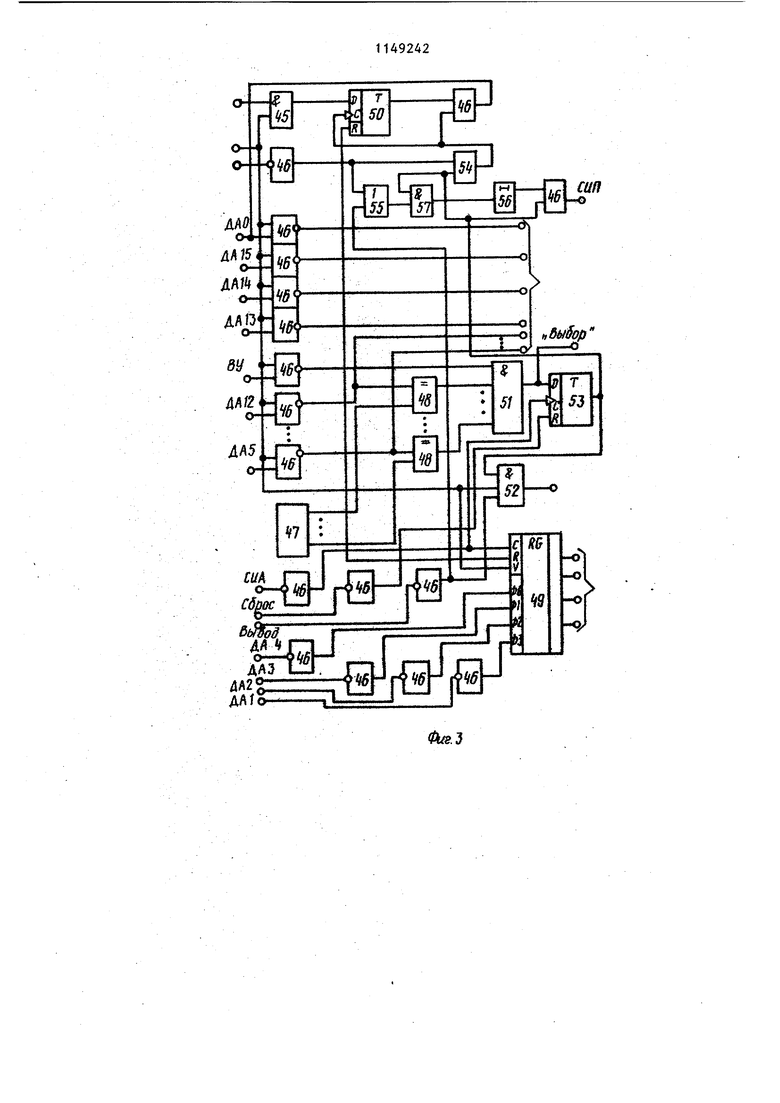

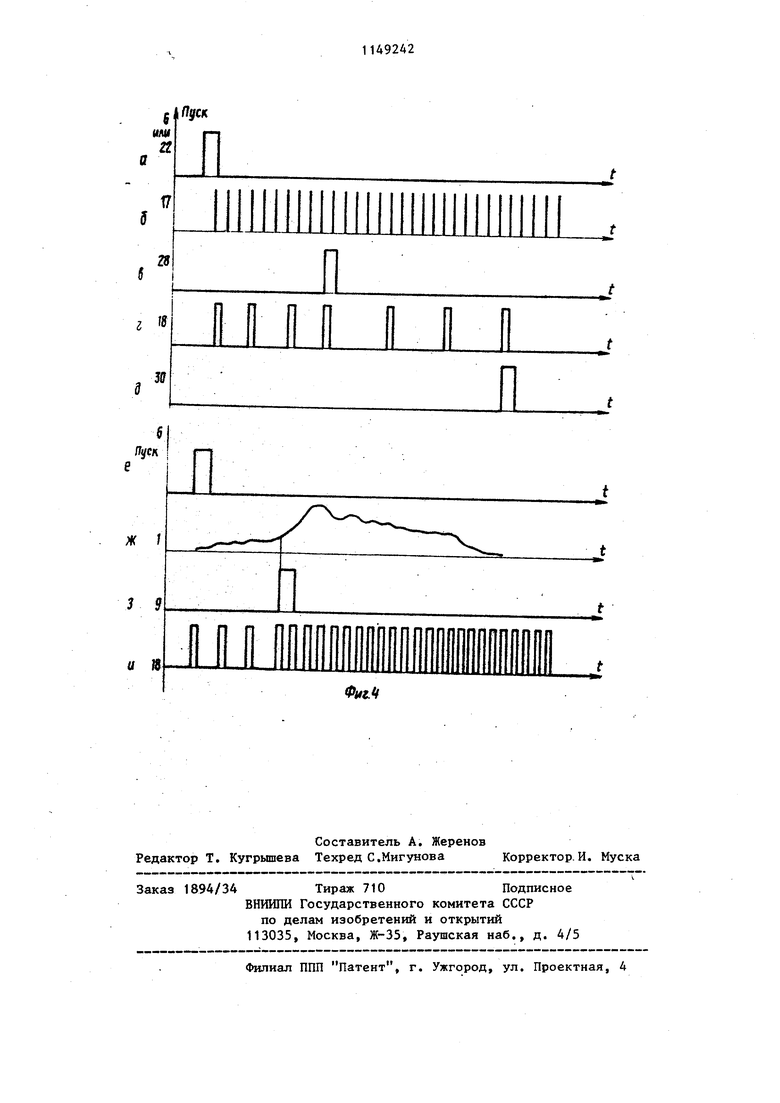

к входам блока управления, шину пускового сигнала, измеритель времениого интервала и блок блокировки источникa частот дискретизации, при этом вход блока блокировки, объединенный с входом Старт измерителя временны интервалов, подключен к шине пускового сигнала, вход Стоп измерителя временных интервалов подключен к одному из выходов источника частот дискретизации . Недостатком известной системы являются ее ограниченные функциональные возможности, так как нет возможности оперативно устанавливать задан ные частоты дискретизации на заданных участках периода регистрации. Кроме этого, все параметры режима регистрации устанавливаются оператором вручную и нет возможности исполь зования для этих целей электронной вычислительной машины (ЭВМ), т.е. применение ЭВМ для управления экспе риментом при использовании указанной системы регистрации ограничено. Целью изобретения является расширение функциональных возможностей за счет оперативного установления частот дискретизации на заданньпс участках периода регистрации и повышения производительности. Поставленная цель достигается тем что в систему, содержащую в каждом канале усилитель, выход которого под ключен к информационному входу аналого-цифрового преобразователя, выход которого соединен с входом запоминающего блока, входы усилителей являются информационными входами сие темы, вход запуска каждого аналогоцифрового преобразователя соединеи с выходом коммутатора, введены блок ввода программ, блок задания режимов, дешифратор команд, формировател импульса сброса, мультиплексор, регистр номера канала, формирователь одиночных импульсов, элемент ШШ, первый, второй и третий триггеры, первый и второй элементы И, элемент ИЛИ-НЕ, генератор тактовых импульсов и блоки формирования частот дискретизации,; каждый из которых Ш4еет первый и второй запом шающие узлы, счетчик адреса, распределитель импульсов, деш1фратор конца прогрш4мы, первый и второй реверсивные счетчики, одновибратор, четвертый и пятый триггеры, третий, четвертый, пятый и шестой элементы И, перш, второй и третий элементы И-НЕ, первый, второй и третий элементы НЕ, первый и 1 24 второй элементы задержки, причем установочные входы первого, второго и третьего триггеров соединены с выходом элемента ИЛИ, выход первого элемента И соединен с первым входом второго элемента И и с разрешающим входом блока ввода программ, входы данных которого являются входами данных системы, синхронизирующие входы и выход являются синхронизирующими входами и выходом системы, вход блокировки подключен к управляющему блокировкой выходу блока задания режимов , первые информационные выходы блока ввода программ и блока задания режима соединены с информационными входами регистра номера канала, первого и второго запоминающих узлов и счетчика адреса, вторые информационные выходы блока ввода программ и блока задания режимов соединены с информационными входами дешифратора команд, выход номера канала которого подключен к управляющему входу записи регистра номера канала, каждый выход разрешения записи которого подключен к тактовому входу распределителя импульсов соответствующего блока формирования частот дискретизации, установочные входы распределителя импульсов, счетчика адреса, четвертого триггера, первого и второго реверсивных счетчиков соединены с выходом элемента ИЛИ, выход элемента ИЛИ-НЕ подключен к единичному входу первого триггера, к единичному входу четвертого триггера, к единичному и нулевому входам пятого триггера, тактовый вход которого и первый вход третьего элемента И соединены с выходом генератора тактовых импульсов, выход второго триггера подключен к первому входу четвертого элемента И, выход которого соединен. со счетным входом первого реверсивного счетчика, выходы разрядов регистра номера канала соединены с адресным входом мультиплексора, информационные входы которого соединены соответственно с выходами усилителей, выход мультиплексора подключен к входу формирователя одиночных импульсов, выход которого соединен с нулевым входом второго триггера, единичный вход которого соединен с выходом предварительного запуска дешифратора команд, выхода внешнего запуска, пуска, останова и сброса которого соединены соответственно с единичным входом третьего триггера, с первым входом элемента ИЛИ-НЕ,с нулевым входом первого триггера и с первым входом элемента ИЛИ, второй вход которого соединен с выходом формирователя импульса сброса, второй вход второго элемента И соединен с входом внешнего запуска системы, третий вход подключен к выходу третьего триггера выход второго элемента И соединен с вторым входом элемента ИЛИ-НЕ, выход первого триггера соединен с входом генератора тактовых импульсов, выход одновибратора каждого блока формирования частот дискретизации соединен с соответствующим входом коммутатора, выход первого элемента НЕ подключен к соответствующему входу первого элемента И, второй вход третьего элемента И соединен с выходом пятого триггера, третий вход третьего элемента И и вход первого элемента НЕ подключены к выходу первого элемента И-НЕ, выход второго элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом четвертого триггера, выход третьего элемента И-НЕ соединен с первым входом первого элемента И-НЕ, второй вход которого, вход первого элемента задержки и счетный вход счетчика адреса соединены с вьпсодом переноса первого реверсивного счетчика, выход пятого элемента И соединен с тактовым входом второго реверсивного счетчика, выход шестого элемента И соединен с тактовым входом первого реверсивного счетчика, информационный вход которого и информационный вход дешифратора конца программы соединены с выходом первого запоминающего уэла, выход дешифратора Конца программы подключен к первому входу второго элемента И-НЕ и к ВХОДУ второго элемента НЕ, выход которого соединен с вторым входом четвертого элемента И и с первым входом шестого элемента И, второй вход которого соединен с выходом первого элемента задержки, третий вход шестого элемента счетный вход второго реверсивного счетчика и первый вход пятого элемента И подключен к выходу третьего элемента И, второй вход пятого элемента И соединен с выходом второго элемента задержки, вход которого, третий вход четвертого элемента И, входы одновибратора и третьего элемента НЕ соединены с выходом переноса второго реверсивного счетчика, выход третьего элемента НЕ соединен с вторым входом второго элемента И-НЕ, выходы разрядов счетчика адреса подключены к адресным входам первого и второго .запоминающих уэяов, тактовые входы счетчика адреса, первого и второго запоминающих узлов соединены соответственно с первым, вторым и третьим выходами распределителя импульсов, выход второго запоминающего узла подключен к информационному входу второго реверсивного счетчика. Блок ввода программ содержит элементы И, ИЛИ задержки, схемы сравнения, триггеры, регистр команд, регистр адреса и согласующие элементы, причем информационные входы с первого по шестнадцатый согласующих элементов являются входами данных блока, выходы согласующих элементов с первого по четвертый подключены соответственно к информационным входам регистра команд, информационные входы согласующих элементов с семнадцатого по двадцать первый являются синхронизирующими входами блока, выход двадцать второго согласукнцего элемента является синхронизирующим выходом блока, выход двадцать третьего согласующего элемента, вход блокировки блока соединен с разрешающими входами согласукицих элементов с пятого по шестнадцатый и двадцать первого, с первыми входами первого и второго элементов И, с входом блокировки регистра команд, выходы разрядов которого и выход второго элемента И являются BToiHiiM информаиионHbw выходом лока, выходы согласукгщих элементов с пятого по шестнадцатый ЯВЛ5ПОТСЯ первым ннфо1и 1ационным выходом блока, выход каждого согласующего элемента с пятого по двенадцатый соединен с первым входом со- ответствутощей схемы сравнения, второй вход которой подключен к выходу соответствующего разряда регистра адреса, первый вход третьего злемента И соединен с выходом двадцать первого согласующего элемента, входы, начиная с второго, третьего злеента И соединены соответственно с выходами схем сравнения, выход третьего элемента И соединен с единичным входом первого триггера, выход которого подключен к второму входу второ го элемента И, к разрешающему входу двадцать второго согласующего элемента и к первым входам четвертогд и пятого элементов И, второй вход первого элемента И является разрешаю щим входом блока, выход подключен к единичному входу второго триггера, информационньй и разрешакщий входы двадцать третьего согласующего элемента соединены соответственно с вы ходами четвертого элемента И и второ го триггера, тактовый вход которого подключен к выходу четвертого элемен та И, установочные входы первого и второго триггеров и регистра команд подключены к выходу восемнадцатого согласующего элемента, выход двадца.того согласующего элемента соединен вторым входом четвертого элемента И и с первым входом элемента ИЛИ, второй вход которого и третий вход второго элемента И подключены к выходу девятнадцатого согласующего элемента, выход элемента ИЛИ соединен с вторым входом пятого элемента И, ход которого через элемент задержки соединен с информационным входом двадцать второго согласующего элемен та, тактовые входы первого триггера и регистра команд соединены с выходом семнадцатого согласукнцего элемен та. На фиг.1 схематически представлена предлагаемая система; на фиг.2 схема блока задания частот дискретизации; на фиг.З - схема блока ввода программ; на фиг.4 - временные диаграммы работы системы. Система содержит усилители 1, аналого-цифровые преобразователи 2, запоминающие блоки 3 блок 4 ввода программ, блок 5 задания режимов, вы полняющий функции пульта оператора; дешифратор 6 команд, регистр 7 номер канала, мультиплексор 8, формирователь 9 одиночных импульсов, формирователь 10 импульса сброса, элемент ИЛИ 11, элемент И 12, триггеры 13 и 14, элемент ИЛИ-НЕ 15, триггер 16, генератор 17 тактовых импульсов, бло ки 18 формирования частот дискретиза ции, коммутатор 19, элемент И 20, входы-выходы 21, вход 22 внешнего запуска, распределитель 23 импульсов запоминающий узел 24, счетчик 25 лдреса, запоминающий узел 26,триггер 27, реверсивный счетчик 28, реверсивный счетчик 29, дешифратор 30 конца |Программы, триггер 31, элемент И-НЕ 32, элемент И-НЕ 33, элемент 34, элемент И 35, элемент И 36, элемент И 37, элемент И 38, одновибратор 39, элемент НЕ 40, элемент 41 задержки, элемент И-НЕ 42, элемент НЕ 43, элемент 44 задержки, элемент И 45, согласующие элементы 46, регистр 47 адреса, схемы 48 сравнения, регистр 49 команд, триггер 50, элемент И 51, элемент И 52, триггер 53, элемент И 54, элемент ИЛИ 55, элемент 56 задержки, элемент И 57. Адрес блока 4 содержится в регистре 47 и задается, как правило, перемычками или переключателями на соответствующих входах схем 48 сравнения. Разрядность управляющего слова, которое запоминается в регистре 49 команд, равна: м 4 и, следовательно, количество команд равно: К 2 16. Так как общих команд управления в системе С 6 (пуск, останов, сброс, предварительный запуск, внешний запуск, номера канала), то в этом случае в системе можно применить количество блоков 18, равное: Н К-С 16-6 10. Канал обмена информацией, например, микроэвм Электроника-60 имеет шестнадцать разрядов данных и адреса (ДА О - ДА 15). Для осуществления обмена информацией с указанной ЭВМ используется пять управляющих шин канала, четыре из них входные (ввод, вьтод, сброс, СИА - синхроимпульс процессора) и одна выходная (СИП синхроимпульс внешнего устройства). Разряды адреса 5-12 определяют выбор устройства, разряды 1 - А команду для системы. Для увеличения числа команд системы можно увеличить разрядность командного слова. Сигнал ЭВМ СИА информирует о том, что. на этих шинах установлен адрес и он может быть использован для запоминания сигнала Выбор в триггере 53 и разрядов команды 1-4 в регистре 49. Сигнал стробирования дешифратора 6 команд вырабатывается на выходе элемента И 52. Элементами 55 - 57 вырабатывается сигнал СИП, являющийся ответным сигналом блока 4 на обращение к нему ЭВМ. В момент действия сигнала Вывод информация с шин ДА О - ДА 15 заносится в запоминаю9щие узлы 24 и 26 и счетчик 25 адреса блоков 18, а также в регистр номера канала или выполняются команды управления. Элементами 45, 50, 54 в рабатывается потенциал разряда состояния ДАО, который формируется элементом И 12 и сигнализирует о готовности системы принять программ ее функционирования во время цикла Ввод микроэвм. Сигналом Блокиров ка, поступающим с выхода блока 5, блок 4 блокируется (выходы соответствующих элементов 46, 52 и регистр 49 переходят в состояние Обрыв). При этом функцию программирования р жима регистрации системы выполняет оператор с блока 5 вручную. Блок 5 может содержать в своем составе последовательно соединенные клавиатуру, шифратор и регистры дан ных и команд, а также формирователь импульса стробирования дешифратора 6 команд, клавишу блокировки блока - 4, выходные буферные элементы, кото рые находятся в состоянии Обрьш при функционировании блока 4. Формирователь 9 может содержать в своем составе последовательно соединенные компаратор напряжения и одновибратор. Формирователь 10 импульса сброса может содержать инвер тор, вход которого через параллельн соединенные резистор и конденсатор подключен к проводу нулевого потенциала, а выход - к выходной шине. При подаче напряжения питания к системе на выходе формирователя 10 импульса сброса появляется сигнал, который через элемент ИЛИ 11 произв дит установку в исходное состояние соответствующих триггеров и счетчиков . Сигналы с входа 21 поступают на вход блока 4, где дешифрируется адрес внешнего устройства, к которо обращается ЭВМ, и если ЭВМ обращает ся к данному блоку 4, то в соответствии с сигналами на выходе дешифра тора 6 команд производится одна из операций управления системой регист ции. Пусть на выходе дешифратора 6 ко манд появляется сигнал Запись 1. По этому сигналу производится прием информации с выхода блока 4 в счетчик 25 адреса первогр блока 18. Сиг Запись 1, подающийся на тактовый вход распределителя 23 импульсов, с 42 держащего, например, последовательно соединенные счетчик и дешифратор, поступает с первого выхода распределителя 23 импулвсов на вход счетчика 25 адреса. По заднему фронту этого сигнала состояние распределителя 23 импульсов изменяется на единицу. При появлении второго сигнала Запись 1 производится прием информации в запоминающий узел 24 по адресу, поступающему с выхода счетчика 25. При появлении третьего сигнала Запись 1 производится прием информации в запоминающий узел 26. Если разрядность и емкость запоминающих узлов 24 и 26 большая, то прием информации в один адрес может производиться в несколько тактов. Сначала - прием адреса в счетчик 25, затем - прием данных в запоминающие узлы 24 и 26. При этом число разрядов распределителя 23 импульсов должно быть увеличено. Аналогично заносится программа функционирования в другие блоки 18. Причем по последнему адресу программы запоминающего узла 24 пишется признак конца программы, например, во все разряды заносятся нули. После окончания записи всей программы ЭВМ устанавливает командой Сброс счетчик 25 адреса в исходное состояние и может выдать команду Пуск (фиг. 4а), которая через элемент ИЛИ-НЕ 15 устанавливает в 1 триггер 13, запускай тем самым генератор 17 тактовых импульсов (фиг. 46), а также обнуляет триггер 27, устанавливает в 1 триггер 31. При появлении первого импульса на тактовом входе триггера 27 последний по переднему фронту импульса устанавливается в 1, и через элемент И 38 начинают проходить тактовые импульсы. Первьй тактовый импульс через элементы И 35 и 37 производит запись информации соответственно в реверсивные счетчики 28 и 29 с выходов запоминающих узлов 24 и 26. При этом состояния этих счетчиков изменяются, и на их выходах обратных переносов устанавливается О, при этом на выходе одновибратора 39 формируется первый импульс дискретизации, который через коммутатор 19 поступает на соответствуияцие входы аналого-цифровых преобразователей 2. Счетчик 29 работает в режиме вычитания. После того как на его счетный вход поступят тактовые импульсы количество которых равно числу, записанному в счетчик 29 с выхода запоминающего узла 26, на его выходе переноса появится 1, которая через элемент И 36 произведет уменьшение на единицу содержимого счетчика 28.

Выбирая соответствукнцим образом число заносимое в реверсивный счетчик 29, и при известном периоде еледования тактовых импульсов можно устанавливать необходимый период импульсов дискретизации системы, а задавая число, заносимое в реверсивньй счетчик 28, работающий в режиме вычитания, MOJKHO устанавливать нужное количество измерений при заданном периоде дискретизации. После появления 1 на выходе реверсивного счетчика 28 (фиг. 4в), содержимое счетчика 25 адреса увеличивается на единицу и при очередном тактовом имцульсе происходит занесение новой информации в реверсивные счетчики 28 и 29 соответственно с выходов запоминающих узлов 24 и 26. Генерирование импульсов дискретизации.с заданными параметрами (фиг. 4г) продолжается до тех пор, пока с выхода запоминающего узла 24 не поступит код конца программы. При этом на выходе дешифратора 30 появляется 1 (фиг. 4д) и на выходе элемента НЕ 40 появляется О. При поступлении очередного тактового импульса производится запись информации в счетчик 29 и генерирование последнег импульса дискретизации. Величины времени задержки элементов 41 и 44 выбираются несколько большими длительности тактового импульса, чтобы предотвратить занесение информации в соответствующие реверсивные-счетчики по тактовому импульсу, обнуляющему их.

Система может работать в режиме запуска от внешнего источника, при этом после программирования режимов регистрации выдается команда Внешний запуск. При этом на выходе триггера 16 устанавливается 1, и если устройство готово (на выходе элемента И 12 t), то при поступлении сигнала запуска с входа 22 через элемент И 20 происходит запуск систе мы.

Система может работать также в релоше предварительного запуска.

который необходим в случае, когда нужно получить информацию о предыстории исследуемого сигнала. В этом случае в запоминающий узел 26 заносятся коды тактовой частоты импульсов дискретизации в периоды до начала исследуемого сигнала и после него, а в запоминающий узел 24 заносится код, которьш определяет количество измерений происходимых после появления исследуемого сигнала. При этом по команде Номер канала производится занесение соответствующего кода номера канала исследуемого сигнала в регистр 7, затем с помощью мультиплексора йроизводится коммутация выхода усилителя 1 выбранного канала с входом формирователя 9. По команде Предварительный запуск на выходе триггера 14 устанавливается О, который блокирует элемент И 36, а по команде Пуск (фиг. 4е) начинается регистрация информации с заданной частотой дискретизации (фиг. 4и), При появлении исследуемого сигнала (фиг. 4ж) на выходе формирователя 9 появляется импульс (фиг, 4з), который обнуляет триггер 14, на инверсном выходе которого появляется 1, при этом элемент И 36 деблокируется и импульсы с вькода реверсивного счетчика 29 поступают на счетньй вход реверсивного счетчика 28. Регистрация заканчивается после количества измерений, заданного кодом, занесенным в «счетчик 28,

В системе имеется возможность оперативно устанавливать заданные частоты дискретизации на заданных участках периода регистрации. Это позволяет значительно сократить объем запоминающих блоков 3 при регистрации переходных процессов и импульсов сложной формы. Помимо этого имеется возможность производить последовательно ряд полных периодов регистрации с заданной фиксированной частотой дискретизации в каждом периоде регистрации. Это позволяет, например, автоматически осуществлять программу испытаний различных источников аналоговых сигналов в заданном частотном диапазоне. Режи1Ф1 регистрации определяются программой функционирования системы регистрации вводимой в блоки 18 системы автоматически с ЭВМ или вручную оператором с пульта.

Пдск

S

или

tt

tri

,

2

jffi

д

г

Пуск

ж Г

Г

и 18

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Соколов М.П | |||

| Применение автоматических устройств в физическом эксперименте | |||

| М., 1969, с, 290 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальная система регистрации аналоговых процессов | 1981 |

|

SU951146A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-04-07—Публикация

1983-09-14—Подача