Изобретение относится к вычислительной технике и .может быть использовано в мультипроцессорных системах.

Цель изобретения - упрощение устройства,

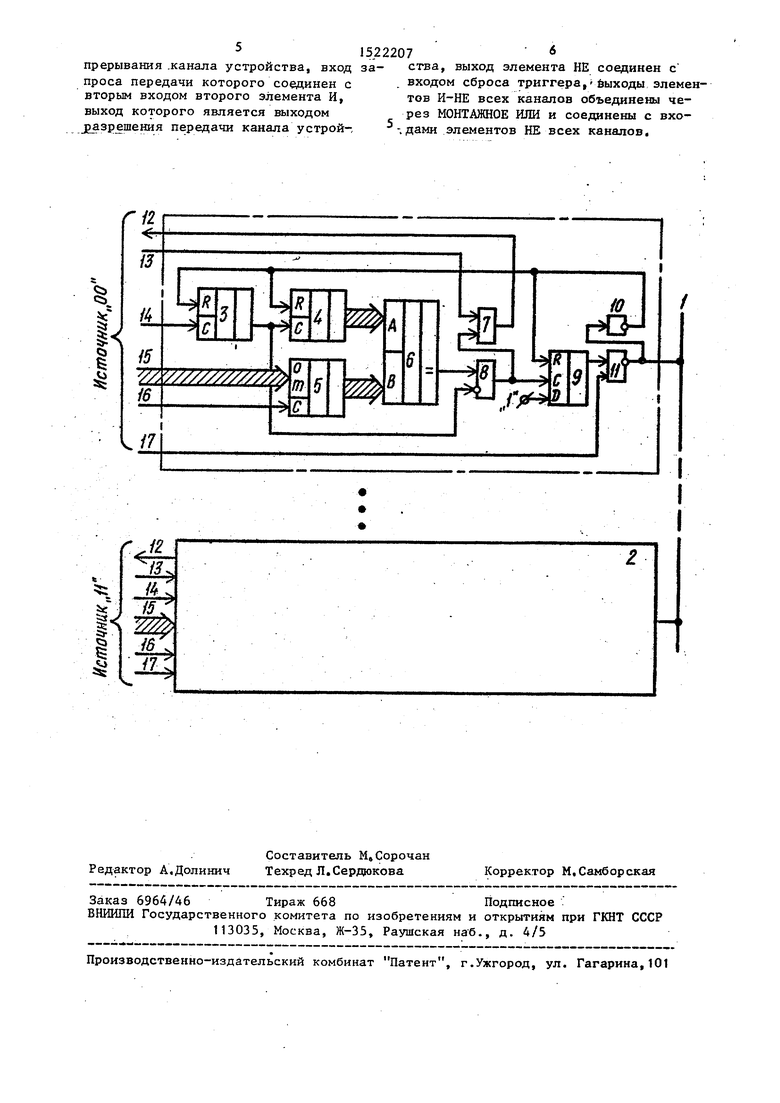

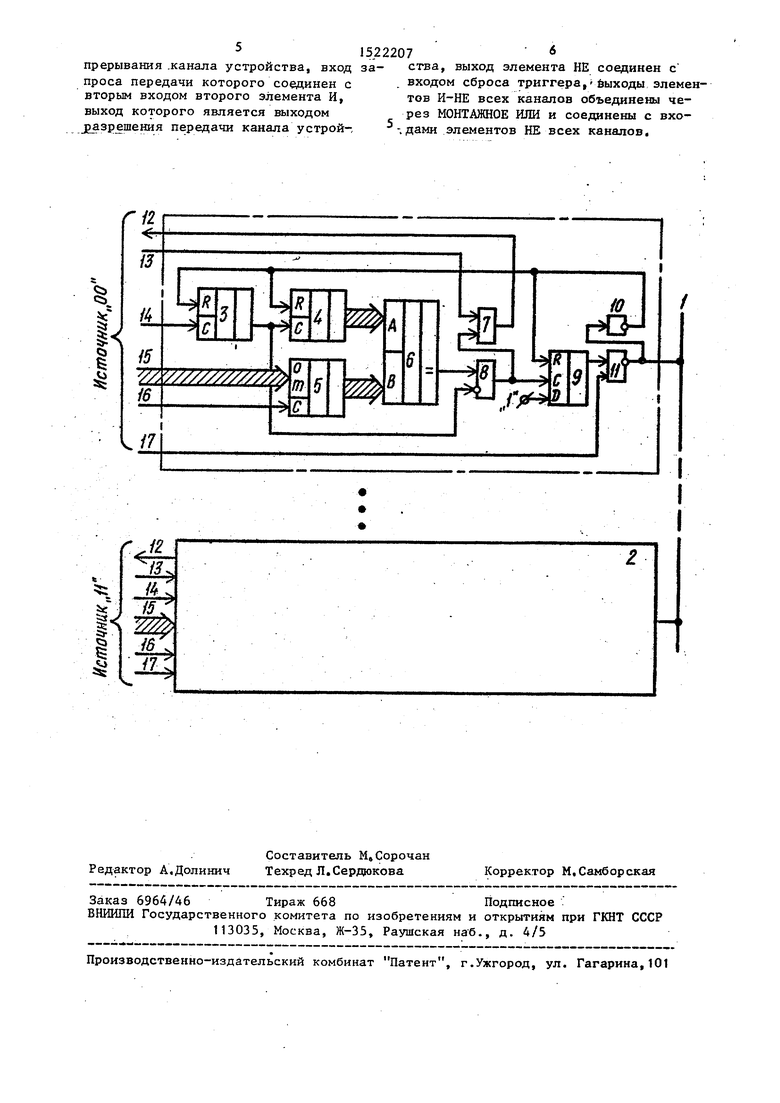

На чертеже представлена структурная схема устройства.

Устройство содержит линию 1 синхронизации и каналы 2, а в каждом канале делитель 3, счетчик 4 текущего адреса, регистр 5 адреса, схему 6 сравнения, элементы И 7 и 8, триггер 9, элемент НЕ 1-0, элемент И-НЕ 11, выход 12 разрешения передачи источнику информации, вход 13 запроса передачи источника информации, тактовьш вход 14, : адресные входы 15, вход 16 занесения адреса источника информации, вход 17

запроса прерывания источника информации.

Делитель 3 предназначен для задания длительности одного сеанса передачи- и представляет собой счетчик, который по модулю .N. N определяется выражением

N TS/TI,

где TI - длительность периода следования импульсов синхронизации источника информации, обслуживаемого дан- каналом устройства;

TS - длительность одного сеанса передачи устройства.

Работу устройства рассмотрим применительно к вычислительной системе, содержащей четыре источника информации .

ел ю IND

1чд

В зависимости от приоритета источникам присваиваются адреса: 00, О, 10 и 11, которые при инициализации U системы заносятся ими в ре- . гистры 5 соответствующих каналов, Ис--. точник II устанавливает на входе 7 своего канала единичньй сигнал запроса прерьшания., делители 3,, счетчики 4 и триггеры 9 находятся в сброшенном состоянии (цепи начальной установки не показаны),

Устройство работает следутощим образом

Делители 3 в каждом канале вырабатывают импульсы длительностью Т, сле- дущие с периодом TS, которые практически синхронно переключают счетт-шки 4 из начального,состояния 00 в сос- .тонине 01, 10 i1.

В каждом из каналов при равенстве {Содержимого счетчика 4 и регистра 5 на выходе схемы 6 появляется единич- , ный сигнал, который по окончанию импульса на выходе делителя 3 через эле мент 8 И поступает на вход элемента .7 И и на С-вход триггера 9 Если при этом .на другой вход вырабатывается единичный сигнал свидетельствующий источнику о разрешении передачи При завершении очередного сеанса переда- ; чк в соответствующем канале фронт .c.irn редкого импульса с выхода дели1 еля 3, I кроме переключения счетчика 4 через

элемент 8 И записывает в триггер 9 единичньш сигнал с его В-входау что ; содержимое счетчиков 4 текущего адре- Гса .устройства превьшает адрес ника, связанного с данным каналом, ;Так как на входе 17 канала, соответ- ствующего источнику 11, при инициализации системы последний устанавливает единичный сигнал запроса прерывания,, то по окончании сеа.нса передачи, выделенного источнику % единичный :сигнал с выхода триггера 9 открывает элемент И-НЕ 11 и сигнал с входа 17 через элемент И-НЕ канала источника 11, линию устройства и элементы НЕ 10 сбрасывает все делители 3, счетчики 4 и триггеры 9 устройства,Таким образом, каждому из источников 00, 0 10 и 11 последовательно передается :право проведения одного сеанса пере- :дачи. Если какому-то из источников необходимо осуществить экстренную передачу данных то он вместе с сигна- лом запроса передачи на вход 13 выставляет сигнал запроса прерывания на

5

0

0

5

0

5.

входе 17. При этом, если триггер 9 в соответствующем канале находится в единичном со стоянии, что говорит об обслуживании устройством .менее приоритетного, чем выставившего запрос прерывания источника, то установленный сигнал запроса прерывания через элемент, И-НЕ 1 1, линию 1 устройства

и элементы НЕ 10 сбрасывает делители 3, счетчики 4 и триггеры 9. Если запрос прерывания выставил источник OOj то время .реакции составит TS, если источник 01 - (при-отсутствии запроса прерывания от источника 00), если источник 10 - 3 TS (при отсутствии запроса прерывания от источ ш- ков 00 н 01), Причем источник 00 может полностью монополизировать ресурс магистрали,источнис 01-1/2 ресурса магистрали,право передачи при этом предоставляется только источникам с йыс0шим приоритетом, При снятии запросов пер,едачи устройство опять переходит в циклический peMiM работы,,

Формула изобретения

Многокан-альное устройство для под-, ключения истсчников информации к общей -магистралиj содержащее в каждом канале схему сравнения, счетчик текущего адреса, регистр адреса, делитель, лг.гемент НЕ, первый и второй элементы Я;, причем в каждом канале тактовый вход канала устройства соединен с так- товрзш входом делителя, выход которого соединен со счетным входом счетчика адреса и первым входом первого элемента И, адресный вход канала устройетва сое динен с информационным входом регистра адреса, выход которого соеди-г нен с первым входом схемы сравнения, .выход Равно которой соединен с вторым входом первого элемента И, выход элемента НЕ соединен с выходами сброса делителя и счетчика текущего адреса, выход которого соединен с вторым входом схемы сравнения, вход занесения адреса канала устройства соединен с входом записи регистра адреса, отличающееся тем, что, с целью упрощения, каждый канал устройства содержит триггер и элемент И-НЕ, причем в каждом канале выход первого элемента И соединен.с первьш входом второго элемента И и с тактовым входом триггера, выход которого соединен с первьм входом элемента И-НЕ, .второй вход которого является входом запроса

прерывания .канала устройства, вход проса передачи которого соединен с вторым входом второго элемента И, выход которого является выходом .азрешения передачи канала устройза1522207

ства, выход элемента НЕ соединен с

входом сброса триггера,-йыходы элементов И-НЕ всех каналов объединены через МОНТАЖНОЕ ИЛИ и соединены с вхо5.

-.дамн элементов НЕ всех каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1280631A1 |

| Контроллер для связи процессоров с общей магистралью | 1988 |

|

SU1575197A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения ЭВМ с синхронным каналом передачи данных | 1986 |

|

SU1424023A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ЛЕКАРСТВЕННОГО УЧЕТА | 1994 |

|

RU2111534C1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах. Цель изобретения - упрощение устройства. Устройство содержит линию синхронизации и каналы по числу источников информации. В каждый канал входят делитель, счетчик текущего адреса, схема сравнения, регистр адреса, триггер, два элемента И. Упрощение устройства достигается за счет использования в каждом канале триггера, фиксирующего в каждом цикле обмена момент срабатывания канал. Любой запрос на передачу, поступающий в канал при установленном состоянии триггера, расценивается как более приоритетный, чем обслуживаемый в данный момент устройством. Это позволяет применить в устройстве схемы сравнения только по равенству, использующие по крайней мере в два раза меньше логических элементов. 1 ил.

| Патент ФРГ № 2913288, ют, G 06 F, 9/46, 1978 | |||

| Устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1280631A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-08—Подача