Изобретение относится к вычислительной технике и может быть использовано для построения близкодействую- щих мультипроцессорных систем с общей магистралью.

Целью изобретения является расширение области применения контроллера за счет возможности передачи сообщений от источника к нескольким получателям.

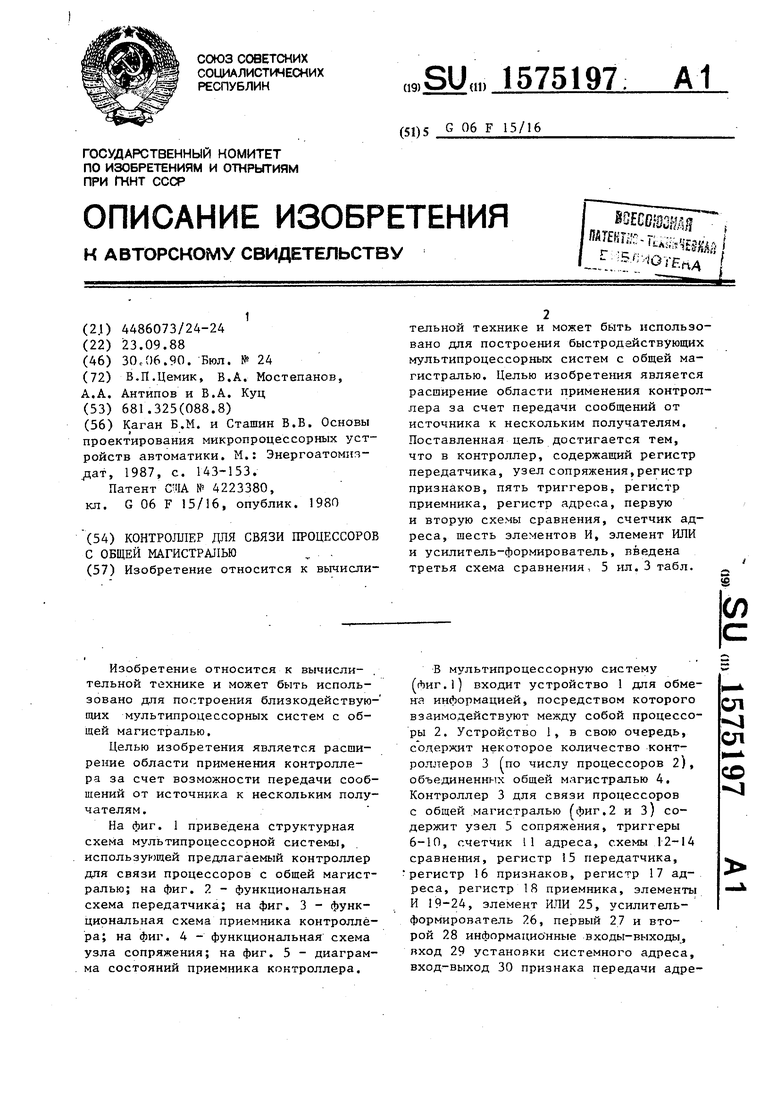

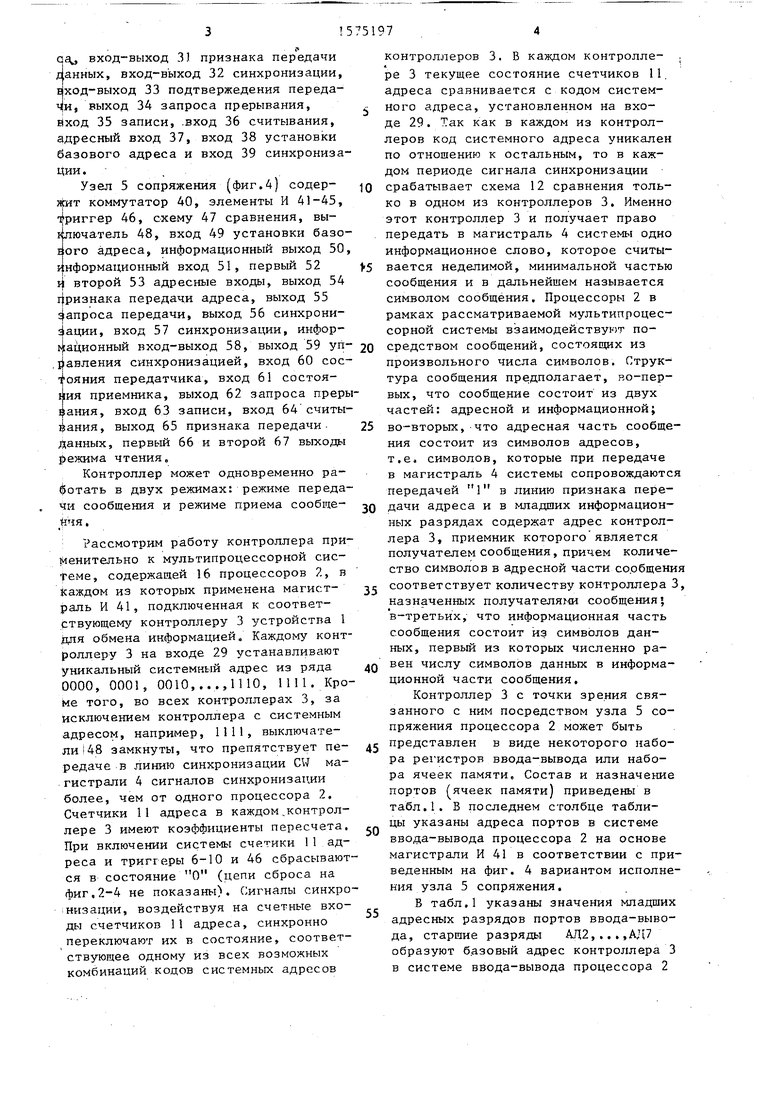

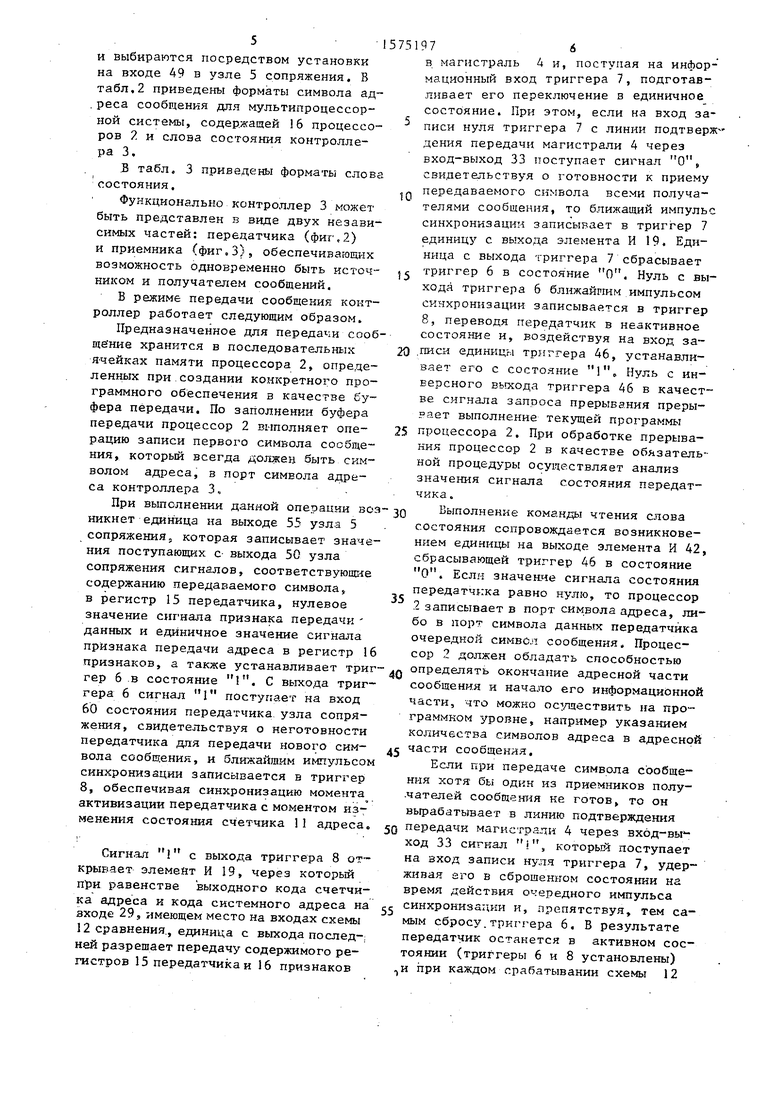

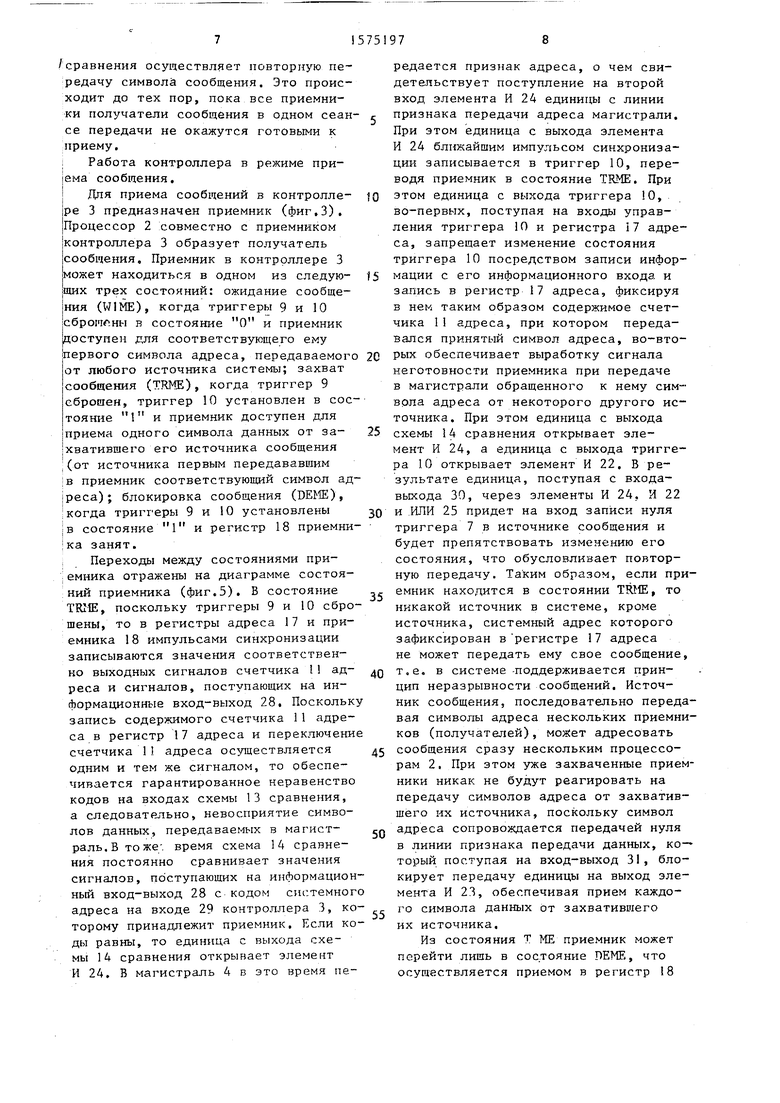

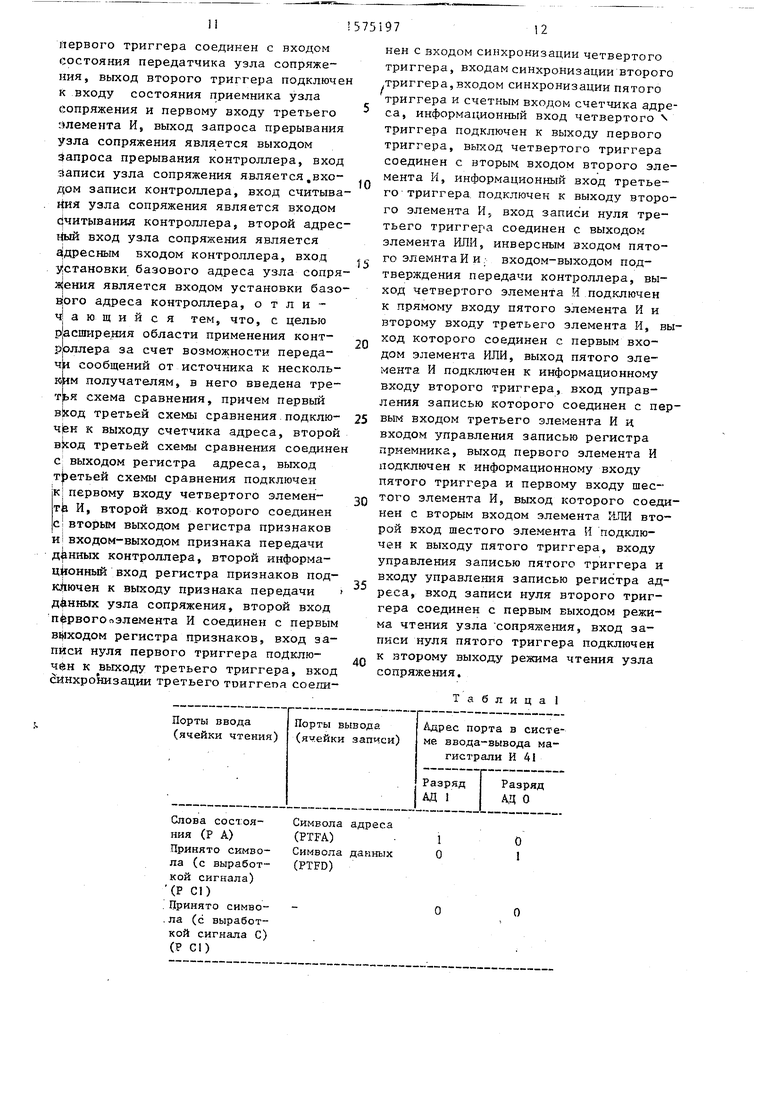

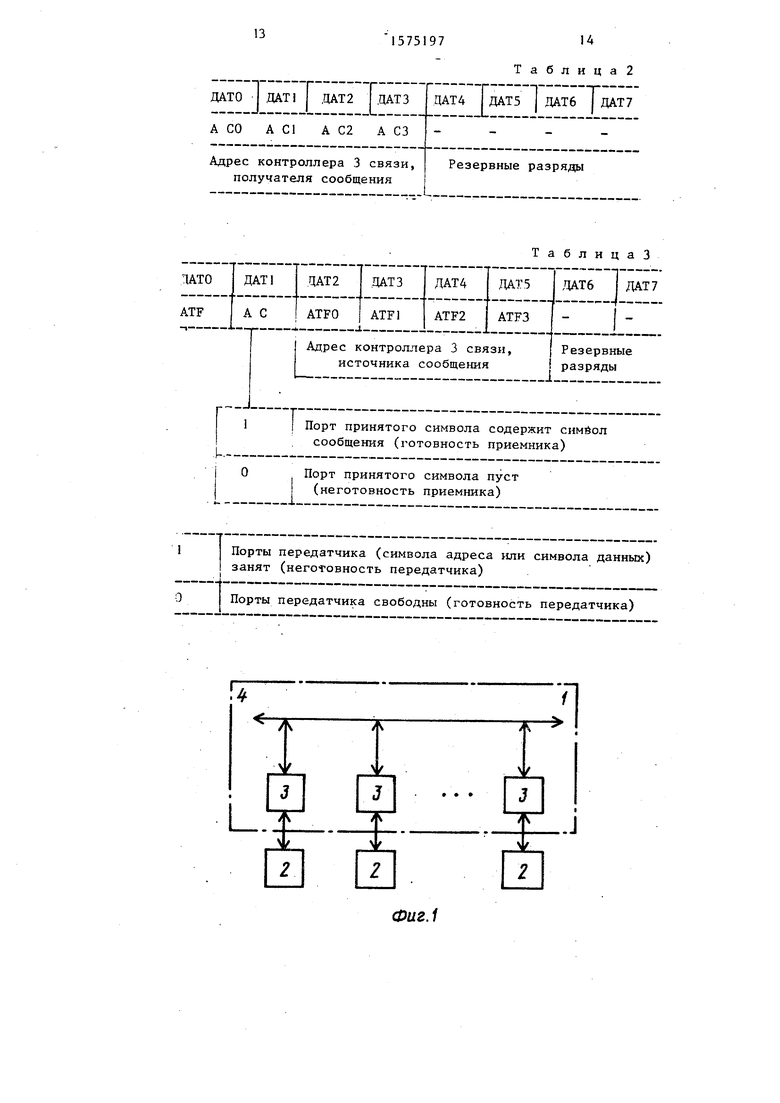

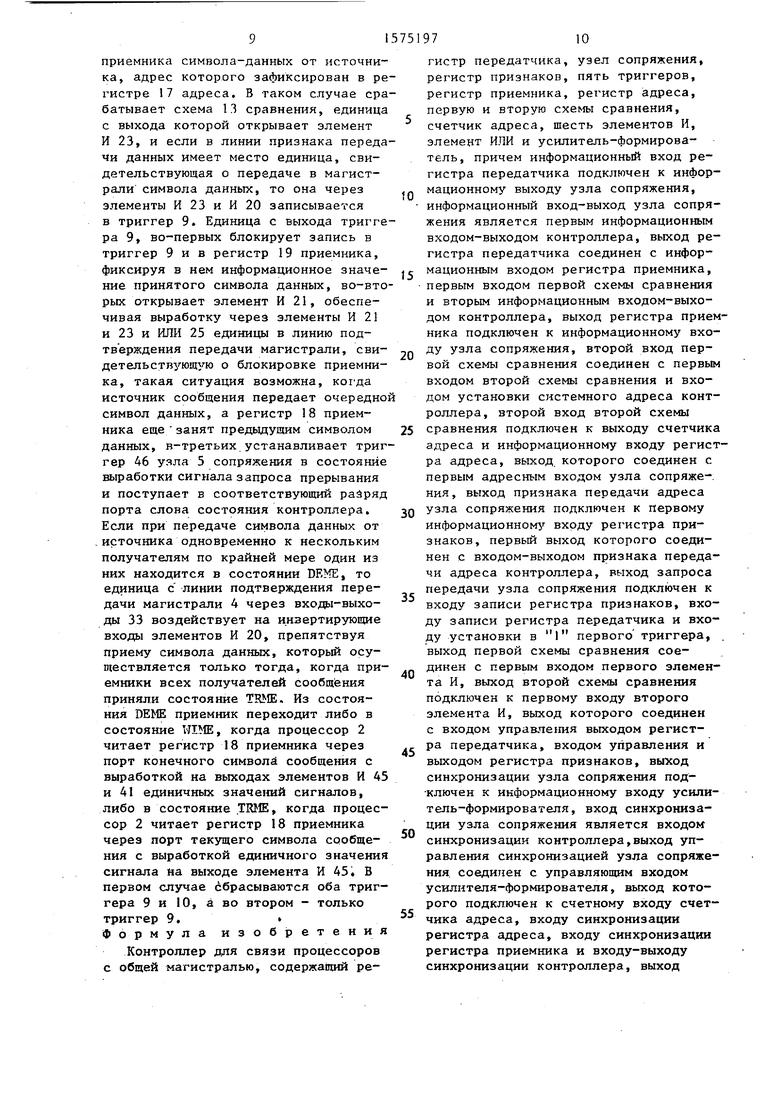

На фиг. 1 приведена структурная схема мультипроцессорной системы, использующей предлагаемый контроллер для связи процессоров с общей магистралью; на фиг. 2 - функциональная схема передатчика; на фиг. 3 - функциональная схема приемника контроллера; на фиг. 4 - функциональная схема узла сопряжения; на фиг. 5 - диаграмма состояний приемника контроллера.

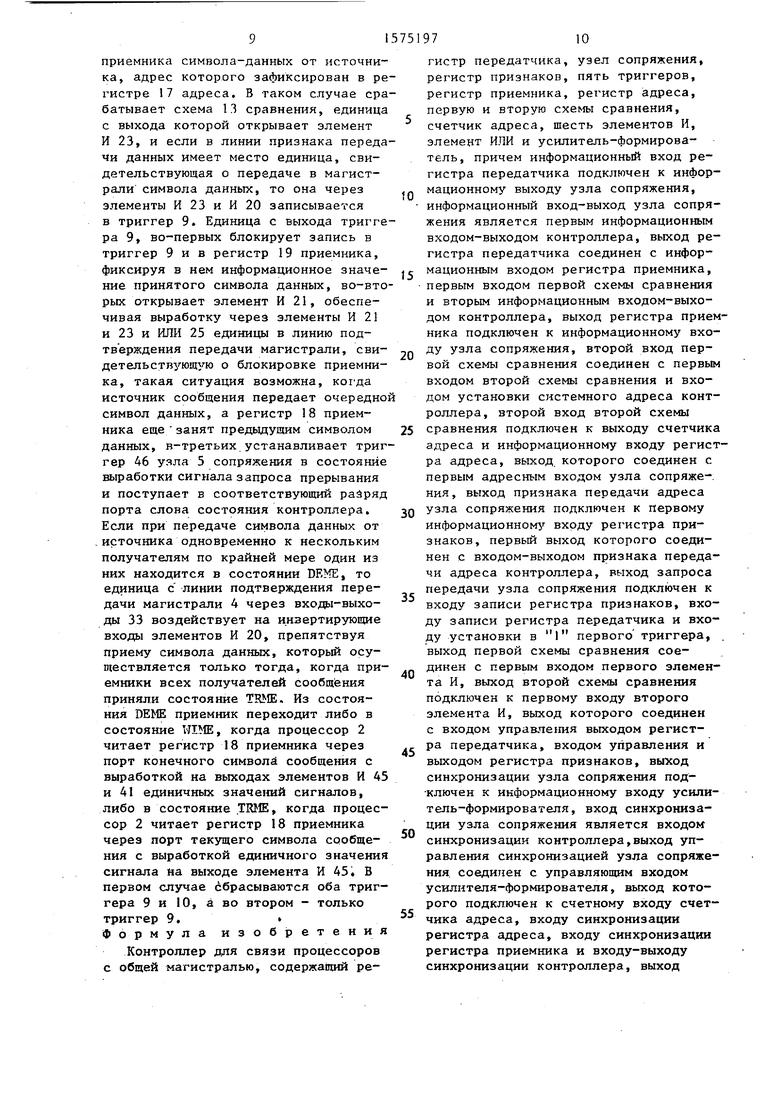

В мультипроцессорную систему ((Ъиг.1) входит устройство 1 для обмена инАормацией, посредством которого взаимодействуют между собой процессоры 2. Устройство 1, в свою очередь, содержит некоторое количество контроллеров 3 (по числу процессоров 2), объединенных общей магистралью 4. Контроллер 3 для связи процессоров с общей магистралью (фиг.2 и 3) содержит узел 5 сопряжения, триггеры 6-10, счетчик 11 адреса, схемы 12-14 сравнения, регистр 15 передатчика, регистр 16 признаков, регистр 17 адреса, регистр 18 приемника, элементы И 14-24, элемент ИЛИ 25, усилитель- формирователь 26, первый 27 и второй 28 информационные входы-выходы, вход 29 установки системного адреса, вход-выход 30 признака передачи адреелvj

СП

со j

qa вход-выход 3) признака передачи Данных, вход-выход 32 синхронизации, Е(ХОД-ВЫХОД 33 подтвержедения передави, выход 34 запроса прерывания, вход 35 записи, вход 36 считывания, адресный вход 37, вход 38 установки базового адреса и вход 39 синхронизации.

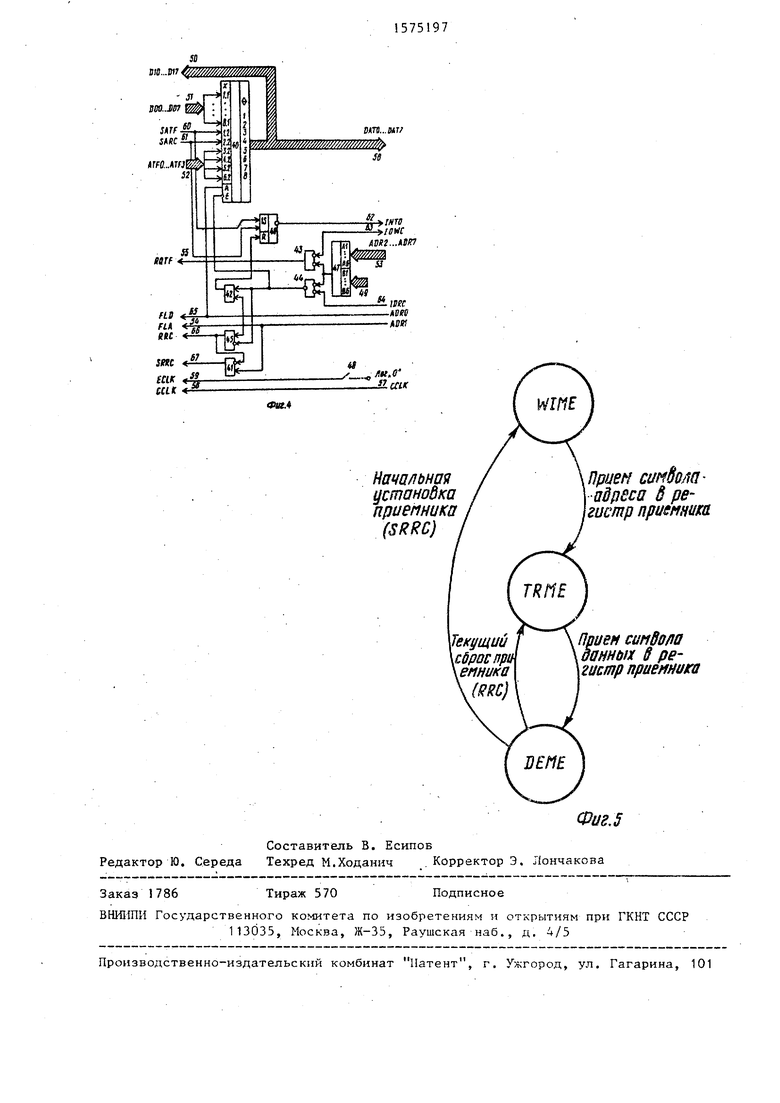

Узел 5 сопряжения (фиг.4) содер- жит коммутатор 40, элементы И 41-45, т риггер 46, схему 47 сравнения, вы- фпочатель 48, вход 49 установки базового адреса, информационный выход 50, информационный вход 51, первый 52 и второй 53 адресные входы, выход 54 Признака передачи адреса, выход 55 Запроса передачи, выход, 56 синхрони- з ации, вход 57 синхронизации, инфор- ационный вход-выход 58, выход 59 уп- Давления синхронизацией, вход 60 состояния передатчика, вход 61 состоя- ия приемника, выход 62 запроса преры ания, вход 63 записи, вход 64 считывания, выход 65 признака передачи данных, первый 66 и второй 67 выходы режима чтения.

Контроллер может одновременно работать в двух режимах: режиме передачи сообщения и режиме приема сообщения .

Рассмотрим работу контроллера применительно к мультипроцессорной системе, содержащей 16 процессоров 2, в каждом из которых применена магистраль И 41, подключенная к соответствующему контроллеру 3 устройства 1 для обмена информацией„ Каждому контроллеру 3 на входе 29 устанавливают уникальный системный адрес из ряда 0000, 0001, 00101110, 1111. Кроме того, во всех контроллерах 3, за исключением контроллера с системным адресом, например, 1111, выключатели 48 замкнуты, что препятствует передаче в линию синхронизации CW магистрали 4 сигналов синхронизации более, чем от одного процессора 2. Счетчики 11 адреса в каждом контроллере 3 имеют коэффициенты пересчета. При включении системы 1 аД реса и триггеры 6-10 и 46 сбрасываются в состояние О (цепи сброса на фиг.2-4 не показаны). Сигналы синхронизации, воздействуя на счетные входы счетчиков 11 адреса, синхронно переключают их в состояние, соответствующее одному из всех возможных комбинаций кодов системных адресов

5 0

5

0

5

0

5

0

5

контроллеров 3. В каждом контроллере 3 текущее состояние счетчиков 11 адреса сравнивается с кодом системного адреса, установленном на входе 29. так как в каждом из контроллеров код системного адреса уникален по отношению к остальным, то в каждом периоде сигнала синхронизации срабатывает схема 12 сравнения только в одном из контроллеров 3. Именно этот контроллер 3 и получает право передать в магистраль 4 системы одно информационное слово, которое считывается неделимой, минимальной частью сообщения и в дальнейшем называется символом сообщения. Процессоры 2 в рамках рассматриваемой мультипроцессорной системы взаимодействунт посредством сообщений, состоящих из произвольного числа символов. Структура сообщения предполагает, во-первых, что сообщение состоит из двух частей: адресной и информационной; во-вторых, что адресная часть сообщения состоит из символов адресов, т.е. символов, которые при передаче в магистраль 4 системы сопровождаются передачей 1 в линию признака передачи адреса и в младших информационных разрядах содержат адрес контроллера 3, приемник которого является получателем сообщения, причем количество символов в адресной части сообщения соответствует количеству контроллера 3, назначенных получателями сообщения; в-третьих, что информационная часть сообщения состоит из символов данных, первый из которых численно равен числу символов данных в информационной части сообщения.

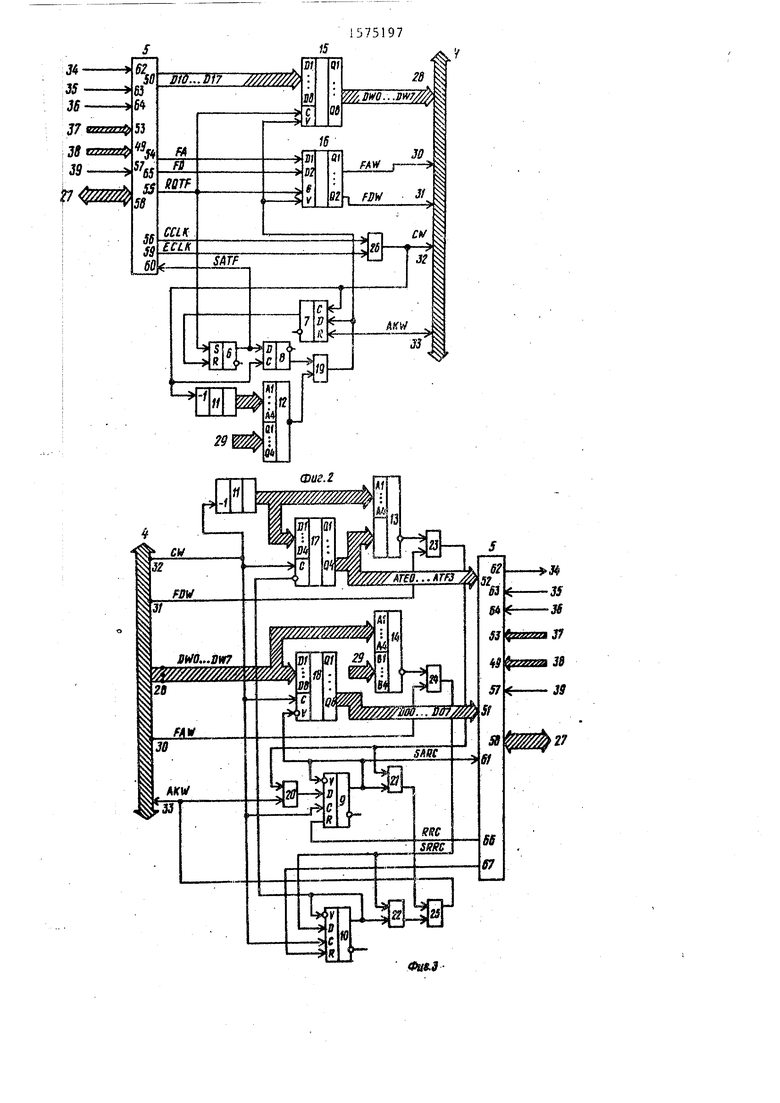

Контроллер 3 с точки зрения связанного с ним посредством узла 5 сопряжения процессора 2 может быть представлен в виде некоторого набора регистров ввода-вывода или набора ячеек памяти. Состав и назначение портов (ячеек памяти) приведены в табл.1. В последнем столбце таблицы указаны адреса портов в системе ввода-вывода процессора 2 на основе магистрали И 41 в соответствии с приведенным на фиг. 4 вариантом исполнения узла 5 сопряжения.

В табл.1 указаны значения младших адресных разрядов портов ввода-вывода, старшие разряды АД2,...,АД7 образуют базовый адрес контроллера 3 в системе ввода-вывода процессора 2

и выбираются посредством установки на входе 49 в узле 5 сопряжения. В табл,2 приведены форматы символа адреса сообщения для мультипроцессорной системы, содержащей 16 процессоров . и слова состояния контроллера 3.

В табл. 3 приведены форматы слова состояния.

Функционально контроллер 3 может быть представлен в виде двух независимых частей: передатчика (фиг,2) и приемника (фиг.З), обеспечивающих возможность одновременно быть источником и получателем сообщений.

В режиме передачи сообщения контроллер работает следующим образом.

Предназначенное для передали сообщение хранится в последовательных ячейках памяти процессора 2, определенных при создании конкретного программного обеспечения в качестве буфера передачи. По заполнении буфера передачи процессор 2 выполняет операцию записи первого символа сообщения, который всегда должен быть символом адреса, в порт символа адреса контроллера 3,

При выполнении данной операции во никнет единица на выходе 55 узла 5 сопряжения, которая записывает значения поступающих с выхода 50 узла сопряжения сигналов, соответствующие содержанию передаваемого символа, в регистр 15 передатчика, нулевое значение сигнала признака передачи - данных и единичное значение сигнала признака передачи адреса в регистр 16 признаков, а также устанавливает триг гер 6 в состояние 1. С выхода триггера 6 сигнал 1 поступает на вход 60 состояния передатчика узла сопряжения, свидетельствуя о неготовности передатчика для передачи нового символа сообщения, и ближайшим импульсом синхронизации записывается в триггер 8, обеспечивая синхронизацию момента активизации передатчика с моментом изменения состояния счетчика 11 адреса.

Сигнал I с выхода триггера 8 открывает элемейт И 19, через который при равенстве выходного кода счетчика адреса к кода системного адреса на входе 29, имеющем место на входах схемы 12 сравнения, единица с выхода последней разрешает передачу содержимого регистров 15 передатчика и 16 признаков

1575197и

в магистраль 4 и, поступая на информационный вход триггера 7, подготавливает его переключение в единичное состояние. При этом, если на вход за- писи нуля триггера 7 с линии подтверждения передачи магистрали 4 через вход-выход 33 поступает сигнал О1

0

5

0

5

Q

свидетельствуя о готовности к приему передаваемого символа всеми получателями сообщения, то ближащий импульс синхронизации записывает в триггер 7 единицу с выхода элемента И 19. Единица с выхода триггера 7 сбрасывает триггер 6 в состояние О. Нуль с выхода триггера 6 ближайшим импульсом синхронизации записывается в триггер 8, переводя передатчик в неактивное состояние и, воздействуя на вход записи единицы триггера 46, устанавливает его с состояние 1, Нуль с инверсного выхода триггера 46 в качестве сигнала залооса прерывания преры- рает выполнение текущей программы процессора 2. При обработке прерывания процессор 2 в качестве обязательной процедуры осуществляет анализ значения сигнала состояния передатчика .

Выполнение команды чтения слова состояния сопровождается возникновением единицы на выходе элемента И 42, сбрасывающей триггер 46 в состояние О. Если значение сигнала состояния передатчика равно нулю, то процессор 2 записывает в порт символа адреса, либо в порт символа данных передатчика очередной симвсл сообщения. Процессор 2 должен обладать способностью определять окончание адресной части сообщения и начало его информационной части, что можно осуществить на программном уровне, например указанием количества символов адреса в адресной

с части сообщения.

Если при передаче символа сообщения хотя бы один из приемников получателей сообщения ке готов, то он вырабатывает в линию подтверждения

0 передачи магистра-ш 4 через вход-выход 33 сигнал , который поступает на вход записи нуля триггера 7, удерживая зго в сброшенном состоянии на время действия очередного импульса синхронизации и, препятствуя, тем самым сбросу.триггера 6, В результате передатчик останется в активном состоянии (триггеры 6 и 8 установлены) и при каждом срабатывании схемы 12

5

0

5

/сравнения осуществляет повторную передачу символа сообщения. Это происходит до тех пор, пока все приемники получатели сообщения в одном сеан- се передачи не окажутся готовыми к приему.

Работа контроллера в режиме при- |ема сообщения.

Для приема сообщений в контролле- (ре 3 предназначен приемник (фиг.З). процессор 2 совместно с приемником контроллера 3 образует получатель Сообщения. Приемник в контроллере 3 |может находиться в одном из следую- |щих трех состояний: ожидание сообще- ,ния (W1ME), когда триггеры 9 и 10 сбропг нн в состояние О и приемник Доступен для соответствующего ему первого символа адреса, передаваемого от любого источника системы; захват сообщения (TRME)f когда триггер 9 сброшен, триггер 10 установлен в состояние и приемник доступен для приема одного символа данных от за- хватившего его источника сообщения (от источника первым передававшим в приемник соответствующий символ адреса) ; блокировка сообщения (DEME), когда триггеры 9 и 10 установлены в состояние 1 и регистр 18 приемника занят.

Переходы между состояниями приемника отражены на диаграмме состояний приемника (фиг.5). В состояние TRIE, поскольку триггеры 9 и 10 сброшены, то в регистры адреса 17 и приемника 18 импульсами синхронизации записываются значения соответственно выходных сигналов счетчика 1 ад- реса и сигналов, поступающих на информационные вход-выход 28. Поскольку запись содержимого счетчика 11 адреса в регистр 17 адреса и переключение счетчика 11 адреса осуществляется одним и тем же сигналом, то обеспечивается гарантированное неравенство кодов на входах схемы 13 сравнения, а следовательно, невосприятие символов данных, передаваемых в магист- раль.Втоже время схема 14 сравнения постоянно сравнивает значения сигналов, поступающих на инАормацион- ный вход-выход 28 с кодом системного адреса на входе 29 контроллера 3, ко- торому принадлежит приемник. Если коды равны, то единица с выхода схемы 14 сравнения открывает элемент И 24. В магистраль 4 в это время передается признак адреса, о чем свидетельствует поступление на второй вход элемента И 24 единицы с линии признака передачи адреса магистрали. При этом единица с выхода элемента И 24 ближайшим импульсом синхронизации записывается в триггер 10, переводя приемник в состояние TRME. При этом единица с выхода триггера 10, во-первых, поступая на входы управления триггера 10 и регистра 17 адреса, запрещает изменение состояния триггера 10 посредством записи информации с его информационного входа и запись в регистр 17 адреса, фиксируя в нем таким образом содержимое счетчика 11 адреса, при котором передавался принятый символ адреса, во-вторых обеспечивает выработку сигнала неготовности приемника при передаче в магистрали обращенного к нему символа адреса от некоторого другого источника. При этом единица с выхода схемы 14 сравнения открывает элемент И 24, а единица с выхода триггера 10 открывает элемент И 22. В результате единица, поступая с входа- выхода 30, через элементы И 24. И 22 и ИЛИ 25 придет на вход записи нуля триггера 7 в источнике сообщения и будет препятствовать изменению его состояния, что обусловливает повторную передачу. Таким образом, если приемник находится в состоянии ТКМЕ, то никакой источник в системе, кроме источника, системный адрес которого зафиксирован в регистре 17 адреса не может передать ему свое сообщение, т.е. в системе поддерживается принцип неразрывности сообщений. Источник сообщения, последовательно передавая символы адреса нескольких приемников (получателей), может адресовать сообщения сразу нескольким процессорам 2, При этом уже захваченные приемники никак не будут реагировать на передачу символов адреса от захватившего их источника, поскольку символ адреса сопровождается передачей нуля в линии признака передачи данных, который поступая на вход-выход 31, блокирует передачу единицы на выход элемента И 23, обеспечивая прием каждого символа данных от захвативщего их источника.

Из состояния т ME приемник может перейти лишь в состояние DEME, что осуществляется приемом в регистр 18

приемника символа-данных от источника, адрес которого зафиксирован в регистре 17 адреса. В таком случае срабатывает схема 13 сравнения, единица с выхода которой открывает элемент И 23, и если в линии признака передачи данных имеет место единица, свидетельствующая о передаче в магистрали символа данных, то она через элементы И 23 и И 20 записывается в триггер 9. Единица с выхода триггера 9, во-первых блокирует запись в триггер 9 и в регистр 19 приемника, фиксируя в нем информационное значение принятого символа данных, во-вторых открывает элемент И 21, обеспечивая выработку через элементы И 21 и 23 и ИЛИ 25 единицы в линию подтверждения передачи магистрали, свидетельствующую о блокировке приемника, такая ситуация возможна, когда источник сообщения передает очередно символ данных, а регистр 18 приемника еще занят предыдущим символом данных, в-третьих устанавливает триггер 46 узла 5 сопряжения в состояние выработки сигнала запроса прерывания и поступает в соответствующий разряд порта слова состояния контроллера. Если при передаче символа данных от источника одновременно к нескольким получателям по крайней мере один из них находится в состоянии DEME, то единица с линии подтверждения передачи магистрали 4 через входы-выходы 33 воздействует на инвертирующие входы элементов И 20, препятствуя приему символа данных, который осуществляется только тогда, когда приемники всех получателей сообщения приняли состояние TRME. Из состояния DEME приемник переходит либо в состояние UIME, когда процессор 2 читает регистр 18 приемника через порт конечного символа сообщения с выработкой на выходах элементов И 45 и 41 единичных значений сигналов, либо в состояние TRME, когда процессор 2 читает регистр 18 приемника через порт текущего символа сообщения с выработкой единичного значения сигнала на выходе элемента И 45. В первом случае сбрасываются оба триггера 9 и 10, а во втором - только триггер 9.

Формула изобретения

Контроллер для связи процессоров с общей магистралью, содержащий реO

5

0

5

0

5

0

5

0

5

гистр передатчика, узел сопряжения, регистр признаков, пять триггеров, регистр приемника, регистр адреса, первую и вторую схемы сравнения, счетчик адреса, шесть элементов И, элемент ИЛИ и усилитель-формирователь, причем информационный вход регистра передатчика подключен к информационному выходу узла сопряжения, информационный вход-выход узла сопряжения является первым информационным входом-выходом контроллера, выход регистра передатчика соединен с информационным входом регистра приемника, первым входом первой схемы сравнения и вторым информационным входом-выходом контроллера, выход регистра приемника подключен к информационному входу узла сопряжения, второй вход первой схемы сравнения соединен с первым входом второй схемы сравнения и входом установки системного адреса контроллера, второй вход второй схемы сравнения подключен к выходу счетчика адреса и информационному входу регистра адреса, выход которого соединен с первым адресным входом узла сопряжения, выход признака передачи адреса узла сопряжения подключен к первому информационному входу регистра признаков, первый выход которого соединен с входом-выходом признака передачи адреса контроллера, выход запроса передачи узла сопряжения подключен к входу записи регистра признаков, входу записи регистра передатчика и входу установки в 1 первого триггера, . выход первой схемы сравнения соединен с первым входом первого элемента И, выход второй схемы сравнения подключен к первому входу второго элемента И, выход которого соединен с входом управления выходом регистра передатчика, входом управления и выходом регистра признаков, выход синхронизации узла сопряжения подключен к информационному входу усилитель-формирователя, вход синхронизации узла сопряжения является входом4 синхронизации контроллера,выход управления синхронизацией узла сопряжения соединен с управляющим входом усилителя-формирователя, выход которого подключен к счетному входу счетчика адреса, входу синхронизации регистра адреса, входу синхронизации регистра приемника и входу-выходу синхронизации контроллера, выход

первого триггера соединен с входом состояния передатчика узла сопряжения, выход второго триггера подключен к входу состояния приемника узла сопряжения и первому входу третьего элемента И, выход запроса прерывания узла сопряжения является выходом Запроса прерывания контроллера, вход записи узла сопряжения является.входом записи контроллера, вход считывания узла сопряжения является входом Считывания контроллера, второй адресной вход узла сопряжения является адресным входом контроллера, вход установки базового адреса узла сопря- ж|ения является входом установки базового адреса контроллера, о т л и - ч ающийся тем, что, с целью р|асширения области применения конт- рЬллера за счет возможности переда- ч сообщений от источника к несколь- ирм получателям, в него введена тре- т|ья схема сравнения, причем первый вход третьей схемы сравнения подключен к выходу счетчика адреса, второй третьей схемы сравнения соединен с выходом регистра адреса, выход третьей схемы сравнения подключен к первому входу четвертого элемен- т& И, второй вход которого соединен с вторым выходом регистра признаков и входом-выходом признака передачи данных контроллера, второй информационный вход регистра признаков подключен к выходу признака передачи данных узла сопряжения, второй вход первогопэлемента И соединен с первым выходом регистра признаков, вход записи нуля первого триггера подклю- чйн к выходу третьего триггера, вход синхронизации третьего тоиггепя соели0

3

0

5

0

5

0

нен с входом синхронизации четвертого триггера, входам синхронизации второго триггера, входом синхронизации пятого триггера и счетным входом счетчика адреса, информационный вход четвертого N триггера подключен к выходу первого триггера, выход четвертого триггера соединен с вторым входом второго элемента И, информационный вход третьего триггера подключен к выходу второго элемента И, вход записи нуля третьего триггера соединен с выходок элемента ИЛИ, инверсным входом пятого элемнта И и входом-выходом подтверждения передачи контроллера, выход четвертого элемента Ч подключен к прямому входу пятого элемента И и второму входу третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, выход пятого элемента И подключен к информационному входу второго триггера, вход управления записью которого соединен с первым входом третьего элемента И и. входом управления записью регистра приемника, выход первого элемента И подключен к информационному входу пятого триггера и первому входу шестого элемента И, выход которого соединен с вторым входом элемента ИЛИ второй вход шестого элемента И подключен к выходу пятого триггера, входу управления записью пятого триггера и входу управления записью регистра адреса, вход записи нуля второго триггера соединен с первым выходом режима чтения узла сопряжения, вход записи нуля пятого триггера подключен к второму выходу режима чтения узла сопряжения.

Таблица 1

Таблица2

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1658159A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU1275453A1 |

| Устройство для сопряжения абонентов с каналом передачи данных | 1987 |

|

SU1444791A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих мультипроцессорных систем с общей магистралью. Целью изобретения является расширение области применения контроллера за счет передачи сообщений от источника к нескольким получателям. Поставленная цель достигается тем, что в контроллер, содержащий регистр передатчика, узел сопряжения, регистр признаков, пять триггеров, регистр приемника, регистр адреса, первую и вторую схемы сравнения, счетчик адреса, шесть элементов И, элемент ИЛИ и усилитель - формирователь, введена третья схема сравнения. 5 ил.

Адрес контроллера 3 связи, Резервные разряды

получателя сообщения

Порт принятого символа содержит символ сообщения (готовность приемника)

Порт принятого символа пуст (неготовность приемника)

Порты передатчика (символа адреса или символа данных) занят (неготовность передатчика)

Порты передатчика свободны (готовность передатчика)

Т

ТаблицаЗ

Фиг.1

575197

Фи&Э

si6...w fy/7///////y/////Mmr/fa

дат $fr

MTF

ШС

wo....

ULK

«K.4

Редактор Ю. Середа

Составитель В. ЕСИПОБ

Техред М.Ходанич Корректор Э. Лончакова

Ш...Ш7

Приен сим8ом- адреса Ј регистр прценнш

Прием сип до на данных 8 ре- штр приемника

Фиг, 5

| Каган Б.М | |||

| и Сташин В.В | |||

| Основы проектирования микропроцессорных устройств автоматики | |||

| М.: Энергоатомич- дат, 1987, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Патент С ЧА № 4223380, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-23—Подача