нения, состоящий из счетчика 35ч адре- JQ импульсов - для дискретизирования не

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Устройство прямого доступа в память ЭВМ | 1988 |

|

SU1689957A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

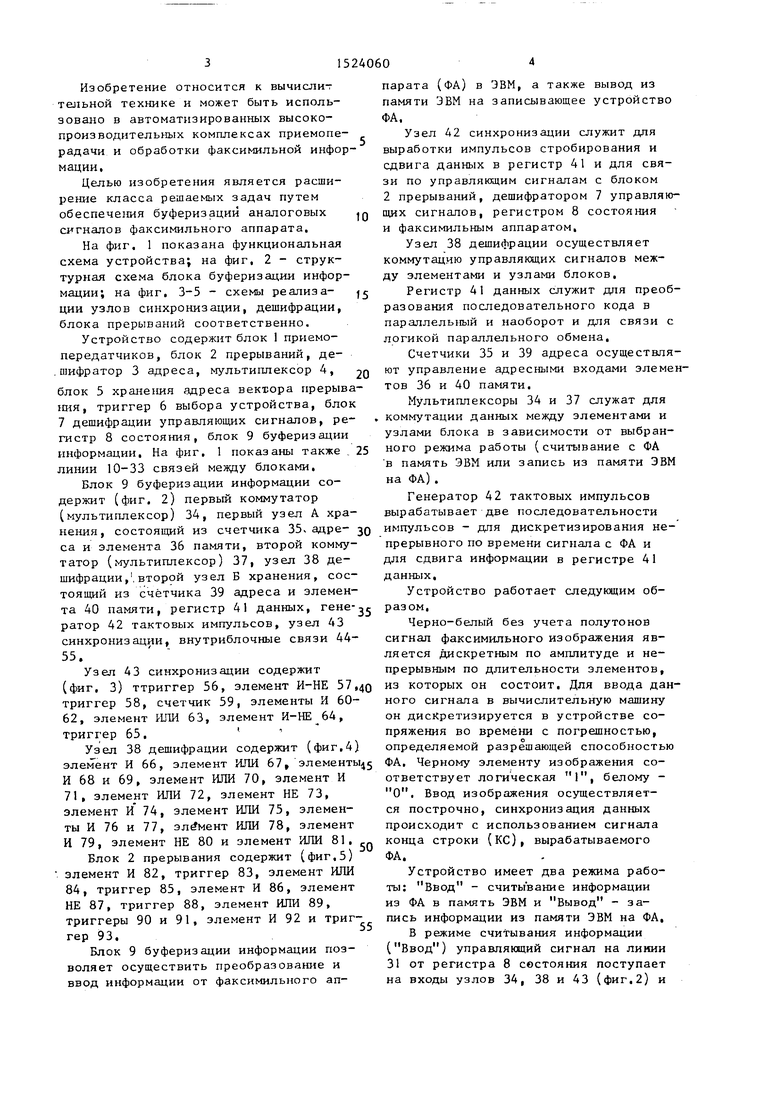

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных высокопроизводительных комплексах приемо-передачи и обработки факсимильной информации. Цель изобретения - расширение класса решаемых задач устройства путем обеспечения буферизации данных, а также исключения жесткой синхронизации между моментами поступления информации в регистр ввода и считывания ее центральным процессом. Для этого в устройство, содержащее блок приемопередатчиков, блок прерываний, дешифратор адреса, мультиплексор 4, блок хранения адреса вектора прерывания, триггер выбора устройства, блок дешифрации управляющих сигналов и регистр 8 состояния, введен блок буферизации информации, состоящей из двух коммутаторов, двух узлов хранения, узла дешифрации, узла синхронизации, генератора тактовых импульсов и регистра данных. Устройство имеет два режима работы - считывания информации из факсимильного аппарата в память ЭВМ и вывод из памяти ЭВМ на факсимильный аппарат. 5 ил.

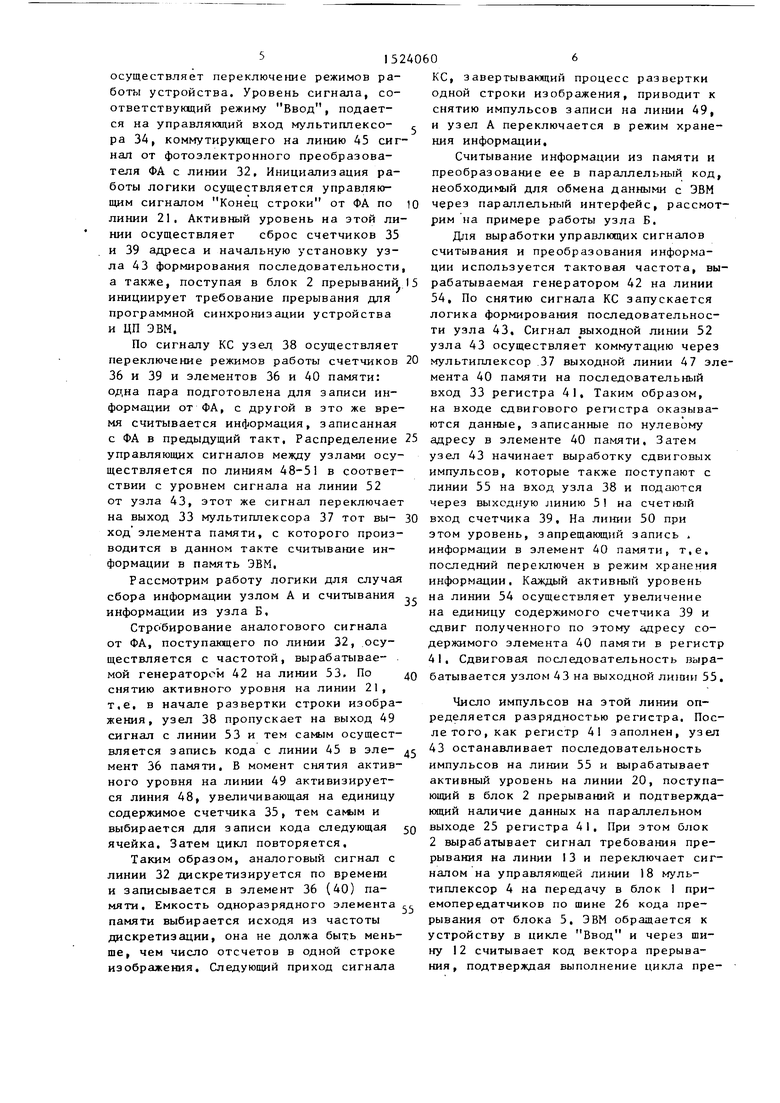

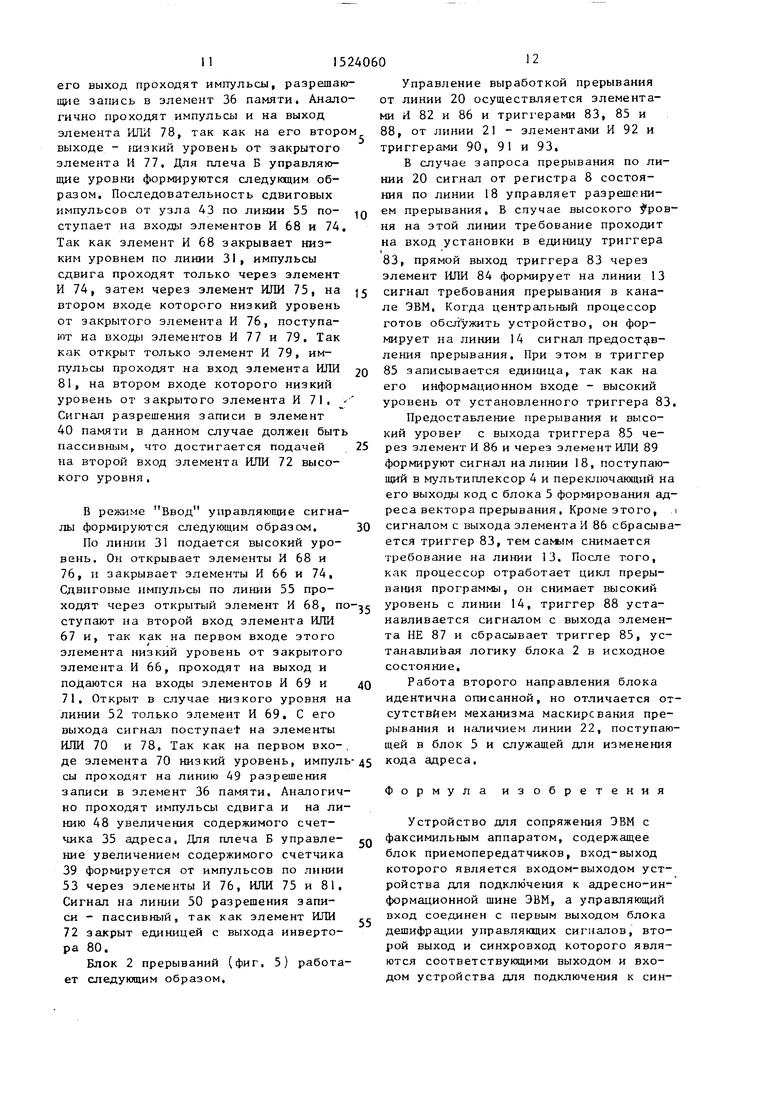

са и элемента 36 памяти, второй коммутатор (мультиплексор) 37, узел 38 дешифрации,, второй узел Б хранения, состоящий из счётчика 39 адреса и элемента 40 памяти, регистр 4 данных, гене- с разом, ратор 42 тактовых импульсов, узел 43 синхронизации, внутриблочные связи 44- 55.

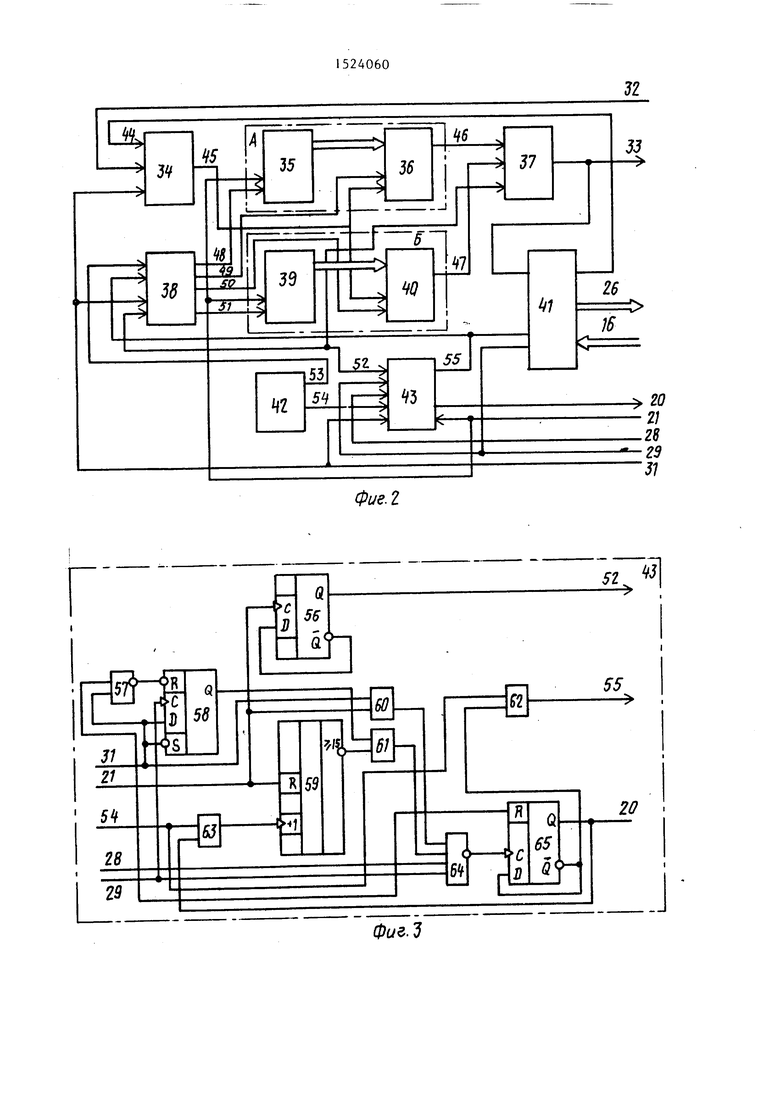

Узел 43 синхронизации содержит

Черно-белый без учета полутонов сигнал факсимильного изображения является дискретным по амплитуде и непрерывным по длительности элементов.

(фиг, 3) ттриггер 56, элемент И-НЕ 57,49 из которых он состоит. Для ввода дан- триггер 58, счетчик 59, элементы И 60- 62, элемент ИЛИ 63, элемент И-НЕ 64, триггер 65, л

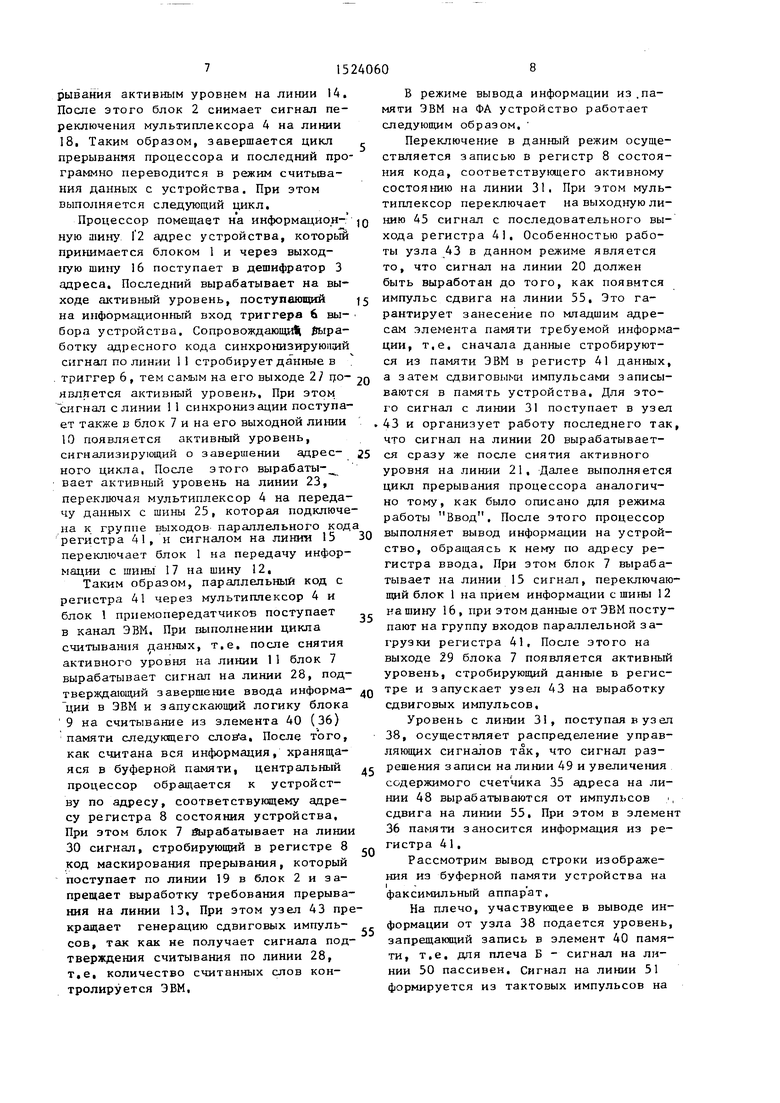

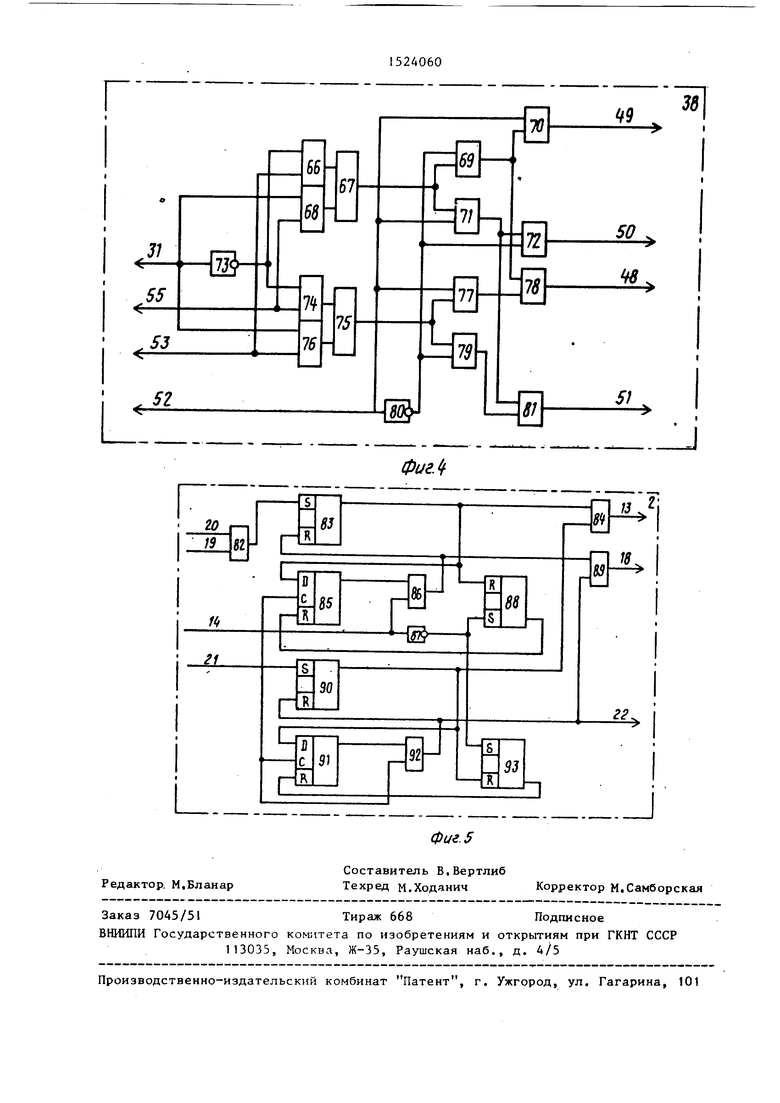

Узел 38 дешифрации содержит (фиг,4) элемент И 66, элемент ИЛИ 67, элементы 5 ФА. Черному элементу изображения соного сигнала в вычислительную машину он дисКретизируется в устройстве сопряжения во времени с погрешностью, определяемой разрешающей способностью

И 68 и 69, элемент ИЛИ 70, элемент И 71, элемент ИЛИ 72, элемент НЕ 73, элемент И 74, элемент ИЛИ 75, элементы И 76 и 77, элемент ИЛИ 78, элемент И 79, элемент НЕ 80 и элемент ЯПИ 81,

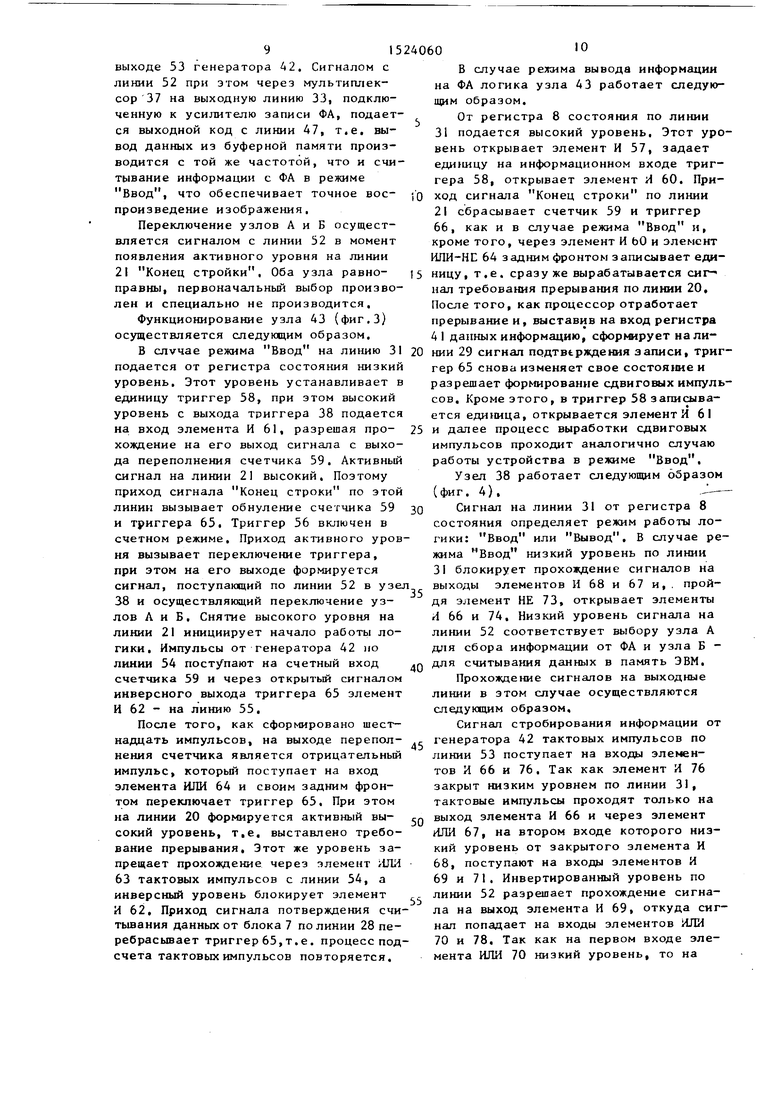

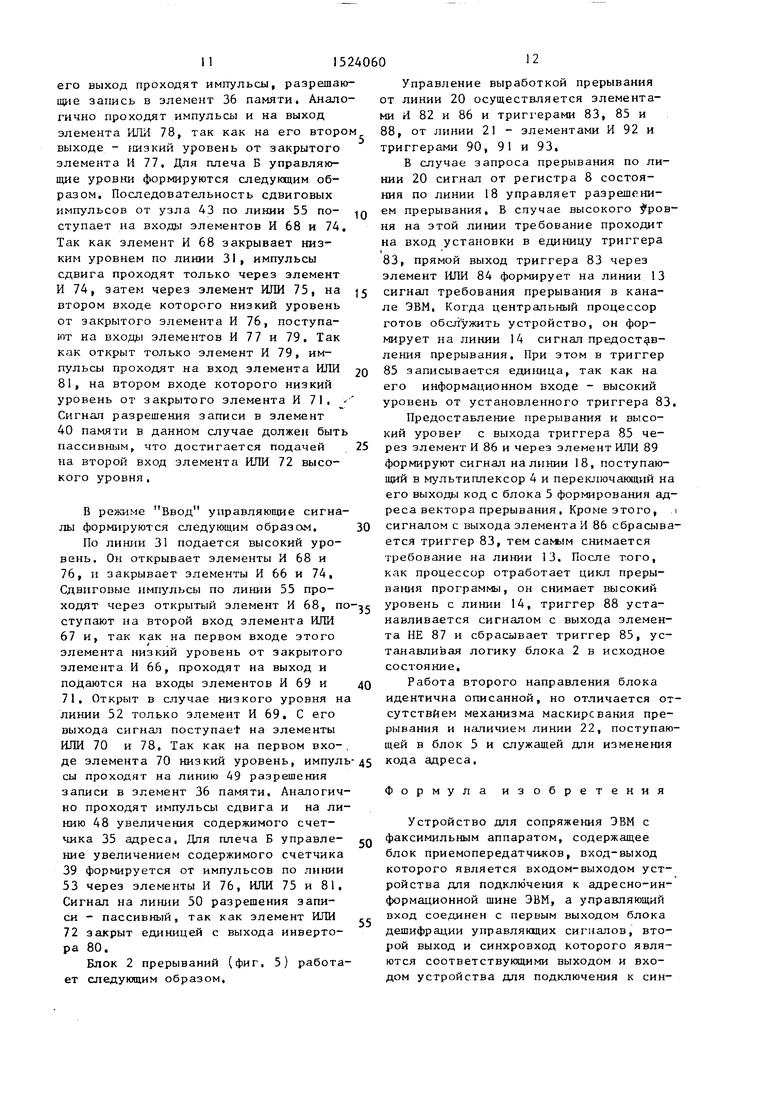

Блок 2 прерывания содержит (фиг,5) элемент И 82, триггер 83, элемент ИЛИ 84, триггер 85, элемент И 86, элемент НЕ 87, триггер 88, элемент ИЛИ 89, триггеры 90 и 91, элемент И 92 и триг гер 93,

Блок 9 буферизации информации позволяет осуществить преобразование и ввод информации от факсимильного ап55

ответствует логическая 1, белому - О. Ввод изображения осуществляется построчно, синхронизация данных происходит с использованием сигнала конца строки (КС), вырабатываемого ФА,

Устройство имеет два режима работы: Ввод - считывание информации из ФА в память ЭВМ и Вывод - запись информации из памяти ЭВМ на ФА,

В режиме считывания информации (Ввод) управляющий сигнал на линии 31 от регистра 8 состояния поступает на входы узлов 34, 38 и 43 (фиг,2) и

прерывного по времени сигнала с ФА и для сдвига информации в регистре 41 данных.

Устройство работает следукяцим образом,

Черно-белый без учета полутонов сигнал факсимильного изображения является дискретным по амплитуде и непрерывным по длительности элементов.

из которых он состоит. Для ввода дан-

ФА. Черному элементу изображения соного сигнала в вычислительную машину он дисКретизируется в устройстве сопряжения во времени с погрешностью, определяемой разрешающей способностью

5

ответствует логическая 1, белому - О. Ввод изображения осуществляется построчно, синхронизация данных происходит с использованием сигнала конца строки (КС), вырабатываемого ФА,

Устройство имеет два режима работы: Ввод - считывание информации из ФА в память ЭВМ и Вывод - запись информации из памяти ЭВМ на ФА,

В режиме считывания информации (Ввод) управляющий сигнал на линии 31 от регистра 8 состояния поступает на входы узлов 34, 38 и 43 (фиг,2) и

осуществляет переключение режимов работы устройства. Уровень сигнала, со- ответствумций режиму Ввод, подается на управляющий вход мультиплексо- ра 34, коммутирующего на линию 45 сигнал от фотоэлектронного преобразователя ФА с линии 32, Инициализация работы логики осуществляется управляющим сигналом Конец строки от ФА по линии 21, Активный уровень на этой линии осуществляет сброс счетчиков 35 и 39 адреса и начальную установку узла 43 формирования последовательности а также, поступая в блок 2 прерываний инициирует требование прерывания для программной синхронизации устройства и ЦП ЭВМ.

По сигналу КС узел. 38 осуществляет переключение режимов работы счетчиков 36 и 39 и элементов 36 и 40 памяти: одна пара подготовлена для записи информации от ФА, с другой в это же время считывается информация, записанная с ФА в предыдущий такт. Распределение управляющих сигналов между узлами осуществляется по линиям 48-51 в соответствии с уровнем сигнала на линии 52 от узла 43, этот же сигнал переключает на выход 33 мультиплексора 37 тот вы- ход элемента памяти, с которого производится в данном такте считывание информации в память ЭВМ,

Рассмотрим работу логики для случая сбора информации узлом А и считывания информации из узла Б,

Стробирование аналогового сигнала от ФА, поступающего по линии 32, осуществляется с частотой, вырабатываемой генератором 42 на линии 53. По снятию активного уровня на линии 21, т.е, в начале развертки строки изображения, узел 38 пропускает на выход 49 сигнал с линии 53 и тем самым осуществляется запись кода с линии 45 в эле- мент 36 памяти, В момент снятия активного уровня на линии 49 активизируется линия 48, увеличивающая на единицу содержимое счетчика 35, тем и выбирается для записи кода следующая ячейка. Затем цикл повторяется.

Таким образом, аналоговый сигнал с линии 32 дискретизируется по времени и записывается в элемент 36 (40) памяти. Емкость одноразрядного элемента памяти выбирается исходя из частоты дискретизации, она не должа быть меньше, чем число отсчетов в одной строке изображения. Следующий приход сигнала

КС, 3авертывающи11 процесс развертки одной строки изображения, приводит к снятию импульсов записи на линии 49, и узел А переключается в режим хранения информации.

Считывание информации из памяти и преобразование ее в параллельный код, необходимый для обмена данными с ЭВМ через параллельный интерфейс, рассмотрим на примере работы узла Б.

Для выработки управлющих сигналов считывания и преобразования информации используется тактовая частота, вырабатываемая генератором 42 на линии 54, По снятию сигнала КС запускается логика формирования последовательности узла 43, Сигнал выходной линии 52 узла 43 осуществляет коммутацию через мультиплексор 37 выходной линии 47 элмента 40 памяти на последовательный вход 33 регистра 41, Таким образом, на входе сдвигового регистра оказываются данные, записанные по нулевому адресу в элементе 40 памяти. Затем узел 43 начинает выработку сдвиговых импульсов, которые также поступают с линии 55 на вход узла 38 и подаются через выходную линию 51 на счетный вход счетчика 39, На линии 50 при этом уровень, запрещающий запись . информации в элемент 40 памяти, т,е, последний переключен в режим хранения информации. Каждый активный уровень на линии 54 осуществляет увеличение на единицу содержимого счетчика 39 и сдвиг полученного по этому адресу содержимого элемента 40 памяти в регистр 41, Сдвиговая последовательность вырабатывается узлом 43 на выходной ли}ши 55

Число импульсов на этой линии определяется разрядностью регистра. После то го, как регистр 41 заполнен, узел 43 останавливает последовательность импульсов на линии 55 и вырабатывает активный уровень на линии 20, поступающий в блок 2 прерываний и подтверждающий наличие данных на параллельном выходе 25 регистра 41, При этом блок 2 вырабатывает сигнал требования прерывания на линии I3 и переключает сигналом на управляющей линии 18 мультиплексор 4 на передачу в блок 1 приемопередатчиков по шине 26 кода прерывания от блока 5, ЭВМ обращается к устройству в цикле Ввод и через шину 12 считывает код вектора прерывания, подтверждая выполнение цикла прерывания активным уровнем на линии 1А, После этого блок 2 снимает сигнал переключения мультиплексора 4 на линии 18, Таким образом, завершается цикл прерывания процессора и последний программно переводится в режим считьша- ния данных с устройства. При этом выполняется следующий цикл.

Процессор помещает на информацион- ную шину 12 адрес устройства, который принимается блоком 1 и через выход- 1гую ши1гу 16 поступает в дешифратор 3 адреса. Последний вырабатывает на выходе активный уровень, поступаншщй на информационный вход триггера 6 вы- бора устройства. Сопровождающей &ыра- бот1су адресного кода синхронизируюилй сигнал по линии 1 1 стробирует данные в . триггер 6, тем самым на его выходе 21 цо- является активный уровень. При этом. ciirHan с линии 1 1 синхронизации поступает также в блок 7 и на его выходной линии 10 появляется активный уровень, сигнализирующий о завершении адрес- ного цикла, После этого вырабаты- вает активный уровень на линии 23, переключая мультиплексор 4 на передачу данных с шины 25, которая подключена к группе выходов параллельного код регистра А1, и сигналом на линии 15 переключает блок 1 на передачу информации с шины 17 на шину 12,

Таким образом, параллельный код с регистра 41 через мультиплексор 4 и блок 1 приемопередатчиков поступает в канал ЭВМ, При выполнении цикла считывания данных, т,е, после снятия активного уровня на линии 11 блок 7 вырабатывает сигнал на линии 28, подтверждающий завершение ввода информа- ции в ЭВМ и запускающий логику блока 9 на считывание из элемента 40 (36) памяти следующего слов а. После того, как считана вся информация, хранящаяся в буферной памяти, центральный процессор обращается к устройству по адресу, соответствующему адресу регистра 8 состояния устройства. При этом блок 7 вырабатывает на линии 30 сигнал, стробирующий в регистре 8 код маскирования прерывания, который поступает по линии 19 в блок 2 и запрещает выработку требования прерывания на линии 13, При этом узел 43 прекращает генерацию сдвиговых импуль- сов, так как не получает сигнала подтверждения считывания по линии 28, т,е, количество считанных слов контролируется ЭВМ,

В режиме вывода информации из .памяти ЭВМ на ФА устройство работает следующим образом,

Переключение в данный режим осуществляется записью в регистр 8 состояния кода, соответствующего активному состоянию на линии 31 При этом мультиплексор переключает на выходную линию 45 сигнал с последовательного выхода регистра 41, Особенностью работы узла 43 в данном режиме является то, что сигнал на линии 20 должен быть выработан до того, как появится импульс сдвига на линии 55, Это гарантирует занесение по младшим адресам элемента памяти требуемой информации, т,е, сначала данные стробируют- ся из памяти ЭВМ в регистр 41 данных, а затем сдвиговыьи импульсами записываются в память устройства. Для этого сигнал с линии 31 поступает в узел 43 и организует работу последнего так что сигнал на линии 20 вырабатывается сразу же после снятия активного уровня на линии 21, Далее выполняется цикл прерывания процессора аналогично тому, как было описано для режима работы Ввод, После этого процессор выполняет вывод информации на устройство, обращаясь к нему по адресу регистра ввода. При этом блок 7 вырабатывает на линии 15 сигнал, переключающий блок 1 на прием информации с шины 12 на шину 16 , при этом данные от ЭВМ поступают на группу входов параллельной загрузки регистра 41, После этого на выходе 29 блока 7 появляется активный уровень, стробирующий данные в регистре и запускает узел 43 на выработку сдвиговых импульсов.

Уровень с линии 31, поступая в узел 38, осуществляет распределение управляющих сигналов так, что сигнал разрешения записи на линии 49 и увеличения содержимого счетчика 35 адреса на линии 48 вырабатываются от импульсов сдвига на линии 55, При этом в элемен 36 памяти заносится информация из регистра 4 1,

Рассмотрим вывод строки изображения из буферной памяти устройства на I -,

факсимильный аппарат.

На плечо, участвукщее в выводе информации от узла 38 подается уровень, запрещающий запись в элемент 40 памяти, т,е, для плеча Б - сигнал на линии 50 пассивен. Сигнал на линии 51 формируется из тактовых импульсов на

выходе 53 генератора 42. Сигналом с линии 52 при этом через мультиплексор 37 на выходную линию 33, подключенную к усилителю записи ФА, подается выходной код с линии 47, т.е. вывод данных из буферной памяти производится с той же частотой, что и считывание информации с ФА в режиме Ввод, что обеспечивает точное вое- произведение изображения.

Переключение узлов А и Б осуществляется сигналом с линии 52 в момент появления активного уровня на линии 21 Конец стройки. Оба узла равно- правны, первоначальный выбор произволен и специально не производится.

Функционирование узла 43 (фиг.З) осуществляется следующим образом.

В случае режима Ввод на линию 31 подается от регистра состояния низкий уровень. Этот уровень устанавливает в единицу триггер 58, при этом высокий уровень с выхода триггера 38 подается на вход элемента И 61, разрешая про- хозкдение на его выход сигнала с выхода переполнения счетчика 59. Активный сигнал на линии 21 высокий. Поэтому приход сигнала Конец строки по этой линии вызывает обнуление счетчика 59 и триггера 63. Триггер 56 включен в счетном режиме. Приход активного уровня вызывает переключение триггера, при этом на его выходе формируется сигнал, поступающий по линии 52 в узел 38 и осуществляющий переключение узлов А и Б. Снятие высокого уровня на линии 21 инициирует начало работы логики. Импульсы от генератора 42 по линии 54 поступают на счетный вход счетчика 59 и через открытый сигналом инверсного выхода триггера 65 элемент И 62 - на линию 55.

После того, как сформировано шестнадцать импульсов, на выходе перепол- нения счетчика является отрицательный импульс, которьй поступает на вход элемента ИЛИ 64 и своим задним фронтом переключает триггер 65. При этом на линии 20 формируется активный вы- сокий уровень, т.е. выставлено требование прерывания. Этот же уровень запрещает прохождение через элемент iUIH 63 тактовых импульсов с линии 54, а инверсный уровень блокирует элемент И 62, Приход сигнала потверждения считывания данных от блока 7 по линии 28 перебрасывает триггер 65,т.е. процесс подсчета тактовых импульсов повторяется.

Q

5

0 5 о Q

,. Q

5

В случае режима вывода информации на ФА логика узла 43 работает следующим образом.

От регистра 8 состояния по линии 31 подается высокий уровень. Этот уровень открывает элемент И 57, задает единицу на информационном входе триггера 58, открывает элемент И 60. Приход сигнала Конец строки по линии 21 сбрасывает счетчик 59 и триггер 66, как и в случае режима Ввод и, кроме того, через элемент И 60 и элемент ИЛИ-НС 64 задним фронтом записывает единицу, т.е. сразу же вырабатывается сиг-- нал требования прерывания по линии 20, После того, как процессор отработает прерывание и, выставив на вход регистра 41 данных информацию, сформирует на линии 29 сигнал подтвьрждення записи, триггер 65 снова изменяет свое состоя ие и разрешает формирование сдвиговых импульсов. Кроме этого, в триггер 58 записывается единица, открывается элемент И 61 и далее процесс выработки сдвиговых импульсов проходит аналогично случаю работы устройства в режиме Ввод.

Узел 38 работает следующим образом (фиг. 4),

Сигнал на линии 31 от регистра 8 состояния определяет режим работы логики: Ввод или Вывод. В случае режима Ввод низкий уровень по линии 31 блокирует прохождение сигналов на выходы элементов Н 68 и 67 и,. пройдя элемент НЕ 73, открывает элементы И 66 и 74. Низкий уровень сигнала на линии 52 соответствует выбору узла А для сбора информации от ФА и узла Б - для считывания данных в память ЭВМ.

Прохождение сигналов на выходные линии в этом случае осуществляются следующим образом,

Сигнал стробирования информации от генератора 42 тактовых импульсов по линии 53 поступает на входы элементов И 66 и 76. Так как элемент И 76 закрыт низким уровнем по линии 31, тактовые импульсы проходят только на выход элемента И 66 и через элемент ИЛИ 67, на втором входе которого низкий уровень от закрытого элемента И 68, поступают на входы элементов И

69и 71. Инвертированный уровень по линии 52 разрешает прохождение сигнала на выход элемента И 69, откуда сигнал попадает на входы элементов ИЛИ

70и 78. Так как на первом входе элемента ИЛИ 70 низкий уровень, то на

его выход проходят импульсы, разрешающие загшсь в элемент 36 памяти. Аналогично проходят импульсы и на выход элемента ИЛИ 78, так как на его второ выходе - шзкий уровень от закрытого элемента И 77, Для плеча Б управляющие уровни формируются следующим образом. Последовательность сдвиговых импульсов от узла 43 по линии 55 поступает на входы элементов И 68 и 74, Так как элемент И 68 закрывает низким уровнем по линии 31, импульсы сдвига проходят только через элемент И 74, затем через элемент ШШ 75, на втором входе которого низкий уровень от закрытого элемента И 76, поступают на входы элементов И 77 и 79, Так как открыт только элемент И 79, импульсы проходят на вход элемента ИЛИ 81, на втором входе которого низкий уровень от закрытого элемента И 71, Сигнал разрешения записи в элемент 40 памяти в данном случае должен быть пассивным, что достигается подачей на второй вход элемента ИЛИ 72 высокого уровня,

В режиме Ввод управляющие сигналы формируются следующим образам.

По ЛИШ1И 31 подается высокий уровень. Он открывает элементы И 68 и 76, и закрывает элементы И 66 и 74, Сдвиговые по линии 55 проходят через открытый элемент И 68, по ступают на второй вход элемента ИЛИ 67 и, так как на первом входе этого элемента низкий уровень от закрытого элемента И 66, проходят на выход и подаются на входы элементов И 69 и 71, Открыт в случае низкого уровня на линии 52 только элемент И 69, С его выхода сигнал поступает на элементы ИЛИ 70 и 78, Так как на первом входе элемента 70 низкий уровень, импуль сы проходят на линию 49 разрешения записи в элемент 36 памяти. Аналогично проходят импульсы сдвига и на линию 48 увеличения содержимого счетчика 35 адреса, Для плеча Б управление увеличением содержимого счетчика 39 формируется от импульсов по линии 53 через элементы И 76, ИЛИ 75 и 81, Сигнал на линии 50 разрешения записи - пассивный, так как элемент ИЛИ 72 закрыт единицей с выхода инвертора 80,

Блок 2 прерываний (фиг, 5) работает следующим образом.

5

0

5

0

О 5

0

5

Управление выработкой прерывания от линии 20 осуществляется элементами И 82 и 86 и триггерами 83, 85 и 88, от линии 21 - элементами И 92 и триггерами 90, 91 и 93,

В случае запроса прерывания по линии 20 сигнал от регистра 8 состояния по линии 18 управляет разрешением прерывания, В случае высокого Уровня на этой линии требование проходит на вход установки в единицу триггера

83, прямой выход триггера 83 через элемент ИЛИ 84 формирует на линии 13 сигнал требования прерывания в канале ЭВМ, Когда центральный процессор готов обслужить устройство, он формирует на линии 14 сигнал предост в- ления прерывания. При этом в триггер 85 записывается единица, так как на его информационном входе - высокий уровень от установленного триггера 83,

Предоставление прерывания и высокий уронен с выхода триггера 85 через элемент И 86 и через элемент ИЛИ 89 формируют сигнал на линии 18, поступающий в мультиплексор 4 и переключающий на его выходы код с блока 5 формирования адреса вектора прерывания, Кроме этого, I сигналом с выхода элемента И 86 сбрасывается триггер 83, тем casfciM снимается требование на линии 13. После того, как процессор отработает цикл прерывания программы, он снимает высокий уровень с линии 14, триггер 88 устанавливается сигналом с выхода элемента НЕ 87 и сбрасывает триггер 85, устанавливая логику блока 2 в исходное состояние.

Работа второго направления блока идентична описанной, но отличается отсутствием механизма маскирсвания прерывания и наличием линии 22, поступающей в блок 5 и служащей для изменения кода адреса.

Формула изобретения

Устройство для сопряжения ЭВМ с факсимильным аппаратом, содержащее блок приемопередатчи-ков, вход-выход которого является входом-выходом устройства для подключения к адресно-информационной щине ЭВМ, а управляющий вход соединен с первым выходом блока дешифрации управлякщих сигналов, второй выход и синхровход которого являются соответствующими выходом и входом устройства для подключения к сини выходу ЭВМ, мул вторая группы ин

хронизирующим входу типлексор, первая и

формационных входов которого подключены соответственно к группам выходов регистра состояния и блока хранения адреса вектора прерывания, пусковым входом соединенного с первым выходом блока прерываний, второй выход и вход разрешения которого являются соответствующими выходом и входом устройства для подключения к входу запроса прерывания и выходу разрешения прерывания ЭВМ, а третий выход и первый вход запроса прерывания подключены соответственно к первому управляющему входу мультиплексора и первому разря ному выходу регистра состояния, управляющим входом соединенного с третьим выходом блока дешифрации управлющйх сигналов, третий выход и вход разрешения которого соединены соответственно с вторым управляющим входом мультиплексора и выходом триггера выбора устройства, выход мультиплексора подключен к информационному входу блока приемопередатчиков, выход которого соединен с информационными входами регистра состояния, блока де- шифации управляющих сигналов и через дешифратор адреса с информационным входом триггера выбора устройства, синхровход которого соединен с входом устройства для подключения к синхронизирующему выходу ЭВМ, отличающееся тем, что, с целью расширения класса решаемых задач устройства путем обеспечения буфери зации аналоговых сигналов факсимильного аппарата, в него введен блок буфериза- ции информации, включающий регистр данных, узел синхронизации, генератор тактовых импульсов, два узла хранения два коммутатора и узел дешифрации.

причем первый информационный вход пер-дзвания и тактовым входом регистра данвого коммутатора и выход второго ком-ных, разрешающий вход которого подмутатора являются соответствующимиключей к пятому выходу блока дешифравходом и выходом устройства для под-ц и управляющих сигналов, ключения к информационным выходу и

5

0

О

5

0

5

входу факсимильного аппарата, первый и второй информационные входы второго коммутатора соединены соответственно с выходами первого и второго узлов хранения, а управляющий вход и выход - сооветственно с первым выходом узла синхронизации и входом последовательного кода регистра данных, информационные вход и выход параллельного кода которого соединены соответственно с выходом блока приемопередатчиков и третьей группой информационных входов мультиплексора, выход последовательного кода регистра данных подключен к второму информадионному входу первого коммутатора, выходом соединенного с инФормационцыми входами первого и второго узлов хранения, а управ- ляю(цим входом - с вторым разрядным выходом регистра состояния, режимным входом узла синхронизации и первым информационным входом узла дешифрации, первый - четвертый выходы которого соединены соответственно с синхронизирующими и разрешающими входами первого и-второго узлов хранения, входы сброса которого соединены с входом начальной установки узла синхронизации и являются входом устройства для подключения к синхронизирующему выходу факсимильного аппарата, второй и третий информационные входы и синхровход узла дешифрации соединены соответственно с первым и вторым выходами узла синхронизгщии и первым выходом генератора тактовых импульсов, вторым выходом подключенного к тактовому входу узла синхронизации, входы пуска и блокировки, третий и второй .выходы которого соединек.1 соответственно с пятым и шестым выходами блока дешифрации управлягацих сигналов, вторым входом запроса прерывания блока прерыФиг. г

Фие. 5

фиг.1

| Устройство для сопряжения измерительного прибора с цифровой вычислительной машиной | 1975 |

|

SU552601A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-28—Подача