Изобретение относится к вычислительной технике, в частности к-устройствам для обмена данными, и может быть использовано в качестве блока передачи данных в каналах ввода-вывода.

Цель изобретения - повьшение пропускной способности устройства.

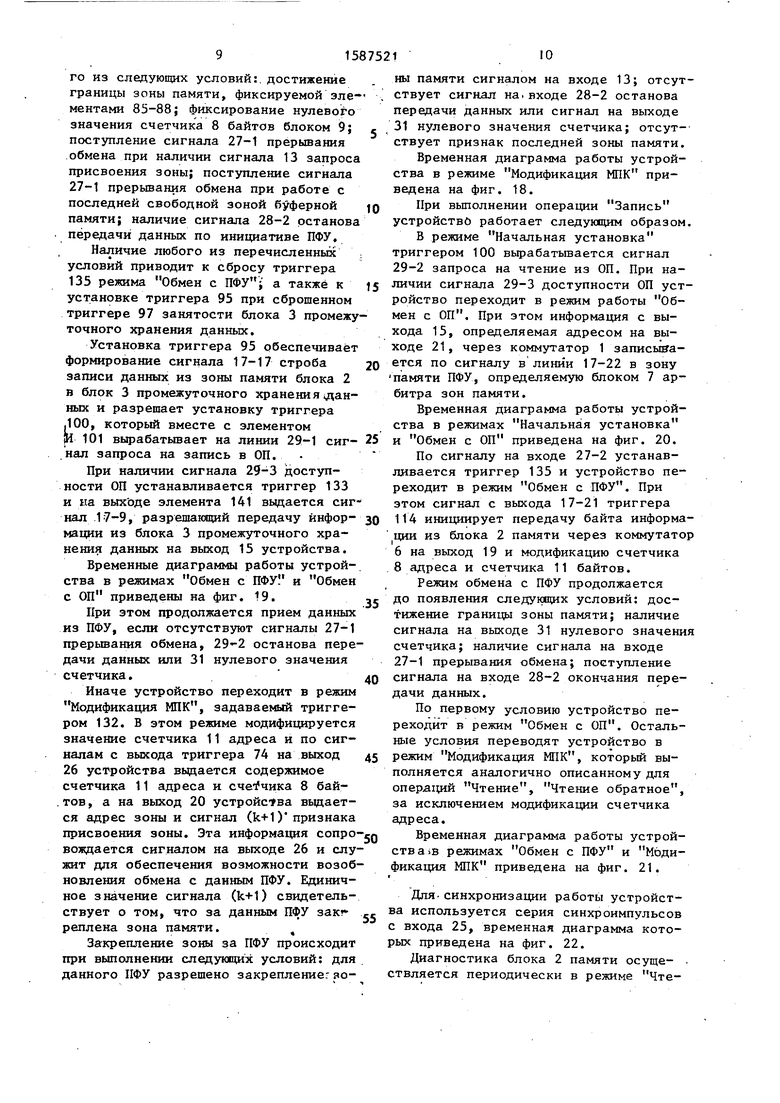

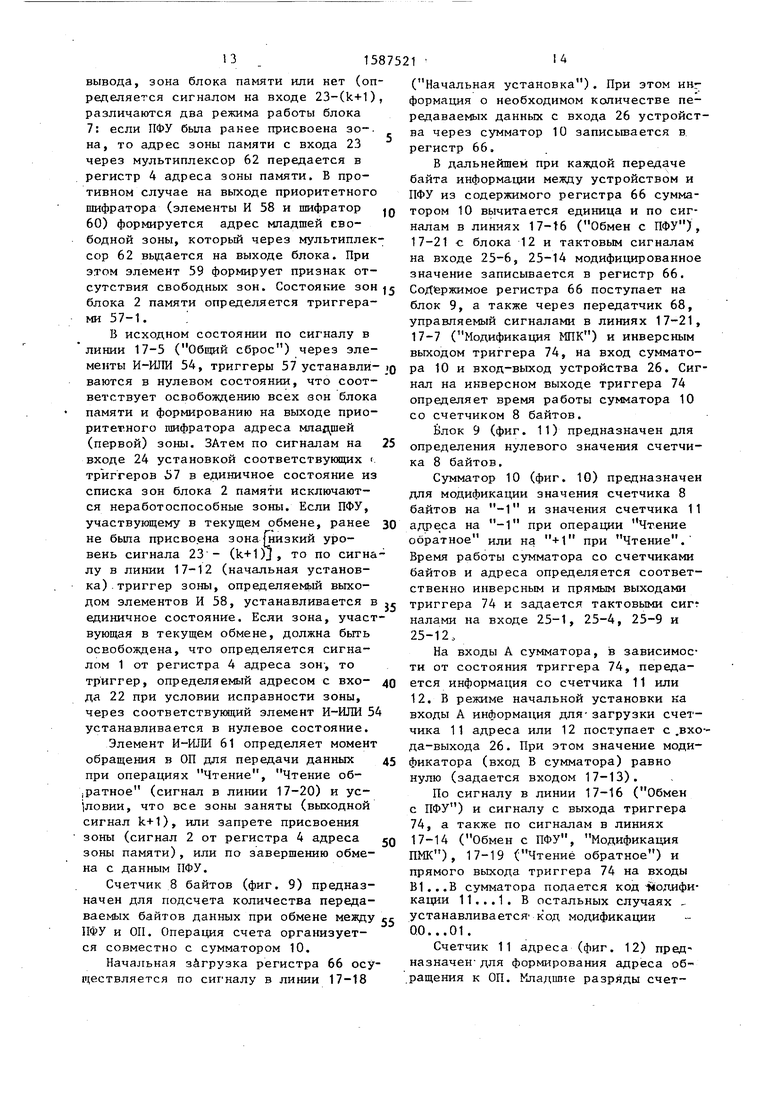

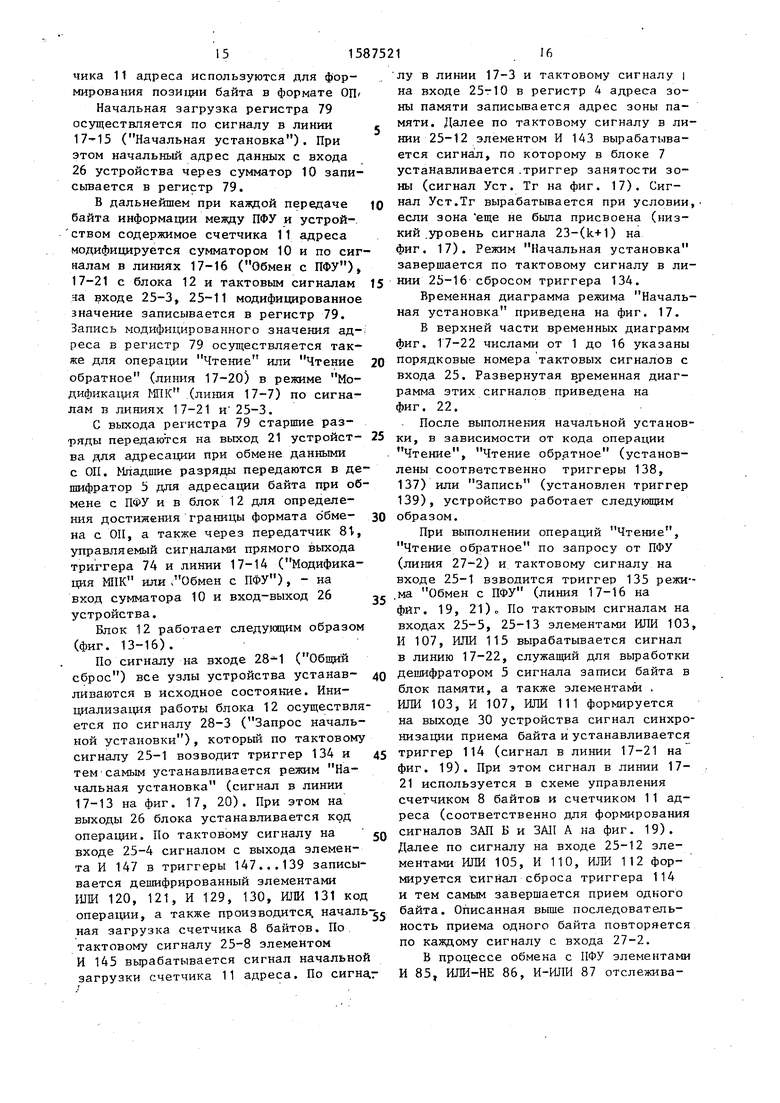

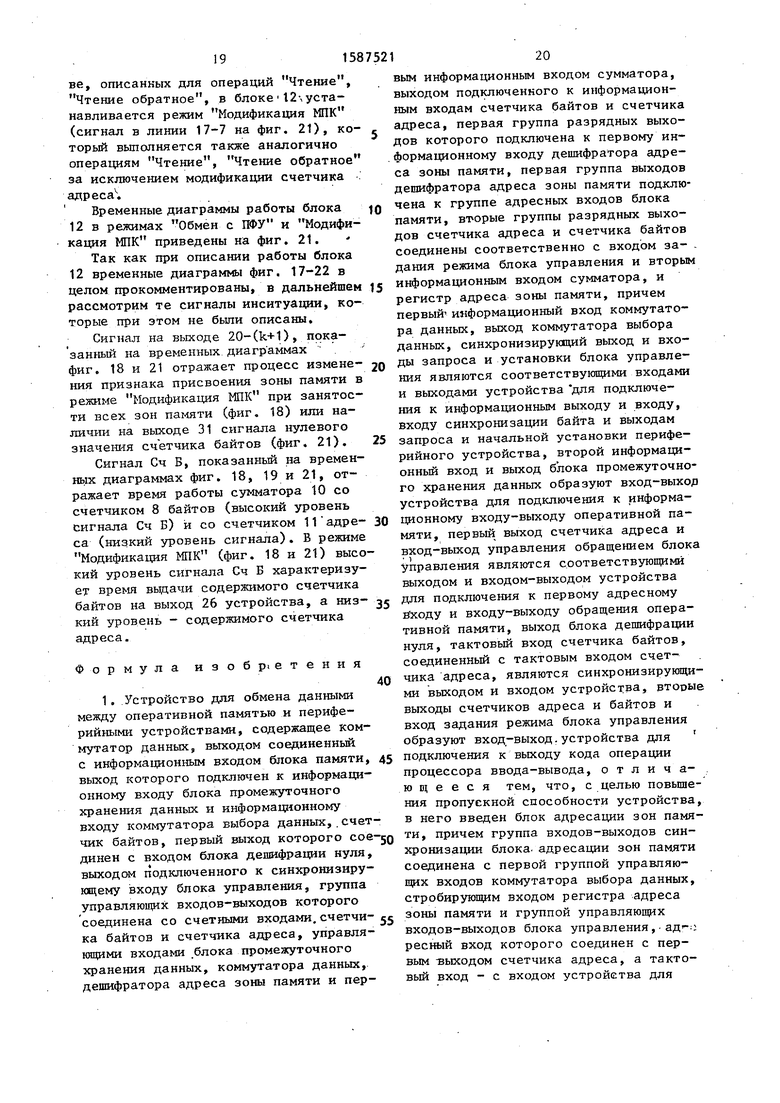

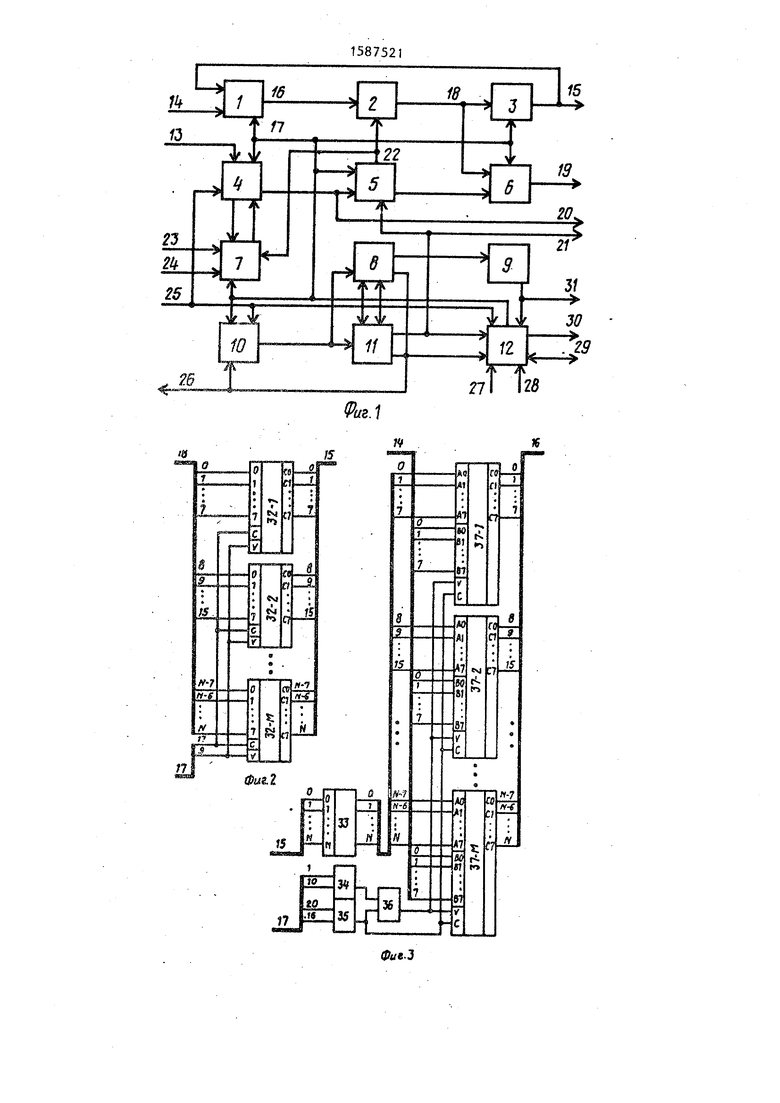

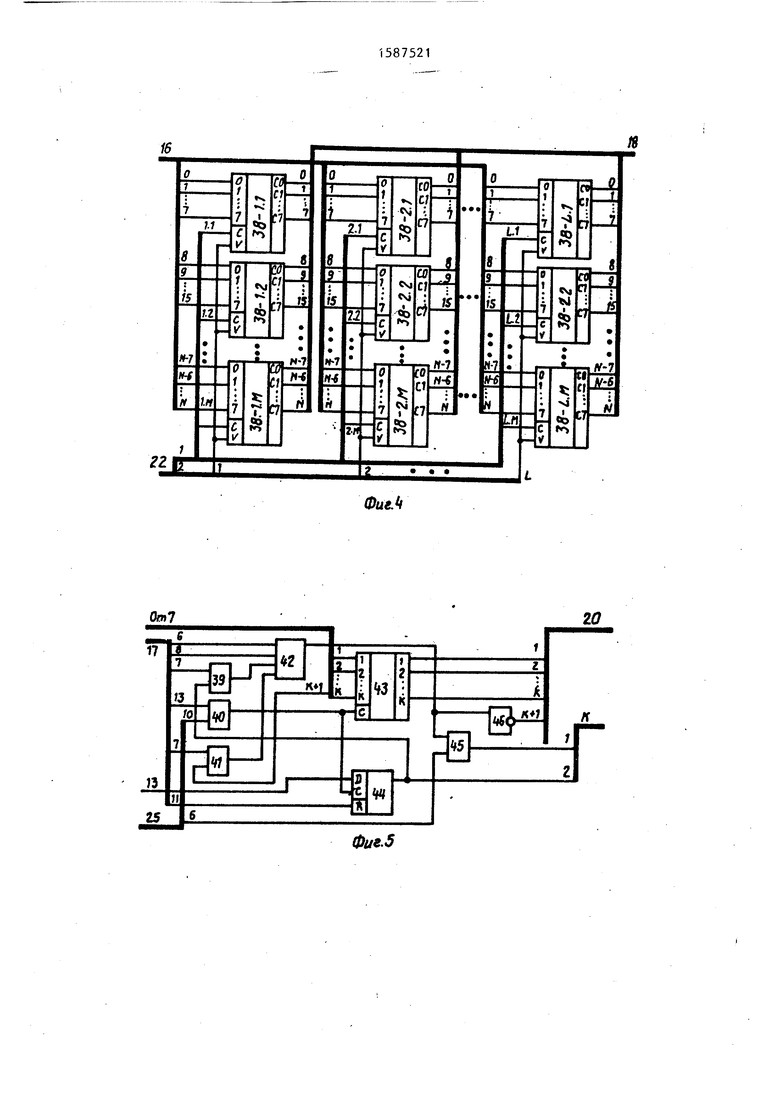

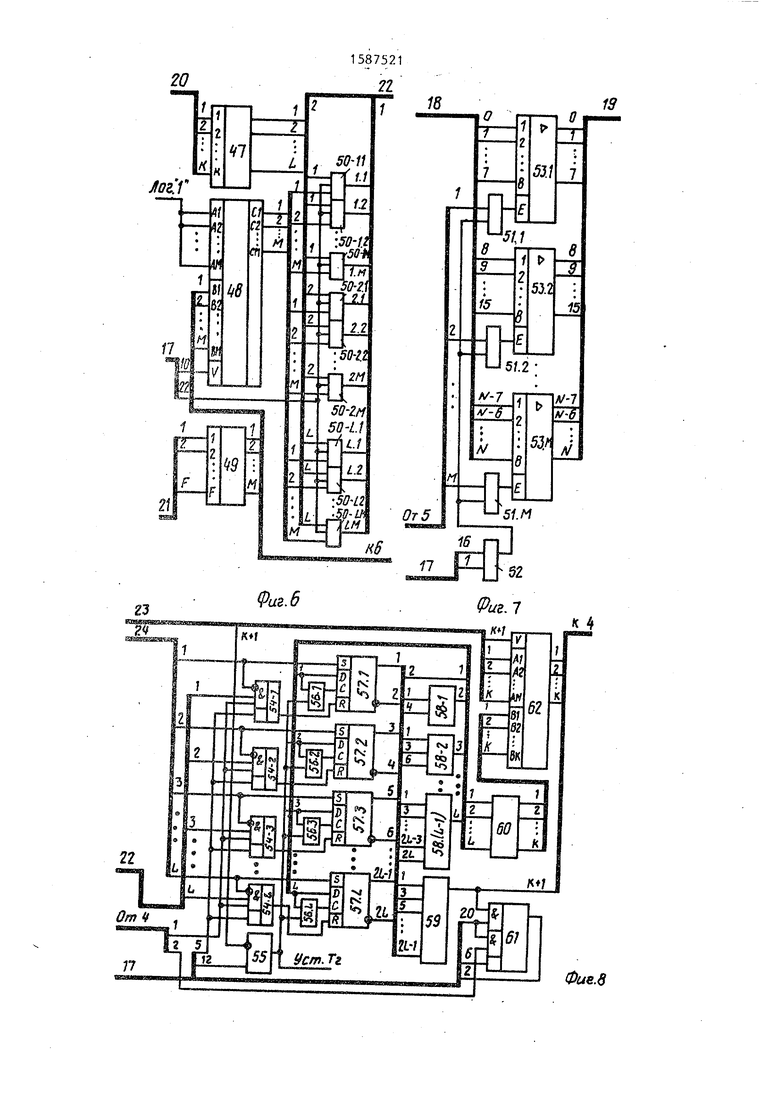

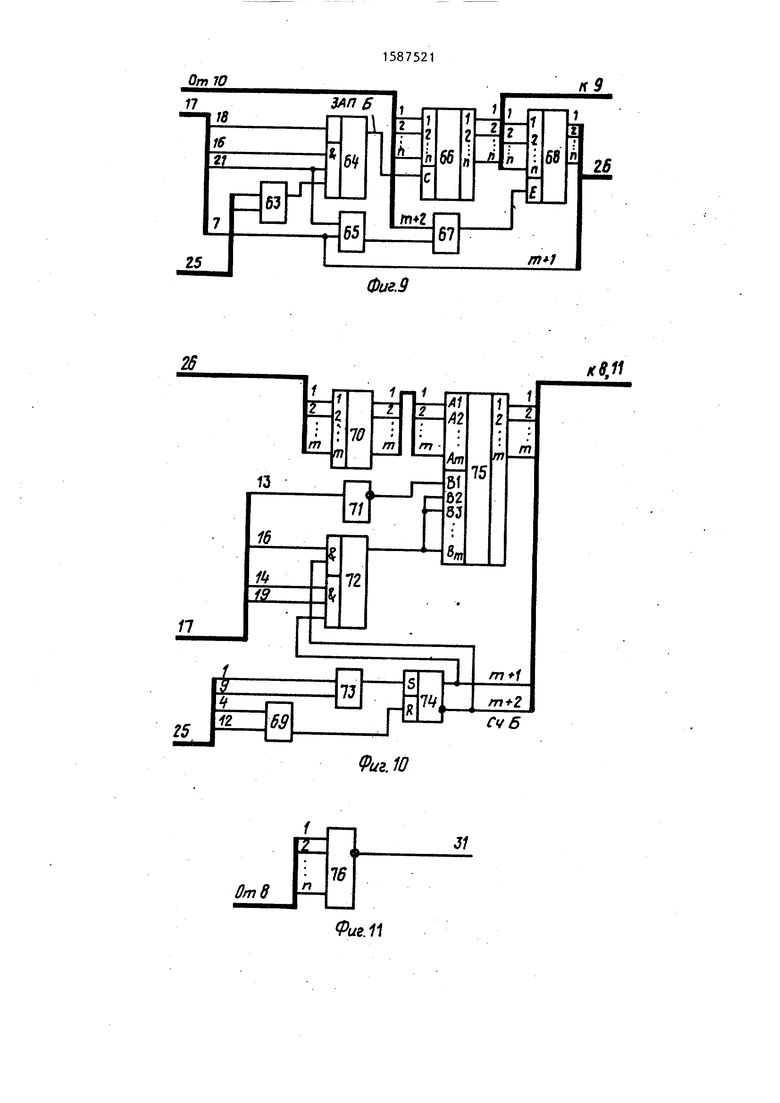

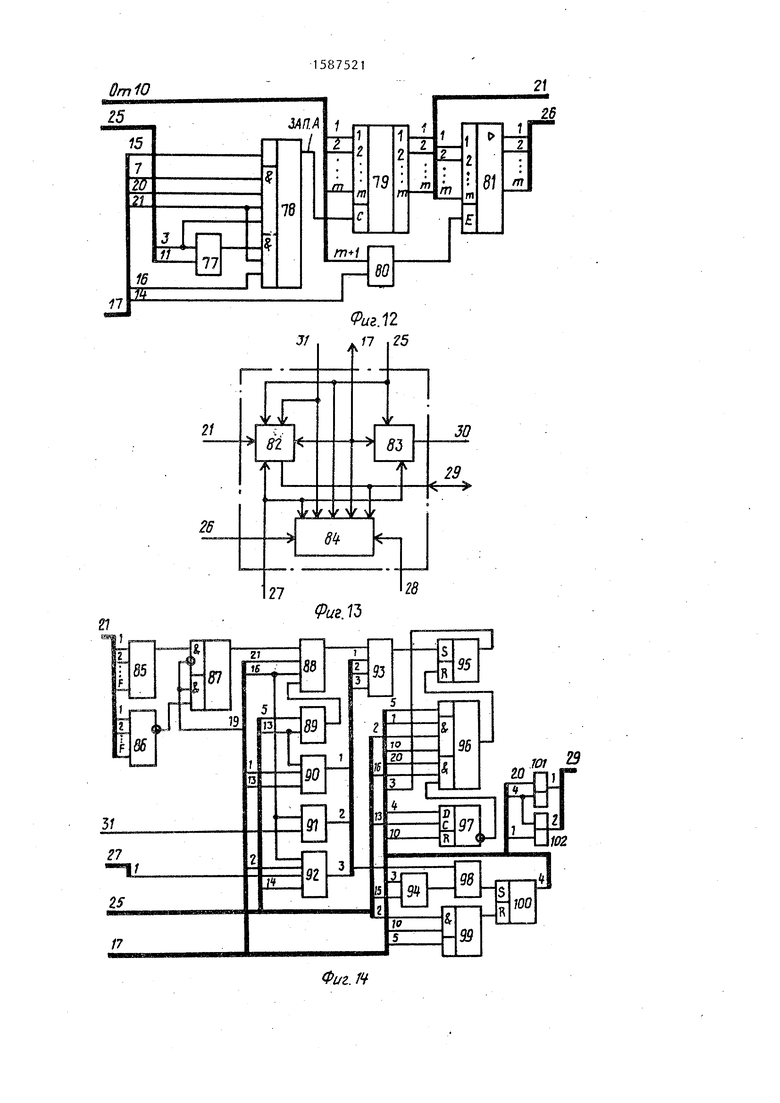

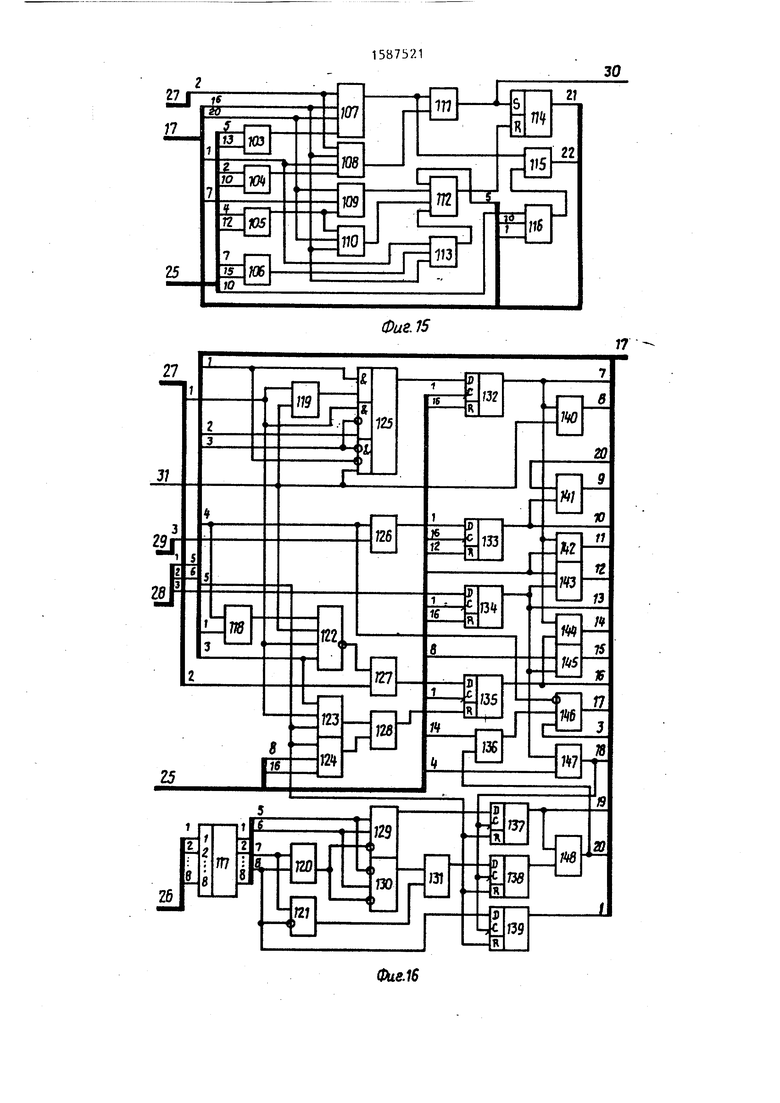

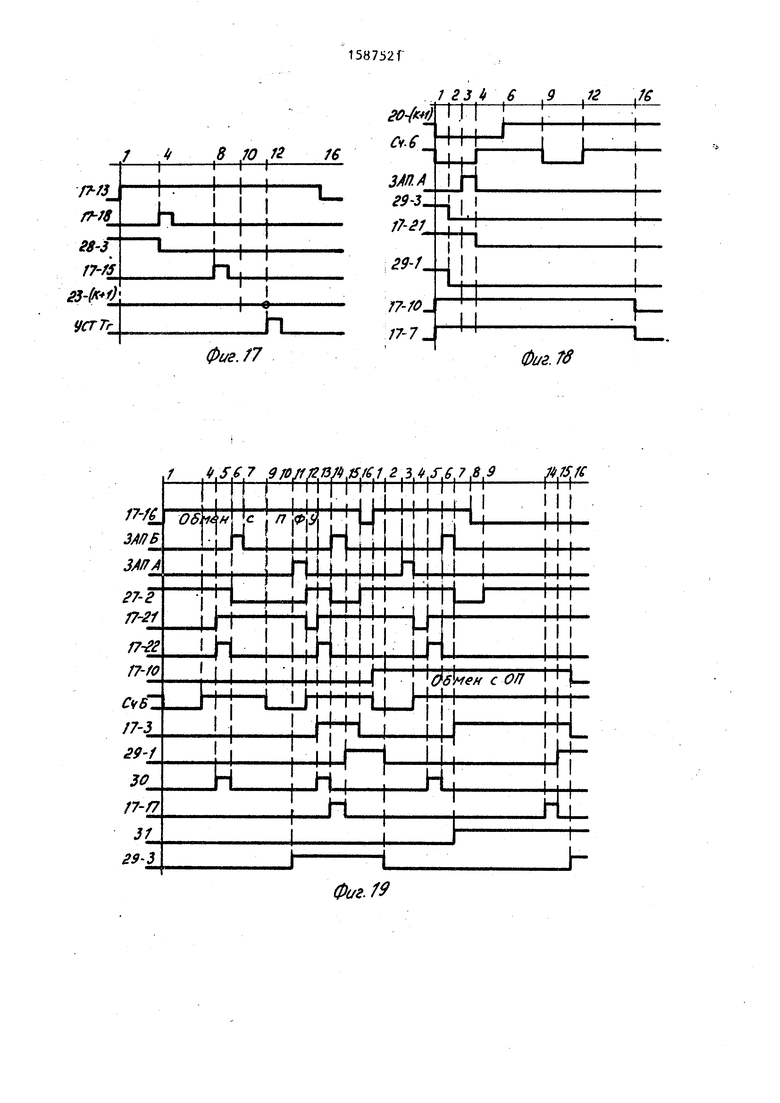

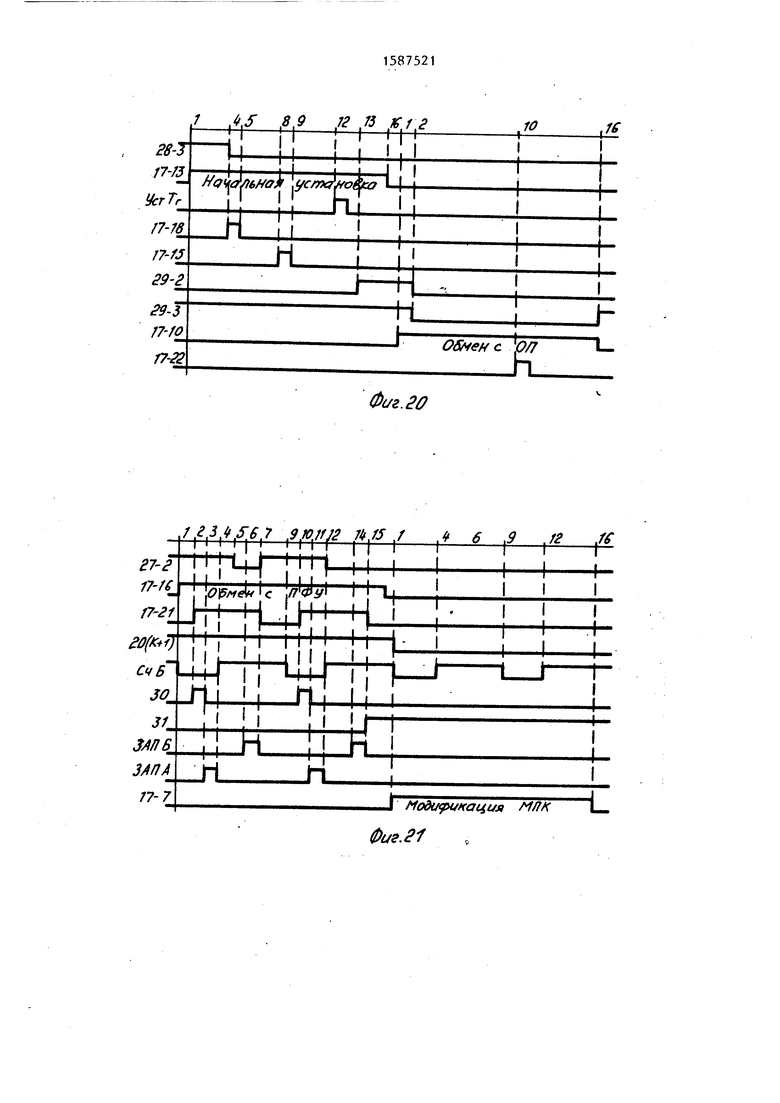

На фиг. 1 представлена структурная схема устройства для обмена данными между оперативной памятью и периферийными устройствами; на фиг. 2 - функ1щональная схема блока промежуточного хранения данных; на фиг. 3 - функциональная схема коммутатора данных; на фиг. 4 - функциональная схема блока памяти; на фиг. 5 - функциональная схема регистра адреса зоны памяти; на фиг. 6 - функциональная схема дешифратора адреса зоны памяти; на фиг. 7 - функциональная схема ком-, мутатора выбора данных; на фиг. 8 - функциональная схема блока адресации зон памяти; на фиг. 9 - функциональная схема счетчика байтов; на фиг. 10- ,функциональная схема сумматора; на фиг.11- функциональная схема блока дешифрации нуля; на фиг. 12 -функщю- нальная схема счетчика адреса; на фиг. 13 - структурная схема блока управления; на фиг. 14 - функциональ - ная схема узла дешифрации сигналов обмена с памятью; на фиг. 15 - функциональная схема узла дешифрации сигналов обмена с периферийными устройства- ,ми; на фиг. 16 - функциональная схема регистра режимов; на фиг. 17 - 19 - временные диаграммы работы устройства для Чтение или Чтение обратное соответственно в режимах Начальная установка, Модификация МПК и Обмен с на фиг. 20 и 21 - временные диаграммы работы устройства для операции Запись соответственно в режимах Начальная установка, Обмен с ОП и Обмен с ПФУ, Модифици- кация на фиг. 22 - временная ди(Л

ел

эо | :п

N5

аграмма последовательности синхросигналов.

Устройство (фиг. 1) содержит коммутатор 1 данных, блок 2 памяти, блок , 3 промежуточного хранения данных, регистр 4 адреса зоны памяти, дешифратор 5 адреса зоны памяти, коммутатор 6 выбора данных, блок 7 адресации зон памяти, счетчик 8 байтов, блок 9 о дешифрации нуля, сумматор 10,.счетчик 11 адреса, блок 12 управления, входы 13 и 14, вход-выход 15, выходы 16-18 блоков 1, 2 и 12, выходы 19-21, выход 22 дешифратора 5, входы 23-28, вход- )5 выход 29, выходы 30 и 31.

Блок 3 промежуточного хранения данных (фиг. 2) содержит регистры 32.

Коммутатор 1 данных (фиг.З) содержит приемник 33, элементы И 34 и 20 35, элемент ИЛИ 3, мультиплексоры 37.

Блок 2 памяти (фиг. 4) содержит регистры 38.

Регистр 4 адреса зоны памяти . (фиг. 5) содержит элементы И 39-41, 25 элемент ИЛИ 42, триггеры 43 и 44, элемент И 45, элемент НЕ (инвертор) 46.

Дешифратор 5 (фиг. 6) адреса зоны памяти содержит дешифратор 47, мультиплексор 48, дешифратор 49, элемен- зо ты И 50.

Коммутатор 6 выбора данных (фиг.7) содержит элементы И 51, 52 и передатчики 53

Блок 7 адресации зон памяти (фиг.8) содержит узел коммутации на элементах И-ИЛИ 54, элемент И 55, элементы И 56 первой группы, триггеры 57 занятости зоны памяти группы,.элементы

35

И 58 второй группы, элемент И 59, шифратор 60, элемент И-ИЛИ 61, мультиплексор 62.

Счетчик 8 байтов (фиг. 9) содержи элементы ИЛИ 63, элемент И-ШШ 64, элемент ИЛИ 65, регистр 66 счетчика байтов, элемент И 67, передатчик 68.

Сумматор 10 (фиГо 10) содержит элмент ИЛИ 69, приемник 70, элемент НЕ 71, элемент И-ИЛИ 72, элемент . ИЛИ 73, триггер 74 управления сумматором, сумматор 75.

Блок 9 дешифрации нуля (фиг. 11) состоит из элемента ИЛИ-НЕ 76.

Счетчик 11 адреса (фиг. 12) со- держит элемент ИЛИ 77, элемент И-ИЛИ 78, регистр 79 адреса, элемент И 80 и передатчик 81.

Блок 12 управления (фиг. 13) содержит узел 82 дешифрации сигналов

обмена с памятью, узел 83 дешифрации сигналов обмена с периферийными устройствами и регистр 84 режимов.

Узел 82 (фиг. 14) содержит элемент И 85, элемент ИЛИ-НЕ 86, элемент И-ИЛИ 87, элемент И 88, элемент ИЛИ 89, элементы И 90 - 92, элемент ИЛИ 93, элемент И 94, триггер 95,элемент И-ИЛИ 96, триггер 97, элемент ИЛИ 98, элемент И-ИЛИ 99, триггер 100 запроса в ОП, элементы И 10.1 и 102.

Узел 83 (фиг. 15) содержит элементы ИЛИ 103-106, элементы И 107-110, элементы ИЛИ 111 и 112, элемент И 113, триггер 114 обмена байтом, элемент ИЛИ 115 и элемент И 116.

Регистр 84 режимов (фиг. 16) содержит приемник 117, элемент И 118, элементы ИЛИ 119-124, элемент И-ШШ 125, элементы И 126-130, элемент ИЛИ 131, триггер 132 режима Модификация МПК, триггер 133 режима Обмен с ОП, триггер 134 режима Нач.льная установка, триггер 135 режима Обмен с ПФУ, элемент И 136, триггер 137 операции Чтение обратное, триггер 138 операции Чтение, триггер 139 операции Запись, элементы И 140 - 143, элемент ИЛИ 144, элементы И 145- 147 и элемент ИШ 148.

Устройство предназначено для работы в процессорах ввода-вывода универсальных, ЭВМ совместно с блоком сопря- ж ения канала ввода-вывода с интерфейт сом (БСИ) и устройством управления .процессора ввода-вывода (УУПВВ). Процессор ввода-вывода управляет обменом данных между периферийными устройствами (ПФУ) и оперативной памятью (ОП) ЭВМ, в процессе которого предлагаемое устройство совместно с БСИ выполняет функцию передаточного звена ОП-ПФУ. При этом устройство слуясит для согласования форматов передаваемых данных между ПФУ и ОП, организации обмена с ПФУ, работающими -в мультиплексном режиме и управления процессором обмена в пределах одной операции ввода-вывода.

Необходимость согласования форматов (форматизации) вызвано тем, что в высокопроизводительных универсальных ЭВМ форматы данных при обмене с ПФУ и ОП различны, что снижает пропускную способность тракта обмена ОП-ПФУ.

Особенности организаций обмена для ПФУ, работающих в мультиплексном режиме, заключаются в том, что данный класс ПФУ предполагает передачу одного или несколько байтов информации за один фрагмент операции ввода-вьшода.

Передача функций управления обменов в пределах одной операции ввода- вьюода устройству является действенной мерой повьшения производительности процессора ввода-вывода и ЗВМ в целом за счет перераспределения функций и освобождения ПВВ для выполнения других операций.

Устройство работает следующим образом.

Процедура согласования форматов осуществляется под общим управлением блока 12 и в зависимости от направления передачи информации в текущей операции ввода-вывода предполагает накопление данных, поступающих на ин- формахщонный вход 14 с БСИ через ком-г мутатор 1 данньк, в блоке 2 памяти до формата обмена с ОП с последующей их передачей, через блок 3 промежуточного хранения, на информационный вход- выход 15 - при передаче данных от ПФУ к ОП; а также запоминание данных, поступающих с ОП по входу-выходу 15, через коммутатор 1,в блоке 2 памяти с последующей их передачей в БСИ через коммутатор 6 выбора данных и информационный выход 19 в формате обмена с ПФУ - в случае передачи данных от ОП к ПФУ. При этом адреса записи/считывания информации блока 2 памяти, разбитого на зоны, формируются дешифратором 5 из адреса зоны памяти (20-1, 20-2,...,20-k (фиг. 5), вырабатываемого блоком 7 совместно с регистром 4 адреса зоны памяти, и адреса байта данных в зоне (21-1, 21-2,...,21-F; ) со счетчика 11 адреса; адрес байта, выдаваемого на выходы коммутатора 6 выбора данных, определяется ПОЗИ1ЩОННЫМ кодом адреса байта в зоне (1, 2,...,М) с выхода дешифратора 5, а адрес ОП вырабатьшается счетчиком 11 адреса и вьщается на первый адресный выход 21.

Возможность мультиплексирования ПФУ на основе принципа динамической

10

15

20

. 25 Ь7521

ределяется уровнем сигнала 23 (k+1), различаются два режима работы блока -- 7, Если ПФУ была ранее присвоена зона, то адрес зоны памяти, поступающий с ТПВВ по входу 23 передается в регистр 4 адреса зоны памяти, где использует-;- ся в качестве рабочего адреса. В противном случае, действуя по принципу поиска младшего свободного адреса, блок 7 присваивает данному ПФУ свободную зону с последующей его передачей в регистр 4 адреса зоны .памяти .При этом, если присвоенная зона оказалась послед- не свободной,в конце текущего фрагмента операции ввода-вывода она освобождается , обеспечивая тем самым путь обмена для других ПФУ. Освобождение зоны осуществляется также по концу операции ввода- вывода и других условий. Кроме перечисленных функций блок 7 обеспечивает отключение неисправных зон блока 2 памяти, определяемых входом 24 с . УУПВВ, а также совместно с блоком 4 регистра адреса зоны памяти управление режимом работы ПФУ (с присвоением зоны или без), определяемым уровнем сигнала на входе 13 с УУПВВ.

Функция управления процессом обмена данных в пределах одной операции ввода-вывода выполняется всеми средствами устройства под управлением блока 12. При этом различаются операции Чтение, Чтение обратное (передача данных из ПФУ и ОП) и Запись (передача данных из ОП в ПФУ). Код операции поступает из УУПВВ по задающему входу-выходу 26. Выполнение каждой из перечисленных операций осуществляется в три этапа: начальная установ- . ка устройства; передача данных; процедура завершения операции.

В период начальной установки по входу-выходу 26 осуществляется загрузка счетчика 11 адреса и счетчика 8 байтов, присвоение ПФУ зоны памяти и установка режима работы.

Передача дан,ных инициируется по запросу от ПФУ (вход 27-2) при опе ра- 50 циях Чтение, Чтение обратное или по инициативе блока 12 при операции Запись. В дальнейшем передача данных осуществляетея. по одному из описанных принципов согласования форма30

35

40

45

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве блока передачи данных в каналах ввода-вывода. Цель изобретения - повышение пропускной способности устройства. Для этого в устройство, содержащее коммутатор данных, блок памяти, блок промежуточного хранения данных, регистр адреса зоны памяти, дешифратор, коммутатор выбора данных, счетчик байтов, блок дешифрации нуля, сумматор, счетчик адреса и блок управления, введен блок адресации зон памяти. 2 з.п. ф-лы, 22 ил.

адресации и присвоения зон блока памя-., тов в зависимости от направления пере- ти обеспечивается блоком 7. В зависимости от того, быпа ли присвоена ПФУ, участвующему в текущей операции ввода- вьшода, зона блока памяти или нет (опдачи информации. При этом блок 12 контролирует границу формата обмена . с ОП и управляет обменом с ОП (по входу-выходу 29), или с ПФУ (вход 27,

тов в зависимости от направления пере-

дачи информации. При этом блок 12 контролирует границу формата обмена . с ОП и управляет обменом с ОП (по входу-выходу 29), или с ПФУ (вход 27,

выход 30); управляет сумматором, счетчиками адреса и байтов; фиксирует момент завершения текущего обмена по сигналам с выхода 31 блока 9 орав- нения, входы 28 - 2 с УУПВВ или входа 27-1 с ПФУ, а также выполняет переход к процедуре завершения операции.

Во время процедуры завершения операции содержимое счетчиков 11 и 8 по входу-выходу 26, а также адрес зоны, присвоенный данному ПФУ с признаком

присвоения зоны уровень сигнала 23,- (k+1)3 по выходу 20, передаются в УУПВБ. Эта информация используется для возобно вления обмена по требованию ПФУ либо анализа условий окончания операции ввода-вывода при завершении операции.

Синхронизация работы устройства осуществляется по серии тактовых импульсов, поступающих с УУПВВ по вхо- ДУ 25. .

При включении питания сигналом с входа 28-1 устройство устанавливается в исходное состояние. Триггеры 57, 95, 100, 135, 137-139 сбрасьшаются в нулевое состояние. Работа устройства начинается режимом Начальная установ ка, задаваемым установкой триггера : 134 в единичное состояние сигналом :28-3.

В этом режиме блоком 12 вырабатываются сигналы 17-18, 17-15, 17-12, по которым с входа 26 устанавливается исходное состояние соответственно счетчика 8 байтов, счетчика 11 адреса и блока 7 адресации зон памяти. По сигналу 17-18 также в триггерах 137-139 записьшается код вьшолняемой операции (Чтение, Чтение обратное, За- пись)..

По сигналу с линии 17-13 в регистр 4 адреса зоны памяти через мультип- лексор 62 с входа 23, ес.пи за сданны периферийньм устройством (ПФУ) была закреплена зона либо код младшей свободной зоны с выхода шифратора 60, если за данными ПФУ не закреплена зона, записывается код зоны памяти.

Источникч адресации зоны памяти определяется сигналом (k+1) с входа 23.

Код зоны памяти находится в ре- гистре 4 адреса зоны памяти в течение всего времени обмена данными и подает ;СЯ на дешифратор 5 адреса зоны памя- ти, выход которого определяет зону

блока 2 памяти, участвующую в данном обмене.

Временная диаграмма работы устройства в режиме Начальная установка приведена на фиг.,17.

После начальной установки устройство переходит к вьтолнению операции ввода-вывода.

При выполнении операции Чтение, Чтение обратное по сигналу 27-2 зап- роса от ПФУ в блоке 12 управления ус- танавливается триггер 135, задаюшрй режим Обмен с ПФУ.

При этом байт данных с входа 14 по- |Ступает через коммутатор 1 данных на информационные входы блока 2 памяти. Регистр в выбранной зоне памяти, в которой записьшается поступающий байт ранньк, определяется значением младших разрядов счетчика.11 адреса.

Далее по сигналу 27-2 на выходе узла 83 вырабатывается сигнал 17-22 строба записи байта данных в блок 2 памяти, на стробирующий выход 30 - сигнал подтверждения приема байта, а на выходе триггера 114 - сигнал 17-21 разрешения модификации счетчика 8 байтов и счетчика 11 адреса. Модификация счетчиков 8 и 11 производится за- писью с выхода сумматора 75 в регистры 66 и 79 модифицированных значений количества байтов и адреса по сигналам ЗАЛ.Б и ЗАП.А.

Режим работы сумматора 75 задается триггером 74, а также соответствующим включением передатчиков 68 и 81. При модификации счетчика 8 байтов триггер 74 вырабатывает сигнал, который вместе с сигналом 17-21 обеспечивает связь выходов регистра 66 через передатчик 68 с входами А сумматора 75. При модификации счетчика 11 адреса триггер 74 вырабатывает сигнал, который вместе с сигналом 17-14 обеспечивает связь выходов регистра 79 через передатчик 81 с входами А сумматора 75.

Модификация счетчика 8 байтов осуществляется вьиитанием единицы, а модификация, счетчика 11 адреса - прибавлением единицы для операций Чтение и Запись, или вычитанием единицы для операции Чтение обратное.

Прием байта информантки с ПФУ заканчивается сбросом триггера 114.

При поступлении следующих запросов от ПФУ последовательность приема байтов повторяется до появления одного из следующих условий:, достижение границы зоны памяти, фиксируемой элементами 85-88; фиксирование нулевого значения счетчика 8 байтов блоком 9; поступление сигнала 27-1 прерывания обмена при наличии сигнала 13 запроса присвоения зоны; поступление сигнала 27-1 прерьшания обмена при работе с последней свободной зоной буферной памяти; наличие сигнала 28-2 останова передачи данных по инициативе ПФУ,

Наличие любого из перечисленных условий приводит к сбросу триггера 135 режима Обмен с а также к установке триггера 95 при сброшенном триггере 97 занятости блока 3 промежуточного хранения данных,

Установка триггера 95 обеспечивает формирование сигнала 17-17 строба записи данных из зоны памяти блока 2 в блок 3 промежуточного хранения данных и разрешает установку триггера .100, который вместе с элементом И 101 вырабатывает на линии 29-1 сиг- нал запроса на запись в ОП,

При наличии сигнала 29-3 доступности ОП устанавливается триггер 133 и на выходе элемента 141 выдается сиг- нал 17-9, разрешаняций передачу йнфор- нации из блока 3 промежуточного хранения данных на выход 15 устройства.

Временные диаграммы работы устройства в режимах Обмен с и Обмен с ОП приведены на фиг. 19.

При этом продолжается прием данных из ПФУ, если отсутствуют сигналы 27-1 прерывания обмена, 29-2 останова передачи данных или 31 нулевого значения счетчика.

Иначе устройство переходит в режим Модификация МПК, задаваемый триггером 132. В этом режиме модифицируется значение счетчика 11 адреса и по сигналам с выхода триггера 74 на выход 26 устройства вьщается содержимое счетчика 11 адреса и счетчика 8 бай- . тов, а на выход 20 устройстгва вьщается адрес зоны и сигнал (k+1) признака присвоения зоны. Эта информация сопровождается сигналом на выходе 26 и служит для обеспечения возможности возобновления обмена с данным ПФУ. Единичное значение сигнала (k+1) свидетельствует о том, что за данным ПФУ закг- реплена зона памяти.

Закрепление зоны за ПФУ происходит при выполнении следующих условий: для данного ПФУ разрешено закрепление:ао

Q

5

0 5

о

0

5 я

5

ны памяти сигналом на входе 13; отсутствует сигнал на.входе 28-2 останова передачи данных или сигнал на выходе 31 нулевого значения счетчика; отсут-- ствует признак последней зоны памяти.

Временная диаграмма работы устройства в режиме Модификация МПК приведена на фиг. 18.

При вьшолнении операции Запись устройство работает следукищм образом.

В режиме Начальная установка триггером 100 вырабатьшается сигнал 29-2 запроса на чтение из ОП. При наличии сигнала 29-3 доступности ОП устройство переходит в режим работы Обмен с ОП. При этом информация с выхода 15, определяемая адресом на выходе 21, через коммутатор 1 записывается по сигналу в линии 17-22 в зону памяти ПФУ, определяемую блоком 7 арбитра зон памяти.

Временная диаграмма работы устройства в режимах Начальная установка и Обмен с ОП приведена на фиг. 20.

По сигналу на входе 27-2 устанавливается триггер 135 и устройство переходит в режим Обмен с ПФУ. При этом сигнал с выхода 17-21 триггера 114 инициирует передачу байта информации из блока 2 памяти через коммутатор 6 на выход 19 и модификацию счетчика 8 адреса и счетчика 11 байтов.

Режим обмена с ПФУ продолжается до появления следующих условий: достижение границы зоны памяти; наличие сигнала на выходе 31 нулевого значения счетчика; наличие сигнала на входе 27-1 прерывания обмена; поступление сигнала на входе 28-2 окончания передачи данных.

По первому условию устройство переходит в режим Обмен с ОП. Остальные условия переводят устройство в режим Модификация МПК, который выполняется аналогично описанному для операций Чтение, Чтение обратное, за исключением модификации счетчика адреса.

Временная диаграмма работы устройствам режимах Обмен с ПФУ и Модификация МПК приведена на фиг. 21.

Для-синхронизации работы устройства используется серия синхроимпульсов с входа 25, временная диаграмма которых приведена на фиг. 22.

Диагностика блока 2 памяти осуще- - ствляется периодически в режиме Чтение передачей с ПФУ тестовых наборов с последующим их анализом схемами диагностики. Обнаруженная неисправная зона отключается соответствующим сиг- налом с входа 24.

В процессе работы устройства его блоки фаботают следующим образом.

Коммутатор 1 данных (фиг. 3) предназначен для. передачи в бло1с 2 памяти информации с входа-выхода 15 в операции Запись или с входа 14 в операциях Чтение, Чтение обратное. Выбор источника данных осуществляется по сигналам на линиях 17-1 (операция Запись), 17-10 (режим обмена с ОП), или 17-20 (операции Чтение, Чтение обратное) и 17-16 (режим обмена с ПФУ) .

Блок 2 памяти (фиг. 4) предназна. чён для coглacoвaшiя форматов данных, передаваемых между ОП и ПФУ, и состоит из L зон размером формата обмена с ОН (М-байтов). Адрес зоны и регистров байтов в зоне определяется дешиф- ратором 5 и поступает на входы С регистров при записи данных с входа 16 в блок 2 памяти или на входы V при считывании информации на вход 18.

Блок 3 промежуточного хранения дан ных (фиг. 2) предназначен для совмещения передачи данных в ОП и записи, в блок 2 памяти при операции Чтение Чтение обратное. Запись информагцш с входа 18 в регистрах 32.1-32,М осутг ществляется по сигналу в ли1ши 17-17 : оторый фop иpyeтcя блоком 12 в операциях Чтение, Чтение обратное при условии, что блок 3 свободен. Выдача данных на выход 15 блока осуще- ствляется по сигналу в линии 17-9 в режиме Обмен с ОП.

Регистр 4 адреса зоны памяти (фиг, 5) предназначен для хранения адреса зоны блока 2 памяти, присвоенной ПФУ, участвующей в текущей операции обмена, .формирования признака при своения зоны памяти данному ПФУ l20-(k+1)3, и сигнала заверщенияс one- рации в устройстве.

Запись адреса зоны памйти с выхода блока 7 (фиг. 8) в регистр 43 осуще- ст:Бляется по сигналу в линии 17-13 (режим Начальная установка) и такто вому сигналу на входе 25-10. При этом в триггер 44 с входа 13 запоминается признак запрещения или разрешениям присвоения зоны памяти данному ПФУ.

Формирование признака присвоения зоны осуществляется в режиме Модификация МПК или при останове устройства по сигналу в линии 17-6 (Останов), или 17-8 (нулевое значение счетчика байтов), или 17-7 (Модификация МПК) совместно с признаком запрещения присвоения зон с выхода триггера 44, или 17-7 совместно с (k+1), поступающим с блока 7 (отсутствие свободных зон). Сигнал завершения операции в. устройстве формируется по условиям формирования признака присвоения зон и тактовому сигналу .25-6 и передается по выходу 1 к блоку 7.

Дешифратор 5 (фиг. 6) предназначен для формирования адреса зоны и регистров байтов в зоне блока 2 памяти, а также определения адреса передаваемого байта из блока 2 памяти на выход 19 устройства через коммутатор 6 выбора данных.

Адрес зоны памяти формируется дешифратором 47 и вьщается на выход 22-1.1...22-2. Адрес регистра байта в выбранной зоне, в зависимости от источника данных (ПФУ или ОП), определяемый входом 7-10, формируется по стробирующему сигналу в линии 17-22 следующим образом: если данные поступают с ПФУ, адрес формируется элементами 50-1.1...50-2.И из младших разря- .дов счетчика 11 адреса, поступакшщх с входа 21 через дешифратор 49 и мультиплексор 48; если данные поступают из ОП, мультиплексор 48 вьщает адрес всех байтов выбранной зоны (Лог. 1 на входах А1, А2,...,АМ).

Выход дешифратора 49 также определяет адрес передаваемого байта из блока 2 памяти на выход 19 устройства через коммутатор 6 выбора данных. Коммутатор 6 выбора данных (фиг. 7) предназначен ДЛЯ согласования форматов данных блока 2 памяти и ПФУ в операци Запись.

Сигналы выбора-байта (входы Е передатчиков 53-1...53-м) формируются элементами И 51 по адресу байта с дешифратора 5 и сигналам в линиях 17-16 (Обмен с ПФУ), 17-1 (операция Запись) .

Блок 7 (фиг. 8) предназначен для динамической адресации и присвоения зон блока 2 памяти ПФУ, работающим в мультиплексном режиме. В зависимости от того, была ли присвоена ПФУ, участвуклцему в текущей операции ввода1315875

вывода, зона блока памяти или нет (определяется сигналом на входе 23-(k4-1), различаются два режима работы блока 7: если ПФУ была ранее присвоена зо-. на, то адрес зоны памяти с входа 23 через мультиплексор 62 передается в регистр 4 адреса зоны памяти. В противном случае на выходе приоритетного шифратора (элементы И 58 и шифратор 60) формируется адрес мпадшей свободной зоны, который через мультиплексор 62 вьщается на выходе блока. При этом элемент 59 формирует признак от10

сутствия свободных зон. Состояние зон Содержимое регистра 66 поступает на

блока 2 памяти определяется триггерами 57-1.

В исходном состоянии по сигналу в линии 17-5 (Общий сброс) через элеблок 9, а также через передатчик 68, управляемый сигналами в линиях 17-21 17-7 (Модификация МПК) и инверсным выходом триггера 74, на вход суммато

блок 9, а также через передатчик 68, управляемый сигналами в линиях 17-21, 17-7 (Модификация МПК) и инверсным выходом триггера 74, на вход сумматомеиты И-ИЛИ 54, триггеры 57 устанавли-JQ pa 10 и вход-выход устройства 26. Сигваются в нулевом состоянии, что соответствует освобождению всех зон блока памяти и формированию на выходе приоритетного шифратора адреса младшей (первой) зоны. ЗАтем по сигналам на 25 входе 24 установкой соответствующих . триггеров 57 в единичное состояние из списка зон блока 2 памяти исключаются неработоспособные зоны. Если ПФУ, участвующему в текущем обмене, ранее зО не бьша присвоена зона низкий уровень сигнала 23 - (k+1)j, то по сигналу в линии 17-12 (начальная установка).триггер зоны, определяемь1й выходом элементов И 58, устанавливается в ,г единичное состояние. Если зона, участвующая в текущем обмене, должна быть освобождена, что определяется сигналом 1 от регистра 4 адреса зон , то триггер, определяемый адресом с входа 22 при условии исправности зоны, через соответствуншщй элемент И-ИЛИ 54 устанавливается в нулевое состояние.

Элемент И-ШШ 61 определяет момент обращения в ОП для передачи данных при операциях Чтение, Чтение об- ipaTHoe (сигнал в линии 17-20) и ус- |Ловии, что все зоны заняты (выходной сигнал k+1), или запрете присвоения зоны (сигнал 2 от регистра 4 адреса зоны памяти), или по завершению обмена с данным ПФУ.

Счетчик 8 байтов (фиг. 9) предназначен для подсчета количества переда40

45

50

ваемых байтов данных при обмена между г с устанавливается код модификации

ПФУ и ОП. Операция счета организуется совместно с сумматором 10.

Начальная з&грузка регистра 66 осуществляется по сиг налу в линии 17-18

0.0... 01 .

Счетчик 11 адреса (фиг. 12) п назначен- для формирования адреса ращения к ОП. Младшие разряды сч

I А

0

(Начальная установка), При этом инг формация о необходимом количестве передаваемых данных с входа 26 устройства через сумматор 10 записьшается в регистр 66. .

В дальнейшем при каждой передаче байта информации между устройством и ПФУ из содержимого регистра 66 сумматором 10 вычитается единица и по сигналам в линиях 17-t6 (Обмен с ПФУ), 17-21 с блока 12 и тактовым сигналам на входе 25-6, 25-14 модифицированное значение записывается в регистр 66.

блок 9, а также через передатчик 68, управляемый сигналами в линиях 17-21, 17-7 (Модификация МПК) и инверсным выходом триггера 74, на вход сумматоpa 10 и вход-выход устройства 26. Сигнал на инверсном выходе триггера 74 определяет время работы сумматора 10 со счетчиком 8 байтов.

Блок 9 (фиг. 11) предназначен для определения нулевого значения счетчика 8 байтов.

Сумматор 10 (фиг. 10) предназначен для модификации значения счетчика 8 байтов на -1 и значения счетчика 11 адреса на -1 при операции Чтение обратное или на +1 при Чтение.

Время работы сумматора со счетчиками байтов и адреса определяется соответственно инверсным и прямым выходами триггера 74 и задается тактовыми сигг налами на входе 25-1, 25-4, 25-9 и 25-12,

На входы А сумматора, в зависимости от состояния триггера 74, передается информация со счетчика 11 или 12. В режиме начальной установки на входы А информация для-загрузки счетчика 11 адреса или 12 поступает с .вхо- да-выхода 26. При этом значение моди- фикатора (вход В сумматора) равно нулю (задается входом 17-13).

По сигналу в линии 17-16 (Обмен с ПФУ) и сигналу с выхода триггера 74, а также по сигналам в линиях 17-14 (Обмен с ПФУ, Модификация ПЖ), 17-19 (Чтение обратное) и прямого выхода триггера 74 на входы В1...В сумматора подается код йодлфи- кации 11... 1 . В остальных случаях ,

0.0... 01 .

Счетчик 11 адреса (фиг. 12) предназначен- для формирования адреса обращения к ОП. Младшие разряды счет

чика 11 адреса используются для формирования ПОЗИ1ЩИ байта в формате ОП

Начальная загрузка регистра 79 осуществляется по сигналу в линии 17-15 (Начальная установка). При этом начальный адрес данных с входа 26 устройства через сумматор 10 запи- сьюается в регистр 79.

В дальнейшем при каждой передаче байта информации между ПФУ и устрой-, ством содержимое счетчика 11 адреса модифицируется сумматором 10 и по сигналам в линиях 17-16 (Обмен с ПФУ) 17-21 с блока 12 и тактовым сигналам да входе 25-3, 25-11 модифицированное значение записывается в регистр 79. Запись модифицированного значения адреса в регистр 79 осуществляется также для операции Чтение или Чтение обратное (линия 17-20) в режиме Модификация ШК .(линия 17-7) по сигналам п линиях 17-21 и 25-3.

С выхода регистра 79 старшие разряды передаются на выход 21 устройст- ва для адресахщи при обмене данными с СП. Младшие разряды передаются в дешифратор 5 для адресации байта при обмене с ПФУ и в блок 12 для определения достижения границы формата о бме- на с ОП, а также через передатчик 8%, управляемый сигналами прямого выхода триггера 74 и линии 17-14 (Модификация МПК или .Обмен с ПФУ), - на вход сумматора 10 и вход-выход 26 устройства.

Блок 12 работает следующим образом (фиг. 13-16).

По сигналу на входе 28 (Общий сброс) все узлы устройства устанавливаются в исходное состояние. Инициализация работы блока 12 осуществляется по сигналу 28-3 (Запрос начальной установки), который по тактовому сигналу 25-1 возводит триггер 134 и тем Самым устанавливается режим Начальная установка (сигнал в линии 17-13 на фиг. 17, 20). При этом на выходы 26 блока устанавливается код операции. По тактовому сигналу на входе 25-4 сигналом с выхода элемента И 147 в триггеры 147...139 записывается дешифрированный элементами ШШ 120, 121, И 129, 130, ИЛИ 131 код операгщи, а также производится, началь ная загрузка счетчика 8 байтов. По тактовому сигналу 25-8 элементом И 145 вырабатывается сигнал начально загрузки счетчика 11 адреса. По сигн

10

15

20

30

-

, ге - 25 еб, м

яудь- ой на.г

58752116

лу в линии 17-3 и тактовому сигналу i на входе 25г10 в регистр 4 адреса зоны памяти записывается адрес зоны памяти. Далее по тактовому сигналу в линии 25-12 элементом И 143 вырабатывается сигна л, по которому в блоке 7 устанавливается .триггер занятости зоны (сигнал Уст. Тг на фиг. 17). Сигнал Уст.Тг вырабатывается при условии, если зона еще не бьша присвоена (низкий .зфовень сигнала 23-(k+1) на фиг. 17). Режим Начальная установка завершается по тактовому сигналу в линии 25-16 сбросом триггера 134.

Временная диаграмма режима Начальная установка приведена на фиг. 17.

Б верхней части временных диаграмм фиг. 17-22 числами от 1 до 16 указаны порядковые номера тактовых сигналов с входа 25. Развернутая в ременная диаграмма этих сигналов приведена на фиг. 22.

После выполнения начальной установки, в зависимости от кода операции Чтение, Чтение обратное (установлены соответственно триггеры 138, 137) или Запись (установлен триггер 139), устройство работает следующим образом.

При выполнении операций Чтение, Чтение обратное по запросу от ПФУ ( 27-2) и тактовому сигналу на входе 25-1 взводится триггер 135 режи- ,ма Обмен с ПФУ (линия 17-16 на фиг. 19, 21)о По тактовым сигналам на входах 25-5, 25-13 элементами ИЛИ 103, И 107, ИЛИ 115 вырабатывается сигнал в линию 17-22, служащий для выработки дешифратором 5 сигнала записи байта в блок памяти, а также эпенентами . ШШ 103, И 107, ИЛИ 111 формируется на выходе 30 устройства сигнал синхронизации приема байта и устанавливается триггер 114 (сигнал в линии 17-21 на фиг. 19). При этом сигнал в линии 17- 21 используется в схеме управления счетчиком 8 байтов и счетчиком 11 адреса (соответственно для формирования сигналов ЗАП Б и ЗАП А на фиг. 19). Далее по сигналу на входе 25-12 элементами ИЛИ 105, И 110, ИЛИ 112 фор- мируется сигнал сброса триггера 114 и тем самым завершается прием одного байта. Описанная вьш1е последовательность приема одного байта повторяется по каждому сигналу с входа 27-2.

В процессе обмена с ПФУ элементами И 85, ИЛИ-НЕ 86, И-Шга 87 отслежива35

40

45

50

ется момент достижения границы форма- .та обмена с ОП (единичное значение младших разрядов счетчика 11 адреса для операции Чтение, Запись или их нулевое значение для операции Чтение обратное) и по тактовым сигналам на входах 25-5, 25-13 через элементы И 88, ШШ 89, 93 устанавлипоступление сигнала на вход 28-2 окончания передачи данных.

При этом устройство переходит в режим работы Модификация МПК, устанавливаемый триггером 132 по тактовому импульсу на входе 25-1 (линия 17-7 на фиг. 18). .

По сигналу в линии 17-7 содержимое

- - - J - ..«.. .1 If , ч v jt- - /ivrinv

вается триггер 95 условия обращения к ю счетчиков 8 и 11, а также регистра А

ОП (линия 17-3 на фиг. t9).

Режим Обмен с ПФУ заканчивается

сигналом сброса триггера 135, кото- ,р.ый формируется элементами ИЛИ 123,

124, И 128 по тактовым сигналам на t5 входах 25-8, 25-16 и сигналу в линии

17-3 или 27-1 (Прерывание обмена). Установка триггера 95 создает условия перехода к режиму Обмен с ОП. По сигналу в линии 17-3, тактовому 20 сигналу на входе 25-14 элементом И 146 вырабатьгаается сигнал для записи слова данных из блока 2 памяти в регистр 3 промежуточного хранения данн| рс. Затем по тактовому сигналу на входе25 25-15 элементами И 94, ИЛИ 98 формируется сигнал установки триггера 100 и через элемент 101 на выход 29-1 устройства выдается сигнал запроса на

адреса зоШ)1 памяти передается вУУПВВ„ При этом содержимое счетчика 11 адреса модифицируется (сигнал ЗАП А на фиг. 18).

-Если в режиме Модификация МПК присутствуют условия освобождения зоны памяти блока 2, то инициируется режим Обмен с СП (линия 17-10 на фиг. 18).

Временная диаграмма работы устройства в режиме Модификация МПК приведена на фиг. 18.

При вьшолнении операции Запись в режиме Начальная установка, кроме описанных вьше действий, по тактовому сигналу на входе 25-13 через элементы И 90, ШШ 98 устанавливается триггер 100 и на выход 29-2 выдается сигнал запроса на чтение из ОП. Режим Обмен

запись в ОП. При этом при наличии сиг-30 с ОП (линия 17-10 на фиг. 20) уста- нала на выходе. 29-3 доступности ОП по навливается аналогично операциям Чте- тактовому сигналу в линии 25-1 уста-....

навливается триггер 133 режима обмена с ОП (линия 17-10 на фиг. 19) и по тактовому сигналу в линии 25-2 через элемент И-ИЛИ 99 триггер 100 сбрасывается.

После перезаписи данных из зоны памяти в блок 3 промежуточного хранения данных при условии отсутствия не- 40 по тактовому сигналу на входе 25-16. обслуженных запросов в ОП (низкий уро-Временные диаграммы работы блока

вень сигнала в линии 17-4) по тактовому импульсу на входе 25-13 триггер

ние и Чтение обратное. При этом элементом И 116 по тактовому сигналу на входе 25-10 формируется сигнал в 35 линии 17-22, который используется в схеме дешифратора 5 для формирования строба записи слова данных из ОП в блок 2 памяти.

Режим Обмен с ОП заканчивается

97 сбрасьгоается. Далее по тактовому сигналу на входе 25-16 через элемент И-ШШ 96 сбрасьшается триггер 95. Режим Обмен с ОП завершается сбросом триггера 133 по тактовому сигналу на входе 25-16,Временные диаграммы работы блока 12 в режимах Обмен с ПФУ, Обмен с ОП для операций Чтение, Чтение обратное приведены на фиг. 19.

Операция ввода-вывода в устройс т- ве завершается по следующим условиям: наличие сигнала на выходе 31 нулевого значения счетчика байтов; наличие сигнала на входе 27-1 прерьшания обмена;.

в режимах Начальная установка и Обмен с ОП для операции Запись приведены на фиг. 20.

45 После обмена с ОП при наличии сигнала на входе 27-2 готовности ПФУ к обмену блок 12 памяти переходит в режим Обмен с ПФУ (г.игнал в линии 17-16 на фиг, 21).

50 Условия установки этого режима аналогичны условиям для операций Чтение, Чтение обратное., Однако установка триггера 114 и выдача сигнала 30 синхронизации передачи байта осу55 ществляется по тактовым сигналам на входах 25-2, 25-10 через элементы . ИЖ 104, И 108, ШШ 111.

При возникновении условий окончания операции ввода-вывода в устройстпоступление сигнала на вход 28-2 окончания передачи данных.

При этом устройство переходит в режим работы Модификация МПК, устанавливаемый триггером 132 по тактовому импульсу на входе 25-1 (линия 17-7 на фиг. 18). .

По сигналу в линии 17-7 содержимое

- - - J - ..«.. .1 If , ч v jt- - /ivrinv

счетчиков 8 и 11, а также регистра А

адреса зоШ)1 памяти передается вУУПВВ„ При этом содержимое счетчика 11 адреса модифицируется (сигнал ЗАП А на фиг. 18).

-Если в режиме Модификация МПК присутствуют условия освобождения зоны памяти блока 2, то инициируется режим Обмен с СП (линия 17-10 на фиг. 18).

Временная диаграмма работы устройства в режиме Модификация МПК приведена на фиг. 18.

При вьшолнении операции Запись в режиме Начальная установка, кроме описанных вьше действий, по тактовому сигналу на входе 25-13 через элементы И 90, ШШ 98 устанавливается триггер 100 и на выход 29-2 выдается сигнал запроса на чтение из ОП. Режим Обмен

с ОП (линия 17-10 на фиг. 20) уста- навливается аналогично операциям Чте- ....

с ОП (линия 17-10 на фиг. 20) уста- навливается аналогично операциям Чте ....

по тактовому сигналу на входе 25-16. Временные диаграммы работы блока

ние и Чтение обратное. При этом элементом И 116 по тактовому сигналу на входе 25-10 формируется сигнал в линии 17-22, который используется в схеме дешифратора 5 для формирования строба записи слова данных из ОП в блок 2 памяти.

Режим Обмен с ОП заканчивается

по тактовому сигналу на входе 25-16. Временные диаграммы работы блока

в режимах Начальная установка и Обмен с ОП для операции Запись приведены на фиг. 20.

После обмена с ОП при наличии сигнала на входе 27-2 готовности ПФУ к обмену блок 12 памяти переходит в режим Обмен с ПФУ (г.игнал в линии 17-16 на фиг, 21).

Условия установки этого режима аналогичны условиям для операций Чтение, Чтение обратное., Однако установка триггера 114 и выдача сигнала 30 синхронизации передачи байта осуществляется по тактовым сигналам на входах 25-2, 25-10 через элементы ИЖ 104, И 108, ШШ 111.

При возникновении условий окончания операции ввода-вывода в устройстве, описанных для операций Чтение, Чтение обратное, в блоке 12%устанавливается режим Модификация МПК (сигнал в линии 17-7 на фиг. 21), ко- торьй вьшолняется также аналогично операциям Чтение, Чтение обратное за исключением модификации счетчика адреса ;

Временные диаграммы работы блока 12 в режимах Обмен с и Модификация МПК приведены на фиг. 21.

Так как при описании работы блока 12 временные диаграммы фиг. 17-22 в целом прокомментированы, в дальнейшем рассмотрим те сигналы инситуации, которые при этом не были описаны,

Сигнал на выходе 20-(k+1), пока- занный на временных диаграммах фиг. 18 и 21 отражает процесс изменения признака присвоения зоны памяти в режиме Модификация МПК при занятости всех зон памяти (фиг. 18) или наличии на выходе 31 сигнала нулевого значе1шя счетчика байтов (фиг. 21).

Сигнал Сч В, показанный на времен- нь1х диаграммах фиг. 18, 19 и 21, отражает время работы сумматора 10 со счетчиком 8 байтов (высокий уровень сигнала Сч Б) и со счетчиком 11 ядре- са (низкий уровень сигнала). В режиме Модификация МПК (фиг. 18 и 21) высокий уровень сигнала Сч Б характеризует время выдачи содержимого счетчика байтов на выход 26 устройства, а низ- кий уровень - содержимого счетчика адреса.

Формула изобр.етени

П;Р ВЬЙ;.К;„ IOTOPO O со,-50 ™. Ри«« - «°-«- МИЛ vjcij-iiw , f ттпничяпиы firFOTca. япоесапии зон памяти

динен с входом блока дешифрации нуля, выходом подключенного к синхронизирующему входу блока управления, группа управляющих входов-выходов которого

хронизации блока, адресации зон памяти соединена с первой группой управляющих входов коммутатора выбора данных, стробирующим входом регистра адреса

управляющих ВХидии-вмлим о лл... «

г,- -пттями гчетчи- ее зоны памяти и группой управляющих

гоелинена со счетными входами.смерчи «

uucM ncno ихоппв-выходов блока управления,ка байтов и счетчика адреса, управляющими входами .блока промежуточного хранения данных, коммутатора данных, дешифратора адреса зоны памяти и первходов-выходов блока управления, ад---; ресный вход которого соединен с первым выходом счетчика адреса, а тактовый вход - с входом устройства для

5

0 35

0

5

40

45 ным информационным входом сумматора, выходом подключенного к информационным входам счетчика байтов и счетчика адреса, первая группа разрядных выходов которого подключена к первому информационному входу дешифратора адреса зоны памяти, первая группа выходов дешифратора адреса зоны памяти подключена к группе адресных входов блока памяти, вторые группы разрядных выходов счетчика адреса и счетчика байтов соединены соответственно с входом задания режима блока управления и вторым информационным входом сумматора, и регистр адреса зоны памяти, причем первый информационный вход коммутатора данных, выход коммутатора выбора данных, синхронизирующий выход и входы запроса и установки блока управления являются соответствующими входами и выходами устройства для подключения к информационным выходу и входу, входу синхронизации байта и выходам запроса и начальной установки периферийного устройства, второй информационный вход и выход блока промежуточного хранения данных образуют вход-выход устройства для подключения к информационному входу-выходу оперативной памяти, первый, выход счетчика адреса и вход-выход управления обращением блока управления являются соответствующими выходом и входом-выходом устройства для подключения к первому адресному йходу и входу-выходу обращения оперативной памяти, выход блока дешифрации нуля, тактовьш вход счетчика байтов, соединенный с тактовым входом счетчика адреса, являются синхронизирующими выходом и входом устройства, вторые выходы счетчиков адреса и байтов и вход задания режима блока управления образуют вход-выход.устройства для подключения к выходу кода операции процессора ввода-вывода, о т л и ч а- . ю DI е е с я тем, что, с целью повышения пропускной способности устройства, в него введен блок адресации зон памя50 ™. Ри«« - «°-«- ттпничяпиы firFOTca. япоесапии зон памяти

™. Ри«« - «°-«- ттпничяпиы firFOTca. япоесапии зон памяти

хронизации блока, адресации зон памяти соединена с первой группой управляющих входов коммутатора выбора данных, стробирующим входом регистра адреса

зоны памяти и группой управляющих

зоны памяти и группой управляющих

ихоппв-выходов блока управления,входов-выходов блока управления, ад---; ресный вход которого соединен с первым выходом счетчика адреса, а тактовый вход - с входом устройства для

подключения к тактовому выходу процессора ввода-вывода, второй управляющий вход коммутатора выбора данных соединен с вторым выходом дешифратора адре-, са зоны памяти, второй информационный вход которого подключен к первому выходу регистра адреса зоны памяти, информационный и тактовый входы которого являются соответствующими входами «л устройства для подключения к выходу запроса присвоения зоны периферийного устройства и синхронизирующему входу устройства, первый выход регистра адреса зоны памяти является выходом ycT-j5 ройства для подключения к второму адресному входу оперативной памяти, а второй выход и группа информационных входов соединены соответственно с входом режима и группой выходов блока:-ад-2о ресации зон памяти, первая группа.адресных входов и группа блокировочных входов которого являются соответствующими группами входов устройства для - подключения к группам задающих входов 25 процессора ввода-вывода, а вторая группа адресных входов соединена с первой группой выходов дешифратора адреса зоны памяти.

группы соединены с выходами элементов И второй группы, группы входов которых подключены к соответствующим пря- мьи и инверсным выходам триггеров занятости зоны паЬм.ти группы, группа входов второго элемента И соединена с прямыми выходами триггеров занятости зоны памяти группы, первая группа информационных входов и управлянщий вход мультиплексора соединены с второй группой адресных входов блока, а вторая группа информационных входов соединена с группой выходов шифратора группа входов которого подключена к выходам элементов И второй группы, группа входов элемента И-ИЛИ соединена с выходом второго элемента И, входом режима блока и группой входов-выходов синхронизации блока, выход элемента И-ИЛИ соединен с группой входов-выходов блока, группа выходов , мультиплексора и выход второго элемента И образует группу выходов блока . 3. Устройство по п. 1, отличающееся тем, что блок управления содержит регистр режимов, узел дешифрации сигналов обмена с памятью и узел дешифрации сигналов обмана с периферийным устройством, причем группы управляющих входов, тактовые входы и первые информационные входы узлов дешифрации сигналов обмена с памятью и с периферийным устройством и регистра режимов соединены соответст- венно с группой управлякищх входов-выходов, тактовым входом и входом запроса блока, второй информационный вход регистра режима и выход узла дешифрации сигналов обмена с памятью образуют вход-выход управления обращением блока, а синхровходы соединены с входом синхронизации блока, группы выходов узлов дешифрации сигналов обмена с памятью и с периферийным устройством и регистра режимов подключены к группе управляющих входов-выходов блока, второй информационный вход узла дешифрации сигналов обмена с памятью является адресным входом блока, выход узла дешифрации сигналов обмена с периферийным устройством является выходом блока, третий информационный вход и вход начальной установки регистра режимов являются соответст-.; веино входами режимов и установки блока.

От

Фиг.5

20

16

19

Фие.д

26

Фиг.11

Фиг.9

к8,11

7

Фиг. /V

27

iai

Л

Фие. 15

Фи8.1б

0Lts,2f

Фив. 22

Авторы

Даты

1990-08-23—Публикация

1987-12-16—Подача