ментов И чтения, соединенного треть входом с выходом мультиплексора данных, первый, второй, третий и четвертый входы которого подключены соответственно к выходам узла чтения, регистра текущего адреса и первым выходам регистра текущей длины массива и регистра циклов, второй вход второго блока ус1 ления соединен с выходом узла элементов И записи, третий вход - с выходом дешифратора адреса, второй вход узла элементов И записи соединен с первым выходом блока обмена, третий выход блока обмена соединен с первым входом блока выполнения прерываний для внепродессорного обмена, четвертый выход - с вторым входом блока выполнения программных прерываний, третий вход блока обмена соединен с вторым выходом блока выполнение программных прерываний, четвертый вход - с вторым выходом блока выполнения прерываний для внепроцессорного обмена и вторым входом мультиплексора адреса, трети вход регистра цикла подключен к вторым входам регистров текущего адреса и текущей длины массива и выходу узла перезаписи, второй вход которого соединен с вторым выходом регистра теку1цей длины массива5первые входы регистра команды, регистров адреса первого и второго внешни устройств соединеР1ы с вторым выходо первого блока усиления, вторые входы - с выходом узла записи, выход регистра команды подключен к первому ВХОДУ узла задания последовательности операций и пятому входу мультиплексора данных, выход регистра адреса первого внещнего устройства подключен ко второму входу узла задания последовательности операции, второму входу мультиплексора адреса, шестому входу мультиплексора данных и первым входам коммутатора запросов внепроцессорного обмена и коммутатора программных

запросов, выход регистра адреса йторого внешнего устройства подключен к седьмому входу мультиплексора данных, к третьему входу мультиплексора адреса, к третьему входу узла задания последовательности операций и к BTopbiM входам коммутатора программных запросов и коммутатора запросов внепроцессорного обмена.

1

5

соедртненного выходом с третьим входом блока выполнения прерываний для внепроцессорного обмена, выход коммутатора программных запросов соединен с третьим входом блока выполнения программных прерываний, а третий вход - с третьим выходом второго блока усиления и третьим входом коммутатора запросов внепроцессорного обмена, подключенного четвертым входом к выходу счетчика фаз,, к пятому входу мультиплексора адреса и к четвертому, входу узла задания последовательности операций, выход которого соединен с пятым входом блока обмена, подключенного пятым выходом к входу счетчика фаз и к третьим входам регистров текущего адреса и текущей длины массива.

2.Устройство по П.1, о т л ичающееся тем, что блок выполнения прерываний для внепрйцессорного обмена содержит три триггера, три элемента И и элемент ШЖ-НЕ, причем синхронизирующий вход первого триггера является вторым входом блока, выход соединен с информационным входом второго триггера и первым входом первого элемента И, инверсньм выход и вход сброса второго триггера подключены соответственно к второму и третьему входам первого элемента И, синхронизирующий вход - к первому входу элемента ИЛИ-НЕ, а прямой выход и вход сброса - соответственно к информационному входу и входу сброса третьего триггера, синхронизирующий вход которого соединен с выходом элемента ИЛИ-НЕ, а прямой и инверсный выходу - соответственно к первым входам второго и третьего элементов И, вторыми входами подключенных к прямому выходу второго триггера, выход второго элемента. И является вторым выходом блока, выходы первого

третьего элементов И образуют первый выход блока, входы сброса первого и второго триггеров и первый ятый входы элемента ИЛИ-НЕ обра- зуют п.ервый вход блока.

3.Устройство по П.1, отличающееся тем, что узел заания последовательности операций одержит дешифратор, два элемена ИЛИ, два элемента И и элемент -ИЛИ, причем группа информационных ходов дешифратора является первым

.110061

ходом узла, первый и второй;управяющие входы - соответственно втоым и третьим входами узла, выход ервого элемента ИЛИ соединен с ервым входом первого элемента И, выход которого соединен с первым . входом второго элемента ИЛИ, а второй вход - с первым выходом дешифратора, вторым выходом соединенного с первым и вторым входами элемента И-ИЛИ, а третьим выходом с первым входом второгр элемента И, второй вход которого соединен с третьим входом элемента И-ИЛИ,выходы элемента И-ИЛИ и второго элемента И; соединены соответственно с вторым и третьим входами второго элемента ИЛИ, выход которого является выходом узла, а группа входов подключена -к группе выходов дешифратора, третий и четвертый входы элемента И-ИЛИ и первый и второй входы первого элемента ИЛИ образуют четвертьш вход узла,

А/Устройство по П.1, отличающееся тем, что узел перезаписи содержит элемент НЕ и два элемента И, причем первые входы первого и второго элементов И соединены через элемент НЕ с вторым входом узла, вторые входы - соответ- . ственно с первой и второй шинами первого входа узла, выходы элементов И и шина второго входа узла образуют выход узла.

5.Устройство по П.1, отличающееся тем, что узел записи содержит де1вифратор и семь элементов И, причем группа входов дешифратора образует первый вход узла, первый и второй входы первого элемента И подключены к соответствующим шинам-второго входа, а г.ыход соединен с первыми входами второго - шестого элементов И, вторые входы которых подключены к соответствующим выходам дешифратора, а выходы образуют выход узла.

6.Устройство по п.i, о т л и- V чающееся тем, что узел чтения содержит дешифратор, элемент ИЛИ элемент И, причем группа входов дешифратора образует первый вход узла, группа выходов подключена

. к группе входов элемента ИЛИ, выходом соединенного с первым входом элемента И, второй и третий входы которого образуют второй вход

узла, группа выходов дешифратора и выход элемента И образуют выход узла. .

7. Устройство по П.1, о т л ичающееся тем, что блок обмена содержит пять элементов Й-ИЛИ, элемент И, элемент ИЛИ, три триггера, три элемента задержки и три формирователя импульсов, причем выходы первого и второго элементов И-ИЛИ соединены соответственно с синхронизирующим входом и входом сброса первого триггера, выход третьего элемента И-ИЛИ соединен через первый элемент задержки с синхронизирующим вхЬдом второго триггера, выходы первого и второго триггеров образуют второй выход блока, выходы четвертого и пятого элементов И-ИЛИ соединены соответственно с синхронизирующим вхбдом и входом сброса третьего триггера, инверсньй выход которого соединен через первый формирователь импульсов с пятым выходом блока и входом второго формирователя импульсов, первые входы первого, второго и третьего элементов И-ИЛИ соединены с выходом элемента И,.БЖРрые входы - соответственно , второй и третьей шинами га РЭрго входа блока, третьи входы - соответственно с четвертой, пятой и первой шинами первого входа блока, четвертые входы первого и третьего элемен; тов И-ИЛИ соединены с четвертым входом блока, первым входом элемента ИЖ и через второй элемент задержки с первым и вторым входами четвертого элемента И-ИЛИ, пятые входы первого и третьего элементов И-ИЛИ соединены соответственно с тречьим и четвертым входами четвертого элемента И-ШШ, первым и вторым входами пятого, элемента И-ШТ и первой и второй шинами пятого вхо блока, пятый вход четвертого эле- / мента И-ИЛИ соединен с первым входо третьего формирователя импульсов,певой шиной второго входа блока и через третий элемент задержки с четвертым и пятым входами второго эле мента И-ИЛИ, шестым входом подключенного к инверсному выходу третьего триггера,шестой вход третьего элемен И-ИЛИ элемента И-ИЛИ соединен с треть входом пятого элемента И-ИЛИ и пято шиной первого входа блока, четвертьй вход пятого элемента И-ИЛИ соединен с второй шиной второго входа блока-и входом сброса второго триггера, второй вход элемента ИЛИ подключен к третьему входу блока, второй вход третьего формирователя импульсов соединен с второй шиной пятого входа блока, группа входов элемента И подключена к группе шин первого входа блока, шестая шина первого входа, соединенная с выходом элемента ИЛИ, и прямой выход третьего триггера образуют первый выход блока, выходы второго и третьего формирователей импульсов, первая и вторая шины второго входа блока, пятая и седьмая шины первого блока образуют третий выход блока, пятая, шестая и восьмая шины первого входа блока образуют четвертый выход блока

8. Устройство по п.1, о т л ичающееся тем, что блок выполнения программных,прерываний содержит группу узлов захвата общей шины, элемент ИЛИ, элемент задержки и шифратор, причем первый вход первого узла захвата общей шины группы является первым входом блока,первые входы остальных узлов захвата общей шины образуют третий вход блока, вторые входы узлов захвата общей шины группы образуют второй вход блока, первые выходы .подключены к группам входов шифратора и элемента ИЛИ, выход которого соединен с входом элемента задержки и вторым

1

15

выходом блока, вторые выходы узлов захвата общей шины группы, выход шифратора и выход элемента задержки образуют первый выход блока.

9. Устройство по п. 1 и 8, о тличающее. ся тем, что узел захвата общей шины содержит два триггера, элемент И-НЕ, элемент ИЛИи три элемента И, причем первый вход первого элемента И соединен с инверсным выходом первого триггера, прямой вход которого подключен к первым входам второго и третьего элементов И и информационному вхоДу второго триггера, а вход сброса - к выходу элемента И-НЕ, вторые входы второго и третьего элементов И подключены соответственно к инверсным и прямым выходам второго триггера, синхронизирующим входом соединенного с выходом элемента ИЛИ-НЕ, а входом сброса с информационным входом первого триггера и вторым входом первого элемента И, первым.входом элемента И-НЕ и первым входом узла, синхронизируюшлй вход первого триггера, соединенньй с первым входом элемента ИЛИ-НЕ, второй вход элемента И-НЕ, соединенный с вторым входом элемента ИЛИ-НЕ,и третий вход элемента ИЛИ-НЕ образуют второй вход узла, выход третьего элемента И является первым выходом УЗЛА, а выходы первого и второго элементов И образуют второй выход узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1399751A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВНЕШНИХ УСТРОЙСТВ С ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШНОЙ, содержащее . дешифратор адреса, блок выполнения программных прерываний, блок обмена, мультиплексор адреса и два блока усиления, группы входов - выходов которых являются соответственно первой и второй группами входов - выходов устройства, первые иходы и выходы соединены соответственно с первыми и вторыми выходами и входами блока обмена, выход мультиплексора адреса соединен с входом дешифратора адреса, a первый выход блока вьшолнения программных прерываний подключен к второму входу первого блока усиления, отличающееся тем, что, с цеЛью повышения пропускной способности устройства, в него введены регистр команды, регистр адреса первого внешнего устройства, регистр адреса второго внешнего устройства, узел задания последовательности операций, счетчик фаз, коммутатор запросов внепроцессорного обмена, коммутатор программных запросов, регистры начального и текущего адреса , регистры начальной и текущей длины массива, регистр циклов, узел перезаписи, мультиплексор данных, узел записи и узел чтения, узлы , элементов И записи и чтения, блок .вьшолнения прерываний для внепроцессорного обмена, причем третий, четвертый и пятый входы первого блока усиления соединены соответственно с выходами узла элементов И чтения, регистра текущего адреса и первым выходом .блока выполнения прерываний для внепроцессорного обмена, первый вход блока вьтолнения програм«Л мных прерываний соединен с первым выходом регистра циклов, первьй выход первого блока усиления соединен с первыми входами узла элементов И записи,- регистра циклов, регистров начального адреса и начальной длины массива, выходы регистра начального о адреса и регистра начальной длины массива связаны соответственно с 3 первыми входами регистра текущего адреса и регистра текущей длины массива, третий выход первого блока :л усиления соединен с первыми входами узла записи, узла чтения и мультиплексора адреса, первый выход первого блока, усиления соединен с вторыми входами узла чтения и узла записи, подключенного выходом к вторым входам регистров начального адреса, начальной длины массива, регистра циклов и первому входу узла перезаписи, второй и первый выходы второго блока усиления соединены соответственно с первым и вторым входами узла эле

Изобретение относится к области вычислительной техники и может быть использовано в управляющих вычислительных комплексах, имею1ЦИХ интерфейс Общая шина.и содерж щих внешние устройства, использующи другие интерфейсы. Известны устройства для сопряжения ЭВМ с внешними устройствами, со держащие дешифратор, регистр управления, блок вьшолнения прерывания, блок обмена, коммутатор, переключатель и блоки усиления, причем трети выход и второй вход первого блока усиления соединены соответственно с ,BTopbw входом и четвертым выходом второго блока усиления, первый и второй выходы коммутатора соединены с третьим и четвертым входами второго блока усиления, выход переключателя соединен с четвертыми входами блока вьшолнения прерывания и дешифратора, четвертый выход дешифратора соединен с четвертым входом блока обмена 1J . В этих устройствах обращение к периферийным устройствам осуществляется через групповое устройство., имеющее собственный адресуемый регистр управления и схему инициирования и чтения запросного слова прерывания. Наличие группового устройства существенно усложняет программирование подключенных к нему внешних устройств особенно в случае многопрограммного режима работы вычислительного комплекса, а также увеличивает время реакции ЭВМ на сигналы прерывания от внешних устройств, операцию чтения или записи. Такая ситуация возникает, например, при необходимости ввода информации с многоканального аналого-цифрового преобразоватёля. При этом ЭВМ передает на коммутатор преобразователя массив адресов, вьтолняя операцию записи, и принимает с преобразователя массив дынных, вьтолняя операцию чтения.

В указанных устройствах- для выполнения такой последовательности операций необходимо сформировать адрес канала, напряжение на котором требуется измерить и выдать его по адресу первого устройства (коммутатора),при возникновении готовности преобразователя - сформировать адрес ячейки памяти и принять по этому адресу данные из второго устройства (преобразователя) . Указанная последовательность операций должна быть запрограммирована на ЭВМ. Выполнение этой программы требует значительного времени, что и является главной причиной низкой пропускной способности известных устройств.

Кроме того, в этих устройствах имеется общая линия запроса прерывания, что увеличивает время реакции ЭВМ на сигналы прерывания, так как прерывание от последующего устройства может быть воспринято только после обслуживания запроса от предыдущего устройства.

Наиболее близким к предлагаемому . техническим решением является устройство для сопряжения ЦВМ с периферийными устройствами, содержащее дешифратор, два триггера, блок выдачи прерываний, блок управления обменом, два коммутатора, сдвиговый регистр, блок формирования четности и два блока усилителей сигналов связи, причем первые и вторые входы и выходы блока управления обменом соединены соответственно с первыми и вторыми выходами и входами блоков усилителей сигналов связи, третьи вход и выход - соответственно с первыми выходом дешифратора и входом

сдвигового регистра, первые входы триггеров и вход дешифратора соединены с соответствующими выходами первого блока усиления сигналов связи, группа входов - выходов которого, является первой группой входов выходов устройства, а группа входов подключена к группам выходов первого коммутатора и блока вьщачи прерывани первым входом соединенного с соответствующими входами блока управления обменом, первого коммутатора и выходом второго блока, усиления сигналов связи, другие входы которого подключены к соответствующим входам сдвигового регистра, блока формирования четности, первого коммутатора и блока управления обменом, входы - к соответствующим выходам блока формирования четности, первого триггера и блока управления обменом, а группа входов - выходов является второй группой входов - выходов устройства, третий вход блока формирования четности подключен к выходу сдвигового регистра, группы входов и выходов которого соединены соответственно с группами выходов и входов второго коммутатора и группами входов и выходов дешифратора 2j .

Недостаток этого устройства состоит в низкой пропускной способности вследствие ограниченных функциональных возможностей, требую1щх повышенных затрат машинного времени в процессе обмена.

Целью изобретения является повьппение пропускной способности устройства.

Поставленная цель достигается тем, что в устройство, содержащее дешифр1тор адреса, блок выполнения программных прерьгоаний, блок обмена, мультиплексор адреса и два блока усиления , группы входов - выходов которых являются соответственно первой и второй группами входов - выхо-г дов устройства, первые входы и вы- ходы соединены соответственно с первыми и вторыми выходами и входами блока обмена, выход мультиплексора адреса соединен с входом дешифратора адреса, а первый выход блока вьшолнения программных прерываний подключен к второму входу первого блока усиления, введены реги.стр команды, регистр адреса первого внешнего устройства, регистр адреса 5 . второго внешнего устоойства. узел задания последовательности операци счетчик фаз, коммутатор запросов в процессорного обмена,коммутатор программных запросов, регистры начального и текущего адреса, регист начальной и текущей длины массива, регистр циклов, узел перезаписи, мультиплексор данных, узел записи и узел чтения, узлы элементов И запи и чтения и блок вьтолнения прерыва ний для внепроцессорного обмена, причем третий, четвертый и пятый в ды первого блока усиления соединены соответственно с выходами узла элементов И чтения, регистра текущего адреса и первым выходом блока вы полнения прерываний для внепроцессорного обмена, первый вход блока вьтолнения программных прерьгоаний соединен с первым выходом регистра циклов, первый выход первого блока усиления соединен с первыми входами узла элементов И записи, регистра циклов, регистров начального адреса и начальной длины массива, выходы регистров начального адреса и начальной длины массива связаны соответственно с первыми входами регистра текущего адреса и регистра текущей длины массива, третий выход первого блока усиления соединен с первыми входами узла записи, узла чтения, и мультиплексора адреса, первый выход первого блока усиления соединен с вторыми входами узла чтения и узла записи, подключенного выходом к вторым входам регистров начального адреса, начальной длины массива, регистра циклов и первому входу узла перезаписи, второй и первый выходы второго блока усиления соединены соответственно с первым и вторым входами узла1 элементов И чтения, соединенного третьим входом с выходом мультиплексора данных, первый, второй, третий и четвертый входы которого подключены соответственно к выходам узла чтени регистра текущего адреса и первым выходам регистра текущей длины массива и регистра циклов, второй вход второго блока усиления соединен с в ходом узла элементов И записи, третий вход - с выходом дешифратора адреса, второй вход узла элементов записи соединен с первым выходом блока обмена, третий выход блока 36 обмена соединен с первым входом блока выполнения прерываний для внепроцессорного обмена,четвертый выход - с вторым входом блока выполнения программных прерываний, третий вход блока обмена соединен с вторым выходом блока выполнения программных прерываний,четвертый вход - с вторым выходом блока выполнения прерываний для внепроцессорного обмена и вторым входом мультиплексора адреса, третий вход регистра цикла подключен к вторым входам регистров текущего адреса и текущей длины массива и выходу узла перезаписи, второй вход которого соединен с вторым выходом регистра текущей длины массива, первые входы регистра команды, регистров адреса первого и второго внешних устройств соединены с вторым выходом первого блока усиления, вторые входы - с выходом, узла .записи, выход регистра команды подключен к первому входу узла задания последовательности операций и пятому входу мультиплексора данных, выход регистра адреса первого внешнего устройства подключен к второму входу узла задания поседовательности операций,второму входу мультиплексора адреса, шестому входу мультиплексора данных и первым входам коммутатора запросов внепроцессорного обмена и коммутатора программньи запросов, выход регистра адреса второго внешнего устройства подключен к седьмому входу мультиплексора данных, к третьему входу мультиплексора адреса, к третьему входу узла задания последовательности операций и к вторым входам коммутатора программных запросов и коммутатора запросов внепроцессорного обмена, соединенного выходом с третьим входом блока выполнения прерываний для внепроцессорного обкена, выход коммутатора программных запросов соединен с третьим входом блока выполнения программных прерываний, а третий вход - с третьим выходом второго блока усиления и третьим входом коммутатора запросов внепроцессорного обмена, подключенного четэертым входом к выходу счетчика фаз, к пятомувходу мультиплексора адреса и к четвертому входу узла задания 7.1 последовательности операций, выход которого соединен с пятым входом блока обмена, подключенного пятым выходом к входу счетчика фаз и к третьим входам регистров текущего адреса и текущей длины массива. Блок выполнения прерываний для внепроцессорного обмена содержит три триггера, три элемента И и элемент ИЛИ-НЕ, причем синхронизируюищи вход первого триггера является вторым входом блокаj выход соединен с информационным входом второго триггера и первым входом первого элемента И, инверсный выход и вход сброса второго триггера подключены соответственно к второму и третьему входам iiepaoro элемента И, синхронизирунщий вход - к первому входу элемента ИЖ-НЕ, а прямой выход и вход сброса - соответственно информационному входу и входу сбро са третьего триггера, синхронизирую щий вход которого соединен с выходо элемента ШШ-НЕ, а прямой и инверсный выходы - соответственно к первым входам второго и третьего элементов И, вторыми входами подключенных к прямому выходу второго триггера, выход второго элемента И является вторым выходом блока, выходы первог и третьего элементов И образуют пер вый выход блока, входы сброса перво и второго триггеров и первый - пяты входы элемента ИЛЙ-НЕ образуют первьй вход блока. Узел задания последовательности операций содержит дешифратор, два элемента ИЛИ, два элемента И и элемент И-ИЛИ, причем группа информационных входов дешифратора является первым входом узла, первый и второй управляющие входы - соответственно вторым и третьим входами узла, выхо первого элемента ИЛИ соединен с перв входом первого элемента И, выход ко торого соединен с первым входом вто рого элемента ИЛИ, а второй вход первым выходом дешифратора, вторым вых:одом соединенного с первым и вто рым входами элемента И-ИЛИ, а третьим выходом - с первым входом вторЬго элемента И, второй вход которого соединен с третьим входом элемента И-ШВД, выходы элемента И-ИЛИ и второго элемента И соеди нены соответственно с вторым и трет им входами второго элемента ИЛИ, выход которого является,выходом уза, а группа входов подключена к . группе выходов дешифратора, третий и четвертый входы элемента ИтИЛИ и первый и второй входы первого элемента ИЛИ образуют четвертый вход узла. Узел перезаписи содержит элемент НЕ и два элемента И, причем первые входы первого и второго эдементов И соединены через элемент НЕ с вторым входом узла, вторые входы - соответственно с первой ивторой шинами первого входа узла, выходы элементов И и шина второго входа узла образуют выход узла. Узел записи содержит дешифратор и семь элементов И, причем группа входов дешифратора образует первый вход узла, первый и второй входы первого элемента И подключены к соответствующим шинам второго входа, а выход соединен с первыми входами второго - шестого элементов И,вторыевходы которых подключены к соответствуюпщм выводам дешифратора, а выходы образуют выход узла. Узел чтения содержит дешифратор, элемент ИЛИ и элемент И, причем группа входов дешифратора образует первый вход узла, группа выходов подключена к группе входов элемента ИЛИ, выходом соединенного с первым входом элемента И, второй и третий входы которого образуют второй вход узла, группа выходов дешифратора и выход элемента И образуют выход узла. Блок обмена содержит пять элементов И-ИЛИ, элемент И, элемент ИЛИ, три триггера, три элемента задержки и три формирователя импульсов, причем выходы первого и второго элементов И-ИЛИ соединены соответственно с синхронизирующим входом и входом сброса первого триггера, выход третьего элемента И-ИЛИ соединен через первый элемент задержки с синхронизирующим входом второго триггера, выходы первого и второго триггеров образуют второй выход блока, выходы четвертого и пятого элементов И-ИЛИ соединены соответственно с синхрони. зирующим входом и входом сброса третьего триггера, инверсный выход которого соединен через первый формирователь импульсов с пятым выходом блока и входом второго

формирователя импульсов, первые входы первого, второго и третьего элементов И-ИЛИ соединены с выходом элемента И, вторые входы соответственно с первой, второй и третьей шинами первого входа блока, третьи входы - соответственно с четвертой, пятой и первой шинами первого входа блока, четвертые входы первого и третьего элементов И-ИЛИ соединены с четвертым входом блока, первым входом элемента ИЛИ и через второй элемент задержки с первым и вторым входами четвертого элемента И-ИЛИ,пятые входы первого и третьего элементов И-ШШ соединены соответственно с третьим и четвертым входами четвертого элемента И-ИЛИ и первым и вторым входами пятого элемента И-ИГМ и первой и второй шинами пятого входа блока, пятьш вход четвертого элемента И-ИЛИ соединен с первым входом третьего формирователя импульсов, первой шиной второго входа блока и через третий элемент задержки с четвертым и пятым входами второго элемента И-ИЛ шестым входом подключенного к инверсному выходу третьего триггера, шестой вход третьего элемента И-ИЛИ соединен с третьим входом пятого элемента И-ИЛИ и пятой шиной первого входа блока, четвертый вход пятого элемента И-ИЖ соединен с второй шиной второго входа блока и входом сброса второго триггера,второй вход элемента ИЛИ подключен к третьему входу блока, второй вход третьего формирователя импульсов соединен с второй шиной пятого вход блока, группа входов элемента И подключена к группе шин первого входа блока, шестая шина первого входа соединенная с выходом элемента ИЛИ, и прямой выход третьего триггера образуют первый выход блока, выходы второго и третьего формирователей импульсов, первая и втораяшины второго входа блока, пятая и седьмая щины первого блока.образуют третий выход блока, пятая, шестая и восьма шины первого входа блока образуют четвертьй выход блока.

Блок вьтолнения программных прерываний содержит группу узлов захвата общей шины, элемент ИЛИ, элемент задержки и шифратор, причем

первый вход первого узла захвата общей шины группы является первым входом блока, первые входы остальных узлов захвата общей шины образуют третий вход блока, вторые входы узлов захвата общей шины группы образуют второй вход блока, первые выходы подключены к группам входов шифратора и элемента ИЛИ, выход которого соединен с входом,элемента задержки и вторым выходом блока,вторые выходы узлов захвата общей шины группы, выход шифратора и выход элемента задержки образуют первый выход блока.

Узел захвата общей шины содержит два триггера, элемент И-НЕ, элемент ИЛИ-НЕ и три элемента И, причем первый вход первого элемента И соединен с инверсным выходом первого триггера,прямой вход которого подключен к первым входам второго и третьего элементов И и информационному входу второго триггера, а вход сброса - к выходу элемента И-НЕ, вторые входы второго и третьего элемента И подключены соответственно к инверсным и прямым выходам второго триггера,синхронизирующим входом соединенного с выходом элемента ИЛИ-НЕ а входом сброса с информационным входом первого триггера и вт.орым входом первого элемента И,первым входом элемента И-НЕ и первым входом узла, синхронизирующий вход первого триггера, соединенньй с первым входом элемента ИЛИ-НЕ,второй вход элемента И-НЕ, соединенный с вторым входом элемента ИЛИ-НЕ, и третий вход элемента ИЛИ-НЕ образуют второй вход узла, выход третьего элемента И является первым выходом узла, а выходы первого и Второго элементов И образуют второй выход узла., .

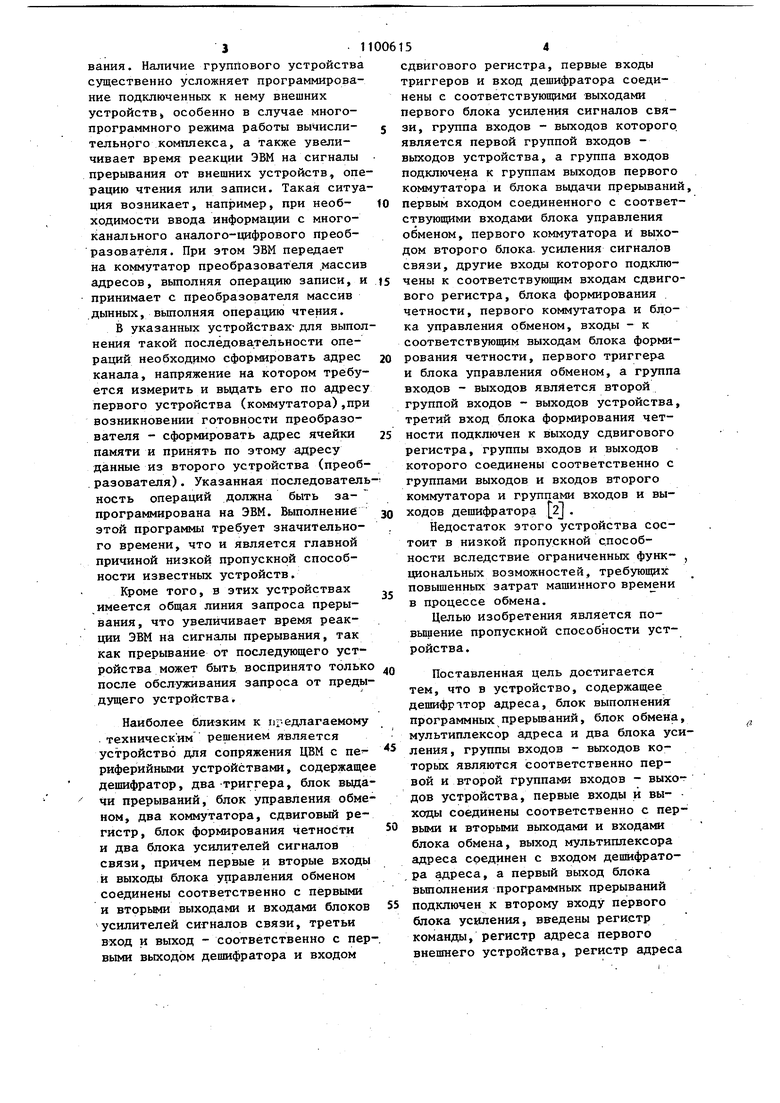

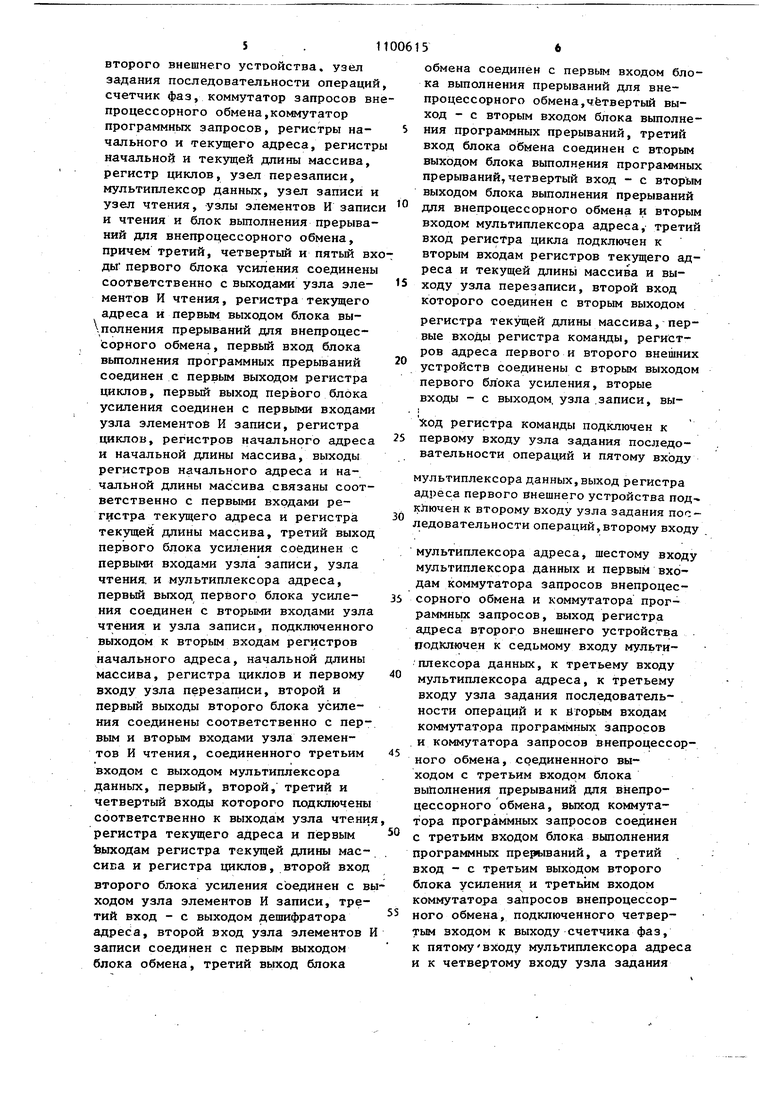

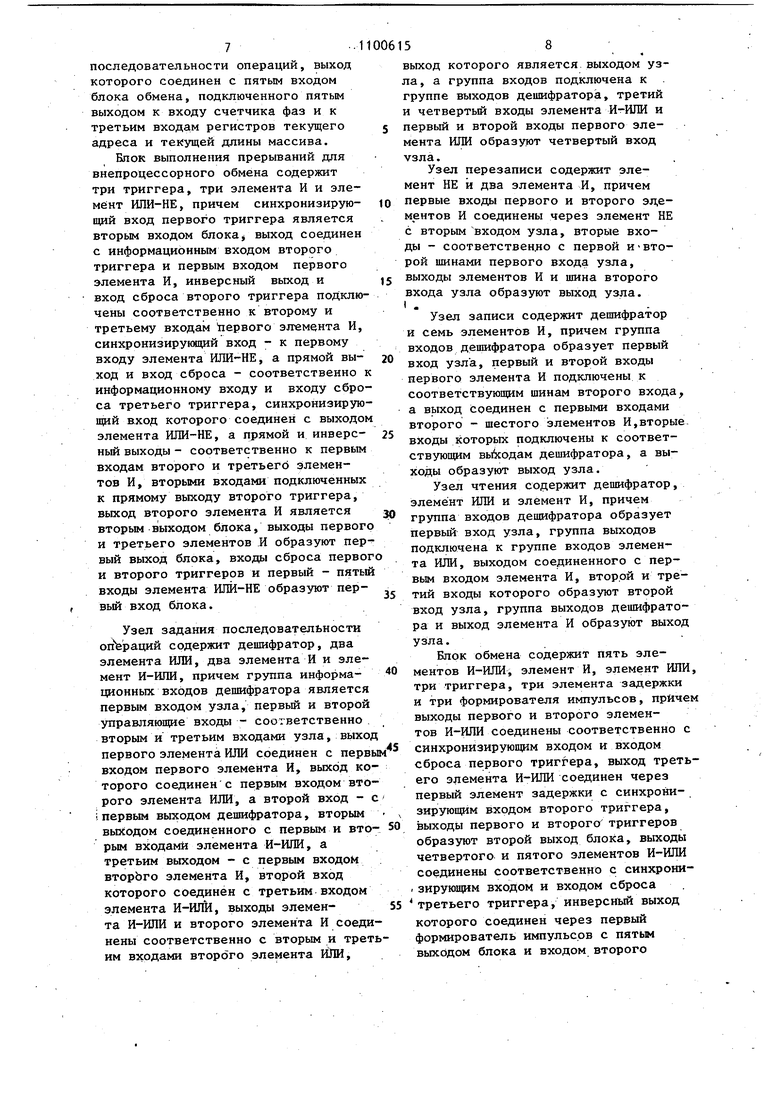

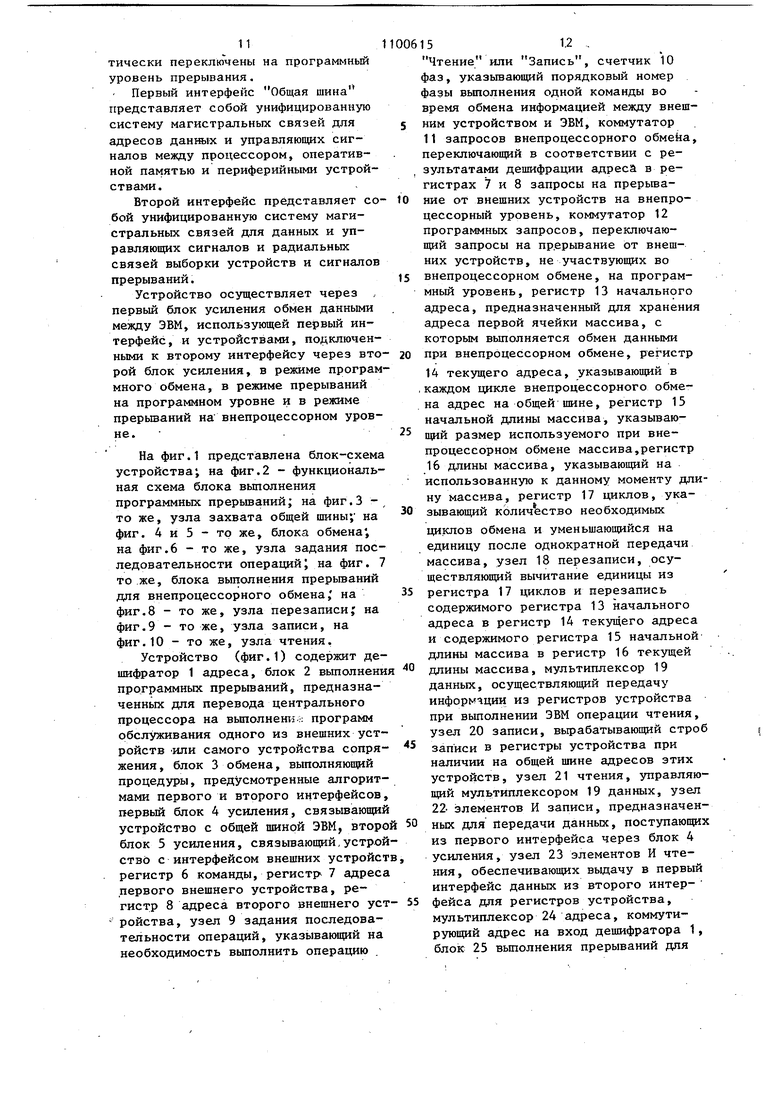

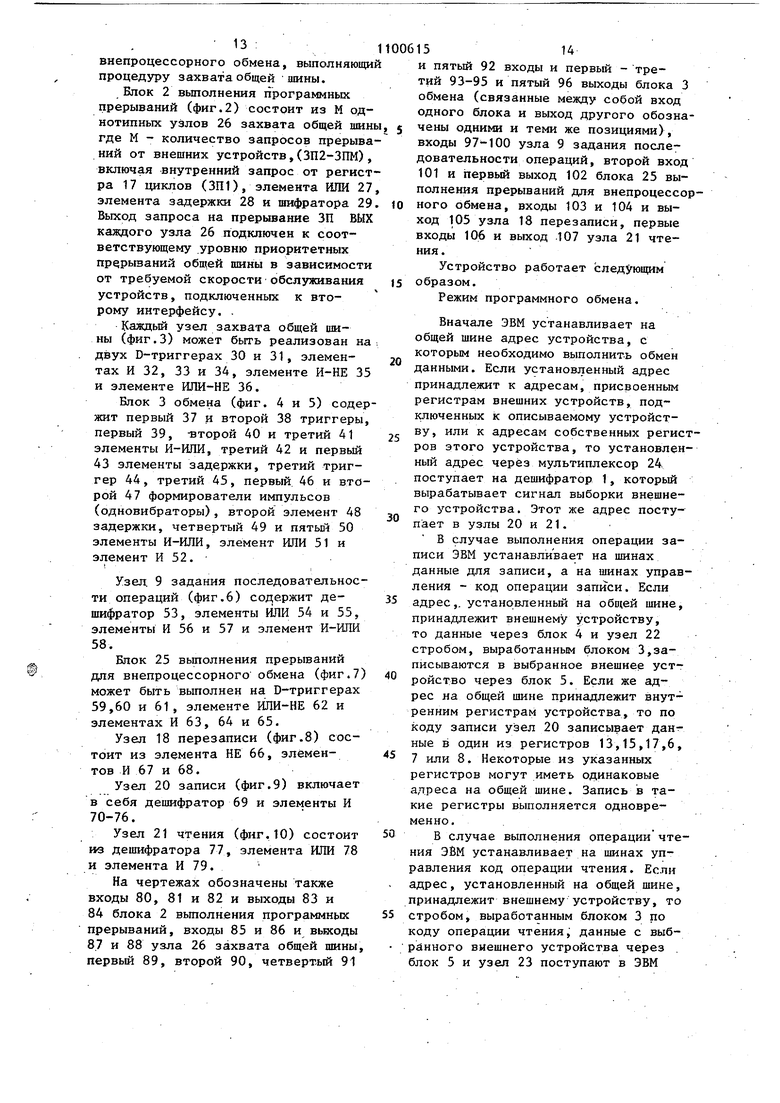

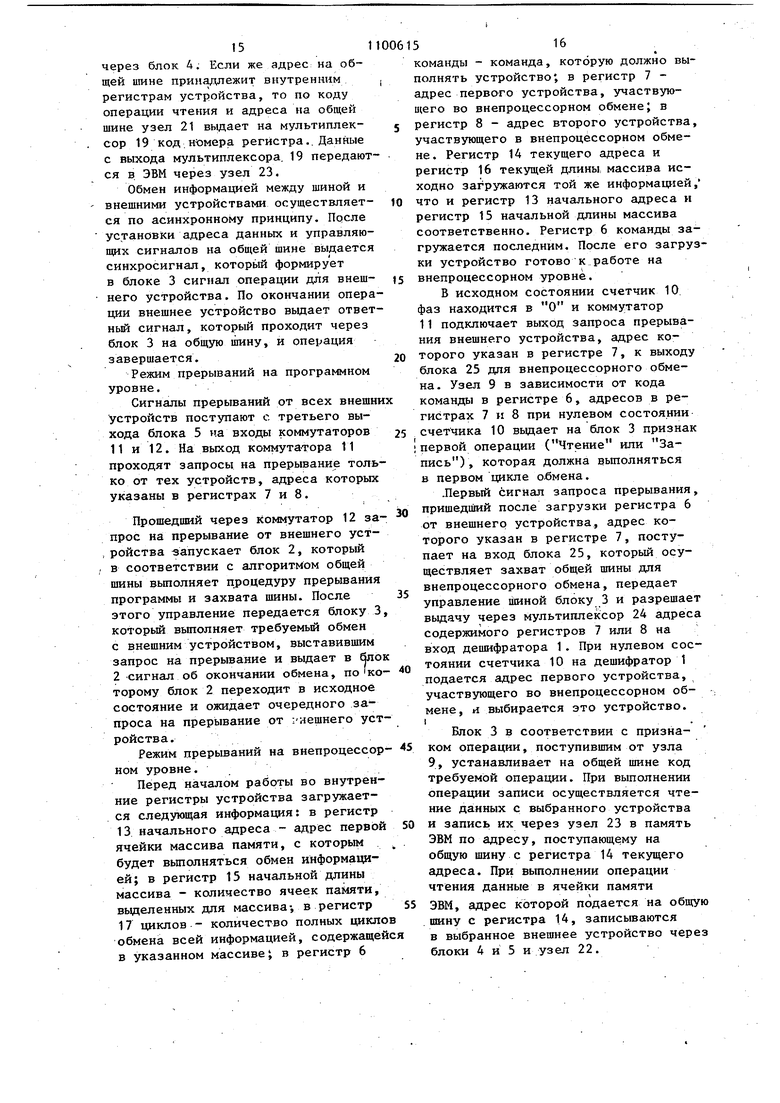

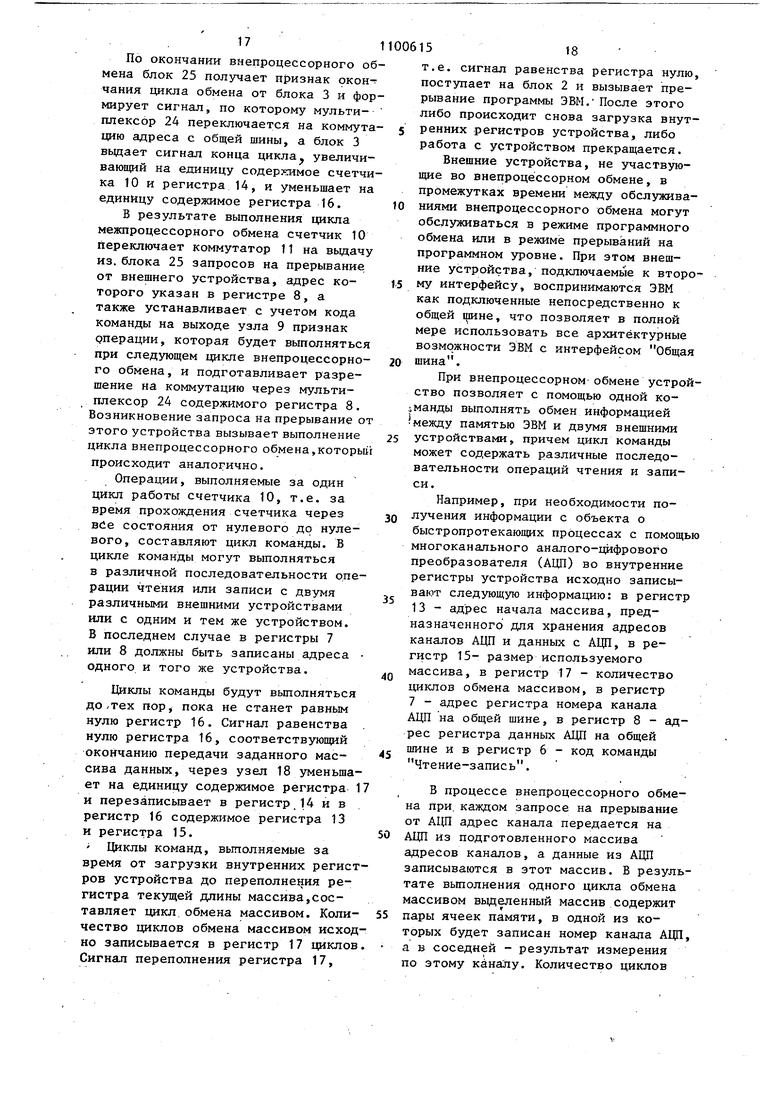

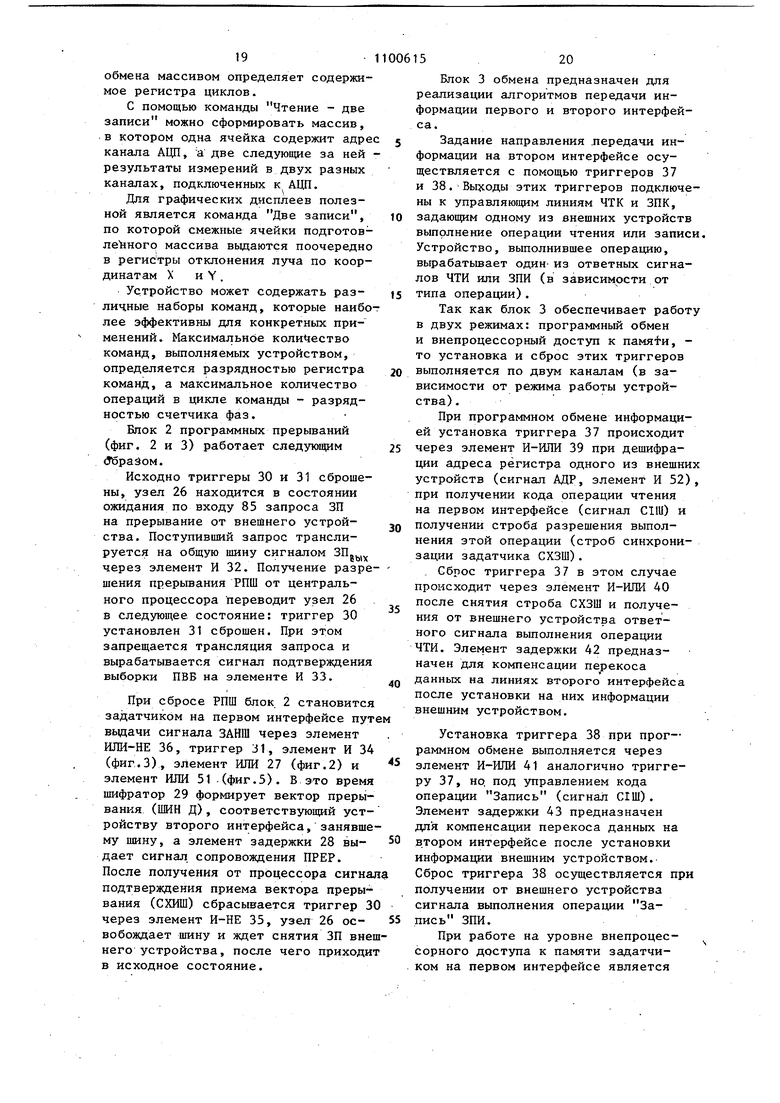

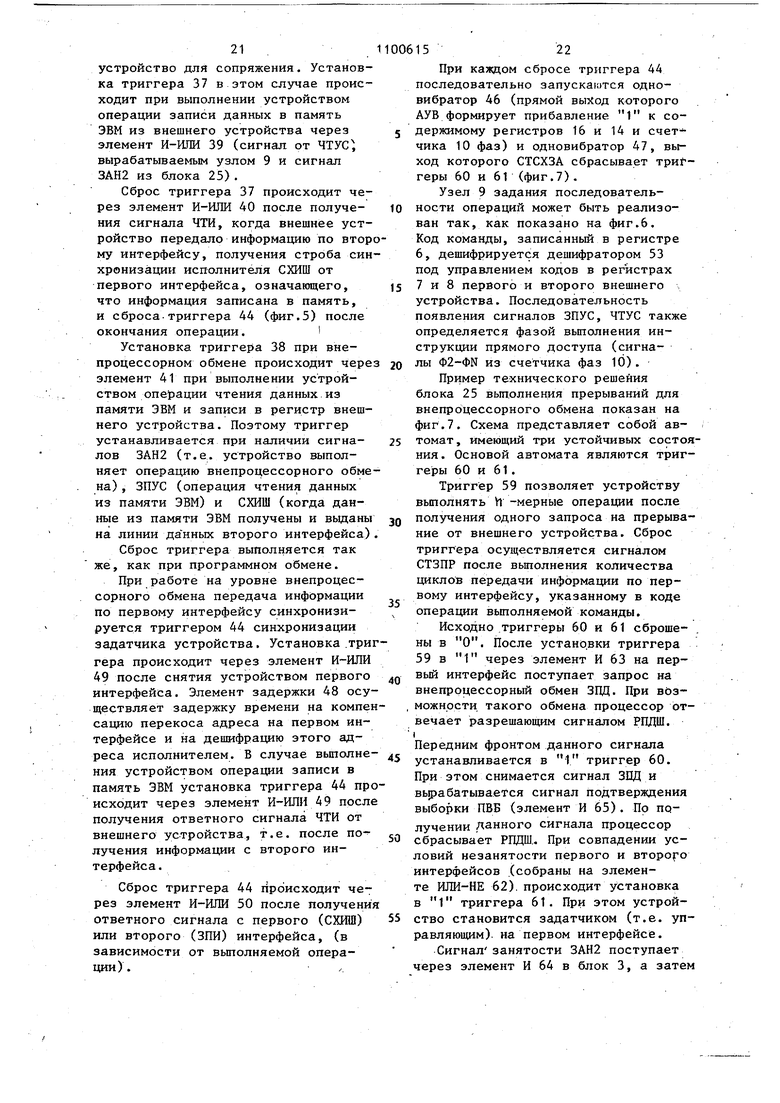

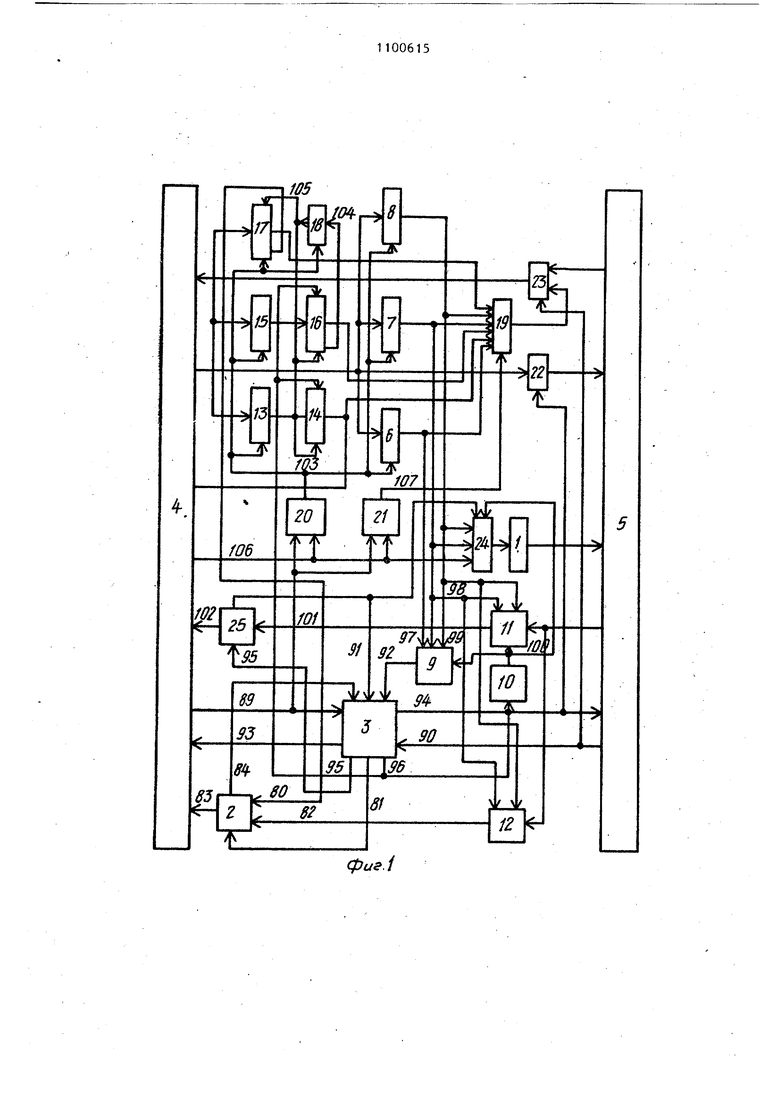

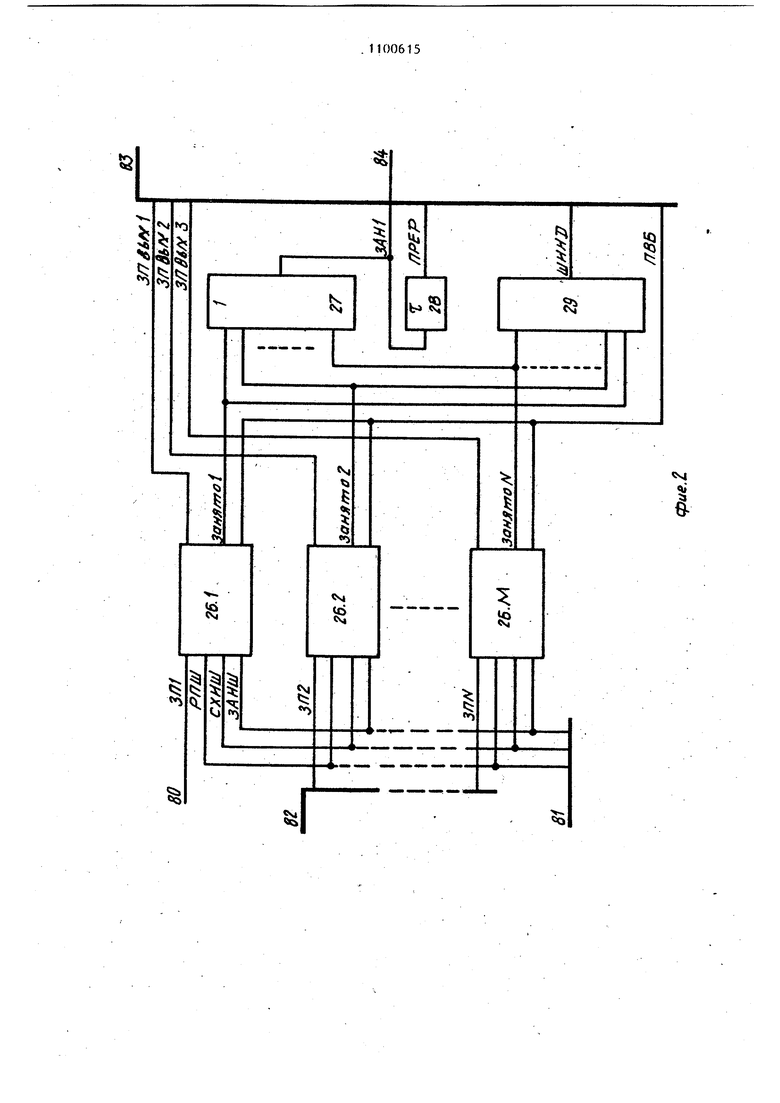

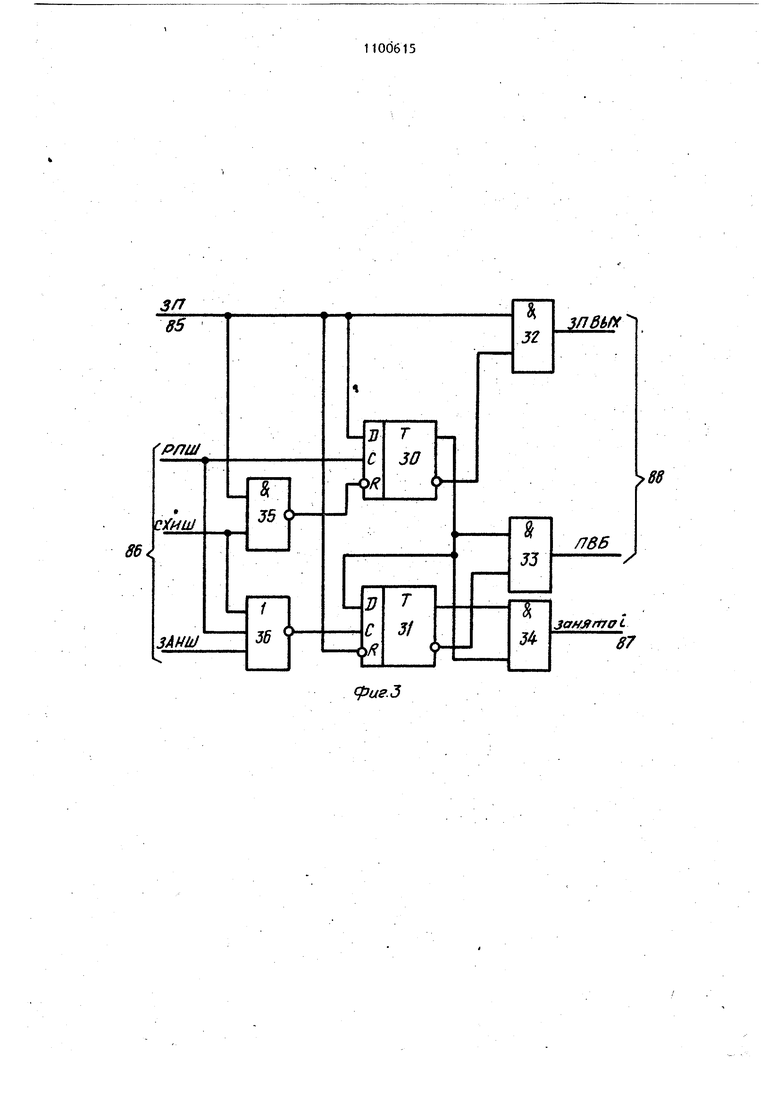

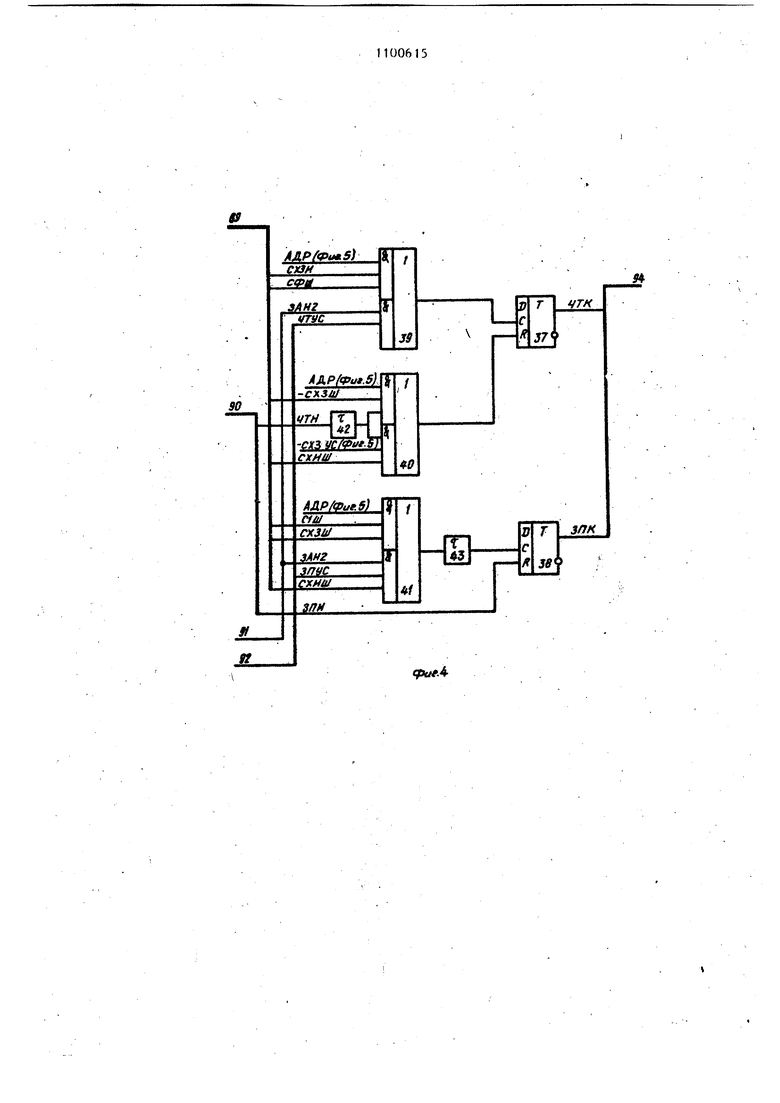

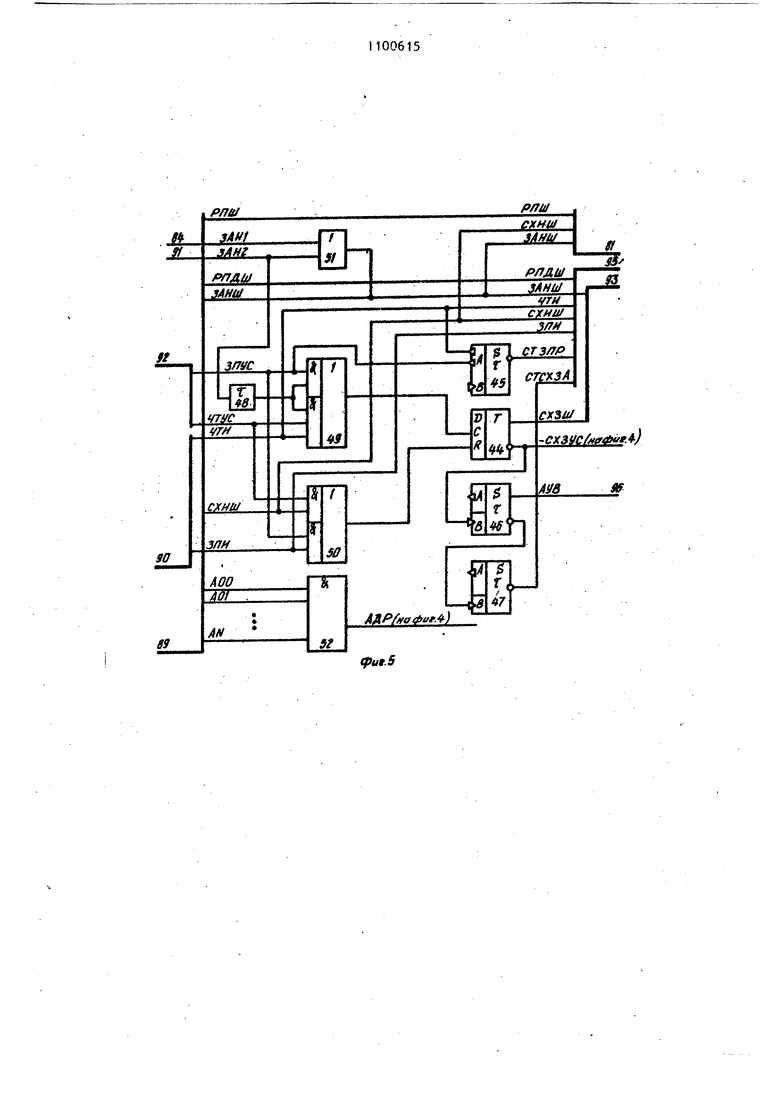

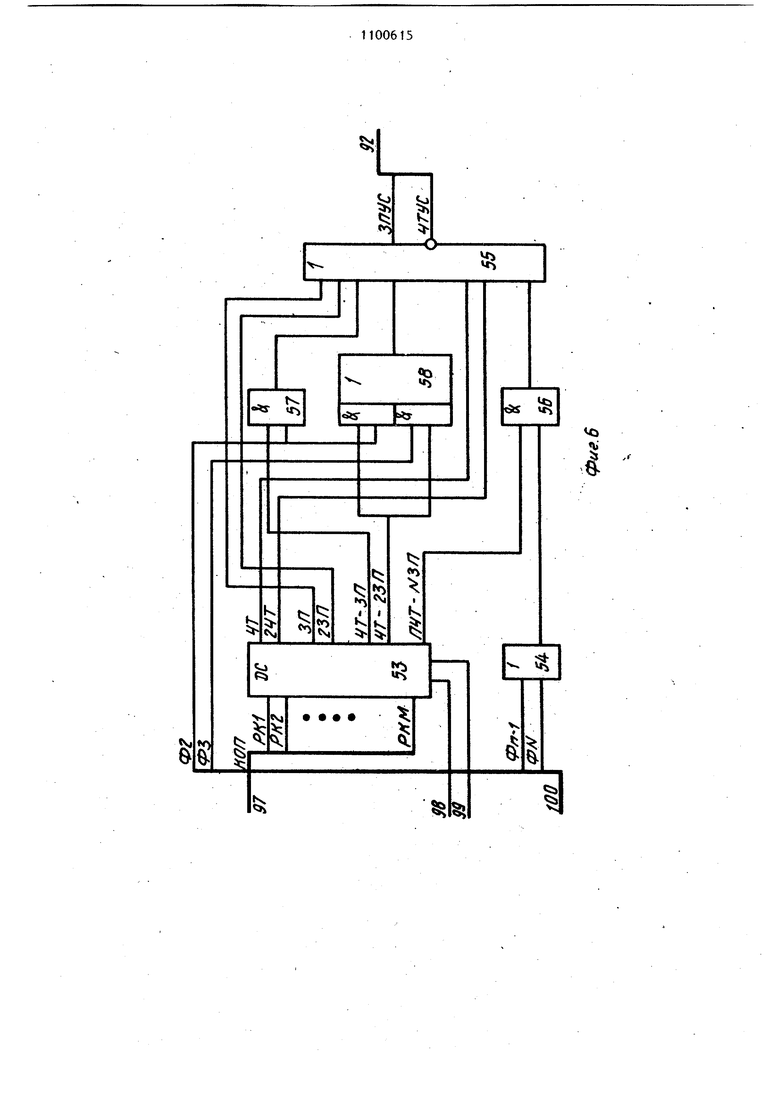

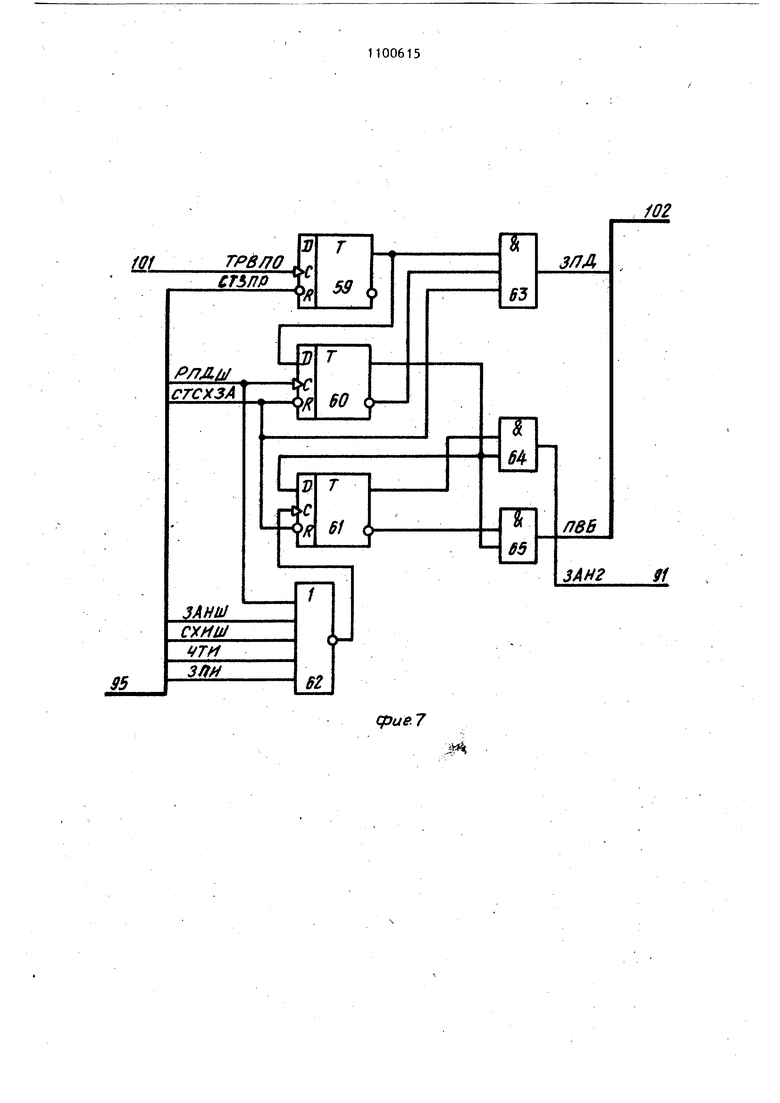

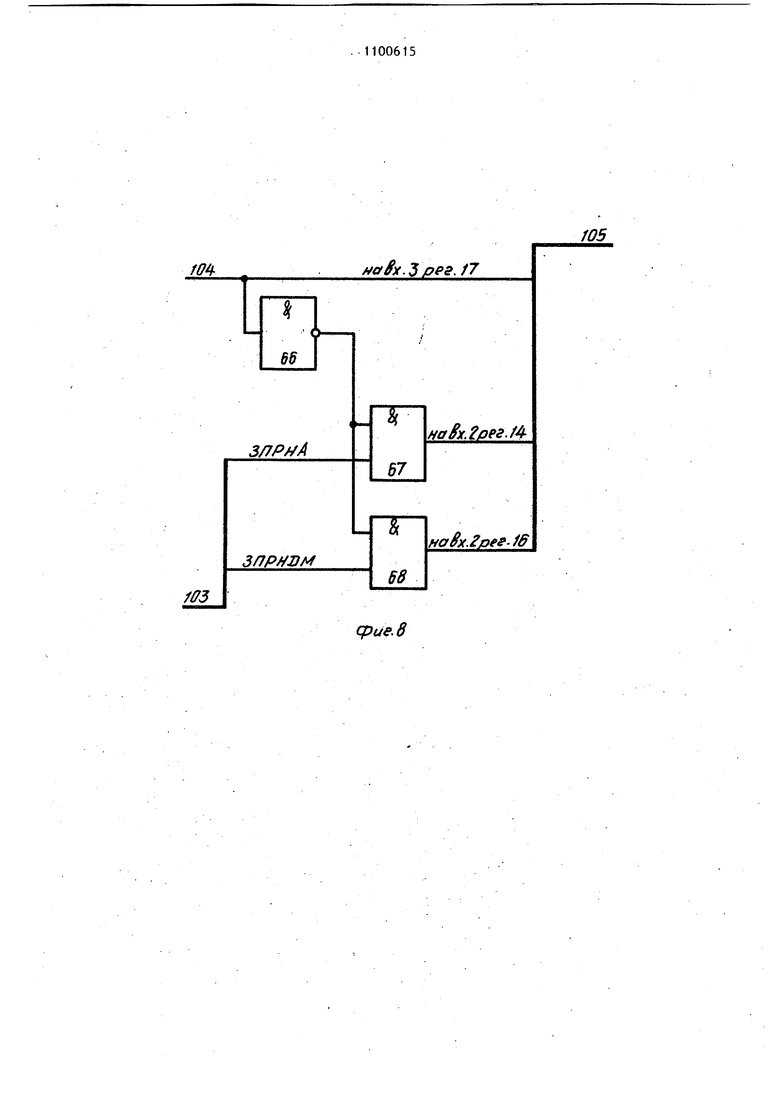

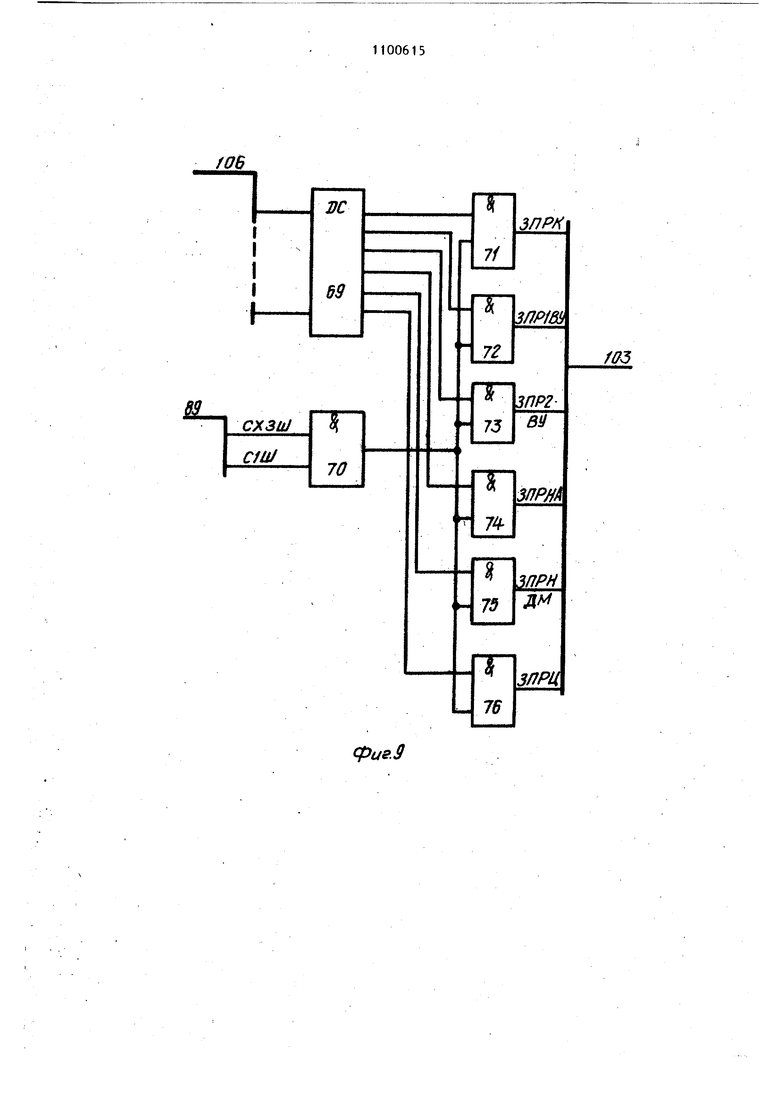

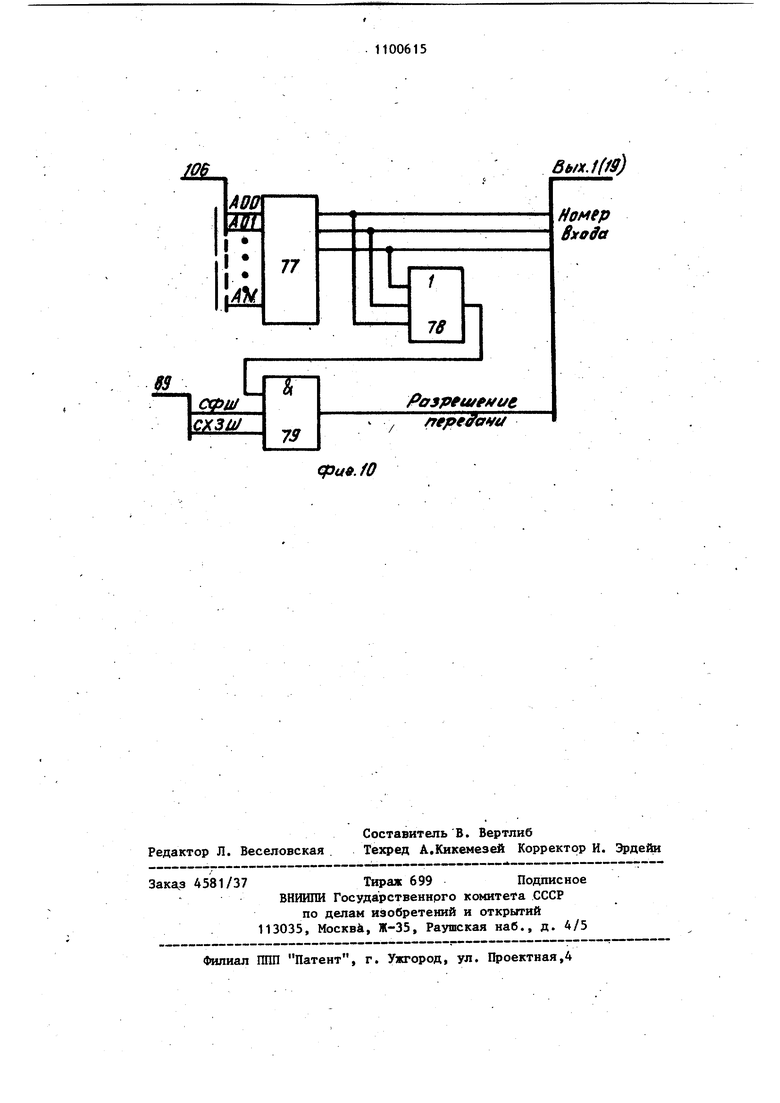

Устройство позволяет подключать любые два внешних устройства, адреса которых указаны в регистрах адреса первого и второго устройств, к внепроцессорному Уровню прерывания и в соответствии с одной командой, записанной в регистре команд, выполнять в любом сочетании операции записи или чтения с адресованными устройствами до полной передачи заданного массива, при этом остальные внешние устройства автома11тически переключены на программный уровень прерывания. Первый интерфейс Общая шина представляет собой унифицированную систему магистральных связей для адресов данных и управляющих сигналов между процессором, оперативной памятью и периферийными устройствами. Второй интерфейс представляет со бой унифицированную систему магистральных связей для данных и управляющих сигналов и радиальных связей выборки устройств и сигналов прерываний. Устройство осуществляет через первый блок усиления обмен данными между ЭВМ, использующей первый интерфейс, и устройствами, подключенными к второму интерфейсу через вто рой блок усиления, в режиме програм много обмена, в режиме прерываний на программном уровне и в режиме прерываний на внепроцессорном уровне. . На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока вьшолнения программных прерьшаний; на фиг.3 то же, узла захвата общей шины; на фиг. 4 и 5 - то же, блока обмена; на фиг.6 - то же, узла задания последовательности операцийJ на фиг. 7 то .же, блока выполнения прерьгеаннй для внепроцессорного обмена, на фиг.8 - то же, узла перезаписи; на фиг.9 - то же, узла записи, на фиг.10 - то же, узла чтения, Устройство (фиг.1) содержит дешифратор 1 адреса, блок 2 выполнени программных прерываний, предназначенных для перевода центрального процессора на выполнена:; программ обслуживания одного из внешних устройств ИЛИ самого устройства сопряжения, блок 3 обмена, выполняющий процедуры, предусмотренные алгоритмами первого и второго интерфейсов первый блок 4 усиления, связывающий устройство с общей шиной ЭВМ, второ блок 5 усиления, связывающий,устрой ство с интерфейсом внешних устройст регистр 6 команды, регистр 7 адреса первого внешнего устройства, регистр 8 адреса второго внешнего уст ройства, узел 9 задания последовательности операций, указываниций на необходимость выполнить операцию 151.2 . Чтение или Запись, счетчик 10 фаз, указьгаающий порядковый номер фазы вьтолнения одной команды во время обмена информацией между внешним устройством и ЭВМ, коммутатор 11 запросов внепроцессорного обмена, переключающий в соответствии с результатами дешифрации адреса в регистрах 7 и 8 запросы на прерьшание от внешних устройств на внепроцессорный уровень, коммутатор 12 программных запросов, переключающий запросы на пр.ерывание от внешних устройств, не участвующих во внепроцессорном обмене, на программный уровень, регистр 13 начального адреса, предназначенный для хранения адреса первой ячейки массива, с которым вьтолняется обмен данными при внепроцессорном обмене, регистр 14 текущего адреса, указывающий в каждом цикле внепроцессорного обмена адрес на общейшине, регистр 15 начальной длины массива, указывающий размер используемого при внепроцессорном обмене массива,регистр 16длины массива, указывающий на использованную к данному моменту длину массива, регистр 17 циклов, указывающий кЬлич ество необходимых циклов обмена и уменьшающийся на единицу после однократной передачи массива, узел 18 перезаписи, осуществляющий вычитание единицы из регистра 17 циклов и перезапись содержимого регистра 13 начального адреса в регистр 14 текущего адреса и содержимого регистра 15 начальнойдлины массива в регистр 16 текущей длины массива, мультиплексор 19 данных, осуществляющий передачу информяции из регистров устройства при выполнении ЭВМ операции чтения, узел 20 записи, вырабатывающий строб записи в регистры устройства при наличии на общей шине адресов этих устройств, узел 21 чтения, управляющий мультиплексором 19 данных, узел 22- элементов И записи, предназначенных для передачи данных, поступающих из первого интерфейса через блок 4 усиления, узел 23 элементов И чтения, обеспечивающих вьщачу в первый интерфейс данных из второго интерфейса для регистров устройства, мультиплексор 24 адреса, коммутирующий адрес на вход дешифратора 1, блок 25 выполнения прерываний дпя 13 ; внепроцессорного обмена, выполняющи процедуру захвата общей шины. Блок 2 вьшолнения программных прерываний (фиг.2) сострит из М однотипных узлов 26 захвата общей шин где М - количество запросов прерыва ний от внешних устройств,(ЗП2-ЗПМ) включая внутренний запрос от регист ра 17 циклов (ЗП1), элемента ИЛИ 2 элемента задержки 28 и шифратора 29 Выход запроса на прерывание ЗП ВЫХ каждого узла 26 подключен к соответствующему уровню приоритетных прерываний общей шины в зависимости от требуемой скорости обслуживания устройств, подключенных к второму интерфейсу. . Каждый узел захвата общей щины (фиг.3) может быть реализован на двух D-триггерах 30 и 31, элементах И 32, 33 и 34, элементе И-НЕ 35 и элементе ИЛИ-НЕ 36. Блок 3 обмена (фиг. 4 и 5) содер жит первый 37 и второй 38 триггеры первый 39, -второй 40 и третий 41 элементы И-Ш1И, третий 42 и первый 43 элементы задержки, третий триггер 44, третий 45, первый, 46 и второй 47 формирователи импульсов (одновибраторы), второй элемент 48 задержки, четвертый 49 и пятьп 50 элементы И-ИЛИ, элемент ИЛИ 51 и элемент И 52. Узел. 9 задания последовательности операций (фиг. 6) содержит дешифратор 53, элементы ИЛИ 54 и 55, элементы И 56 и 57 и элемент И-ШШ 58. Клок 25 вьшолнения прерываний для внепроцессорного обмена (фиг.7) может быть выполнен на D-триггерах 59,60 и 61, элементе ИЛИ-НЕ 62 и элементах И 63, 64 и 65. Узел 18 перезаписи (фиг.8) состоит из элемента НЕ 66, элементов И 67 и 68. Узел 20 записи (фиг.9) включает в себя дешифратор 69 и элементы И 70-76. Узел 21 чтения (фиг.10) состоит пз дешифратора 77, элемента ИЛИ 78 и элемента И 79. На чертежах обозначены также входы 80, 81 и 82 и выходы 83 и 84 блока 2 вьтолнения программн к прерываний, входы 85 и 86 и выходы 87 и 88 узла 26 захвата общей шины, первый 89, второй 90, четвертый 91 1514 и пятый 92 входы и первый - третий 93-95 и пятый 96 выходы блока 3 обмена (связанные между собой вход одного блока и выход другого обозначены одними и теми же позициями), входы 97-100 узла 9 задания последовательности операций, второй вход 101 и первый выход 102 блока 25 выполнения прерываний для внепроцессорного обмена, входы 103 и 104 и выход 105 узла 18 перезаписи, первые входы 106 и выход .107 узла 21 чтения. Устройство работает следующим образом. Режим программного обмена. Вначале ЭВМ устанавливает на общей шине адрес устройства, с которым необходимо выполнить обмен данными. Если установленный адрес принадлежит к адресам, присвоенным регистрам внешних устройств, подключенных к описываемому устройству, или к адресам собственных регистров этого устройства, то установленный адрес через мультиплексор 24, поступает на дешифратор 1, который вырабатывает сигнал выборки внешнего устройства. Этот же адрес поступает в уэлы 20 и 21. В случае выполнения операции записи ЭВМ устанавливает на шинах данные для записи, а на шинах управления - код операции записи. Если адрес,, установленный на обп(ей шине, принадлежит внешнему устройству, то данные через блок 4 и узел 22 стробом, выработанным блоком 3,записываются в выбранное внешнее устройство через блок 5. Если же адрес на общей шине принадлежит внутренним регистрам устройства, то по коду записи узел 20 записывает дан ные в один из регистров 13,15,17,6, 7 или 8. Некоторые из указанных регистров могут иметь одинаковые адреса на общей шине. Запись в такие регистры выполняется одновременно, В случае выполнения операции чтения ЭВМ устанавливает на шинах управления код операции чтения. Если адрес, установленный на общей шине, принадлежит внешнему устройству, то стробом, выработанным блоком 3 по коду операции чтения, данные с выбранного внешнего устройства через . блок 5 и узел 23 поступают в ЭВМ

1511006

ерез блок 4. Если же адрес на обей шине принадлежит внутренним | егистрам устройства, то по коду операции чтения и адреса на общей ине узел 21 выдает на мультиплек- j ор 19 код.номера регистра.. Данные с выхода мультиплексора. 19 передаются в ЭВМ через узел 23.

Обмен информацией между шиной и внешними устройствами осуществляет- ю ся по асинхронному принципу. После установки адреса данных и управляющих сигналов на общей шине выдается синхросигнал, который формирует в блоке 3 сигнал операции для внеш- fs него устройства. По окончании операции внешнее устройство вьщает ответный сигнал, который проходит через блок 3 на общую шину, и операция завершается.20

Режим прерываний на программном уровне.

Сигналы прерываний от всех внешних устройств поступают с третьего выхода блока 5 на входы коммутаторов 25 11 и 12. На выход коммутатора 11 проходят запросы на прерывание только от тех устройств, адреса которых указаны в регистрах 7 и 8.

Прошедший через коммутатор 12 запрос на прерывание от внешнего устройства запускает блок 2, который в соответствии с алгоритмом общей шины выполняет процедуру прерывания программы и захвата шины. После 35 этого управление передается блоку 3, которьй вьтолняет требуемый обмен с внешним устройством, выставившим запрос на прерывание и выдает в блок 2 Сигнал об окончании обмена, поко- 0 торому блок 2 переходит в исходное состояние и ожидает очередного запроса на прерывание от :нешнего устройства.

Режим прерываний на внепроцессор- 5 ном уровне.

Перед началом работы во внутренние регистры устройства загружается следующая информация: в регистр 13 начального адреса - адрес первой 50 ячейки массива памяти, с которым будет выполняться обмен информацией; в регистр 15 начальной длины массива - количество ячеек памяти, вьщеленных для массива-, в регистр 55 17 циклов - количество полных циклов обмена всей информацией, содержащейся в указанном массиве, в регистр 6

16

15

команды - команда, которую должно выполнять устройство; в регистр 7 адрес первого устройства, участвующего во внепроцессорном обменеJ в регистр 8 - адрес второго устройства участвующего в внепроцессорном обмене. Регистр 14 текущего адреса и регистр 16 текущей длины, массива исходно загружаются той же информацией что и регистр 13 начального адреса и регистр 15 начальной длины массива соответственно. Регистр 6 команды загружается последним. После его загруки устройство готово к работе на внепроцессорном уровне.

В исходном состоянии счетчик 10 фаз находится в О и коммутатор 11 подключает выход запроса прерывания внешнего устройства, адрес которого указан в регистре 7, к выходу блока 25 для внепроцессорного обмена. Узел 9 в зависимости от кода команды в регистре 6, адресов в регистрах 7 и 8 при нулевом состоянии счетчика 10 выдает на блок 3 признак ;первой операции (Чтение или Запись), которая должна выполняться в первом цикле обмена.

.Первый сигнал запроса прерывания, пришедший после загрузки регистра 6 от внешнего устройства, адрес которого указан в регистре 7, поступает на вход блока 25, который осуществляет захват общей шины для внепроцессорного обмена, передает управление йиной блоку 3 и разрешает выдачу через мультиплексор 24 адреса содержимого регистров 7 или 8 на вход дешифратора 1. При нулевом состоянии счетчика 10 на дешифратор 1 подается адрес первого устройства, участвующего во внепроцессорном обмене, и выбирается это устройство. I

Блок 3 в соответствии с признаком операции, поступившим от узла 9, устанавливает на общей шине код требуемой операции. При выполнении операции записи осуществляется чтение данных с выбранного устройства и запись, их через узел 23 в память ЭВМ по адресу, поступающему на общую шину с регистра 14 текущего адреса. При выполнении операции чтения данные в ячейки памяти ЭВМ, адрес которой подается на общую шину с регистра 14, записьюаются в выбранное внешнее устройство чере блоки 4 и 5 и узел 22.

t7

По окончании внепроцессорного обмена блок 25 получает признак окончания цикла обмена от блока 3 и формирует сигнал, по которому мультиплексор 24 переключается на коммутацию адреса с общей шины, а блок 3 выдает сигнал конца цикла увеличивающий на единицу содержимое счетчика 10 и регистра 14, и уменьшает на единицу содержимое регистра 16.

В результате выполнения цикла межпроцессорного обмена счетчик 10 переключает коммутатор 11 на вьщачу из. блока 25 запросов на прерывание от внешнего устройства, адрес которого указан в регистре 8, а также устанавливает с учетом кода команды на выходе узла 9 признак операции, которая будет выполняться при следующем цикле внепроцессорного обмена, и подготавливает разрешение на коммутацию через мультиплексор 24 содержимого регистра 8. Возникновение запроса на прерывание от этого устройства вызывает выполнение цикла внепроцессорного обмена,которьш происходит аналогично.

Операции, выполняемые за один цикл работы счетчика 10, т.е. за время прохождения счетчика через вйе состояния от нулевого дез нулевого, составляют цикл команды. В цикле команды могут выполняться в различной последовательности операции чтения или записи с двумя различными внешними устройствами или с одним и тем же устройством. В последнем случае в регистры 7 или 8 должны быть записаны адреса одного и того же устройства.

Циклы команды будут выполняться до/тех nopj пока не станет равным нулю регистр 16. Сигнал равенства нулю регистра 16, соответствующий окончанию передачи заданного массива данных, через узел 18 уменьшает на единицу содержимое регистра 1 и перезаписьшает в регистр.14 и в регистр 16 содержимое регистра 13 и регистра 15.

Циклы команд, выполняемые за время от загрузки внутренних регистров устройства до переполнения регистра текущей длины массива,составляет цикл обмена массивом. Количество циклов обмена массивом исходно записывается в регистр 17 циклов Сигнап переполнения регистра 17,

100615

18

т.е. сигнал равенства регистра нулю, поступает на блок 2 и вызывает прерывание программы ЭВМ, После этого либо происходит снова загрузка внутренних регистров устройства, либо работа с устройством прекращается.

Внешние устройства, не участвующие во внепроцёссорном обмене, в промежутках времени между обслуживаниями внепроцессорного обмена могут обслуживаться в режиме программного обмена или в режиме прерываний на программном уровне. При этом внешние устройства, подключаемые к второму интерфейсу, воспринимаются ЭВМ как подключенные непосредственно к общей цмне, что позволяет в полной мере использовать все архитектурные возможности ЭВМ с интерфейсом Общая

шина.

При внепроцёссорном обмене устройство позволяет с помощью одной команды выполнять обмен информацией между памятью ЭВМ и двумя внешними

устройствами, причем цикл команды может содержать различные последовательности операций чтения и записи.

Например, при необходимости получения информации с объекта о

быстропротекающих процессах с помощью многоканального аналого-цифрового преобразователя (АЦП) во внутренние регистры устройства исходно записывают следующую информацию: в регистр 13 - адрес начала массива, предназначенного для хранения адресов каналов АЦП и данных с АЦП, в регистр 15- размер используемого

массива, в регистр 17 - количество циклов обмена массивом, в регистр 7 - адрес регистра номера канала АЦП на общей шине, в регистр 8 - адрес регистра данных АЦП на общей

шине и в регистр 6 - код команды Чтение-запись.

В процессе внепроцессорного обмена при. каждом запросе на прерывание от АЦП адрес канала передается на

АЦП из подготовленного массива адресов каналов, а данные из АЦП записываются в этот массив. В результате выполнения одного цикла обмена массивом выделенный массив содержит

пары ячеек памяти, в одной из которых будет записан номер канала АЦП, а в соседней - результат измерения по этому канайу. Количество циклов 19 обмена массивом определяет содержимое регистра циклов. С помощью команды Чтение - две записи можно сформировать массив, в котором одна ячейка содержит адре канала АЦП, а две следующие за ней результаты измерений в двух разных каналах, подключенных к АЦП. Для графических дисплеев полезной является команда Две записи, по которой смежные ячейки подготовленного массива вьодаются поочередно в регистры отклонения луча по координатам X и Y . Устройство может содержать различные наборы команд, которые наибо лее эффективны для конкретных применений. Максимальное количество команд, выполняемых устройством, определяется разрядностью регистра команд, а максимальное количество операций в цикле команды - разрядностью счетчика фаз. Блок 2 программных прерываний (фиг. 2 и 3) работает следующим (Убразом. Исходно триггеры 30 и 31 сброшены, узел 26 находится в состоянии ожидания по входу 85 запроса ЗП на прерывание от внешнего устройства. Поступивший запрос транслируется на общую шину сигналом через элемент И 32. Получение разре шения прерывания РПШ от центрального процессора переводит узел 26 в следующее состояние: триггер 30 установлен 31 сброшен. При этом запрещается трансляция запроса и вырабатывается сигнал подтверждения выборки ПВВ на элементе И 33. При сбросе РПШ блок, 2 становится задатчиком на первом интерфейсе пу вьщачи сигнала ЗАНШ через элемент ИЛИ-НЕ 36, триггер 31, элемент И 3 (фиг.З), элемент ИЖ 27 (фиг.2) и элемент ИЛИ 51 (фиг.5). В это врем шифратор 29 формирует вектор преры вания (шин Д), соответствующий уст ройству второго интерфейса, занявш му шину, а элемент задержки 28 выдает сигнал сопровождения ПРЕР. После получения от процессора сигн подтверждения приема вектора преры вания (СХИШ) сбрасывается триггер через элемент И-НЕ 35, узел 26 освобождает шину и ждет снятия ЗП вн него устройства, после чего приходи в исходное состояние. 5 Блок 3 обмена предназначен для реализации алгоритмов передачи информации первого и второго интерфейса. Задание направления .передачи информации на втором интерфейсе осуществляется с помощью триггеров 37 и 38. Выходы этих триггеров подключены к управляю1дим линиям ЧТК и ЗПК, задающим одному из внешних устройств выполнение операции чтения или записи. Устройство, выполнившее операцию, вырабатьшает один- из ответных сигналов ЧТИ или ЗПИ (в зависимости от типа операции). Так как блок 3 обеспечивает работу в двух режимах: программный обмен и внепроцессорный доступ к памяти, то установка и сброс этих триггеров выполняется по двум каналам (в зависимости от режима работы устройства). При программном обмене информацией установка триггера 37 происходит через элемент И-ИЖ 39 при дешифрации адреса регистра одного из внешних устройств (сигнал АДР, элемент И 52), при получении кода операции чтения на первом интерфейсе (сигнал С1Ш) и получении строба разрешения выполнения этой операции (строб синхронизации задатчика СХЗШ). Сброс триггера 37 в этом случае происходит через элемент И-ИЛИ 40 после снятия строба СХЗШ и получения от внешнего устройства ответного сигнала выполнения операции ЧТИ. Элемент задержки 42 предназначен для компенсации перекоса данных на линиях второго интерфейса после установки на них информации внешним устройством. Установка триггера 38 при программном обмене выполняется через элемент И-ИЛИ 41 аналогично триггеру 37, но, под управлением кода операции Запись (сигнал С1Ш). Элемент задержки 43 предназначен дпя компенсации перекоса данных на втором интерфейсе после установки информации внешним устройством. Сброс триггера 38 осуществляется при получении от внешнего устройства сигнала выполнения операции Запись ЗПИ. При работе на уровне внепроцессорного доступа к памяти задатчиком на первом интерфейсе является

устройство для сопряжения, Установка триггера 37 в этом случае происходит при выполнении устройством операции записи данных в память ЭВМ из внешнего устройства через элемент И-ИЛИ 39 (сигнал от ЧТУС вырабатываемым узлом 9 и сигнал ЗАН2 из блока 25).

Сброс триггера 37 происходит через элемент И-ИЛИ 40 после получения сигнала ЧТИ, когда внешнее устройство передало информацию по второ му интерфейсу, получения строба синхронизации исполнителя СХИШ от первого интерфейса, означающего, что информация записана в память, и сброса-триггера 44 (фиг.5) после окончания операции. I

Установка триггера 38 при внепроцессорном обмене происходит через элемент 41 при выполнении устройством опе эации чтения данных.из памяти ЭВМ и записи в регистр внешнего устройства. Поэтому триггер устанавливается при наличии сигналов ЗАН2 (т.е. устройство выполняет операцию внепроцессорного обмена) , ЗПУС (операция чтения данных из памяти ЭВМ) и СХИШ (когда данные из памяти ЭВМ получены и выданы на линии данных второго интерфейса) .

Сброс триггера выполняется так же, как при программном обмене.

При работе на уровне внепроцессорного обмена передача информации по первому интерфейсу синхронизируется триггером 44 синхронизации задатчика устройства. Установка .триггера происходит через элемент 49 после снятия устройством первого интерфейса. Элемент задержки 48 осуществляет задержку времени на компенсацию перекоса адреса на первом интерфейсе и на дешифрацию этого адреса исполнителем. В случае выполнения устройством операции записи в память ЭВМ установка триггера 44 происходит через элемент И-ИЛИ 49 после получения ответного сигнала ЧТИ от внешнего устройства, т.е. после получения информации с второго интерфейса .

Сброс триггера 44 происходит через элемент И-ИЛИ 50 после получения ответного сигнала с первого (СХИШ) или второго (ЗПИ) интерфейса, (в зависимости от выполняемой операции) ..

0061522

При каждом сбросе триггера 44 последовательно запускаются одновибратор 46 (прямой выход которого АУВ формирует прибавление 1 к со5 держимому регистров 16 и 14 и счетчика 10 фаз) и одновибратор 47, выход которого СТСХЗА сбрасывает триггеры 60 и 61 (фиг.7).

Узел 9 задания последователь0 ности операций может быть реализован так, как показано на фиг.6. Код команды, записанный в регистре 6, дешифрируется дешифратором 53 под управлением кодов в регистрах 5 7 и В первого и второго внешнего устройства. Последовательность появления сигналов ЗПУС, ЧТУС также определяется фазой выполнения инструкции прямого доступа (сигна0 лы 02-ON из счетчика фаз 10).

Пример технического решейия блока 25 выполнения прерываний для внепроцессорного обмена показан на фиг.7. Схема представляет собой ав5 томат, имеющий три устойчивых состояния . Основой автомата являются триггеры 60 и 61.

Триггер 59 позволяет устройству выполнять VI -мерные операции после Q получения одного запроса на прерывание от внешнего устройства. Сброс триггера осуществляется сигналом СТЗПР после выполнения количества циклов передачи информации по первому интерфейсу, указанному в коде операции вьтолняемой команды.

Исходно .триггеры 60 и 61 сброшены в О. После установки триггера 59 в 1 через элемент И 63 на перQ вый интерфейс поступает запрос на

внепроцессорный обмен ЗПД. При воз, можнрсти такого обмена процессор отвечает разрешающим сигналом РПДШ. I , Передним фронтом данного сигнала

5 устанавливается в 1 триггер 60. При этом снимается сигнал ЗПД и вьрабатывается сигнал подтверждения выборки ПВБ (элемент И 65). По получении данного сигнала процессор

0 сбрасывает РПДШ,. При совпадении условий незанятости первого и второго интерфейсов (собраны на элементе ИЛИ-НЕ 62). происходит установка в 1 триггера 61. При этом устрой5 ство становится задатчиком (т.е. управляющим), на первом интерфейсе.

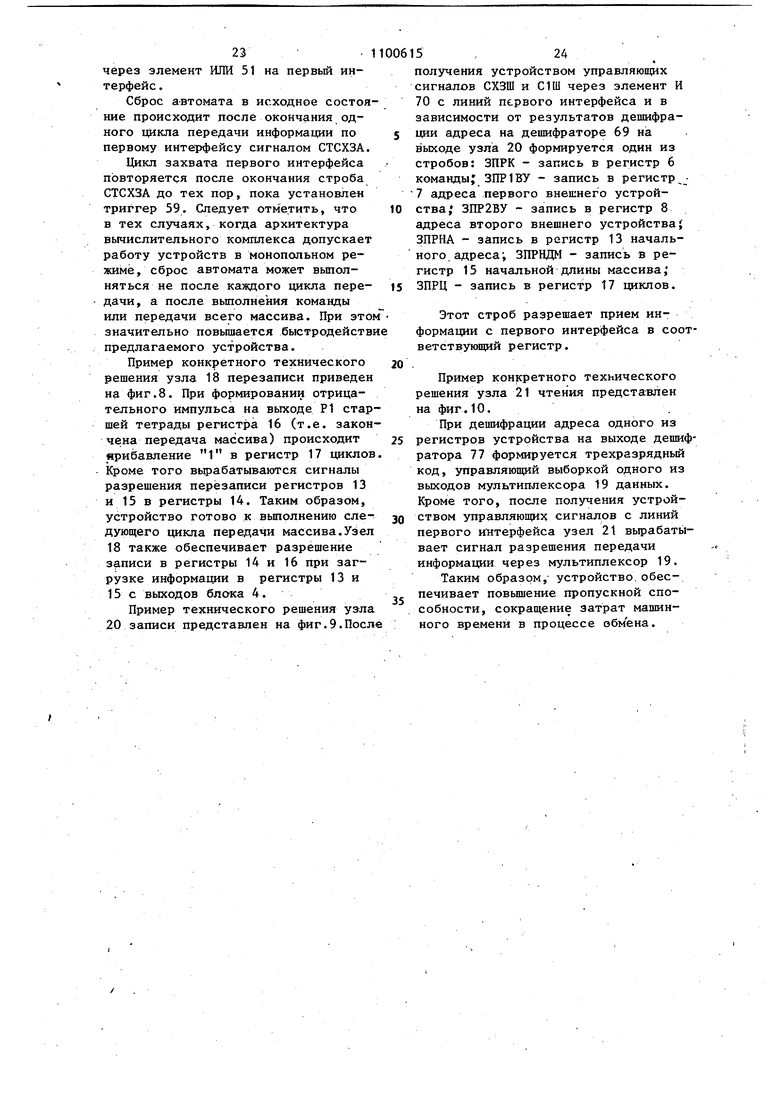

Сигналзанятости ЗАН2 поступает через элемент И 64 в блок 3, а затем 23 через элемент ИЛИ 51 на первый интерфейс . Сброс автомата в исходное состоя ние происходит после окончания одного Щ1кла передачи информации по первому интерфейсу сигналом СТСХЗА. Цикл захвата первого интерфейса повторяется после окончания строба СТСХЗА до тех пор, пока установлен триггер 59. Следует отметить, что в тех случаях, когда архитектура вычислительного комплекса допускает работу устройств в монопольном режиме, сброс автомата может выполняться не после каждого цикла передачи, а после выполнения команды или передачи всего массива. При это значительно повьпиается быстродейств предлагаемого устройства. Пример конкретного технического решения узла 18 перезаписи приведен на фиг.8. При формировании отрицательного импульса на выходе Р1 стар шей тетрады регистра 16 (т.е. закон чена передача массива) происходит ярибавление 1 в регистр 17 циклов Кроме того вырабатываются сигналы разрешения перезаписи регистров 13 и 15 в регистры 14. Таким образом, устройство готово к выполнению следующего цикла передачи массива.Узел 18 также обеспечивает разрешение записи в регистры 14 и 16 при загрузке информации в регистры 13 и 15 с выходов блока 4. Пример технического решения уэла 20 записи представлен на фиг.9.Посл 524 получения устройством управляющих сигналов СХЗШ и С1Ш через элемент И 70 с линий первого интерфейса и в зависимости от результатов дешифрации адреса на дешифраторе 69 на выходе узла 20 формируется один из стробов: ЗПРК - запись в регистр 6 команды; ЗПР1ВУ - запись в регистр 7 адреса первого внешнего устройства/ ЗПР2ВУ - запись в регистр 8 адреса второго внешнего устройства} ЗПРНА - запись в регистр 13 начального адреса; ЗПРНДМ - запись в регистр 15 начальной длины массива, ЗПРЦ - запись в регистр 17 циклов. Этот строб разрешает прием информации с первого интерфейса в соответствующий регистр. Пример конкретного технического решения узла 21 чтения представлен на Фиг.10.. При дешифрации адреса одного из регистров устройства на выходе дешифратора 77 формируется трехразрядный код, управляющий выборкой одного из выходов мультиплексора 19 данных. Кроме того, после получения устройством управляющих сигналов с линий первого интерфейса узел 21 вьфабатывает сигнал разрешения передачи информации через мультиплексор 19. Таким образом, устройство, обеспечивает повьш1ение пропускной способности, сокращение затрат машинного времени в процессе обмена.

фиг.1

(риг.З

РЛй/

3AHt

I

зАнг

51

рпдш

ЗАНШ

зтс

т

ЧТУС

УГН

9

С)(НШ

зпн

50

90

АОО

1Г

ML

АИ

89

9г

pfftit I схнш

ЗАНШ

-4

рлдш I j; ЗАНШ r-JaСТЗ/ТР

схза/

-СХЗ /С/маа.4-)

««

АУВ

№

«X

mJ

и

47

AЛPfffaФ f.)

л г

ТРбЛО

СГ5Л0

77

РЛЛШ СГОСЗА

ВО

D

61

ЗАНШ

3ftH

SZ

т

3fJA

S5

пев

91

ЗАИ2

срие.7

fff

3/7P//A

ah. pPS.t7

.2рег./4

./joff- fff

срие.8

fOB I

cpue.3

10В

99

ери. W

Bbfx,1(f9)

Номер Входа

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3286965/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1983-02-04—Подача