Изобретение относится к вычислительной технике и может использоваться для контроля микропроцессорных устройств.

Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля систем с мультиплексированной шиной, использущих для обмена информацией между модулями циклы различной неупорядоченной структуры.

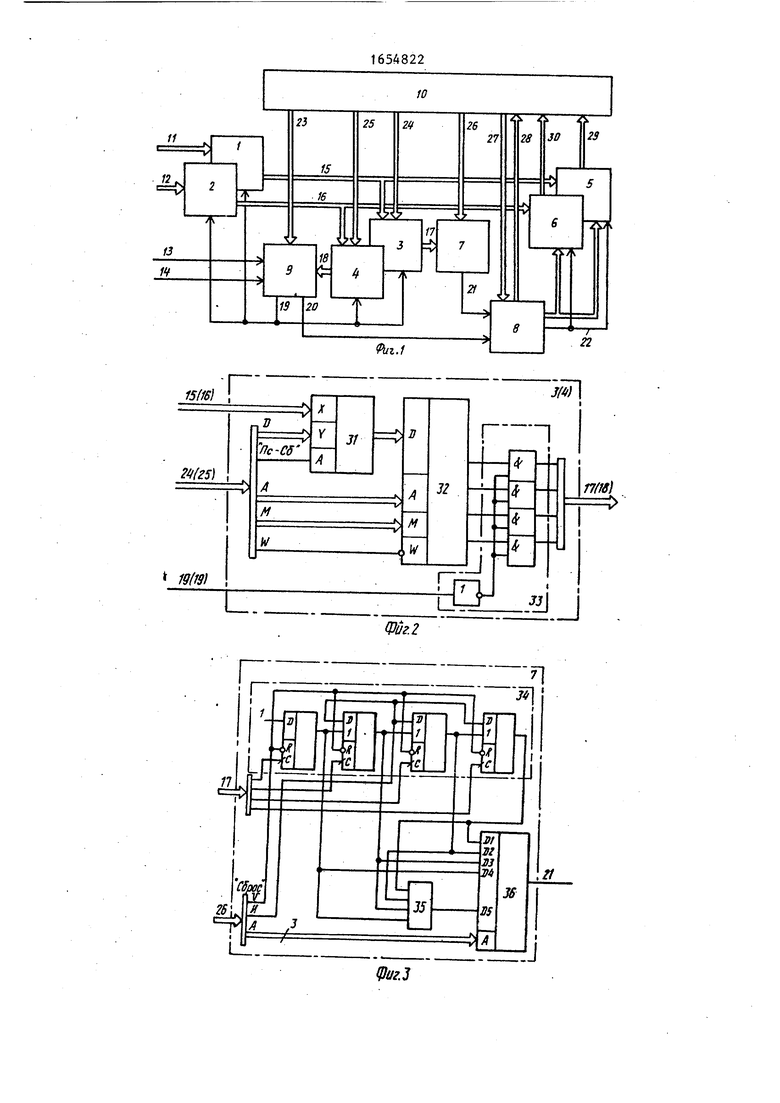

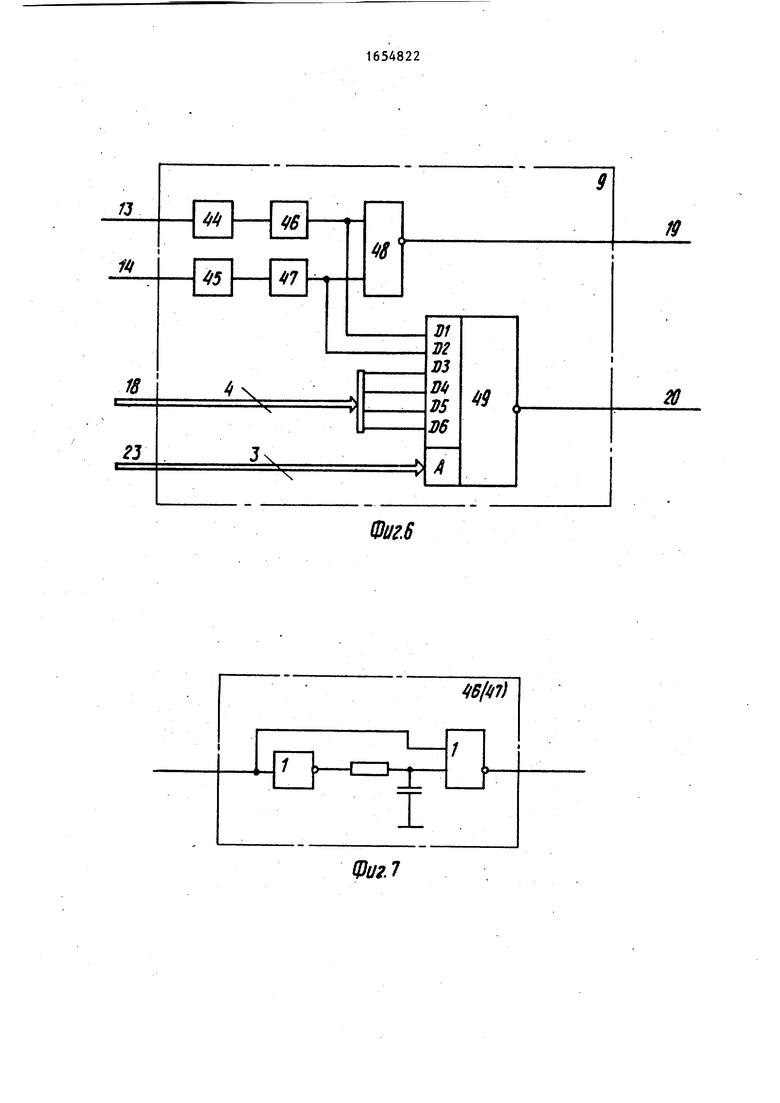

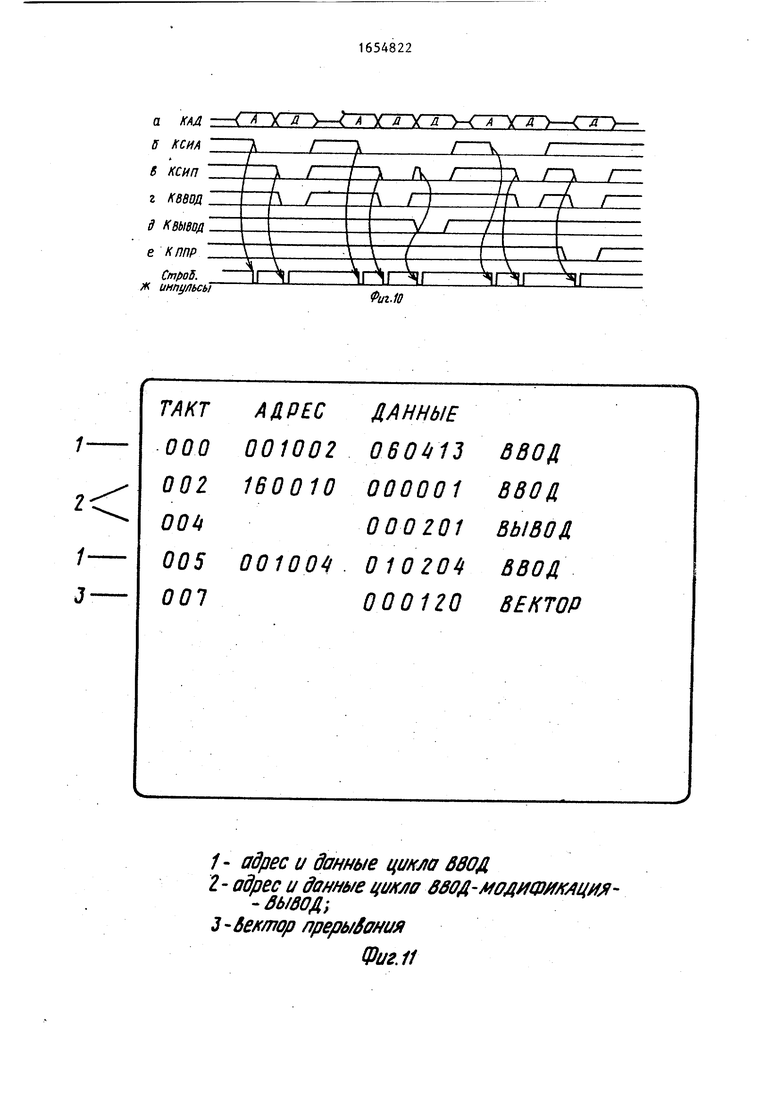

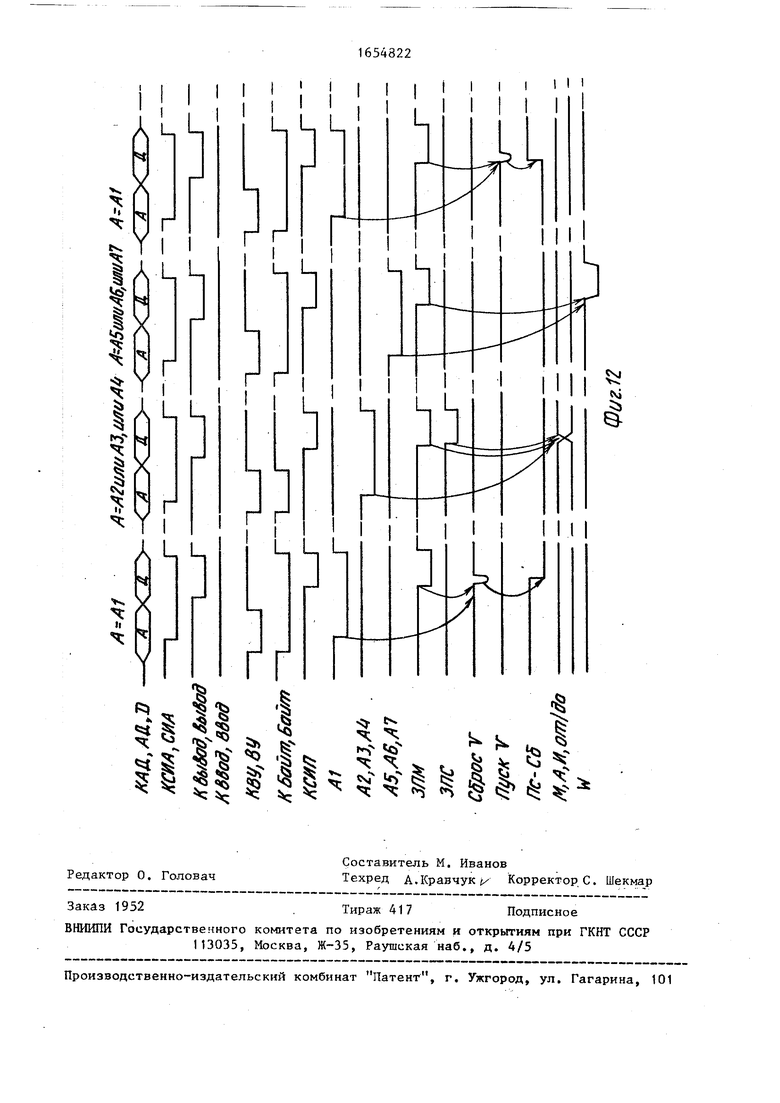

На фиг. 1 приведена структурная схема логического анализатора; на фиг. 2 - 7 - примеры реализации селектора, блока запуска, блока управления памятью, формирователя импульсов синхронизации, формирователя коротких импульсов и контроллера соответственно; на фиг. 8 и 9 - пример реализации интерфейсного блока контроллера; на фиг. 10 - диаграммы, иллюстрирующие обмен по мультиплексированной шине

циклами нерегулярной структуры; на Фиг.11- вариант отображения информа- ции на экране дисплея; на фиг. 12 - временные диаграммы сигналов на выходе контроллера.

Логический анализатор (фиг. 1) содержит первый 1 и второй 2 буферные регистры, селекторы признаков запуска 3 и записи ч, первый 5 и второй 6 блоки памяти, блок 7 запуска, блок 8 уп- .равления и формирователь 9 импульсов синхронизации, контроллер 1U, группу 11 и 12 информационных входов, тактовые входы 13 и 14, выходы 15-22 блоков анализатора, группы 23-27 входов задания режима, группу 28 информационных выходов для считывания слова состояния анализатора и группы 29 и 30 информационных выходов для считывания зарегистрированной информации.

Буферные регистры 1 и 2 предназначены для записи информации и признаков соответственно с входов 11 и 12 И хранения их в течение времени срабатывания селекторов 3 и 4, блока 7 запуска, блока 8 управления, блоков 5 и 6 памяти.

Селектор 3 признаков запуска предназначен для хранения наборов кодов (признаков) запуска, поступающих на входы селектора с входов 24. При совпадении кодов на выходах селектора 3 появляются сигналы совпадения с признаками, стробированные сигналом с тового входа селектора.

Селектор 3 (4) может быть выполнен на основе микросхем ассоциативной памяти К589РА04 (фиг. 2).

Селектор 3 содержит мультиплексор 2 31, ассоциативную память 32 и элемент 33 стробирования признаков. Мультиплексор 31 служит для переключения Сигналов, поступающих на входы данных ассоциативной памяти 32 в режиме 2 поиска или программирования признаков. и режиме поиска открываются каналы X мультиплексора 31, в режиме программирования - каналы Y.

Ассоциативная память 32 служит для 3 хранения признаков, записываемых в нее на этапе программирования, и поиска признаков во входной последовательности состояний. При совпадении кода на входах D с одним из признаков на Соответствующем выходе появляется сигнал совпадения. Элемент 33 служит для Стробирования сигналов совпадения сигналом, поступающим со стробирующего

Входа селектора 3. Входы ассоциатив

ной памяти 32: входы выбора признаков А, входы маскирования М и вход записи W. Мультиплексор 31 может быть Выполнен на основе микросхем К531КП11 ассоциативная, память 32 - на микросхе мах К589РА04.

Селектор 4 признаков записи предназначен для хранения значений признаков записи и сравнения их с кодами, поступающими на входы селектора 4 с входов 25 анализатора, и выработки сигналов совпадения. Блок 5 памяти Предназначен для записи информации, поступающей с входов 11 анализатора, ранения записанной информации и выдачи ее в контроллер 10 для последующего отображения. Блок 6 памяти предназначен для записи информации, поступающей с входов 12 анализатора,

0

5

0

5

„

5

хранения записанной информации и выдачи ее в контроллер для дальнейшего использования.

Блок 7 запуска предназначен для выработки сигнала начала/окончания записи в анализатор, в дальнейшем называемого сигналом запуска. Сигнал запуска вырабатывается из сигналов признаков запуска с выходов 17 селектора 3 по алгоритму, определяемому схемным решением блока 7 и кодом режима, поступающим на блок 7 с входов 26 анализатора.

Рассмотрим пример реализации блока

7запуска, осуществляющего выработку сигнала запуска по любому из признаков запуска, по совокупности всех признаков, появляющихся в определенной или произвольной последовательности (фиг. 3). Блок 7 содержит регистр 34, элемент И 35 и мультиплексор 36. Регистр 34 предназначен для фиксации факта появления признаков, причем триггеры регистра могут фиксировать признаки независимо один от другого или последовательно: каждый последующий триггер срабатывает от соответствующего признака после установки в 1 предыдущего триггера. Элемент

И 35 предназначен для выработки сигнала по совокупности всех признаков. Мультиплексор 36 позволяет выбрать в качестве сигнала запуска любой из сигналов, вырабатываемых триггерами регистра 34 или элементом 35. Регистр 34 может быть выполнен на основе микросхем К531ТМ2 и микросхем К531ЛЛ1 для организации по входам D триггеров функции ИЛИ, а мультиплексор 36 на микросхеме К531КП7.

Блок 8 управления памятью предназначен для формирования в течение окна контроля адресов для выбора ячеек памяти блоков 5 и 6 и сигнала записи. Формирование окна контроля производится по алгоритму, определенному схемным решением блока 8 и кодом режима, поступающим на блок с входов 27.

Рассмотрим пример реализации блока

8управления памятью, формирующего окно контроля от сигнала запуска до переполнения памяти блоков 5 и 6 (далее такой режим формирования окна контроля называют положительным запуском) и от сигнала Пуск до сигнала запуска (отрицательный запуск, фиг.5) Блок 8 содержит триггер 37 положительного запуска, триггер 38 отрицательного запуска лементы И-ИЛИ 39 и 40, триггер 41 останова, триггер 42 индикации заполнения памяти и счетчик 43 адреса. Триггер 37 положительного за- ауска предназначен для выработки сиг- дала от момента появления сигнала запуска до переполнения счетчика 43 адреса. Триггер 38 отрицательного запуска предназначен для выработки сиг- нала от прихода сигнала Пуск до появления сигнала запуска. Элемент И-ИЛИ 39 предназначен для ограничения строба записи окном контроля. Элемент И-ИЛК 40 предназначен для вьщеления сигнала, указывающего об окончании записи в анализатор.Данный сигнал устанавливает в О триггер останова 41 Триггер 41 является 0-м разрядом регистра состояния анализатора. Триггер 42 индикации заполнения памяти предназначен для фиксации факта однократного заполнения памяти, состояние триггера 42 учитывается при считывании содержимого блоков 5 и 6 памяти, заполненных в режиме отрицательного запуска. Состояние триггера 42 является 1-м разрядом слова состояния анализатора. Счетчик 43 адреса предназначен для формирования адресов ячеек памяти блоков 5 и 6.

Триггеры 37, 38, 41 и 42 могут быть выполнены на микросхемах К531ТМ2 Функция ИЛИ для входа триггера 37 может быть реализована на элементе И микросхемы К531ЛИ1, счетчик адреса 43- на микросхемах К155ИЕ7. .

Формирователь 9 импульсов синхронизации предназначен для выработки стробов запуска и записи в моменты истинности определенных групп состояний на информационных входах анализатора. Критерием истинности той или иной группы состояний является при

Q 0 5 0

д

5

стробов - коротких импульсов по отрицательному фронту тактового сигнала. Элемент ИЛИ-НЕ 48 формирует строб запуска анализатора, осуществляя сборку стробов формирователей 46 и 47. Мультиплексор 49, управляемый кодом режима с линией задания режима 23, осуществляет выбор сигнала, используемого в качестве строба записи: один из выходных сигналов формирователей 46 и 47 или один из сигналов признаков записи, поступающих с выходов 18 селектора 4.

Выполнение элементов формирователя 9 может быть следующим: шинные формирователи 44 и 45 - на основе микросхем К559ИП2, формирователи 46 и 47 короткого импульса - на основе микросхем К531ЛН1, К531ЛЕ1 и интегрирующей RC-цепочки (фиг. 3), элемент ИЛИ-НЕ 48 на основе микросхемы К531ЛЕ1 и мультиплексор 49 - на основе микросхемы К531КП7.

Контроллер 10 является примером средств для задания режима работы анализатора, считывания записанной в анализатор информации для представления ее на экране дисплея.

Контроллер 10 (фиг. 4) содержит управляющую ЭВМ 50 и блок 51 интерфейса. Входы/выходы ЭВМ 50 через магистраль 52 связаны с группой входов/ /выходов блока интерфейса 51. Группы выходов блока 51 интерфейса являются группами выходов контроллера 10, а группы входов блока 51 интерфейса - группами входов контроллера. Блок 51 содержит адресуемые из ЭВМ 50 регистры. ЭВМ 50 записывает в регистры блока 51 интерфейса коды, определяющие режимы работы блока 9, селекторов 3 и ч, блоков 7 и 8. Кроме того, блок 51 лроизводит передачу содержимого

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1989 |

|

SU1730627A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Логический анализатор | 1989 |

|

SU1734093A1 |

ИзоЬретение относится к вычислительной технике и может использоваться в контрольно-испытательной аппаратуре. Цель изобретения - расширение функциональных возможностей. Логический анализатор содержит два буферных регистра, два селектора, два блока памяти, блок запуска, блок управления и формирователь импульсов синхронизации. Логический анализатор обеспечивает контроль микропроцессорных систем с мультиплексированной шиной,использующих для обмена информацией между модулями циклы различной неупорядоченной структуры. 3 з.п. ф-лы, 12 ил.

сутствие на входах квалификаторов ана- 45 блоков 5 и 6 памяти и слова состояния анализатора в ЭВМ 50.

лизатора соответствующего сигнала или сочетания сигналов при одлновре- менном поступлении сигнала на тактовый вход.

В состав формирователя 9 (фиг. 6) входят два шинных формирователя 44 и 55, два формирователя 46 и 47 короткого импульса, элемент ИЛИ-НЕ 48 и мультиплексор 49.

Шинные формирователи 44 и 45 предназначены для повышения помехозащищенности анализатора по так,товым входам. Формирователи 46 и 47 короткого импульса предназначены для формирования

блоков 5 и 6 памяти и слова состоя

ния анализатора в ЭВМ 50.

Реализация блока 51 интерфейса зависит от типа используемой ЭВМ 50, ее интерфейса. Рассмотрим вариант блока интерфейса 51, (фиг. 8, 9), если в качестве ЭВМ 50 используется персональная ЭВМ типа ДВК-1, ДВК-2, ДВК-3, а блок 51 интерфейса подключается к ДВК через магистраль МПИ. Выполнен блок 51 на основе микропроцессорного комплекта серии К588. Блок 51 включает в себя селектор адреса с блоком 53 переключателей, шинные Формирователи 54, формирователи сигналов Пуск 55, Сброс 56 и Пс-Сб 57, мультиплексор 58, регистры 59 и 60 маскирования признаков записи, формирователь 61 сигнала W линий 25 задания режима работы селектора 4, регистры 62 и 63 маскирования признаков запуска, формирователь 64 сигнала W линии 24 задания режима работы (селектора 3, регистр 65 адресации признаков, регистр 66 режима и формирователь 67 сигнала W линий 27.

Селектор 53 адреса вырабатывает сигналы адресации внутренних узлов блока 51 и сигналы управления записью младшего ЗПМ, старшего ЗПС байтов или чтения ЧТ информации в (из) регистров . Шинные формирователи 54 служат для развязки и снижения общей нагрузки от блока 51 на магистраль 52. Формирователь 55 при передаче 1 (низкого уровня сигнала в отрицательный логике) по младшему разряду ма- гистрали 52 - разряду АД ф в цикле вывода формирует короткий отрицатель- ный импульс - сигнал Пуск. Аналогично от 1 по разряду АД1 вырабатывается сигнал Сброс. Сигнал Сброс Переводит анализатор в режим программирования, сигнал Пуск - в режим анализа и записи контролируемых состояний. Формирователь 57 выдает сигнал Пс-Сб - положительный импульс, начало импульса определяется сигналом

Рассмотрим работу анализатора на примере контроля мультиплексированно шины типа МПИ (фиг. 12). Подключение данной шины к входам анализатора дол но быть: мультиплексированные линии адрес-данные КАД - к информационным входам 11, линии управления КВВОД, КСИИ, КИПР и подобные им - к входам 12, а линии синхронизации данной шины КСИА и КСИИ - к входам 13 и 14 ана лизатора. Оставшиеся неиспользованны ми входы анализатора следует подключить к шине лог. 1. Данные состояния контролируемой шины Адрес запи сываются в первый блок 5 памяти в той последовательности, как они чередуют

Пуск, конец - сигналом Сброс. Мульде ся на линиях КАД. Одновременно запитиплексор 58 предназначен для организации считывания информации из блоков анализатора. По каналам К считывается Содержимое блока 5 памяти, по каналам L - блока 6 памяти, по каналам М - содержимое счетчика адреса и регистра состояния из блока 8. Регистры 59 и 60 предназначены для записи и хранения кода маски для второго селектора 4, формирователь 61 служит для выработки сигнала записи W на эта пе программирования второго селектора 4. Аналогично назначение регистров 63 и 62 и формирователя 64 для первого селектора 3, Регистр 65 предназначен для записи и хранения кода адреса признака (унитарного кода) на этапе программирования селекторов 3 и 4, Регистр 66 режима предназначен для записи и хранения кода режима формирователя 9(0,1 и 2-й разряды), кода режима блока управления 8 (7-й разряд), кода режима блока запуска 7 (3,4)5 и 6-й разряды). Формирователь

40

45

50

55

санные в блок 6 памяти сигналы управ ления КВВОД, КСИП и другие позволяют при считывании содержимого блока 5 памяти идентифицировать считываемые состояния, сигнал КСИП позволяет выд лить из всей записанной информации группу данных. КВВОД позволяет отличить группу данных циклов чтения от группы данных циклов записи и КШ1Р - определить данные, являющиеся векторами прерывания. Перечислим некоторые положения, касающиеся шины типа МПИ, которые помогут пониманию дальнейшего описания работы анализатора. Выражение лог. О соответствует высокому уровню сигнала, лог. 1 - низкому. Младший или нулевой разряд слов соответствует линии КАДО, первый разряд - линии КАД1 и т.д. Шина типа МПИ выступает в данном случае и как магистраль (52 управляющей ЭВМ 50 в контроллере 10, и как контролируемая шина Рассмотрим работу анализатора в ре жиме положительного запуска, з аписи

67 служит для выработки сигнала запис W адреса в счетчик адреса 43 блока 8 управления.

Реализованные узлы блока 51 интерфейса могут быть на следующих элементах: шинные формирователи 54 - на основе микросхем К531АП2, селектор 53 адреса - на основе микросхем К588ВТ1, К53ишЗ и переключателей типа ВДМ1 . Формирователи 55-57 могут быть выполнены на основе микросхем К531ТМ2, резисторов и конденсаторов, мультиплексор 58 - на основе микросхем , K155KII2, регистры 59 - 66 на основе микросхем К588ИР1 и К531ЛЛ1, формиро- ватели 61,64 и .67 - на основе микросхем К531ЛЛ1.

Рассмотрим работу анализатора на примере контроля мультиплексированной шины типа МПИ (фиг. 12). Подключение данной шины к входам анализатора должно быть: мультиплексированные линии адрес-данные КАД - к информационным входам 11, линии управления КВВОД, КСИИ, КИПР и подобные им - к входам 12, а линии синхронизации данной шины КСИА и КСИИ - к входам 13 и 14 анализатора. Оставшиеся неиспользованными входы анализатора следует подключить к шине лог. 1. Данные состояния контролируемой шины Адрес записываются в первый блок 5 памяти в той последовательности, как они чередуются на линиях КАД. Одновременно запи

санные в блок 6 памяти сигналы управления КВВОД, КСИП и другие позволяют при считывании содержимого блока 5 памяти идентифицировать считываемые состояния, сигнал КСИП позволяет выделить из всей записанной информации группу данных. КВВОД позволяет отличить группу данных циклов чтения от группы данных циклов записи и КШ1Р - определить данные, являющиеся векторами прерывания. Перечислим некоторые положения, касающиеся шины типа МПИ, которые помогут пониманию дальнейшего описания работы анализатора. Выражение лог. О соответствует высокому уровню сигнала, лог. 1 - низкому. Младший или нулевой разряд слов соответствует линии КАДО, первый разряд - линии КАД1 и т.д. Шина типа МПИ выступает в данном случае и как магистраль (52 управляющей ЭВМ 50 в контроллере 10, и как контролируемая шина. Рассмотрим работу анализатора в режиме положительного запуска, з аписи

всех подряд состояний, начиная с последовательности состояний линий КАД: 001ОООд-000123g. Весь цикл работы анализатора можно разбить на три этапа: программирования на требуемый режим работы, контроля и считывания записанной информации в контроллер анализатора.

Этап программирования начинается с выработки сигнала Сброс записью в формирователь 56 лог. 1.

At j разряд : 1 2.

Сигнал Сброс устанавливает в исходное состояние формирователь Пс-СБ 57, регистр 34 в блоке 7 запуска, триггеры запуска 37 и 38, триггер 41 останова и триггер 42 в блоке 8 управления.

Низкий уровень сигнала Пс-Сб переводит мультиплексор 31 в селекторах 3 и 4 в режим программирования, т.е. подключения к входам D ассоциативной памяти 32 линий D группы линий 24 (25). Затем обращением по со- ответствующим адресам из ЭВМ 50 пр9граммируются регистры блока 51 интерфейса, селекторы 3 и 4 и счетчик 43 адреса в блоке 8 управления. Последовательность этих операций может быть следующей:

Программирование селектора 4.

А2 : 177777s г запись в регистры 59 и 60 всех единиц, что означает маскирование всех разрядов селектора 4.

Действия по дальнейшему программированию признаков селектора 4 можно не выполнять в виде полного маскирования. В таком режиме на выходах эле- мента 32 в селекторе 4 присутствуют постоянно сигналы высокого уровня, а, следовательно, выходными сигналами на линии 18 сигналы, идентичные стробам, приходящим на вход селектора 4. Это сигналы сопровождения адреса и данных, вырабатываемые формирователем 9 импульсов синхронизации на выходе 19 от сигналов КСИА и КСИП, поданными на входы формирователя 9 (фиг.12, линия ж).

Программирование режима синхронизации.

А4 (0,1,2 разряды : 010 запись в 0,1,2 разряды регистра 66. Задание кода синхронизации на линии 23, открывающего в мультиплексоре 49 в формирователе 9 канал, соответствующий входу D3. Следовательно, на линию 20

|Q

j

20 25 30

4Q с

0

выдается сигнал, соответствующий одному первому признаку селектора 4. Программирование режима запуска.

А4 1 разряд : 12 запись в 7 разряд регистра 66. Задание низкого уровня сигнала От/До для открытия первого плеча элемента И-ИЛИ 39 в блоке 8 управления, т.е. задание режима От (положительного запуска).

А4 J3 разряд : 1 - задание режима запуска по последовательности признаков. Низкий уровень сигнала линии И в группе линий 26 задает разрешение на последовательное срабатывание триггеров в регистре 34.

А4 4,5,6 разряды : 0102 задание режима запуска но последовательности двух первых признаков. Кодом 010 через линии А группы линий 26 мультиплексор 36 открыт по входу 3, и сигнал запуска на линию 21 вырабатывается по срабатыванию двух первых триггеров в регистре 34.

Программирование селектора 3.

A3 : 000000g - запись в регистры всех нулей, что означает отсутствие маскирования разрядов селектора 3.

Так как маскирование признаков отсутствует, необходимо выполнить запись значений признаков в селектор 3. Запись признаков проводится последовательно: сначала первый признак, затем второй и т.д.

А4 ч, 5,6,7 разряды : ЮООг- запись в 4 - 7 разряды регистра 65 кода адресации первого признака.

А6 : OOlOOOg- запись кода ООЮООд в качестве первого признака из селектор 3. Обращение по адресу Аб Формирует импульс записи, который поступает через линию W группы линий 24 на вход записи ассоциативной памяти 32 в селекторе 3. Данные OOlOOOg . поступают на селектор 3 через линии D группы линий 24.

А4 ,5,6,: OlOOj,- запись кода адресации второго признака селектора 3.

Аб : 000123g - запись второго признака, равного 000123д.

Ввиду того, что в качестве условия запуска задана отработка последовательности двух признаков OOlOOOg0001238, то значения остальных признаков можно не конкретизировать.

Запись кода в счетчик адреса 43 блока 8 управления.

А7 : 177777д - запись адреса, равного нулю. ЭВМ 50 оперирует в отридательной логике. При обращении по адресу А7 на линии W в группе линий 27 вырабатывается сигнал, который производит запись адреса в счетчик 43.

Контроль начинается с выработки сигнала Пуск записью в нулевой разряд формирователя 55 лог. 1 Стрсби. запуска, вырабатываемые формирователем 9, поступают с его выхода 19 на входы регистров 1 и 2 и производят запись в указанные регистры состояний с входов 11 и 12. Регистры 1 и 2 хранят записанные состояния до очередного строба и передают их через выходы 15 и 16 на блоки 5 и 6.

Сигнал Пуск ведет к переводу сигнала Пс-Сб в формирователе 57 в высокое состояние. Сигнал Пс-Сб поступает через группы линий 24 и 25 на адресный вход мультиплексора 31 в селекторах З и 4, тем самым разрешая прохождение на входы данных ассоциативной памяти 32 состояний с внутренних информационных линий 15 и линий 16 квалицшкаторов. При поступлении на входы данных ассоциативной памяти 32 состояний, совпадающих со значениями признаков (с учетом маски)s записанных в селекторы 3 и 4 на зтапе программирования, на выходах памяти 32 появляются сигналы совпадения с признаками, которые стробируются сигналами стробов, поступающих через

линию 19 от формирователя 9. Сигналы , вход С триггера 41. ЭВМ 50 контроллепризнаков с выходов 18 селектора 4 поступают на формирователь 9, Формирователь 9 в соответствии с кодом режима синхронизации, поступающим с входов 23, пропускает на выход 20 Сигнал совпадения с первым признаком, которьй используется блоком 8 как строб записи для блоков 5 и 6. Сигналы совпадения с признаками, вырабатываемые селектором 3 запуска, поступают через выходы 17 на блок 7, который, обрабатывая их в соответствии с кодом режима запуска, поступающим с входов 26, выдает при выполнении условия запуска сигнал на выход 21. Для рассматриваемого примера после появления высокого уровня сигнала Пс-Сб, поступающего на вход D триггера 37 триггер устанавливается в 1 сигналом запуска с выхода 21 блока 7. Тем самым через элемент 39 разрешается прохождение сигналов, поступающих с выхода 20 формирователя 9. Стробирующие сигналы поступают на

ра 10 анализатора периодически опрашивает регистр состояния анализатора, обращаясь в цикле чтения по адресу А7. При этом открываются каналы М

40 мультиплексора 58 блока 51 интерфейса а состояния счетчика 43 адреса, триггера 41 останова и триггера 42 передаются через шинные формирователи 54 в ЭВМ 50. После получения информации об

д5 останове анализатора ЭВМ 50 может переходить к считыванию записанной в анализатор информации. Порядок считывания содержимого i-й ячейки блоков 5 и 6 должен быть следующим

50

55

А7 : адрес i - запись в счетчик 43 адреса адреса i.

, BVFFj : 3 A82 - обращение по адресу /А8 в цикле чтения и запись считанного значения в буфер (ОЗУ ЭВМ 50) с меткой BVFF . При чтении из ЭВМ 50 ячейки с адресом А8 открываются каналы К мультиплексора 58 и в ЭВМ передается содержимое i-й ячейки блока 5 памяти.

счетный вход счетчика 43 адреса и через линию W группы 22 выходов производят запись в ячейки блоков 5 и 6 состояний, присутствующих на выходах 15 и 16 регистров 1 и 2. Запись в блоки 5 и 6 производится до переполнения счетчика 43 адреса. Сигнал переполнения поступает на один из входов R триггера 37 и переводит его в нулевое состояние, .элемент 39 закрывается, прохождение стробов записи через него прекращается. Одновременно сигнал переполнения, поступая через элемент 40 на вход С триггера 41 останова, переводит его в нулевое состояние. Сигнал Останов с выхода триггера 41 поступает через группу 28 входов на блок 51 интерфейса и считывается в ЭВМ 50.

В режиме отрицательного запуска (режим До) окно контроля формирует триггер 38, Начинается окно контроля по сигналу Пуск, поступающему на

5 вход S триггера 38, и заканчивается по приходу на вход С триггера 38 сигнала запуска. Содержимое ячеек блоков 5 и 6 при этом может многократно обновляться. По окончанию записи счет0 чик 43 адреса хранит адрес ячейки, в которую происходит последняя запись. Триггер 41 останова при отрицательном запуске срабатывает от сигнала запуска, поступающего через элемент 40 на

5

0

ра 10 анализатора периодически опрашивает регистр состояния анализатора, обращаясь в цикле чтения по адресу А7. При этом открываются каналы М

мультиплексора 58 блока 51 интерфейса, а состояния счетчика 43 адреса, триггера 41 останова и триггера 42 передаются через шинные формирователи 54 в ЭВМ 50. После получения информации об

останове анализатора ЭВМ 50 может переходить к считыванию записанной в анализатор информации. Порядок считывания содержимого i-й ячейки блоков 5 и 6 должен быть следующим

А7 : адрес i - запись в счетчик 43 адреса адреса i.

, BVFFj : 3 A82 - обращение по адресу /А8 в цикле чтения и запись считанного значения в буфер (ОЗУ ЭВМ 50) с меткой BVFF . При чтении из ЭВМ 50 ячейки с адресом А8 открываются каналы К мультиплексора 58 и в ЭВМ передается содержимое i-й ячейки блока 5 памяти.

BVFF,. : любой адрес из А1-Аб - в мультиплексоре 58 открываются каналы L, и в ЭВМ 50 передается содержимое i-й ячейки блока 6.

После считывания содержимого 1-й ячейки блока 6 памяти ЭВМ 50 по значениям разрядов квалификаторов идентифицирует состояние, считанное из ячейки блока 5 памяти и соответствующим образом (фиг. 13) представляет считанную информацию на экране дисплея.

Последовательность считывания содержимого ячеек памяти анализатора, а соответственно в таком же порядке и распаковка считанной информации на экране дисплея, должна быть следующей: при положительном запуске - начать считывание с нулевой ячейки и далее по порядку все ячейки памяти блоков 5 и 6. Если триггер 42 в блоке 8 не установлен в О, что указывает на неполное заполнение памяти (это может произойти, если к считыва нию из анализатора приступили до останова анализатора), то считывать до ячейки, адрес которой равен содержимому счетчика 43 адреса на момент

начала считывания из анализатора. Для 30 па разрядных выходов второго буферного регистра соединена с группой информационных входов селектора признаков записи и группой информационных входов второго блока памяти, группы инотрицательного запуска считывать нужно, начиная с ячейки, на которую указывает счетчик 43 адреса на момент останова анализатора, далее в порядке возрастания адресов до максимально-35 формационных выходов первого и второго блоков памяти образуют первую и вторую группы информационных выходов анализатора для считывания зарегистрированной информации, группы входов

40 задания режима блока управления памятью, блока запуска, селектора признаков запуска и селектора признака записи образуют соответственно первую, вторую, третью и четвертую группы вхо45 дов задания режимов анализатора, группа адресных входов первого блока памяти подключена к первой группе выходов блока управления памятью, вход режима первого блока памяти подключен к

50 выходу блока управления памятью,

вторая группа выходов которого образует третью группу информационных выходов анализатора для считывания слова состояния анализатора, вход запуска

55 блока управления памятью соединен с выходом блока запуска, группа выходов которого подключена к группе выходов селектора признаков запуска, отличающийся тем, что, с целью

го значения, затем с нулевой ячейки и до ячейки, предшествующей ячейке, в которую произошла последняя запись. Если триггер 42 в блоке 8 управления не установлен в О, то значит многократного обновления блоков 5 и 6 памяти после пуска не произошло, и считывать записанную информацию следует, начиная с -нулевой ячейки и далее по порядку до ячейки, адрес которой ра-- вен содержимому счетчика 43 адреса на момент останова анализатора.

Таким образом, анализатор, позволяющий записывать состояния мультиплексированной шины в один блок памяти в той последовательности, как они появляются на шине, и одновременно позволяющий фиксировать значения сигналов квалификаторов для последующей идентификации записанных состояний, обеспечивает контроль шин с нерегуляр ной сменой групп сигналов и разной частотой их появления. Ввод формиро0

5

5

0

вате ля обеспечивает конкретизацию групп состояний, которые должны быть {зафиксированы в памяти анализатора, т.е. позволяет из многообразия групп , состояний мультиплексированной шины: адресов, данных при чтении, данных при записи, векторов прерывания и других, выделить те группы, которые интересны для оператора и тем самым сократить общее время на проведение испытаний мультиплексированных шин.

Формула изобретения

мятью, группа адресных входов и вход 25 выходов блока, первый и четвертый

режима второго блока памяти подключены к первой группе выходов и выходу блока управления памятью соответственно о

ч а

входов задания режима формирователя импульсов синхронизации.

нены с входами элемента И, информационные входы мультиплексора подключены к разрядным выходам регистра и выходу элемента И.

входы элемента ЗИ-ИЛИ объединены и образуют тактовый вход блока, тактовые входы первого и второго триггеров, первый вход элемента 2И-ИЛИ объединены и образуют вход запуска блока, выход первого триггера соединен с вторым входом элемента ЗИ-ИЛИ, информационные входы, вход параллельной загрузки счетчика, третий инверсный и пятый

входы элемента ЗИ-ИЛИ, второй инверсный и третий входы элемента 2И-ИЛИ, D-вход первого триггера, первый вход сброса первого триггера, вход сброса второго триггера, установочные входы

третьего и четвертого триггеров, установочный вход второго триггера образуют группу входов задания режима блока, выход второго триггера соединен с шестым входом элемента ЗИ-ИЛИ,

выход которого соединен со счетным входом счетчика и образует выход блока, выход переполнения счетчика соединен с вторым входом сброса первого триггера, входом сброса четвертого

триггера и четвертым входом элемента 2И-ИЛИ, выход которого соединен с тактовым входом третьего триггера, D-входы второго и третьего триггеров объединены и подключены к шине нулевого потенциала, разрядные выходы

счетчика и выходы третьего и четвертого триггеров образуют вторую группу выходов блока.

L.

г

-J

7

l

F

фиг 4

i

2В

М

J

Фиг. 5

Фиг.6

46/47)

Щи г. 7

Pvt9

/- адрес и данные цикла 680Д

2- адрес и данные цима 880Д-МОДИФИКАЦИЯ- бЬ/вОД ,

3-бек /лор прерывания

Фиг. 11

5 ч

К

t V К)

Й1:

| Патент США № 4434488, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1991-06-07—Публикация

1988-11-21—Подача