К)

Изобретение относится к контрольно-измерительной технике и может быть использовано при регулировке устройств на интегральных схемах, в частности для контроля различных импульсных последовательностей.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности обнаружения превышения частоты обьекта контроля допустимых значений.

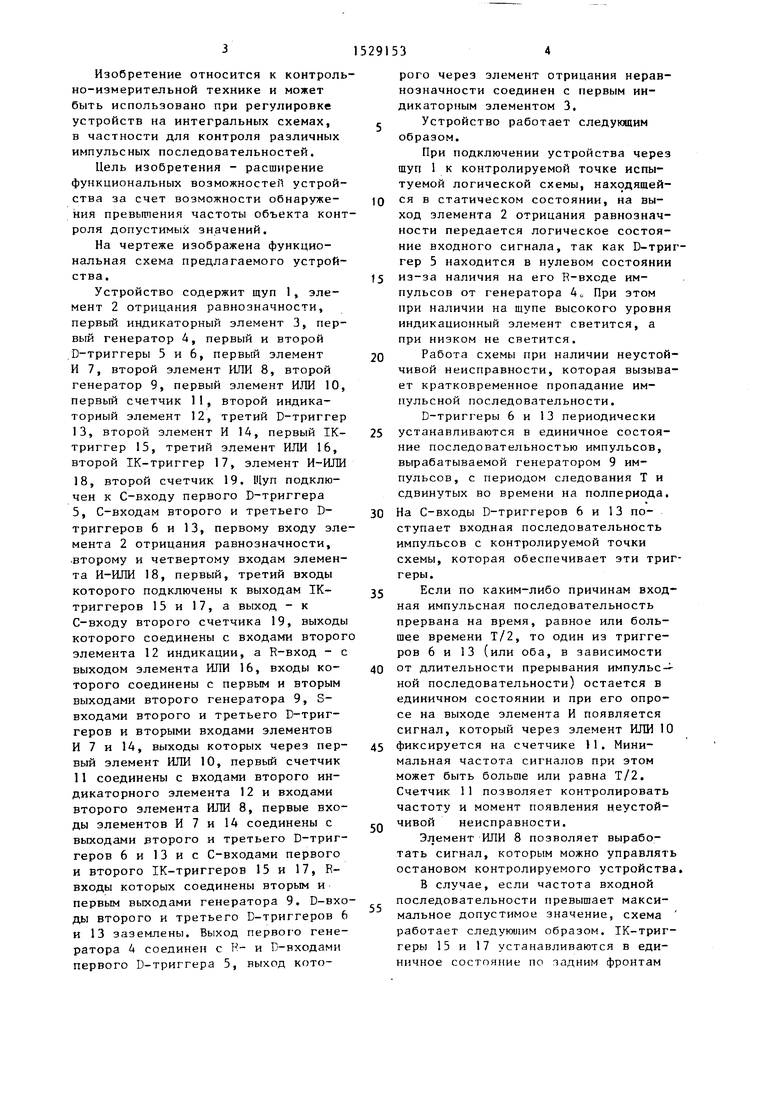

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит щуп 1, элемент 2 отрицания равнозначности, первый индикаторный элемент 3, первый генератор 6, первый и второй D-триггеры 5 и 6, первый элемент И 7, второй элемент ИЛИ 8, второй генератор 9, первый элемент ИЛИ 10, первый счетчик 11, второй индикаторный элемент 12, третий D-триггер 13, второй элемент И 14, первый IK- триггер 15, третий элемент ИЛИ 16, второй 1К-триггер 17, элемент И-ИЛИ 18, второй счетчик 19. Щуп подключен к С-входу первого D-триггера 5, С-входам второго и третьего D- триггеров 6 и 13, первому входу элемента 2 отрицания равнозначности, второму и четвертому входам элемента И-ИЛИ 18, первый, третий входы которого подключены к выходам IK- триггеров 15 и 17, а выход - к С-входу второго счетчика 19, выходы которого соединены с входами второг элемента 12 индикации, а R-вход - с выходом элемента ИЛИ 16, входы которого соединены с первым и вторым выходами второго генератора 9, S- входами второго и третьего D-триг- геров и вторыми входами элементов И 7 и 14, выходы которых через первый элемент ИЛИ 10, первый счетчик 11 соединены с входами второго индикаторного элемента 12 и входами второго элемента ИЛИ 8, первые входы элементов И 7 и 14 соединены с выходами второго и третьего D-триг- геров 6 и 13 и с С-входами первого и второго 1К-триггеров 15 и 17, R- входы которых соединены вторым и первым выходами генератора 9. D-BXO ды второго и третьего D-триггеров 6 и 13 заземлены. Выход первого генератора 4 соединен с R- и D-входами первого D-триггера 5, выход которого через элемент отрицания неравнозначности соединен с первым индикаторным элементом 3. с Устройство работает следующим образом.

При подключении устройства через щуп 1 к контролируемой точке испытуемой логической схемы, находящей0 ся в статическом состоянии, на выход элемента 2 отрицания равнозначности передается логическое состояние входного сигнала, так как D-триггер 5 находится в нулевом состоянии

5 из-за наличия на его R-входе импульсов от генератора 4„ При этом при наличии на щупе высокого уровня индикационный элемент светится, а при низком не светится.

0 Работа схемы при наличии неустойчивой неисправности, которая вызывает кратковременное пропадание импульсной последовательности.

D-триггеры 6 и 13 периодически

5 устанавливаются в единичное состояние последовательностью импульсов, вырабатываемой генератором 9 импульсов, с периодом следования Т и сдвинутых во времени на полпериода.

0 На С-входы D-триггеров 6 и 13 поступает входная последовательность импульсов с контролируемой точки схемы, которая обеспечивает эти триггеры.

5 Если по каким-либо причинам входная импульсная последовательность прервана на время, равное или большее времени Т/2, то один из триггеров 6 и 13 (или оба, в зависимости

0 от длительности прерывания импульсной последовательности) остается в единичном состоянии и при его опросе на выходе элемента И появляется сигнал, который через элемент ИЛИ 10

5 фиксируется на счетчике I1. Минимальная частота сигналов при этом может быть больше или равна Т/2. Счетчик 11 позволяет контролировать частоту и момент появления неустойQ чивой неисправности.

Элемент ИЛИ 8 позволяет выработать сигнал, которым можно управлять остановом контролируемого устройства,

В случае, если частота входной последовательности превышает максимальное допустимое значение, схема работает следующим образом. 1К-триг- геры 15 и 17 устанавливаются в единичное состояние по задним фронтам

51

импульсов с выходов триггеров 6 и 13 и сбрасываются в ноль импульсами с выходов генератора 9. В случае, если частота входной последовательности больше допустимой, совпадения на элементе И-ИЛИ 18 входной последовательности с импульсами с выходов триггеров 15 и 17 не происходит. Если частота входной последователь- ности становится больше максимальной, то в этом случае изменяется длительность импульсов на выходах триггеров 6 и 13 и соответственно изменяется длительность импульсов на выходе триггеров 15 и 17 и происходит совпадение на элементе И-ИЛИ 18. На вход счетчика 19 поступают

лишние импульсы с элемента И-ИЛИ 18. Содержимое счетчика индицирует- ся элементом 12 индикации. Обновление содержимого счетчика идет каждые полпериода импульсной последовательности генератора 9.

Таким образом, по характеру сне- чения индикаторного элемента 3 можно судить о скважности контролируемой последовательности, а также по характеру работы индикаторного элемента 12 можно определить возникно- вение кратковременных неисправностей и осуществить количественную оценку входных контролируемых импулсов.

36

Таким образом, дoпoлиvIтeльнoe введение в схему двух 1К-триггеров, элемента И-ИЛИ, третьего элемента ИЛИ и второго счетчика позволяет контролировать не только пропадание импульсов в рассматриваемой последовательности сигналов, а также появления лишних импульсов.

Формула изобретения

Устройство для контроля логических схем по авт. св. № 1140066, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены первый и второй 1К-триггеры, элемент И-ИЛИ, третий элемент ИЛИ и второй счетчик, С-вхо- ды 1К-триггеров соединены с выходами второго и третьего D-триггеров соответственно, R-входы первого и второго 1К-триггеров соединены с вторым и первым выходами второго генератора и с входами третьего элемента ИЛИ, выход которого соединен с R- входом второго счетчика, выходы которого соединены с входами второго индикаторного элемента, а С-вход - с выходом элемента И-ИЛИ, первый и третий входы которого соединены с выходом первого и второго 1К-триг- геров, а второй и четвертый входы - со щупом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических схем | 1983 |

|

SU1140066A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1383236A1 |

| Устройство для контроля логических схем | 1980 |

|

SU892364A1 |

| Устройство для контроля генератора тактовых импульсов | 1987 |

|

SU1465838A2 |

| Устройство фазовой синхронизации | 1985 |

|

SU1332553A1 |

| Устройство для допускового контроля частоты | 1989 |

|

SU1626358A1 |

| Устройство контроля импульсов тактовой частоты | 1986 |

|

SU1378033A1 |

| Устройство для контроля логических схем | 1976 |

|

SU716040A1 |

| Нормализатор длительности импульсов | 1985 |

|

SU1257822A1 |

| Устройство для определения моментов экстремумов | 1987 |

|

SU1524008A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано при регулировке устройств на интегральных схемах. Цель изобретения - расширение функциональных возможностей - достигается путем обеспечения обнаружения превышения частотой объекта контроля допустимых значений. Устройство содержит щуп 1, элемент 2 отрицания равнозначности, индикаторные элементы 3 и 12, генераторы 4 и 9, D - триггеры 5,6,13, элементы И 7 и 14, элементы ИЛИ 10,8 и 16, счетчики 11 и 19, JK-триггеры 15 и 17, элемент И-ИЛИ 18. Введение в устройство двух JK-триггеров, элемента И-ИЛИ, третьего элемента ИЛИ и второго счетчика позволяет контролировать не только пропадание импульсов в контролируемой последовательности, но и появление лишних импульсов. 1 ил.

| Устройство для контроля логических схем | 1983 |

|

SU1140066A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-12-15—Публикация

1987-12-21—Подача