IS - 23

Нэобретенне относится к контрольно-измерительной технике и может быть использовано нри наладке, контроле и диагностике цифровых уст- ройств, выполненных на интегральных микросхемах, включ ая БИС и микросхемы, выходы которых переключаются в- третье состояние.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности контроля импульсных сигналов с выходов элементов с третьим состоянием, а также контроля одиночных или редко появляющихся импульсных сигналов малой длительности.

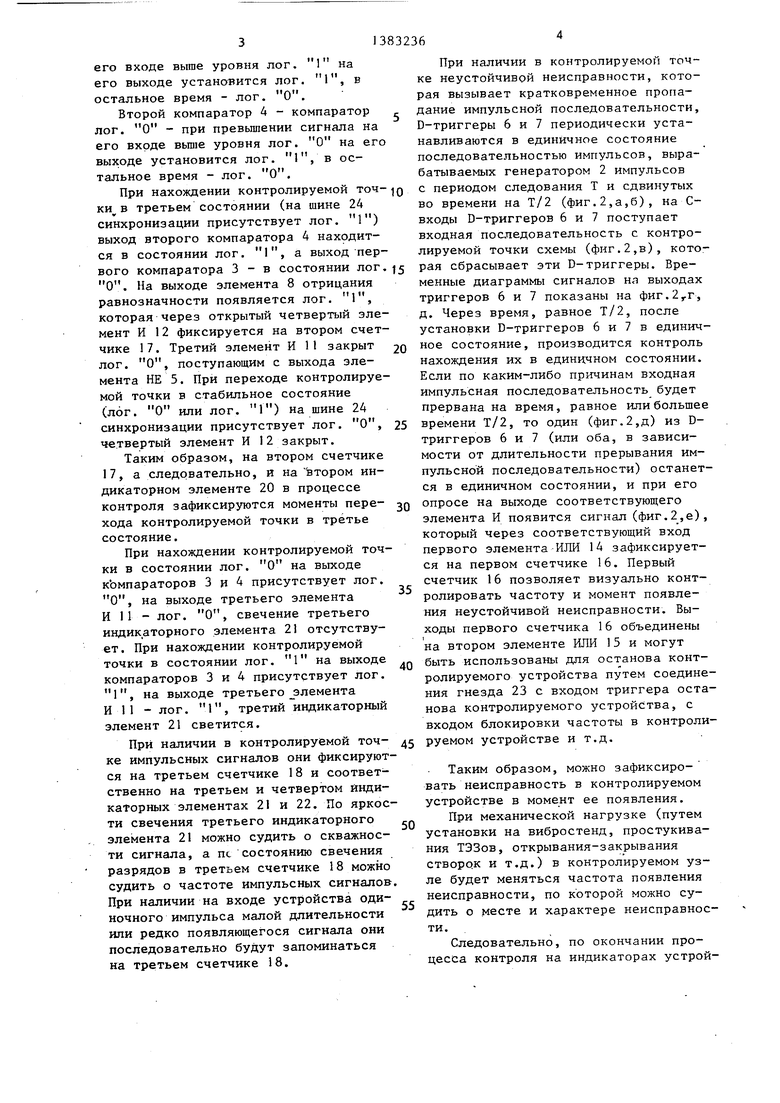

На фиг.1 изображена функциональная схема устройства; на фиг.2 - временные диаграммы, поясняющие его ра- боту.

Устройство содержит щуп 1, генератор 2 импульсов, первый 3 и второй 4 компараторы, элемент НЕ 5, первый 6 и второй 7 D-триггеры, элемент 8 от- рицания равнозначности, первый 9, второй 10, третий II и четвертый 12 элементы И, кнопку 13, первый 14 и второй 15 элементы ИЛИ, первый 16, второй 17 и третий 18 счетчики, пер- вый 19, второй 20, третий 21 и четвертый 22 индикаторные элементы, гнездо 23 и шину 24 синхронизации.

Щуп 1 соединен с входами первого 3 и второго 4 компараторов, выход первого компаратора 3 соединен с первым входом элемента 8 отрицания равнозначности и первым входом третьего элемента И 11, третий вход которого соел,инен с выходом элемента НЕ 5, вход которого соединен с первым входом четвертого элемента И 12 и с шиной 24 синхронизации, выход элемента 8 отрицания равнозначности соединен с вторым входом четвёртого элемента И 12, выход которого соединен со счетным входом второго счетчика 17, выходы которого соединены с соответствующими входами второго индикаторного элемента 20, выход третьего эле- мента И 11 соединен с входом третьего индикаторного элемента 21, с С- входами первого 6 и второго 7 D-триггеров и со счетным входом третьего счетчика 18, выходы которого соедине- ны с соответствующими входами четвертого индикаторного элемента 22, единичный вход первого D-триггера 6 соединен с первым выходом генератора 2

импульсов, единичный вход второго D-триггера 7 - с вторым выходом генератора 2 импульсов, D-входы первого. 6 и второго 7 D-триггеров соединены с нулевой шиной, а выходы - с первыми входами первого 9 и второго 10 элементов И соответственно, второй вход первого элемента И 9 соединен с вторым выходом генератора 2 импульсов, а второй вход второго элемента И 10 - с первым выходом генератора 2 импульсов, выходы первого 9 и второго 10 элементов И соединены с соответствующими входами первого элемента ИЛИ 14, выход которого соединен со счетным входом первого счетчика 16, выходы которого соед инены с соответствующими входами первого индикаторного элемента 19 и входами второго элемента ИЛИ 15, выход которого соединен с гнездом 23, R-входы первого 16, второго 17 и третьего 18 счетчиков соедииены с выходом кнопки 13, причем выход второго компаратора 4 соединен с вторым входом элемента 8 отрицания равнозначности и вторым входом третьего элемента И 11.

Устройство работает следующим образом.

Минимальная длительность неустойчивых неисправностей, вызванных временным нарушением контакта в цепи, наличием непропаев, появлением микро трещин в печатных платах, появлением замыканий и т.д., находится обычно в миллисекундном интервале времени, поэтому в этом же интервале должна быть и частота генератора 2 импульсов. Ген(ератор 2 импульсов вырабатывает две серии импульсов, -сдвинутые во времени на полпериода в миллисекундном диапазоне времени, например Р,3 мс.

В исходном состоянии счетчики 16- 18 находятся в сброшенном состоянии. Сброс осуществляется нажатием кнопки 13, щуп 1 подключается к контролируемой точке испытуемой логической схемы, а шина 24 синхронизации - к сигналу в испытуемой схеме, который управляет элементами с третьим состоянием. Причем, если выход э лемента находится в третьем состоянии, на шине 24 синхронизации должна быть лог.1 в остальное время на шине 24 синхронизации должен быть лог. О.

Первый компаратор 3 - компаратор лог. 1 - при превышении сигнала на

1 на 1, в

его входе выше уровня лог. его выходе установится лог остальное время - лог. О,

Второй компаратор 4 - компаратор лог. О - при превьппении сигнала на его входе вьш1е уровня лог. О на его выходе установится лог. 1, в остальное время - лог. О.

При нахождении контролируемой ТОЧки в третьем состоянии (на шине 24 синхронизации присутствует лог. 1) выход второго компаратора 4 находится в состоянии лог. I, а выход первого компаратора 3 - в состоянии лог О. На выходе элемента 8 отрицания равнозначности появляется лог. 1, которая через открытый четвертый элемент И 12 фиксируется на втором счетчике 17. Третий элемент И П закрыт лог. О, поступающим с выхода элемента НЕ 5. При переходе контролируемой точки в стабильное состояние (лог. О или лог. 1) на шине 24 синхронизации присутствует лог. О, четвертый элемент И 12 закрыт.

Таким образом, на втором счетчике 17, а следовательно, и на втором индикаторном элементе 20 в процессе контроля зафиксируются моменты перехода контролируемой точки в третье состояние.

При нахождении контролируемой точки в состоянии лог. О на выходе к омпараторов 3 и 4 присутствует лог. О, на выходе третьего элемента И 11 - лог. О, свечение третьего индикаторного элемента 21 отсутствует. При нахождении контролируемой точки в состоянии лог. 1 на выходе компараторов 3 и 4 присутствует лог. 1, на выходе третьего элемента И 11 - лог. 1, третий индикаторный элемент 21 светится.

При наличии в контролируемой точке импульсных сигналов они фиксируются на третьем счетчике 18 и соответственно на третьем и четвертом индикаторных элементах 21 и 22. По яркости свечения третьего индикаторного элемента 21 можно судить о скважности сигнала, а пс состоянию свечения разрядов в третьем счетчике 18 можно судить о частоте импульсных сигналов При наличии на входе устройства одиночного импульса малой длительности или редко появляющегося сигнала они последовательно будут запоминаться на третьем счетчике 18.

При наличии в контролируемой точке неустойчивой неисправности, которая вызывает кратковременное пропадание импульсной последовательности, D-триггеры 6 и 7 периодически устанавливаются в единичное состояние последовательностью импульсов, вырабатываемых генератором 2 импульсов с периодом следования Т и сдвинутых во времени на Т/2 (фиг.2,а,б), на С- входы D-триггеров 6 и 7 поступает входная последовательность с контролируемой точки схемы (фиг,2,в), которая сбрасывает эти D-триггеры. Временные диаграммы сигналов на выходах триггеров 6 и 7 показаны на фиг.2,.г, д. Через время, равное Т/2, после установки D-триггеров 6 и 7 в единичное состояние, производится контроль нахождения их в единичном состоянии. Если по каким-либо пр гчинам входная импульсная последовательность будет прервана на время, равное или большее времени Т/2, то один (фиг.2,д) из D- триггеров 6 и 7 (или оба, в зависимости от длительности прерывания импульсной последовательности) останется в единичном состоянии, и при его опросе на выходе соответствующего элемента И появится сигнал (фиг.2,е), который через соответствующий вход первого элемента-ИЛИ 14 зафиксируется на первом счетчике 16. Первый счетчик 16 позволяет визуально контролировать частоту и момент появления неустойчивой неисправности. Выходы первого счетчика 16 объединены на втором элементе ИЛИ 15 и могут быть использованы для останова контролируемого устройства путем соединения гнезда 23 с входом триггера останова контролируемого устройства, с входом блокировки частоты в контролируемом устройстве и т.д.

Таким образом, можно зафиксиро- вать неисправность в контролируемом устройстве в момент ее появления.

При механической нагрузке (путем установки на вибростенд, простукивания ТЭЗов, открывания-закрывания створок и т.д.) в контролируемом узле будет меняться частота появления неисправности, по которой можно судить о месте и характере неисправности.

Следовательно, по окончании процесса контроля на индикаторах устройства для контроля логических схем будет представлена информация о моментах перехода контролируемой точки в третье состояние, о наличии сбойной ситуации, вызванной кратковременным пропаданием импулыгной последовательности, о наличии в контролируемой точке одиночных или редко появляющихся импульсных сигналов малой длительности, по совокупности которой можно судить о работоспособности контролируемого устройства.

Формула изобретения

Устройство для контроля логических схем, содержащее щуп, элемент отрицания равнозначности, генератор импульсов, первый и второй D-триггеры,

первый и второй элементы И, первый и второй элементы ИЛИ, первый счетчик, первый индикаторный элемент и гнездо причем единичный вход первого О-триг гера соединен с первым выходом гене- ратора импульсов, единичный вход второго D-триггера - с вторым выходом генератора импульсов, D-входы первого и второго D-триггеров соединены с нулевой шиной, а выходы - с первыми входами первого и второго элементов И соответственно, второй вход первого элемента И соединен с вторым выходом генератора импульсов, а второй вход второго элемента И - с первым выходом генератора импульсов, выходы первого и второго элементов И соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, выходы которого соединенй

с соответствующими входами первого индикаторного элемента и входами второго элемента ИЛИ, выход которого соединен с гнездом, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены первый и второй компараторы, элемент НЕ, третий и четвертый элементы И, второй .и третий счетчики, второй, третий и четвертый индикаторные элементы, кнопка, причем щуп соединен с входами первого и второго компараторов, выход первого компаратора соединен с первым входом элемента отрицания равнозначности и с первым входом третьего элемента И, выход второго компаратора соединен с вторым входом элемента отрицания равнозначнос.ти и с вторым входом третьего элемента И, третий вход которого соединен с выходом элемента НЕ, вход которого соединен с первым входом четвертого элемента И и с шиной синхронизации, выход элемента отрицания равнозначности соединен с вторым входом четвертого элемента И, выход которого соединен со счетным входом второго счетчика, выходы которого соединены с соответствующими входами второго индикаторного элемента, выход третьего элемента И соединен с входом третьего индикаторного элемента, с С-входами первого и второго D-триггеров и со счетным входом третьего счетчика, выходы которого соединены с соответствующими входами четвертого индикаторного элемента, R-входы первого, второго и третьего счетчиков соединены с кнопкой.

.LJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических схем | 1983 |

|

SU1140066A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля логических схем | 1987 |

|

SU1529153A2 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля цифровых последовательностей | 1988 |

|

SU1603388A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| Устройство контроля электрического монтажа | 1987 |

|

SU1478165A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля хода программы | 1983 |

|

SU1236487A1 |

Изобретение может быть использовано при наладке, контроле и диагностике цифровых устройств, выполненных на интеграл1 ных микросхемах. Цель изобретения - расширение функциональных возможностей устройства. Устрой- -ство содержит генератор 2 импульсов, D-триггеры 6 и 7, элемент 8 отрицания равнозначности, элементы И 9 и 10, элементы ИЛИ 14 и 15, счетчик 16 и индикаторный элемент 19. Введение компараторов 3 и 4, элемента НЕ 5, элементов И 11 и 12, счетчиков 17 и 18 индикаторных элементов 20, 21 и 22 и образование новых функциональных связей обеспечивает возможность контроля импульсных сигналов с выходов элементов с третьим состоянием. Кроме того, становится возможным контроль одиночных или редкоподводя- щихся импульсных сигналов малой длительности. 2 ил. (О (Л

Фиг. 2

| Многофункциональный логический зонд | 1981 |

|

SU970280A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-02—Подача