Г

Изобретение относится к области вьг-. числительной техники и может быть использовано для контроля исправности и поиска неисправностей в логических схемах цифровой и импульсной,техники.

Известно устройство для проверки логических -схем, позволяющее фиксировать уровень логического .6й гнала, а также индицировать наличие импульсного сигнала l..

Наиболее близким техническим решением к данному изобретению является , устройство для контроля логических схем содержащее элемент отрицания равнозначности, первый вход которого соединен со щупом, другой вход - с выходом Д-триггера, а выход - со входом индикаторного элемента, С-вход Д-триггера соединен со щупом, а его Д-и R -входы - с выходом генератора импульсов Lsj.

Недостаток известных устройств состоит в том, что они дают возможность

лишь наблюдать за состоянием схемы, но не позволяют изменять его.

Цель изобретения заключается в расширении ;функциональных возможностей устройства.

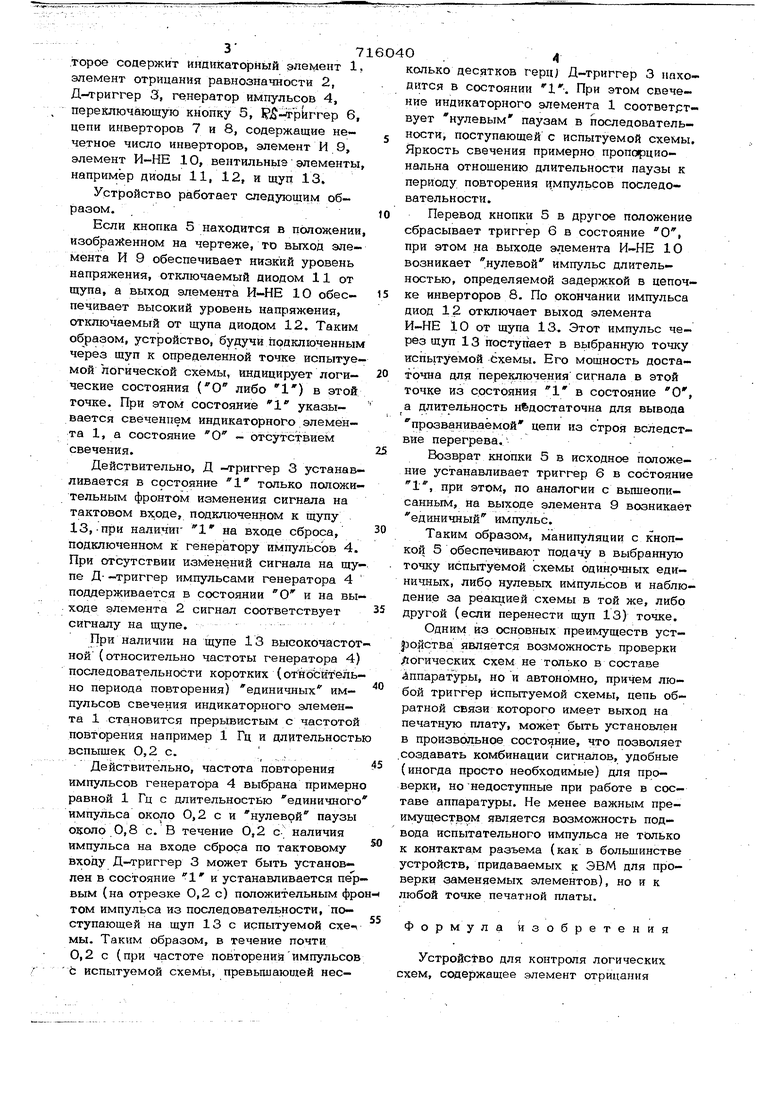

Это достигается тем, что в предлагаемое устройство для Контроля логических схем введены RS- триггер, входы которого соединены с переключающим элементом, а выходы - со входами двух цепей пос0ледовательно соединенных инверторов, элементы И, И-НЕ и вентильные элемен- ты, причем один выход PS-триггера соединен с одним из входов элемента И, другой вход которого со,единен с выхо5дом одной цепи инверторов, другой выход R§-триггера соединен с одним из входов элемента И-НЕ, другой вход которого соединен с другой цепи инверторов, выходы элементов И и И-НЕ соединены через вентильные элементрл со щупом.

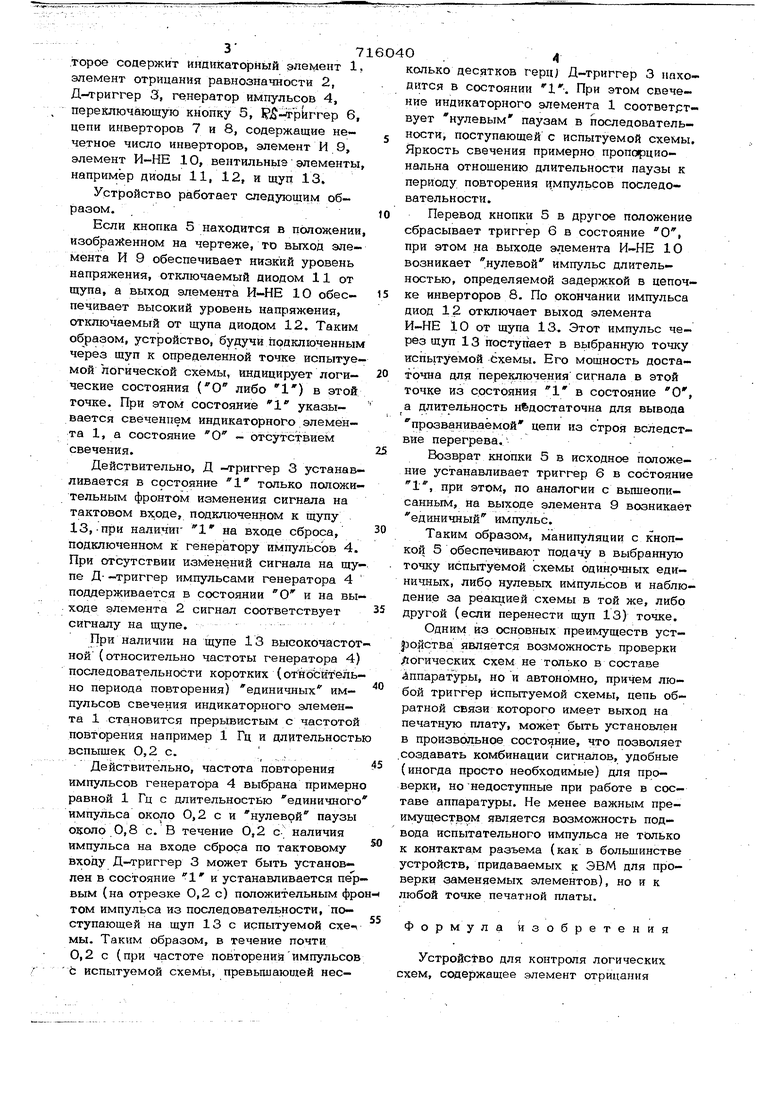

На чертеже изображенп фупкциональ- ная схема предлагаемого устройства, ко.торое содержит индикаторный элемент 1, элемент отрицания равнозначности 2, Д-триггер 3, генератор импульсов 4, переключающую кнопку 5, 6, цепи инверторов 7 и 8, содержащие нечетное число инверторов, элемент И 9, элемент И-НЕ 10, вантильныэ элементы, например диоды 11, 12, и щуп 13, Устройство работает следующим образом. Если кнопка 5 находится в положении, изображенном на чертеже, то выход элемента И 9 обеспечивает низкий уровень напряжения, отключаемый диодом 11 от щупа, а выход элемента И-НЕ 10 обеспечивает высокий уровень напряжения, отключаемый от щупа диодом 12. Таким образом, устройство, будучи подключенным через щуп к определенной точке испытуемой логической схемы, индицирует логические состояния (О либо 1) в этой точке. При этом состояние i указывается свечением индикаторного элемента 1, а состояние О - отсутствием свечения. Действительно, Д -триггер 3 устанавливается в состояние 1 только положительным фронтом изменения сигнала на тактовом входе, подключенном к щупу 13,-при наличиг I на входе сброса, подключенном к генератору импульсов 4. При отсутствии изменений сигнала на щупе Д- -триггер импульсами генератора 4 поддерживается в состоянии О и на выходе элемента 2 сигнал соответствует сигналу на щупе. При наличии на щупе 13 высокочастот ной (относительно частоты генератора 4) последовательности коротких (отНбсительно периода повторения) единичных импульсов свечения индикаторного элемента 1 становится прерывистым с частотой повторения например 1 Гц и длительность вспышек 0,2 с., Действительно, частота повторения импульсов генератора 4 выбрана примерн равной 1 Гц с длительностью единичного импульса около 0,2 с и нулеврй паузы О5ОЛО 0,8 с. В течение 0,2 с- наличия импульса на входе сброса по тактовому входу Д- риггер 3 может быть установлен в состояние 1 и устанавливается пер вым (на отрезке 0,2 с) положительным фр том импульса из последовательности, поступающей на щуп 13с испытуемой схе мы. Таким образом, в течение почти 0,2 с (при частоте повторенийимпульсов fc испытуемой схемы, превышающей несколько десятков герц/ Д-триггер 3 находится в состоянии 1. При этом свечение индикаторного элемента 1 соответртвует нулевым паузам в последовательности, поступающей с испытуемой схемы. Яркость свечения примерно пропорциональна отнощению длительности паузы к периоду повторения импульсов последовательности. Перевод кнопки 5 в другое положение сбрасывает триггер 6 в состояние О, при этом на выходе элемента И-НЕ 10 возникает .нулевой импульс длительностью, определяемой задержкой в цепочке инверторов 8. По окончании импульса диод 12 отключает выход элемента И-НЕ 10 от щупа 13 Этот импульс через щуп 13 поступает в выбранную точ1су испытуемой Схемы. Его мощность достаточна для переключения сигнала в этой точке из состояния 1 в состояние О, а длительность недостаточна для вывода - прозваниваемой цепи из строя вследствие перегрева. Возврат кнопки 5 в исходное положение устанавливает триггер 6 в состояние I, при этом, по аналогии с вышеописанным, на выходе элемента 9 возникает единичный импульс. Таким образом, манипуляции с кнопкой 5 обеспечивают подачу в выбранную точку испытуемой схемы одиночных единичных, либо нулевых импульсов и наблюдение за реавдией схемы в той же, либо другой (если перенести щуп 13) точке. Одним из основных преимуществ уст|эойства является возможность проверки Логических схем не только в составе Аппаратуры, но и автономно, причем любой триггер испытуемой схемы, цепь обратной связи которого имеет выход на печатную плату, может быть установлен в произвольное состояние, что позволяет .создавать комбинации сигналов, удобные (иногда просто необходимые) для проверки, но недоступные при работе в составе аппаратуры. Не менее важным преимуществом является возможность подвода испытательного импульса не тсшько к контактам разъема (как в большинстве устройств, придаваемых к ЭВМ для проверки заменяемых элементов), но и к любой точке печатной платы. Формула изобретения Устройство для контроля логических схем, содержащее элемент отрицания равнозначности, первый вход которого соединен со щупом, другой вход - с выходом Д-триггера, а выход - со входом индикаторного элемента, С - вход Д-триггера соединен со щупом, а его Ди R - входы - с выходом генератора импульсов, о т л и ч а и ш е е с я тем, что, с .целью .расширения функцио.нальных возможностей устройства, в него введены РЙ-триггер, входы которого соединены с переключающим злемейтШу а выходы - со входом-двух цепей после довательно соединенных инверторов, элементы И, И-НЕ и вентильные элементы. ....- .., ..,-,.д- .. ,-лллг.ю.4Ц1о o «v-™v5niiii, причем ОДИН выход 1 3-трйггера соединен с одним из входов элемента И, дру706 гой вход которого соеднйен с выходом одной дёпи инверторов, другой выход RS-триггера соединен с одним их входом элемента И-НЕ, другой вход которого соединен с выходом другой цепи инверторов, выходы элементов И и И-НЕ соединены через вентильные элементы со щупом, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 428291, кл. d 01 I 19/16, 1974. 2.Назаров Н. Ф. Индикатор проверки логических устройств Приборы и ЛИ jiui . /отрОИО-ГВ ИрИООрЫ системы управления N 12, 1974, с. 38-39 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических схем | 1980 |

|

SU892364A1 |

| Устройство для контроля логических схем | 1983 |

|

SU1140066A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1383236A1 |

| Устройство для проверки логических блоков | 1978 |

|

SU734625A1 |

| Устройство для контроля логических схем | 1987 |

|

SU1529153A2 |

| Управляемый вентильный электродвигатель | 1977 |

|

SU738059A1 |

| Устройство для контроля временных параметров реле | 1981 |

|

SU1022117A1 |

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ИСПЫТАНИЙ | 1973 |

|

SU382983A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ СРАБАТЫВАНИЯ БЛОКОВ ЗАЩИТЫ ЭЛЕКТРОПИТАНИЯ | 1992 |

|

RU2093941C1 |

| Устройство для контроля электрического монтажа | 1989 |

|

SU1698843A1 |

Авторы

Даты

1980-02-15—Публикация

1976-01-22—Подача