Изобретение относится к области контрольно-измерительной техники и может быть использовано для контроля логических схем цифровой и импульсной техники.

Известно устройство для проверки логических схем, позволяющее фиксировать уровень логического сигнала, а также индицировать наличие импульсного периодического сигнала СИ.

Недостатком известного устройства являются ограниченные функциональные возможности вследствие того, что оно лишь обеспечивает контроль состояния логической схемы, но не может изменить его.

Наиболее близким техническим решением к изобретению является устройство для контроля логических схем, содержащее элемент отрицания равнозначности, первый вход которого соединен со щупом, другой вход - с выходом Д-триггера, а выход - со входом индикаторного элемента, С-вход Д-триггера соединен со щупом, а его Д и R - входы - с выходом генератора импульсов, R S - триггер, входы ,которого соединены с переключающим элементом, а выходы - со входами двух цепей последовательно соединенных инверторов,элементы И, И-НЕ и вентильные элементы, причем йыход R S-триггера соединен с одним из входов элемента И, второй вход которого соединен с выходом одной цепи инверторов, инверсный выход R S триггера соединен с одним из входов элемента И-НЕ,второй вход которого соединен с выходом другой цепи ин10верторов, выходы элементов И и И-НЕ соединены через вентильные элементы со щупом С 2.

Недостатком известного устройства является низкая надежность, обуслов15 ленная тем, что испытательный сигнал на контролируемую точку логической схемы должен содержать и нулевые и единичные кратковременные импульсы независимо от того, какой постоян20ней логический уровень присутствуетна контролируемой точке. Вследствие этого, устройство должно содержать две цепи последовательно связанных инверторов, что снижает его нгщеж25ность за счет большого чиспа инверТСфОВ.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, 30 что в устройство для контроля логическиX схем, содержащее первый вентильный элемент, элемент отрицания равнозначности, первый вход которого соединен со щупом, другой вход с выходом Д-триггера, а первый выход - со входом индикаторного э.лемента. С- вход Д -триггера соединен со щупом, а его Д и R - входы с втлходом генератора импульсов, R Sтриггер, входы которого соединены с переключающим элементом , а выход со входом цепи последовательно соединенных инверторов, первый элемент И, один из входов которого соединен с выходом R S - триггера, другой вход - с выходом цепи последователь но соединенных инверторов, элемент И-ИЕ, выход которого соединен со входом второго вентильного элемента выход которого соединен с выходом первого вентильного элемента и со щупом, введен второй элемент И, причем, выход первого элемента И соединен с первыми входа .и элемента И-НЕ и BTOjioro элемента И, вторые входы которых соединены соответственно с первым и вторым выходами элемента отрицания равнозначности, а выход второго элемента И соединен со входом первого вентильного элемента.

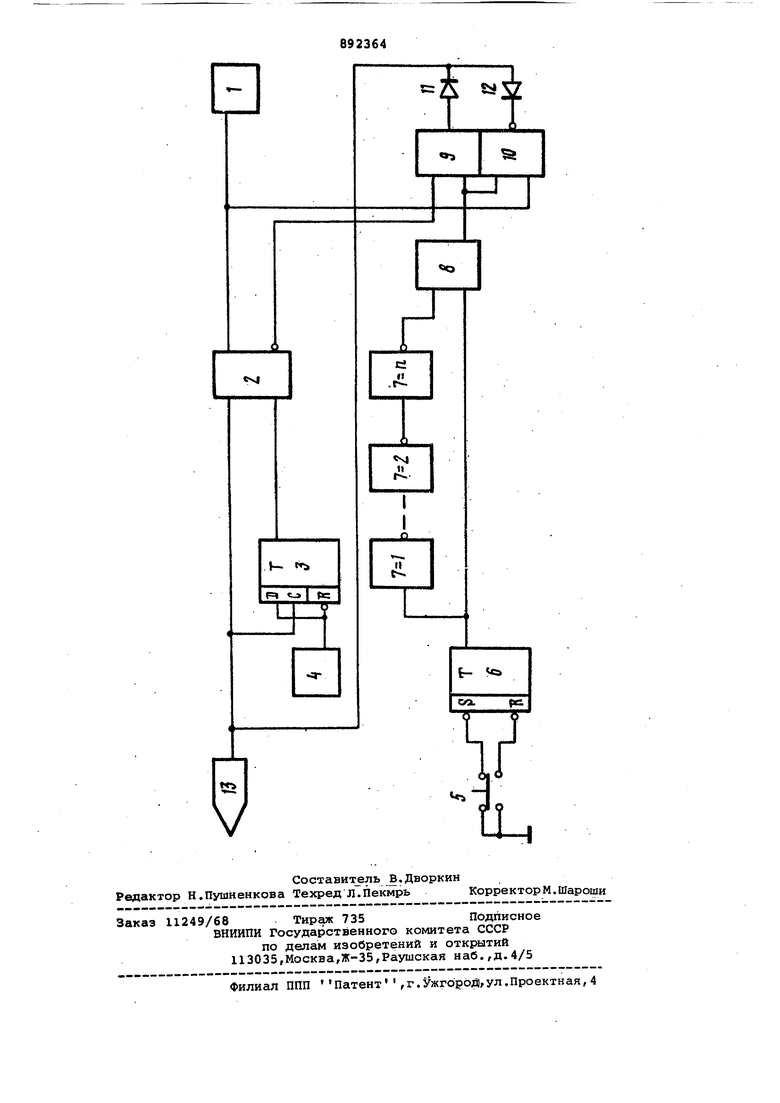

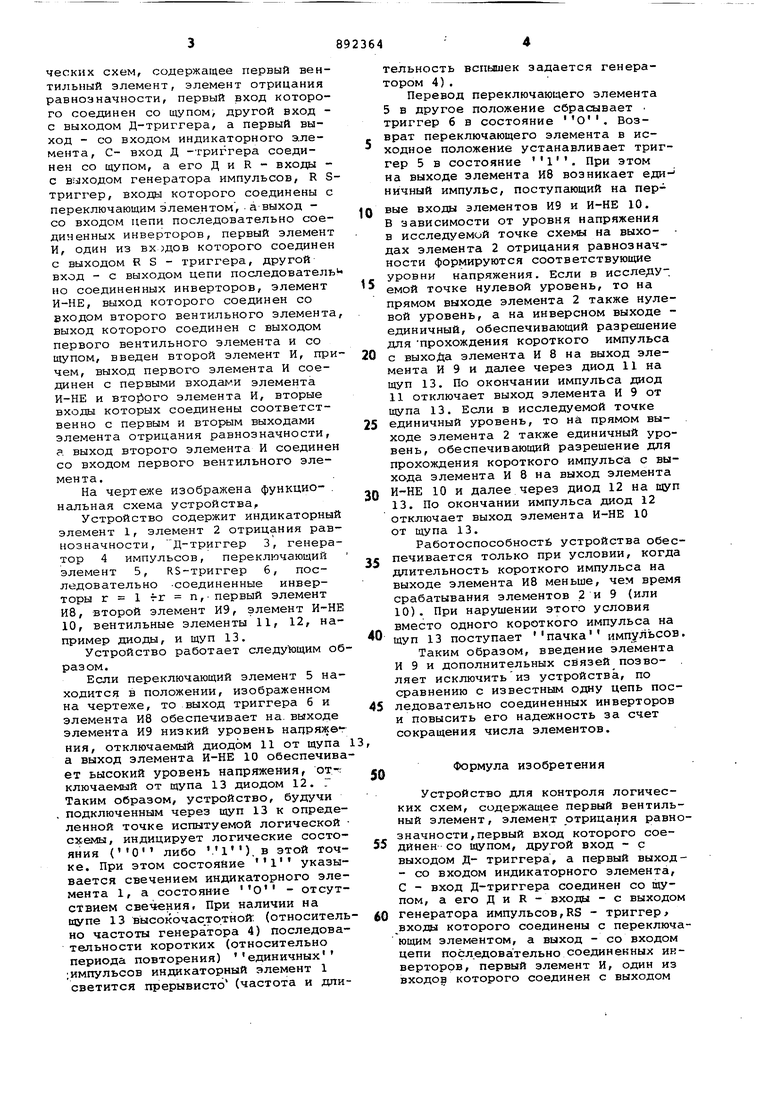

На чертеже изображена функцио- . налъная схема устройства.

Устройство содержит индикаторный элемент 1, элемент 2 отрицания равнозначности, Д-триггер з, генератор 4 импульсов, переключающий элемент 5, RS-триггер 6, последовательно -соединенные инверторы г 1 тг п,- первый элемент И8, второй элемент И9, элемент И-НЕ 10, вентильные элементы 11, 12, например диоды, и щуп 13.

Устройство работает следующим образом.

Если переключающий элемент 5 находится в положении, изображенном на чертеже, то выход триггера б и элемента И8 обеспечивает на. выходе элемента И9 низкий уровень напряжения, отключаемый диодом 11 от щупа а выход элемента И-НЕ 10 обеспечивает высокий уровень напряжения, ключаемый от щупа 13 диодом 12. Г Таким образом, устройство, будучи , подключенным через щуп 13 к определенной точке испытуемой логической схемы, индицирует логические состояния С О либо .), в этой точке. При этом состояние указывается свечением индикаторного элемента 1, а состояние О - отсутствием сведения г При наличии на щупе 13 высокочас тотной: (относительно частоты генератора 4) последовательности коротких (относительно периода повторения) единичных ;импульсов индикаторный элемент 1 светится прерывисто (частота и длительность вспьвиек задается генератором 4) .

Перевод переключающего элемента 5 в другое положение сбрасывает . триггер 6 в состояние О. Возврат переключающего элемента в исходное положение устанавливает триггер 5 в состояние . При этом на выходе элемента И8 возникает единичный импульс, поступающий на первые входы элементов И9 и И-НЕ 10. В зависимости от уровня напряжения в исследуемой точке схемы на выходах элемента 2 отрицания равнозначности формируются соответствующие уровни напряжения. Если в исследуемой точке нулевой уровень, то на прямом выходе элемента 2 также нулевой уровень, а на инверсном выходе единичный, обеспечивающий разрешение для прохождения короткого импульса с выхода элемента И 8 на выход элемента И 9 и далее через диод 11 на щуп 13. По окончании импульса диод 11 отключает выход элемента И 9 от щупа 13. Если в исследуемой точке единичный уровень, то на прямом выходе элемента 2 также единичный уровень, обеспечивающий разрешение для прохождения короткого импульса с выхода элемента И 8 на выход элемента И-НЕ 10 и далее через диод 12 на щуп 13. По окончании импульса диод 12 отключает выход элемента И-НЕ 10 от щупа 13.

Работоспособность устройства обеспечивается только при условии, когда длительность короткого импульса на выходе элемента И8 меньше, чем время срабатывания элементов 2 и 9 (или 10). При нарушении этого условия вместо одного короткого импульса на щуп 13 поступает пачка импульсов

Таким образом, введение элемента И 9 и дополнительных связей позволяет исключить из устройства, по сравнению с известным одну цепь последовательно соединенных инверторов и повысить его надежность за счет сокращения числа элементов.

Формула изобретения

Устройство для контроля логических схем, содержащее первый вентильный элемент, элемент отрицания равнозначности, первый вход которого соединен со щупом, другой вход - с выходом Д- триггера, а первый выход- со входом индикаторного элемента, С - вход Д-триггера соединен со щупом, а его Д и R - входы - с выходом генератора импульсов,RS - триггер входы которого соединены с переключающим элементом, а выход - со входом цепи последовательно соединенных инверторов, первый элемент И, один из входо которого соединен с выходом

R S - триггера, другой вход - с выходом цепи последовательно соединенных инверторов,элемент И-НЕ выход которо-го соединен со входом второго вентильного элемента,выход которого соединен с выходом первого вентильного элемента

и со щупом, отлич atpmeec я тем, что, с целью повьшения надеж-, ности устройства, в него введен второй элемент И, причем выход первого элемента И соединен с первыми элемента И-НЕ и второго элемента И, вторые входы которых соединены соответственно с первым и вторым выходами элемента.отрицания равнозначности, а выход второго элемента И соединен со входом первого вентильного элемента.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №428291, кл. G 01 R 19/16, 1974.

2.Авторское свидетельство СССР

0 716040, кл. G 01 R 31/28, 1970 (прототип).

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических схем | 1976 |

|

SU716040A1 |

| Устройство для контроля логических схем | 1983 |

|

SU1140066A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1383236A1 |

| Устройство для контроля логических схем | 1987 |

|

SU1529153A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345204C2 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ | 1991 |

|

SU1819100A1 |

| Устройство для проверки логических блоков | 1978 |

|

SU734625A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345203C2 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| Устройство для контроля токового режима управляемого вентильного преобразователя | 1984 |

|

SU1229893A1 |

Авторы

Даты

1981-12-23—Публикация

1980-04-09—Подача